基于FPGA的帧转移面阵CCD驱动电路设计

CCD驱动电路及处理电路设计

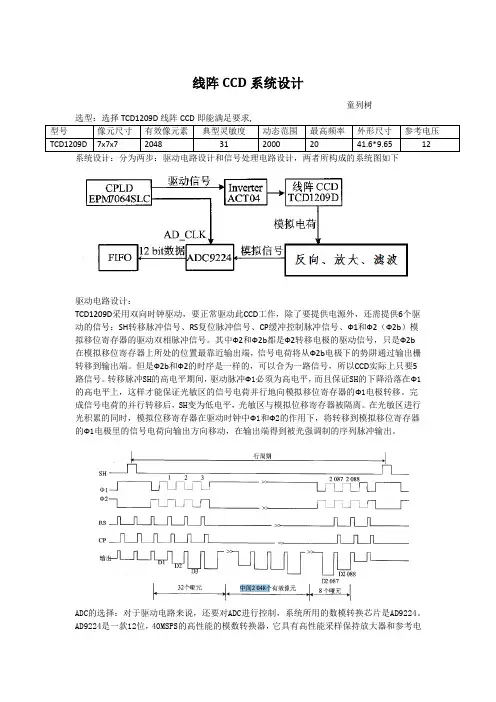

线阵CCD系统设计童列树驱动电路设计:TCD1209D采用双向时钟驱动,要正常驱动此CCD工作,除了要提供电源外,还需提供6个驱动的信号:SH转移脉冲信号、RS复位脉冲信号、CP缓冲控制脉冲信号、Ф1和Ф2(Ф2b)模拟移位寄存器的驱动双相脉冲信号。

其中Ф2和Ф2b都是Ф2转移电极的驱动信号,只是Ф2b在模拟移位寄存器上所处的位置最靠近输出端,信号电荷将从Ф2b电极下的势阱通过输出栅转移到输出端。

但是Ф2b和Ф2的时序是一样的,可以合为一路信号,所以CCD实际上只要5路信号。

转移脉冲SH的高电平期间,驱动脉冲Ф1必须为高电平,而且保证SH的下降沿落在Ф1的高电平上,这样才能保证光敏区的信号电荷并行地向模拟移位寄存器的Ф1电极转移。

完成信号电荷的并行转移后,SH变为低电平,光敏区与模拟位移寄存器被隔离。

在光敏区进行光积累的同时,模拟位移寄存器在驱动时钟中Ф1和Ф2的作用下,将转移到模拟移位寄存器的Ф1电极里的信号电荷向输出方向移动,在输出端得到被光强调制的序列脉冲输出。

ADC的选择:对于驱动电路来说,还要对ADC进行控制,系统所用的数模转换芯片是AD9224。

AD9224是一款12位,40MSPS的高性能的模数转换器,它具有高性能采样保持放大器和参考电压参考。

因为AD9224使用的时候受ADC 时钟的控制,图3所示是其工作的采样时序图。

AD9224 概述:AD9224是一款单芯片、12位、40 MSPS 模数转换器(ADC ),采用单电源供电,内置一个片内高性能采样保持放大器和基准电压源。

AD9224采用多级差分流水线架构,内置输出纠错逻辑,在40 MSPS 数据速率时可提供12位精度,并保证在整个工作温度范围内无失码。

AD9224 特性∙ 低功耗:415 mW ∙ +5 V 单电源 ∙ 保证无失码∙ 微分非线性(DNL )误差:±0.33 LSB ∙ 片内采样保持放大器和基准电压源 ∙ 信噪比(SNR ):68.3 dB∙无杂散动态范围(SFDR ):81 dB ∙ 超量程指示∙ 数据输出格式:标准二进制 ∙ 28引脚SSOP 封装 ∙与3 V 逻辑兼容AD9224 参数AD9224 基本参数分辨率(Bits) 12吞吐率 40 MSPS AD9224 其他特性 工作电压(V) 4.75-5.25 输入通道数 1AD9224 封装与引脚SSOP28信号的调理:在带有模拟电路的设计中,信号的调理成为不可缺少部分。

基于嵌入式平台的面阵CCD图像采集系统

声放大和相关双采样输出数字信号, 数字图像信号

通过 F G P A临时存储到 S A 中 , RM 并根据 需要 进行

第9 第 期 2 3 卷

萎

避 篓

度决定。相关双采样 电路的传递函数为:

Ts ( )= T o

3 9

相 关 图像处理 , 把数据 图像 显示在 L D上 。 并 C

S C 复位信号 R T以及用于变换漏极反模糊偏 R, , S 置供应 电压 O B C 3B有多种读出模 式 , D 。T 27 可

选择单通道或双通道输出。选择不同模式 , 其驱

誊 溅 藿

譬I 翊

r。’ 。 . ' -

第9第 期 2 3 卷

I

克

I扦 — 出一 芒 粤l— — j ! —

0. 2 % 。 05

的输 出端 发送 出去 。

V ro 语言实现的。根据时序 的各个时段进行 el ig

有 限 状 态 机 的设计 。各 个状 态 的转 移 如 图 4所

示。

采集图像的最后 1 个阶段就是要把存储 区的 像素经过串行寄存器发送到输出端。读 出期包含

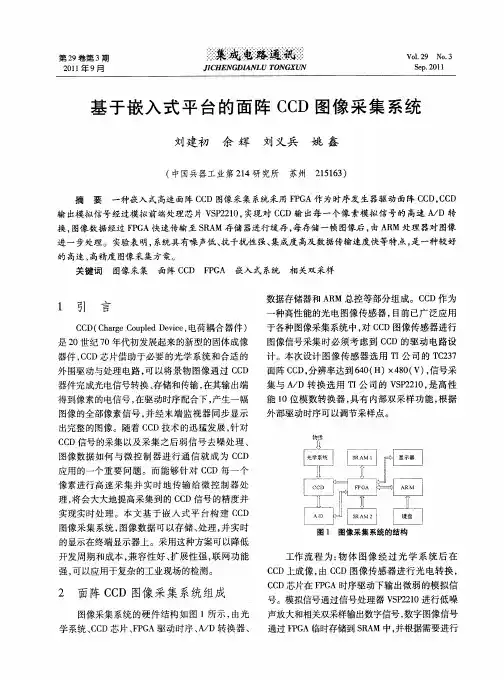

工作 流程 为: 物体 图像经 过光 学 系统后 在

C D上成像 , C D图像传感器进行光 电转换 , C 由 C

C D芯片在 F G C P A时序驱动下输出微弱的模拟信 号。模拟信号通过信号处理器 V P20进行低噪 S2 1

2 面阵 C D 图像采集系统组成 C

图像采集 系统 的硬 件 结构 如 图 1所 示 , 由光 学系统 、C C D芯 片 、P A驱动 时序 、/ FG A D转换 器 、

r: = 一

。

弱的场所 , 应该根据实际情况 , 配合光学系统 , 选

基于FPGA的背照式CCD47-10驱动电路设计

e t d T eh r wae cr u t s c mp s d o e u n e g n r t l c ba o a e e ea e b o k, rvn e eao l k VHDL n e . h ad r ic i wa o o e fs q e c e e ae b o k, i v h g s g n r t c d ii g g n r tr b o . s l c

Ke r s b c — lmia e CD; rvn ic i; P y wo d : a k i u n t d C l d iig c ru t F GA

0 引言

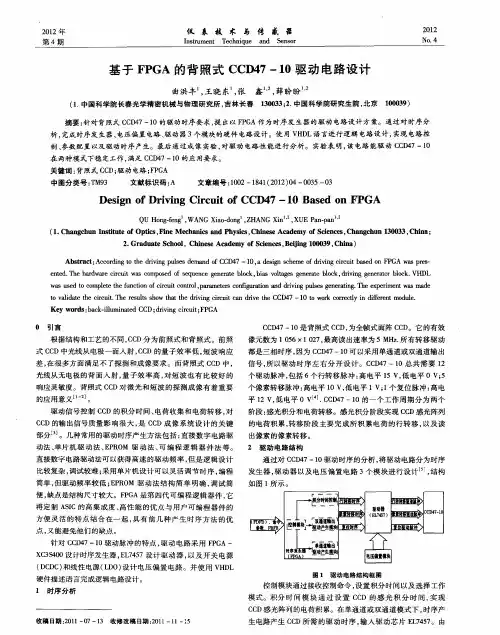

C D 7—1 C4 0是背照式 C D, C 为全帧式面阵 C D C 。它的有效

根据结构和工艺的不同 , C C D分为前 照式 和背照式 。前 照

响应灵敏度 。背照式 C D对微光 和短波 的探 测成像 有着重 要 C 的应用意义 J 。

基于FPGA的高帧频CCD驱动控制系统的设计

l两个左 右 对称 象 限 , , 每个 象 限都 有 独立 的垂 直

和水 平 转 移 的 时 钟 输 入 信 号 A1~A 4和 c 1~c 。 3

图像传感器 , 其它有效像 素为 1M( 2 i l 104p e ×1 x

21 0 1年 1 月 7 日收 到 1

这种结构设计使 C D能以 1 2路两种方式输出 , C 或

需产生极少偏置 电压 即可生成 所需全部偏压 , 这是 目前 十分 安全 的偏 压解决 方案 , 并选用 了 F G P A作 为核心控 制器件 实验

表 明: 此设 计不仅 简化 了电路 , 还具 有性能好 、 功耗低 、 体积小的优 点, 实现 了对高帧频 C D 图像采集 系统 的驱动控制。 C 关键词 帧转移 型 C D C 中 图法 分类 号 T 3 6 5 N 8. ; 驱 动控 制电路 文献标志码 FG PA A 高帧频

2 1 SiTc . nr. 0 2 c eh E gg .

通 信 技 术

基于 F G P A的高帧频 C D驱动控制 系统的设计 C

翟昱 云 梁 志毅

( 北 工 业 大 学 航 天 学 院 , 安 70 7 ) 西 西 10 2

摘

要

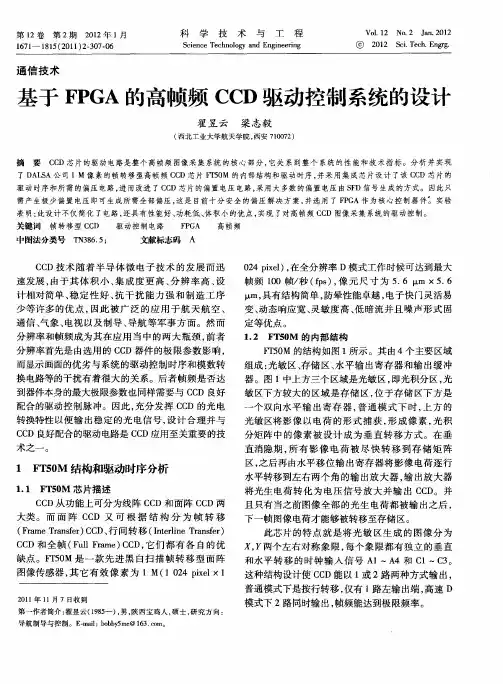

C D芯片 的驱动 电路是整个高 帧频图像 采集系统 的核 心部分 , C 它关系到 整个 系统的性 能和技术指 标。分析 实现

C D 良好 配合 的驱 动 电路是 C D应用至 关重 要 的技 C C

术 之一 。

F 5 M 的结 构如 图 1所示 。其 由4个 主要 区域 T0 组成 : 敏 区 、 光 存储 区、 平 输 出寄存 器 和输 出缓 冲 水

器 。 图 1中上 方三 个 区域是 光敏 区 , 即光积 分 区 , 光

基于CPLD的CCD驱动电路的设计

前 3种 方法基 本偏 重硬 件 的实现 , 调试 困难 , 活性 灵 较差 。而后 一种 方法 虽 编 程 灵 活 , 但存 在 资源 浪 费

较 多 、 率较低 的缺陷 ¨ 。 频

离 行 。该 C D需要 l 驱动 信 号 。包 括 感光 区转 C 2路 移 脉 冲 ( :12,, ) 存储 区转 移脉 冲 M i i , 34 、 ( ( =1 i , =1234 、 储 区到 水 平读 出移位 寄存 器 转移 脉 , ,,)存 冲 M、 水平 读 出移 位 寄 存 器 转 移 脉 冲 2 、 出放 大器 复位脉 冲 彻 。 )读 由该 款 C D的结 构可 知 , C C C D的一个 工作 周期 分 为 两个 阶段 : 光 阶段 和 高 速 转移 阶段 。感 光 阶 感

只须将 C L 内部 逻 辑 重 新 编 程 即可 。2因此 非 常 PD l 适合 C D驱 动 电路 的 设 计 、 作 、 试 和进 一 步 开 C 制 调 发、 升级 。现 给 出一 个 基 于 C L P D技 术 的 面阵 C D C 驱动 电路 的完 整 的硬件设 计 。

S iT c n lg n gn e i g ce e h oo y a d En ie rn

基于 C L P D的 C D驱 动 电路 的 设 计 C

陈 智 邱 跃 洪 张 伯 珩 ’

( 中国科学院西安光学精密机械研究 所 西安 7 0 1 ; , 1 19 中国科学院研究生院 北京 10 3 , 0 09)

智( 9 8 ) 女 , 17 一 , 陕西西安 人, 汉族 , 中国科 学

院西安光 学精密机械 所在读博士研究生 , 研究方 向: 光电信号处理

及 C D相机设计 。E—ma : n yz i.ia Cr。 C i s dc@rp s .O la n n

面阵CCD应用技术实验指导

①学习面阵CCD的基本工作原理(参考《图像传感器应用技术》第6、7章);

②学习隔列转移型面阵CCD的基本工作原理;

③仔细阅读附录中所叙述的“YHACCD-Ⅲ型彩色面阵CCD多功能实验仪使用手册”,并对照实验仪实物进行学习,尤其注意各个开关、测量插孔、连接线的功能,找到内置面阵CCD摄像机与外置面阵CCD摄像机,及其转换开关。

⑤你能否从所测出的信号波形图中找到奇数场与偶数场来?(参考《图像传感器应用技术》第6章关于奇、偶场的特点进行查找)

3) 视频输出信号的测量

①打开内置面阵CCD摄像头的镜头盖;

②用CH1探头测量VIDEO全电视视频输出信号,CH1的幅度选为200mV,扫描时间间隔分别用5ms、1ms、10μs、1μs和25ns档;

②关闭实验仪的电源;

③关闭示波器的电源;

④整理好所有的连接线及部件。

五、实验总结

①写出实验总结报告;

②用自己的语言结合所观测的驱动脉冲波形图说明隔列转移面阵CCD的基本工作原理.讨论面阵CCD的各路驱动脉冲与PAL电视制式的关系.

一、实验目的

①掌握对面阵CCD输出的复合视频信号进行A/D数据采集的原理和方法;

面阵CCD应用技术实验指导

王庆有

天津市耀辉光电技术有限公司

实验规则及注意事项

为了确保CCD应用技术实验的顺利进行,保障人身安全,避免损坏设备,达到实验目的,要求实验人员必须严格遵守下述实验规则及注意事项,在教师的指导下有秩序、按步骤进行。

1、在实验之前,实验人员必须阅读本实验指导书中所要求的实验准备内容,并阅读必要的参考资料。明确实验目的,了解实验内容的详细步骤,达到要求后方能进行实验.

10、实验报告不但要写实验指导每节规定的内容还要写通过实验自己的心得体会和所取得的进步。

光电-线阵CCD驱动电路的FPGA时序设计

线阵CCD驱动电路的FPGA时序设计实验目标设计一线阵CCD驱动时钟,用一输入的clk,驱动CCD、AD、FIFO组成的整个CCD系统,并要求有一个复位端reset。

本实验主要是基于FPGA设计线阵CCD器件复杂驱动电路和整个CCD的电子系统控制逻辑时序的方法,并给出时序仿真波形,通过对线阵CCD驱动电路的时序设计,了解一个系统设计的基本方法。

总体方案元器件选择1、CCD:sonyILX5112、AD:Analog Devices --- AD92243、FIFO:Integrated Device Technology --- IDT7204方案:FPGA产生CCD线阵、AD、FIFO所需要的驱动时钟,从而实现ccd线阵信号的采集到信号调理,再经由AD进行模数转换后经FIFO 实现信号输出到读接口的过程。

我们需要用一个输入的clk,产生CCD、AD、FIFO所需要的clk,用以驱动它们。

CCD 需要两个时钟:rog和clk,AD和FIFO分别需要一个clk。

实验程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ccd isport(clk,reset:in std_logic;rog,ccd1,ad1,fifo1:out std_logic);end ccd;architecture ccd_1 of ccd issignal count:integer range 0 to 2130;signal rog2:std_logic;signal ccd2:std_logic;signal ad2:std_logic; signal fifo2:std_logic; beginrog<=rog2;ccd1<=ccd2 or clk; ad1<=ad2 or clk; fifo1<=fifo2 or clk; process(reset,clk) beginif reset='0' thenrog2<='1';ccd2<='1';ad2<='1';count<=0;elsif clk'event and clk='1' then count<=count+1;case count iswhen 0 to 6=>rog2<='1';ccd2<='1';ad2<='1';fifo2<='1';when 7 to 16=>rog2<='0';ccd2<='1';fifo2<='1'; when 17 to 22=> rog2<='1';ccd2<='1';ad2<='1';fifo2<='1'; when 23 to 55=> rog2<='1';ccd2<='0';ad2<='1';fifo2<='1'; when 56 to 58=>ccd2<='0';ad2<='0';fifo2<='1';when 59 to 2106=> rog2<='1';ccd2<='0';ad2<='0';fifo2<='0';when 2107 to 2109=> rog2<='1';ccd2<='0';ad2<='0';when 2110 to 2130=> rog2<='1';ccd2<='0';ad2<='1';fifo2<='1';end case;if count>=2130 then count<=0;end if;end if;end process;end ccd_1;仿真结果:全图:实验报告;通过本次实验加深了对CCD的了解,掌握了VHDL的使用方法,加深了解时序电路的设计法。

基于FPGA的面阵CCD成像系统设计

基于FPGA的面阵CCD成像系统设计作者:唐艳秋张星祥李新娥任建岳来源:《现代电子技术》2013年第02期摘要:采用SONY 行间转移型面阵CCD ICX415AL 作为图像传感器,设计了一款新型CCD成像系统。

以Altera公司的FPGA芯片EP1C12F256作为时序发生器产生CCD驱动信号。

采用相关双采样技术滤除了视频信号中的相关噪声,提高信噪比。

在Quartus Ⅱ 9.1开发环境下采用VHDL编程,并利用Modelsim SE 6.5仿真软件进行仿真测试。

实验结果表明,所设计的时序满足ICX415AL的时序要求,在29.5 MHz的时钟驱动下,每秒输出50帧图片,能满足高速跟踪要求。

关键词:行间转移型面阵CCD;驱动时序;相关双采样; FPGA中图分类号:TN386.5⁃34 文献标识码:A 文章编号:1004⁃373X(2013)02⁃0123⁃030 引言CCD(Charge Coupled Device)是20世纪70年代初发展起来的新型半导体集成光电器件,它可以把通过光学镜头投影到其上的景物可见光信号转换成比例的电荷包,并在适当的时钟脉冲的驱动下进行定向转移,从而输出成为电压视频图像。

CCD具有集成度高、功耗小、体积小、工作电压低、灵敏度高等优点[1⁃2],目前已广泛应用与空间遥感、对地观测等领域。

按结构分类,CCD可分为线阵CCD和面阵CCD,而面阵CCD按排列方式又可分为全帧转移(Full Frame)CCD、帧转移(Frame Transfer)CCD以及行间转移(Interline Transfer)CCD。

三种类型的CCD各有优缺点,其中行间转移CCD不需要机械快门,速度最快,最适合用于观测快速运动的物体。

本文设计了一种行间转移型面阵CCD的高速驱动电路[3⁃4]。

1 行间转移型面阵CCD的结构和工作模式本设计采用的是SONY公司的ICX415AL型号 CCD芯片,ICX415AL是行间转移型面阵CCD,对角线为8 mm,尺寸为8.3 μm×8.3 μm,总像元素为823(H)×592(V),有效像元为782(H)×582(V)。

基于高速SOC单片机的面阵CCD驱动电路设计

青 岛港湾职业技术学院 李心平 井延波 郭梅忠

电荷耦合 器件( 是2 世纪7 频率 ,对不 同的CCD器件 只需要修 改 门提供 的配套 电平转 换芯片SN2 8 6 CCD) 0 0 8 4 年 代初发展 起来 的新型 半导体 集成 光 程序 即可 。但 由于 时序 的产生 完全 依 与 T M S3 7 4 3, 实 现 了 C8 5 F3 l 0 1 l 电器件 。近年 来 ,CCD器件 在 图像 赖 程序 指令 的延时 来实现 ,如 果程序 传感和 非接 触测量 领域 的发展 迅速 。 ( 3 3. V)与 C CD( 电 平 2 高 V,低

S RGi RG2 与S 之间严格的时序对应关

( PCAO PL =PC L C n A0 )时 ,CEXn

图2 中,ABG 为防开花脉冲 ,I 系 ,因此 ,利 用C8 5 F3 l 可编程 的电平发生改变 ,同时捕捉/ AG 0 I 1的 比较 模块 为 行 移脉 冲 ,TR G为行 转 移 门控 脉 计数 器阵 列 ( PCA)模块 ,并通过相 的高字节P AO P 与PC c L 相 C C Hn A0 P n 冲 ,S RG1 RG2 串行移位 脉冲 , 、S 为 应的 中断 服务程 序 ,实现 各时序 之间 加的结果再 回送NPCA CPL 。方波 0 n

W 素单元面积为9. ×9 /m m;动态范 围 t 容的 微控制器 内核 ,与 M 一 1 CS 5 指令 P M ,每 个 模 块 的 工 作 方 式 都 可 以被 很 大 、灵敏度高 、噪 声低 ,并 内置 自 集完 全兼 容 ,具 有丰 富的 片上硬 件资 独 立 配 置 。

1 TC2 5 2

TC 2 是TI 2 5 公司推出的一款 全帧 读 出型 面阵 图像 传感 器 ,是 专门为 适

基于FPGA的CCD驱动设计

基于FPGA的CCD驱动设计作者:武琪敬,李自田,胡炳梁,皮海峰来源:《现代电子技术》2010年第12期摘要:以Atmel公司的面阵CCD-TH7888A图像传感器为例,在研究了CCD结构和驱动时序图的基础上提出基于FPGA的驱动脉冲设计方法和硬件电路实现。

使用VHDL语言对驱动时序发生器进行了硬件描述,并采用Quartus 5.0对设计的驱动时序发生器进行仿真。

试验结果表明,涉及的驱动电路可以满足面阵CCD-TH7888A的各项驱动要求。

关键词:CCD; 信号处理; VHDL; 图像传感器中图分类号文献标识码:A文章编号:1004-373X(2010)12-0157-03Design of CCD Driving Circuit Based on FPGA TechnologyWU Qi----(1. Xi’an Institute of Optics and Precision Mechanics, Chinese Academy of Sciences, Xi’an 710119, China;2. Graduate Student College, Chinese Academy of Sciences, Beijing 100039, China)Abstract:The design and implementation of CCD image sensor digital system is introduced. Taking CCD image sensor TH7888A produced by ATMEL as an example, the FPGA-based hardware driving design is proposed by studying the structure and driver schedule of CCD device. The hardware module and its circuit diagram of the driver are studied, the hardware description is given for the driving schedule generator by VHDL, and then the pulse signal needed by CCD is generated, the designed generator is simulated with Quartus 9.0. The experimental results show that the designed generator can meet the demand of the CCD-TH7888A.Keywords: CCD; signal processing; VHDL; image sensor电荷耦合器件(CCD)作为新兴的固体成像器件即图像传感器,具有体积小,重量轻,分辨力高,噪声低,自扫描,工作速度快,灵敏度高,可靠性好等优点,受到人们的高度重视,广泛应用于图像传感、景物识别、非接触无损检测、文件扫描等领域[1] 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Ab t a t Ac o d n sr c : c r i g t CCD6 a k I u i ae M O r d c d b 2 o a y t e d i i g c p b l y o o 7 B c l m n t dNI l p o u e y e v c mp n , h r n a a i t f v i C CD sa ay e . a o t g so wa n lz d Bi sv l e fCCD r e e m i e t M 1 T a d LM 3 T CCD rv r we e a we e d t r n d wi L 1 n h 7 7 ; 1 d ies r d sg e t 0 2 ; h r g a e i n d wi DS 0 6 t ep o r mm a l o i a e ie o e EP K3 RI 4 — f mp n tr s h b e l g c l v c f h F1 d t 0 0 2 04 o Co a y Al a wa e u e o ed sg f s d f rt e i n o h CCD rv n meo d r. x e i e t s o t a ed sg f d i i g t r e E p r n s h w t h e i n o i m h t CCD rv n i u t a d iigcr ic n c me t e n so e ma d f d CCD. Ke W o d : d i i g cr u t b a o t g : CCD r e ; F GA y r s r n ic i: i sv l e v a di r v P

辑器 件 E F 0 0 I4—来设 计C D的驱 动 时序 。实验 结果 表 明 ,设计 的C D驱 动 电路 可 以满足 C D P 1K3R2 04 C C C

的驱动 电 路;偏 置 电压 ;C D驱 动器 ;现 场 可编 程 门阵列 ( P A) C FG 中 图分类 号 :T l N2 5 文 献标 识码 :A 文章 编号 :l0—8 1 060 —590 0 189 ( 0 )90 1—4 2

A sg f r yCCD fFr m eTr n f rDrv ngCic tBa e n FPGA e hni De i no a Ar o a a se ii r ui s d o Tc que C NGP n— i UMig n HE egf ,G n-a ,WANGMocag e j i —hn

直 接 数 字 电路 驱 动 方 法 的特 点 是 可 以获得 高速 的驱 动 频率 ,缺 点 是逻辑 设计 比较 复 杂 ,调 试较 为 难 ; 单 片机 驱动 方法 的特 点 是时序 调 节灵 活方 便 、编 程简

单 ,但通 常 具有驱 动 频率较 低 的缺 点 ,不 能满 足 高速 C D 驱动 时序 的要 求 ;E RO 驱动 方法 结构 简 单 明 C P M 确 ,调试 简便 ,缺 点是 结构 尺寸 较 大 。F GA 是 第 四 P 代可 编程 逻辑 器件 ,它 将 定制 ASC 的 高集 成度 、 高 I

程 鹏飞 ,顾 明剑 ,王模 昌

( 中科 院上海技术 物理研 究所, 卜 2 0 8 ) 海 0 0 3

摘要 :针对ev 司的C D 7 B c l mi t I 型C D 2公 C 6 ak Iu n e N MO l ad C ,对其驱动能力进行详细的分 析;选用 L 17 和L 1T 计C D 需的偏 置 电压 ;DS 06 完成设 计C D驱 动器 ;Alr公 司 的可编 程逻 M 1T M37 设 C 所 02来 C ta e

性 能 的 优 点 与用 户 可编 程 器 件 的方 便 灵 活 的特 点结 合在 一起 ,从 而 避免 了用 定制 ASC 的高 成本 、高 风 I 险、长设计 周 期和 可编 程器 件密 度低 的缺 点 。本 系统

辑 与相 位关 系, 别 是各信 号 的边沿 时序 关系 对其 工 特

作 状态 至 关重要 。而 驱动 电路 就 是为C D提 供其所 需 C 的时序 逻辑 和相 关 的 电压 信号 , 的性 能直接 影 响 它

C D输 出信 号的质 量 ,所 以在 系统研 制 过程 中, C 驱动

电路 的研制 就显 得 十分 的重 。

C D 的驱 动 电路主 要 由偏置 电压 产生 电路 、 C 驱动

维普资讯

第 2 卷 第 9期 8

20 0 6年 9

红 外 技 术

I fa e e h o o y n r r dT c n l g

Vl 8 NO. 0 2 l 9

Sp 2 0 e. 06

基 于 F GA的帧 转 移 面 阵CC P D驱 动 电路 设 计

引 言

近 几 十年来 ,随 着航 天技 术 的发展 ,C D相机 在 C 高精度 测 量 、空 间遥感 和对 地观 测 等领域 ,得 到 了广 泛 的应用 。 C D 件 正常 工作 时需 要驱 动脉 冲信 号 而 C 器 多达 十 几路 , 且各 驱动 脉冲 信 号之 间要保 持严 格 的逻