基于JTAG技术的Flash加载

JTAG模式下的MPC5554外部FLASH编程的设计与实现

JTAG模式下的MPC5554外部FLASH编程的设计与实现0 引言随着信息技术的发展,嵌入式系统越来越广泛地应用于手机通信、汽车、航空航天、工业控制等领域。

在这些电子产品中,大多以嵌人式微处理器为核心,配套相关的外围辅助设备,对控制对象进行软硬件的功能剪裁性设计,并将控制程序固化在非易失性存储器中。

FLASH 作为一种存储速度快,容量大,可多次擦写并且价格便宜的存储器得到了广泛的应用。

由于有些微处理器内部不包含FLASH 或FLASH 存储空间太小、擦写次数有限,为了提供足够的程序存储空间,需要对其进行外部FLASH 扩展。

JTAG 是目前广泛使用的一种系统在线编程的模式,大大方便了嵌入式系统下载程序至FLASH。

该设计使用的微处理器为MPC5554,通过JTAG 接口对外扩FLASH 进行编程。

1 MPC5554 简介MPC5554 是Freescale 公司推出的采用PowerPC 内核的一款32 位微控制器.属于MPC5500 系列第一代产品,可用于航空航天、汽车、工业控制等嵌入式系统中。

如图1 所示,MPC5554 内部带有浮点运算单元,集成DSP 运算指令,拥有较高的计算能力,可以满足多任务处理和实时控制的要求。

MPC5554 包含64 KB 内部SRAM,32 KB Cache,2 MB 内部FLASH,64 路eDMA,24 路eMIOS,64 路eTPU 通道,2 路eSCI,4 路DSPI,3 路FlexCAN,40 路12 b A/D(可扩展为64 路),中断控制器,以及JTAG,Nexus 调试接口等功能模块。

MPC5554 为416 脚PBGA 封装,可在-40~+150℃的环境下工作,系统时钟可达132 MHz,中断延迟小于70 ns(@132 MHz),内部逻辑供电1.5 V,输入/输出供电3.3 V,5 V,外部总线接口支持1.62~3.6 V 操作。

MPC5554 提供2 MB 可编程、非优化内部FLAsH,可用于指令存取和数据存储。

JTAG口及其对Flash的在线编程

JTAG 口及其对 Flash 的在线编程 摘要通过实现对在线编程。

首先,介绍的定义、结构及引脚的定义,并阐述状态机的工作原理。

然后,介绍口的边界扫描寄存器,给出实现在线写的电路,和如何通 过实现的编程及程序流程图。

关键词在线编程随着嵌入式技术的发展,在一些高端的掌上设备中, 都使用了芯片,如的、联想的天祺系列等产品。

但对于研发人员来说,在开发阶段需要大量的程序调试,就意味着要 对进行擦除和改写的工作, 因此, 如何对进行在线编程是问题的关键所在。

本文介绍一种通过对进行的在线编程方法。

1 简介是 1985 年制定的检测和芯片的一个标准,1990 年被修改后成 为的一个标准,即 11491-1990。

通过这个标准,可对具有口芯片的硬件电路进行边界扫描和故障检测。

图 1 控制器的状态机框图具有口的芯片都有如下引脚定义——测试时 钟输入;——测试数据输入,数据通过输入口;——测试数据输出,数据 通过从口输出; ——测试模式选择, 用来设置口处于某种特定的测试模式。

可选引脚——测试复位,输入引脚,低电平有效。

含有口的芯片种类较多,如、、等。

内部有一个状态机,称为控制器。

控制器的状态机通过和进行状态的改变,实现数据和指令的输入。

图 1 为控制器的状态机框图。

范文先生网收集整理 2 芯片的边界扫描寄存器标准定义了一个串行的 移位寄存器。

寄存器的每一个单元分配给芯片的相应引脚,每一个独立的单元称为 -边界扫描单元。

这个串联的在内部构成回路,所有的-边界扫描寄存器通过测试激活, 平时这些引脚保持正常的功能。

图 2 为具有口的内部单元与引脚的关系。

3 在线写的硬件电路设计和与的连接方式以含接口的 1110 为例,为 281283216 容量。

1110 的的、、、分别接并口的 2、3、4、11 线上,通过程序将对口的 控制指令和目标代码从的并口写入的中。

在设计时,必须将 1110 的数据线和地址线及控制线与的地线线、数 据线和控制线相连。

理工毕业论文通过JTAG口对DSP外部Flash存储器的在线编程

通过JTAG口对DSP外部Flash存储器的在线编程引言在采用TI数字信号处理器(DSP)的嵌放式硬件系统开发完成,软件也有CCS2.0集成开发环境下仿真测试通过后,怎样将编译、链接后生成的可执行文件(.Out),经过转换后的十六进制文件(.Hex)写入硬件系统的Flash存储器中,让系统脱机运行,这是许多DSP开发人员及初学者遇到并需要解决的问题。

从JTAG接口对DSP外部Flash的编程方法不只一种。

本文以TMS320C6711-150 DSK板为例,介绍“在线仿真状态下”对Flash 的编程。

1 Flash存储器的擦除Flash编程之前,应对Flash进行擦除,使其每个数据位都恢复为1状态,即全FF状态。

对Flash 的擦除操作需要6个总线周期,总线时序如图1。

从图1可知,各总线周期的操作为:第一总线周期——向2AAAH地址的存储单元写入数据55H;第二总线周期——向2AAAH地址的存储单元写入数据55H;第三总线周期——向5555H地址的存储单元写入数据80H;第四总线周期——向5555H地址的存储单元写入数据AAH;第五总线周期——向2AAAH地址的存储单元写入数据55H;第六总线周期——向5555H地址的存储单元写入数据10H。

完成上述操作后,Flash存储器被完全擦除,内部数据恢复为初始状态,全为FFH。

在TMS320C6711中,用C语言完成上述操作为:void erase_flash(){*(unsigned volatilechar*)FLASH_ADR1=0x00aa;*(unsigned volatilechar*)FLASH_ADR2=0x0055;*(unsigned volatilechar*)FLASH_ADR1=0x0080;*(unsigned volatilechar*)FLASH_ADR1=0x00aa;*(unsigned volatilechar*)FLASH_ADR2=0x0055;*(unsigned volatilechar*)FLASH_ADR1=0x0010;}在TMS320C6711系统中,Flash所在地址段为CE1空间,其开始地址为0x90000000。

用JTAG烧写Flash的方法

文章编号:1006-1576(2005)01-0086-02用JTAG烧写Flash的方法邓启辉(武汉理工大学智能信息系统研究所,湖北武汉 430070)摘要:利用JTAG烧写Flash的方法是通过并口把PC与主控芯片的JTAG连接,PC向Flash的特定地址发出控制命令,把烧写的目的数据、地址和控制信号经JTAG TDI串行输入到对应的边界扫描单元。

调用putp函数转换TAP 状态,更新引脚状态后从系统总线输出到JTAG,即完成烧写操作。

关键词:烧写Flash;JTAG;并口中图分类号:TP311.11 文献标识码:AMethod for Writing Flash By JTAGDENG Qi-hui(Institute of Intelligence Information Systems, Wuhan University of Technology, Wuhan 430070, China) Abstract: The way of burning flash on board by JTAG was that PC is connected JTAG of the host controller on board with parallel port, and then PC sent control command to the address of flash, and burned data and address and control signal was inputted to corresponding boundary scan cell by JATG TDI. The state of TAP was switched with function putp, and after flash was updated by JTAG to output into JTAG from the bus of system. At the same time, the JTAG of host controller receive the data to complete the operation of burning flash.Keywords: Burning flash; JTAG; Parallel port1 引言Flash存储器由于其存储容量大、密度高,在嵌入式系统中得到广泛的应用。

基于JTAG技术的Flash加载

基于JTAG技术的Flash加载

郑先刚;张学斌

【期刊名称】《现代电子技术》

【年(卷),期】2004(27)11

【摘要】主要介绍了目前世界上主要流行的一种Flash加载技术利用JTAG技术加载Flash.文章分为3个部分.首先描述了JTAG加载Flash的原理.然后对JTAG 加载Flash的优点做了说明.最后对实验性能做了详细分析.

【总页数】3页(P5-7)

【作者】郑先刚;张学斌

【作者单位】同济大学,中德学院,上海,210092;同济大学,中德学院,上海,210092【正文语种】中文

【中图分类】TP312

【相关文献】

1.Flash在线数据加载的JTAG通用方法研究 [J], 张琳;周拥军;武飞

2.基于JTAG的DSP外部FLASH在线编程与引导技术 [J], 刘德生;李杰

3.利用JTAG口的FLASH在板加载技术 [J], 谢志迅

4.基于JTAG的TMS320VC33外部FLASH在系统编程与并行自举引导技术 [J], 黄国强;秦传波;江太辉;王小雄

5.基于JTAG技术的FLASH加载——一种新的在板编程技术 [J], 郑先刚;张学斌因版权原因,仅展示原文概要,查看原文内容请购买。

jtag烧写flash原理

jtag烧写flash原理JTAG烧写Flash原理一、JTAG简介JTAG(Joint Test Action Group)是一种标准的芯片测试和编程接口,它可以在不需要物理插头的情况下测试和编程芯片。

它是由IEEE (Institute of Electrical and Electronics Engineers)制定的标准,目前已经成为了一个广泛应用于数字电路测试和调试的标准接口。

二、JTAG烧写Flash原理Flash存储器是一种非易失性存储器,它可以在断电后保持数据。

因此,Flash存储器被广泛应用于各种嵌入式系统中。

在设计和开发过程中,需要对Flash存储器进行烧写操作以更新或修改程序代码。

JTAG接口可以用于烧写Flash存储器。

其原理如下:1. JTAG接口连接首先,将目标设备的JTAG接口与烧写设备的JTAG接口相连。

这个连接通常包括四个信号线:TCK、TMS、TDI和TDO。

2. 进入ISP模式通过向目标设备发送特定的命令序列,在目标设备中进入ISP(In-System Programming)模式。

在ISP模式下,目标设备将会响应来自烧写设备的命令,并将Flash存储器暴露给烧写设备。

3. 读取Flash存储器状态烧写设备通过JTAG接口向目标设备发送命令,以读取Flash存储器的状态。

这些状态包括Flash存储器的大小、页大小、块大小以及是否需要擦除等信息。

4. 擦除Flash存储器在烧写新程序代码之前,必须先将Flash存储器擦除。

为了提高效率,通常只需要擦除需要烧写的代码所在的块。

5. 写入新程序代码在完成Flash存储器的擦除后,可以开始写入新程序代码。

烧写设备通过JTAG接口向目标设备发送命令和数据来完成这个过程。

通常,数据是按页或块大小分批次写入的。

6. 验证新程序代码在完成新程序代码的烧写后,需要进行验证以确保数据正确性。

烧写设备通过JTAG接口向目标设备发送命令和数据来读取已经烧写到Flash存储器中的数据,并将其与原始数据进行比较。

使用Flash Loader(JTAG 模式)下载EPCS 器件的方法

使用Flash Loader(JTAG模式)下载EPCS器件的方法一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS 系列串行FLASH。

一般使用AS模式下载EPCS系列器件,下面介绍通过JTAG方式下载EPCS系列器件。

如果这种方式进行正确的AS模式的下载的话,可能是EPCS器件本身已经不能正常工作了,此时建议更换配置芯片。

建议使用Quartus II 5.1及以上版本(5.1以下版本在devices中有很多器件不能找到)。

使用JTAG下载模式下载EPCS器件的步骤如下:1.把需要下载的工程文件生成*.sof文件2.点击File菜单,选择Convert Programming Files….如图一所示。

图一:File 选项3.执行完第二步后出现图二所示的界面。

图二3.第一、鼠标左键点击Programming file type 栏目的下拉箭头,选择JTAG Indirect configuration File(.jic)项;第二、Configuration device栏目的下拉箭头,选择EPCS4(本文以EPCS4为例,客户选择自己所用的配置芯片);第三、点击File name栏目后的….,选择输出文件保存的路径以及输入保存文件名,其后缀为*.jc;第四、在Memory Map File前的空格中打钩;4.用鼠标点击一下SOF Date-----Page 05.用鼠标点击Add File…, 出现以下界面,并在Select Input File中选择用户所要转换的*.sof文件(注意选择用户文件的路径)6.完成第5步操作后将出现下图界面7.用鼠标点击一下 Flash Loader,如图8.用鼠标点击Add Device…..,出现下图界面,并且选择用户自己的FPGA芯片(本文以Cyclone II中的EP2C20F256为例)9.点击OK,出现下面界面10.点击Generate,将出现如下界面,然后点击确定,既完成文件的转换11.用生成的文件在JTAG模式下对EPCS器件进行下载12.下载完成后出面的信息本文件说明由CZL提供,联系方式lail247@ QQ: 418046050本人开发的USB BLASTER下载线100%完全兼容Altera原装下载线,其下载图如下:1、AS模式2、JTAG模式。

jtag烧写flash原理

JTAG烧写Flash原理一、什么是JTAG?JTAG(Joint Test Action Group)是一种用于芯片测试和调试的标准接口。

它定义了一组用于访问目标设备内部结构、获取芯片状态以及进行调试和编程的信号和协议。

JTAG具有广泛的应用,其中之一是在软件开发过程中用于烧写Flash存储器。

二、Flash存储器简介Flash是一种非易失性存储器,它可以电擦除和编程。

Flash存储器通常用于存储程序代码和数据,它在数字设备中起到了至关重要的作用。

在许多嵌入式系统中,Flash存储器被作为主存储器使用,因此在研发过程中烧写程序代码和数据到Flash存储器是非常常见的任务。

三、JTAG烧写Flash的基本原理JTAG烧写Flash的基本原理是通过JTAG接口读取目标设备的内部状态、控制信号以及访问存储器地址,然后将要烧写的数据写入Flash存储器。

下面将详细介绍JTAG烧写Flash的过程。

JTAG接口的连接首先,需要将烧写设备(如JTAG调试器)与目标设备上的JTAG接口连接。

JTAG 接口通常包括TCK(时钟信号)、TMS(状态信号)、TDI(数据输入信号)和TDO (数据输出信号),通过连接这些信号,烧写设备可以与目标设备进行通信。

进入和退出JTAG模式在JTAG烧写Flash之前,需要将目标设备进入JTAG模式。

这可以通过在JTAG接口上发送一系列特定的JTAG命令来实现。

进入JTAG模式后,目标设备的内部状态机会切换到与JTAG相关的状态,以便进行后续的烧写操作。

完成烧写后需要退出JTAG模式,将目标设备恢复到正常的运行模式。

读取目标设备状态在进行烧写操作之前,需要读取目标设备的当前状态。

这可以通过发送特定的JTAG命令,并从目标设备的TDO信号上读取返回的状态信息。

目标设备的状态包括Flash存储器是否就绪、是否处于保护状态等。

根据不同的状态,可以确定是否可以进行烧写操作。

编程Flash存储器一旦目标设备进入了JTAG模式并且处于可编程状态,就可以开始进行烧写操作了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于JTAG 技术的Fla sh 加载郑先刚,张学斌(同济大学中德学院 上海 210092)摘 要:主要介绍了目前世界上主要流行的一种F lash 加载技术利用JTA G 技术加载F lash 。

文章分为3个部分。

首先描述了JTA G 加载F lash 的原理。

然后对JTA G 加载F lash 的优点做了说明。

最后对实验性能做了详细分析。

关键词:边界扫描;边界扫描国际标准;在板编程;在线编程;系统编程中图分类号:T P 312 文献标识码:B 文章编号:1004373X (2004)1100503JTAG Fla sh Programm i ng Usi ng Boundary scanZH EN G X iangang ,ZHAN G Xueb in(Ch inesisch D eutsches Institute ,TongjiU niversity ,Shanghai ,210092,Ch ina )Abstract :T h is article in troduces one of the mo st popu lar F lash p rogramm ing techno logy u sing JTA G techno logy to p rogram F lash ,con sists of th ree componen ts 1F irst it describes the theo ry of p rogramm ing F lash u sing JTA G ,then exp lain s the strongpo in t of th is m ethod 1L ast analyses the perfo rm ance of the experi m en t detailedly 1Keywords :BS (Boundary Scan );JTA G (Jo in t T est A cti on Group )IEEE 114911;OBP (O n Board P rogramm ing );I CP (In C ircu it P rogramm ing );ISP (In System P rogramm ing )收稿日期:200401211 引 言一般而言,电路板上的F lash 芯片本身不带边界扫描(Boundary Scan ,BS )结构,但是F lash 的周围存在BS 器件,从而可以利用周围的BS 器件(一般为CPU )实现F lash 加载。

利用BS 技术(也称为JTA G 技术)进行对F lash 加载是一项比较新的有效编程方式。

F lash 器件的编程方式分为2大类:在板编程(O n Board P rogramm ing ,OBP )和离板(O ff Board )编程。

离板编程是指在F lash 器件被安装到PCB 之前对其进行编程。

这一般是采用编程器来完成的,常见的编程器有ALL07,ALL11等。

在板编程是指在F lash 器件被焊接到PCB 上以后对其进行编程。

常见的方法有利用I CT 进行再线编程(I CP ),利用CPU 进行系统编程(ISP )和利用JTA G 进行的在板编程(OBP )等。

在线编程I CP (InC ircuitP rogramm ing )或I LD P (In -L ine D evice P rogramm ing )是指通过I CP 夹具把I CT 设备的测试通道连接到PCB 上F lash 器件的各个管脚,把PCB 上和F lash 器件相连的其他器件进行电气隔离,直接对F lash 器件进行编程。

可以在I CT 测试的同时完成F lash 器件的编程,但是在PCB 设计时必须保证F lash 器件的每一个管脚设计I CT 测试点,而且需要占用单板的I CT 测试时间。

I CT 加载F lash 适宜在单板量产时采用,速度比较快,生产效率比较高。

但是采用I CT 加载F lash 要占用昂贵的I CT 设备资源,而且在单板开发阶段单板没有I CT ,测试无法采用,也不适宜于现场维护与升级。

系统编程ISP (In System P rogramm ing )是指通过系统上的CPU 来执行F lash 器件的擦除和编程来实现F lash 器件的编程。

这种方式要求CPU 能够正常工作,并且需要提供额外的网口、串口等硬件接口进行软件下载。

利用BS 技术的在板编程(OBP )既不需要占用额外的设备,也不需要增加额外的硬件,他只需要将相关的BS 器件连接成一条扫描链,并将边界扫描接口引出来即可。

2 JTAG 加载Fla sh 的原理边界扫描加载系统通过一系列的扫描串行移位来完成F lash 的在板编程。

首先是通过指令扫描使得BS 器件处于Extest 状态,这样BS 器件可以通过边界扫描链向外输出数据,然后就是数据移位,将数据刷新输出;再进行数据移位,再刷新数据;……,就这样反复进行数据扫描和数据输出,向F lash 输入各种指令和数据,以及从F lash 读回数据,一直到完成F lash 编程为止。

由于都是一些串行移位的过程,所以利用JTA G 加载F lash 的速度就成为一个重要性能指标。

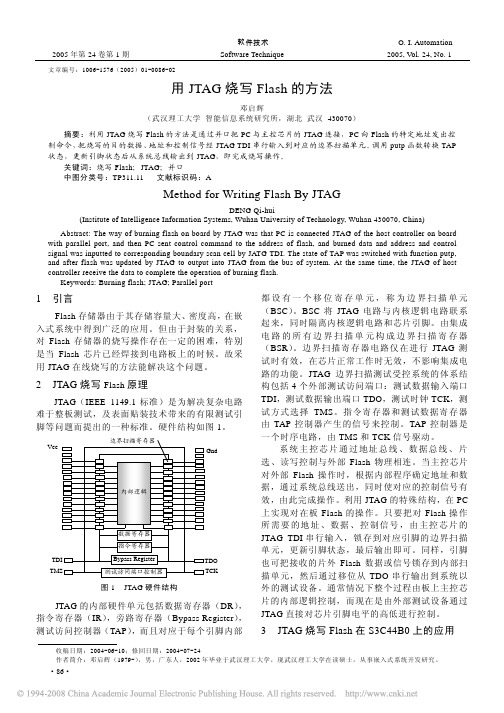

如图1所示。

一个F lash 芯片可以通过一个BS 器件完成控制。

当在边界扫描链中装载了适当的数据后,在Ex 2test 指令下将数据传送给F lash 。

假设图中的边界扫描器件有224个边界扫描单元BSC (以Intel 486DX 2为例),系统必须使用224个CL K 时钟完成在每一个BSC 中装载预定5《现代电子技术》2004年第11期总第178期工控新技术的数据,称为一次数据移位(DR Sh ift )。

图1 JTA G 器件加载F lash 的连接图每次数据移位完毕,所有数据均已经准备好,在进入U pdate DR 状态时BSC 将数据打入F lash ,此时指令寄存器中的指令要求是Extest 。

所以在执行数据移位之前,还要进行一次指令移位,将Extest 指令装入指令寄存器。

但是完成指令装载以后,只要不更改指令,就不再需要进行指令移位了,此时只需要进行数据移位,所以数据移位是编程的主要操作,扫描链的长度是影响F lash 编程速度的关键因素之一。

3 Fla sh 加载的性能分析(结论)以下一些因素影响JTA G 进行F lash 编程的速度。

(1)边界扫描链的长度扫描链越长意味着编程时间越长,当扫描链由多个BS 器件组成,系统会自动将不相关的BS 器件旁路(BYPA SS )。

(2)数据扫描的次数完成每个地址单元(Byte W o rd 等)的编程操作需要的扫描次数越多,编程速度就越低。

这与F lash 的操作时序有关,执行一个F lash 的操作命令所需要的总线周期越多,编程速度就越慢。

(3)数据宽度对相同字节的内容进行编程,8b 的数据宽度要比16b 的数据宽度多需要一倍的编程时间。

也就是说一次编程的数据宽度越大,编程速度越快。

(4)TCK 频率TCK 的频率越低,编程速度越慢;TCK 频率越高,编程速度越快。

但是每一个BS 器件都有一个TCK 频率的上限,超过此频率,信号就不稳定了。

下面举例计算编程一个4-M bit Intel F lash M emo ry (以芯片PA 28F 400BV 为例)所需要的理论时间。

①一次数据移位时间:TCK =80ns Cycle T i m e (1215M H z TCK )224BSC bits ・80ns =17192Λs②编程一个Byte W o rd 的时间:4signl transiti on ・17192Λs =71168Λs③编程4M bit 的F lash 所需要的时间:262144wo rds (flash m emp ry density )・71168Λs =18179s④编程8k wo rd boo t block 所需要的时间:8192wp rds (boo t block size )・71168Λs =0159Λs ⑤由上可知,JTA G 对F lash 编程的时间计算公式为:F lash 编程总时间=(TCK 周期)・(扫描链长度)・(编程一个位或字所需要的扫描次数)・(F lash 编程大小)⑥通过同样的分析可知,JTA G 读F lash 时间计算公式为:读F lash 总时间=(TCK 周期)・(扫描链长度)・(读一个位或字所需要的扫描次数)・(F lash 程序大小)一般而言,F lash 读一个位或字所需要的扫描次数为2,所以通常读F lash 的时间只是编程时间的一半,甚至更少。

数据读回即可进行校验,这个时间是非常短的,可以忽略不计。

4 采用JTAG 加载Fla sh 的好处411 可以削减物料成本以M PC 860 850 8260为CPU 的最小系统为例的框图如图2所示。

图2 M PC 860850 8260最小系统框图其中8b 的Boo trom 用来烧制搬移程序和B I O S 程序,16b 的F lash rom 用来烧制业务软件。

Boo trom 一般采用PL CC 封装的器件,其中的软件预先在软件车间烧制好,单板生产时再插在制成板相应的I C 插座上。

业务软件由于在线升级的要求,所以F lash rom 一般采用ISP 的方式烧制,其软件的获取有3种途径:(1)通过背板总线由主板获得,这需要业务软件已经运行才可以。

6郑先刚等:基于JTA G 技术的F lash 加载(2)通过本板的调试网口,在B I O S软件的配合下通过T FT P或FT P协议下载获得。

(3)通过本板的控制台串口,在B I O S软件的配合下通过Xmodem协议下载获得。

其中第1种方式是产品升级时的主要加载方式,第2和第3种方式主要用于业务软件的初次加载(生产加载)。

可以看出,除主控板外,其他各业务板的本地网口和串口除了在调试阶段有意义外,在产品成熟以后惟一的作用就是用于业务软件的初次加载。

目前按相关资料显示,采用L XT905作为接口I C的10M以太网接口电路的物料成本约70元,加上生产成本实际成本还会高一些,在完成调试以后,去掉网口及其接口芯片就可以降低物料成本。

而且使用JA T G加载方式,不需要CPU运行就可以对电路板进行加载,因此还可以省去单板上PL CC的B I O S芯片和插座,又一次降低了生产成本。

就以上两项进行计算,每一块单板就可节省100多元,而且比这个更加重要的是, JTA G加载方式减少了加工工序,减小了印制板面积,极大地提高了单板的可靠性。