第3章 DSP Builder设计

第三章-DSP-Builder设计入门

The Programmable Solutions Company®

Devices

– Stratix® II™ – Cyclone™ II – Stratix GX – Stratix – Cyclone

Devices (continued)

– MAX® II – Mercury™ Devices – ACEX® Devices – FLEX® Devices – MAX Devices

……………………

…A…lte…ra…D…SP…B…ui…lder Fixed-Point Blockset DSP Blockset Communications Blockset SimPowerSystems Blockset Others

Matlab / Simulink Model Created with Altera DSP Builder Libraries

Design Flow with DSP Builder

(八步法)

What Is DSP Builder?

Links MATLAB/Simulink Design Environment to Quartus II Development Tool for Altera FPGAs Automatic HDL Code Generation from Simulink Model Generated by DSP Builder Libraries Generates Bit & Cycle Accurate Models for DSP Functions Automatic Generation of HDL Testbench Integrated Intellectual Property (IP) Library Support Enables Rapid Prototyping with Altera DSP Development Board Facilitates Integration of Complex DSP Functions

dsp基本系统设计

04

同时,随着人工智能、物联网等技术的快速发展, DSP技术将与这些技术进行更紧密的结合,以实现更 高效、智能的数据处理和分析。

THANKS FOR WATCHING

感谢您的观看

算法实现与优化

总结词

DSP系统的核心是实现各种数字信号处理算法,因此算法实现与优化是DSP系统软件设计的关键环节 。

详细描述

在算法实现与优化方面,需要考虑算法的复杂度、运算量、存储需求等因素,并采用适当的优化技术 ,如循环展开、流水线设计、并行计算等,以提高DSP系统的性能。

程序结构与流程控制

总结词

存储器与I/O接口设计

存储器设计

根据DSP系统的需求,设 计适当的存储器容量和类 型,如SRAM、DRAM、 Flash等。

I/O接口设计

根据应用需求,设计适当 的I/O接口,如GPIO、SPI、 I2C、UART等。

考虑因素

在存储器和I/O接口设计时, 需要考虑容量、速度、功 耗以及与处理器的兼容性 等因素。

信号的频域分析

频域分析是将信号从 时域转换到频域进行 分析的方法。

频谱分析可以揭示信 号的频率成分、频率 范围和频率变化等特 性。

傅里叶变换是频域分 析的基础,可以将信 号表示为不同频率分 量的叠加。

04 DSP系统硬件设计

硬件平台选择

通用硬件平台

选择通用的DSP硬件平台,如TI 的TMS320系列或ADI的Blackfin 系列,这些平台具有成熟的开发 工具和丰富的应用案例。

05 DSP系统软件设计

软件开发环境选择

总结词

选择合适的软件开发环境是DSP系统设计的重要步骤,它影响着软件开发的效 率、可维护性和可扩展性。

DSPBuilder用户指南(中文)

6.0 用户指南1.关于特性⏹支持以下特性:把 (信号处理工具箱和滤波设计工具箱)和软件与公司的软件连接。

⏹支持以下器件系列:●®和器件●和器件●™, 20和 20器件●™器件●®1K器件● 10K®和®6000器件⏹使用开发板快速建立样机。

⏹支持®逻辑分析仪,探测来自上器件嵌入式信号分析仪和把数据转入到工作空间,以利用可视化分析。

⏹在库中支持的转入模块:●或设计授权转入●转入在工程文件中的⏹回路中的硬件模块()能够使硬件在( )中加速二次模拟。

⏹在中的包括了你能用于建立一些定制逻辑的模块,这些定制逻辑和以及其它的设计一起工作。

●低级和辅接口模块●和捆绑模块●全部模块是用户可以配置的●分离的模块可用来支持端口●将接口拖拉进设计模块中,你能建立任何的元件●根据中的仿真,你能验证接口,用生成的和文件把你的设计输出到⏹包括状态机模块。

⏹支持系统算法和执行的统一表示。

⏹自动生成或测试平台或者自动地从和测试向量中自动生成向量文件()。

⏹自动启动编译。

⏹使能用位及周期精确设计仿真。

⏹提供和软件一起使用的各种定点算法和逻辑运算。

⏹生成信号名的自动传播。

⏹使用工作空间或已标记的子系统变量,你能说明模块参数对话框中的大部分值。

一般描述在可编程逻辑器件()的数字信号处理()系统设计中,需要高级算法与硬件描述语言()开发工具。

集成了这些工具,把的和系统级设计工具的算法开发、仿真和验证能力与和设计流程(包括软件)组合在一起。

借助于你在友好的算法环境中生成的设计硬件表示,缩短了设计周期,你能把已存在的函数和模块与模块以及®函数组合在一起,把系统级设计和执行算法开发连接在一起。

在这种方法中,允许系统、算法和硬件设计人员共享一个共同的开发平台。

你能使用中的块在中建立一个模拟系统的硬件执行。

包含位和周期精确的块,这些块又包括许多基本操作,如算法或存储函数以及对关键设计特性优势的运用,如嵌入式,块或嵌入式存储器。

数字集成系统 第十三讲DSP Builder

i =0 i =1 M N

x (n ) x (n -1) x (n -2)

b0 z-1 b 1 z …

-1

y (n ) a1 a2 … … … a N-1 aN z -1 z

-1

y (n -1) y (n -2)

h (0)

h (1)

h (N -3)

h (N -2)ຫໍສະໝຸດ h (N -1) y (n )

11

级联型FIR滤波器

当需要控制系统传输零点时,将传递函数H(z)分解成二阶实 系数因子的形式:

N −1 n =0

H ( z ) = ∑ h( n ) z −n = ∏ ( a0i + a1i z −1 + a2i z −2 )

6

x (n )

z-1

x (n -1)

x (n )

z-1

x (n -1)

x (n )

ax (n )

x (n )

a

ax (n )

a x 1(n ) x 1(n )+x 2(n ) x 1(n ) x 1(n )+x 2(n )

x 2(n )

x 2(n )

三种基本运算的流图

7

直接型Ⅰ型 N阶IIR滤波器

y ( n ) = ∑ bi x ( n − i ) + ∑ ai y ( n − i )

i =0 i =1

M

N

则其系统函数,即滤波器的传递函数为

−i b z ∑i M

H ( z) =

1 − ∑ ai z

i =1

i =0 N

−i

5

对于同一个系统函数H(z), 对输入信号的处理可实现的算法有 很多种,每一种算法对应于一种不同的运算结构(网络结构)。 例如:

dsp

专题二:时序仿真、约束与优化

专题三:FPGA 高级接口与系统协同设计

√ FPGA 与 DSP 处理器协同设计 课程实验 √ 使用 ModelSim 搭建测试平台并验证设计 √ SPI 总线的 Slave 控制器 √ FIR 滤波器设计与优化 √ 乘法器时序约束优化 √ FFT 算法设计与优化 八、 授课专家介绍 张老师:上海交通大学电气工程博士后流动站博士后,上海交通大学 -ALTERA 学生创新实验室主任,在 FPGA 教学及培训方面拥有丰富的经验, 《FPGA 与 SOPC 设计教程—DE2实践》一书的作者。 孙老师:毕业于上海交通大学电子与电气工程学院,拥有丰富的 ALTERA FPGA 设计经验,多次参加 FPGA 培训授课,获得学员的一致好评。现任上海 交通大学-ALTERA 学生创新实验室副主任。主要研究方向为基于 FPGA 的嵌 入式系统设计、基于 FPGA 嵌入式系统性能优化。

² ② FIR 滤波器设计 ● 实验描述 ² 实验1:使用 Simulink 库与 Altera DSP Builder 库在 Simulink 中建立一个 FIR 滤波器。 ² 实验2:在 Simulink 中仿真并声称 FIR 滤波器的代码。 Ⅳ.嵌入式设计流程 ALTERA 引入的 NIOS 系列软核处理器给 FPGA 的设计注入了新的活力, 让 FPGA 的优势得到更好地发挥。本节通过实验与演示对于向学员展示 NIOS II 给 基于 FPGA 的嵌入式设计带来的活力。 ● 课程描述 ² ① NIOS II IDE 概述 ② NIOS II 软核处理器极其 指令扩展 ² ③ 嵌入式系统的硬件构成 ④ Avalon 总线与其外设扩 展 ² ⑤ HAL 与嵌入式软件设计 ⑥ NIOS II 软件开发流程 与调试环境 ² ⑦ 基于 uCLinux 的设计与应用 ● 实验描述 ² 实验1:使用 SOPC Builder 和 NIOS II IDE 在 DE2开发板上建立嵌入式开 发平台。 ² 实验2:为系统添加外设及其编程。 ² 实验3:NIOS II 软件的 C 语言设计与跑马灯样例 ² 实验4:精确定时与 UART 控制 ² 实验5:自定义外设与自定义指令 ² 实验6:基于 uClinux 的设计 NIOS II 系统设计 ² 实验7:NIOS II 系统高级应用演示

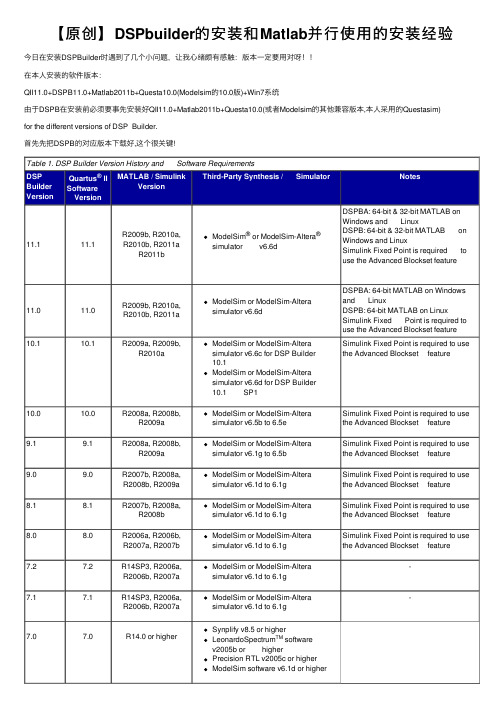

【原创】DSPbuilder的安装和Matlab并行使用的安装经验

【原创】DSPbuilder的安装和Matlab并⾏使⽤的安装经验今⽇在安装DSPBuilder时遇到了⼏个⼩问题,让我⼼绪颇有感触:版本⼀定要⽤对呀!!在本⼈安装的软件版本:QII11.0+DSPB11.0+Matlab2011b+Questa10.0(Modelsim的10.0版)+Win7系统由于DSPB在安装前必须要事先安装好QII11.0+Matlab2011b+Questa10.0(或者Modelsim的其他兼容版本,本⼈采⽤的Questasim) for the different versions of DSP Builder.⾸先先把DSPB的对应版本下载好,这个很关键!然后,安装相应的软件,安装顺序:QII11.0+Questa10.0+Matlab2011b,在安装的时候,因为我⽤的是Questasim10.0,这⼀软件在安装是⾃动⽣成的环境变量很奇怪,但是没有这⼀变量不好使,现在把这⼀变量值写在这⾥:D:\questasim_10.0c\LICENSE.TXT;通常⼤家见到的破解软件都是licence.dat、但是这个很奇特,这也造成了我下⾯很不理解的⼀点,就是在安装好DSPB时,Win7系统并没有添加好环境变量,于是我按照:DSP builder安装指南(以9.1为例)所讲的,添加环境变量,但是发现MATLAB竟然把DSPB的启动环境变量⾃动设置为:D:\questasim_10.0c\LICENSE.TXT;这⼀点我⼗分不理解——不管如何,继续往下看……在matlab中输⼊:dos('lmutil lmdiag C4D5_512A')查看是否破解成功,正常的结果是出现:但是,由于在matlab中显⽰的环境变量是LM_LICENSE_FILE----D:\questasim_10.0c\LICENSE.TXT;我试着在环境变量中添加:LM_LICENSE_FILE---- D:\altera\11.0\quartus\bin\my_superlicense1.dat,但是matlab⼼眼挺直得⼀直赖着LM_LICENSE_FILE----D:\questasim_10.0c\LICENSE.TXT;不⾛,也不肯更换新添加的这个变量⽆奈之下,我就把my_superlicence1.dat中的有关与DSPB破解的内容代号给复制粘贴到D:\questasim_10.0c\LICENSE.TXT的txt的⽂档中可是,最令我想不到的事情发⽣了:Matlab2011b竟然承认了licence中有了DSPB的许可,也就是说我的DSPB的库可以在Simulink中使⽤了这让我很兴奋~但是在把 MATLAB2012a换成2011b之前,我打开Simulink去调⽤Altera DSP Blockset时,在系统初始化的时候,Matlab就会⾃动退出,⽽且没有任何报错的动静。

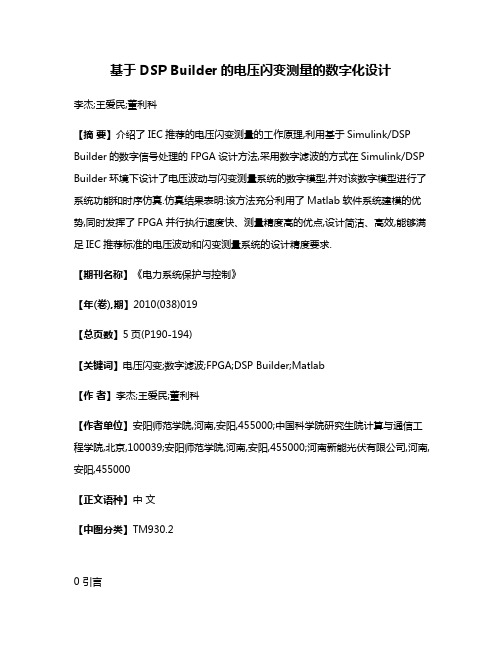

基于DSP Builder的电压闪变测量的数字化设计

基于DSP Builder的电压闪变测量的数字化设计李杰;王爱民;董利科【摘要】介绍了IEC推荐的电压闪变测量的工作原理,利用基于Simulink/DSP Builder的数字信号处理的FPGA设计方法,采用数字滤波的方式在Simulink/DSP Builder环境下设计了电压波动与闪变测量系统的数字模型,并对该数字模型进行了系统功能和时序仿真.仿真结果表明:该方法充分利用了Matlab软件系统建模的优势,同时发挥了FPGA并行执行速度快、测量精度高的优点,设计简洁、高效,能够满足IEC推荐标准的电压波动和闪变测量系统的设计精度要求.【期刊名称】《电力系统保护与控制》【年(卷),期】2010(038)019【总页数】5页(P190-194)【关键词】电压闪变;数字滤波;FPGA;DSP Builder;Matlab【作者】李杰;王爱民;董利科【作者单位】安阳师范学院,河南,安阳,455000;中国科学院研究生院计算与通信工程学院,北京,100039;安阳师范学院,河南,安阳,455000;河南新能光伏有限公司,河南,安阳,455000【正文语种】中文【中图分类】TM930.20 引言电压波动为一系列电压变动或工频电压包络线的周期性变化。

闪变是由于电网中电压波动所引起的灯光闪烁对人视觉产生刺激的响应[1]。

它不仅和电压波动的大小有关,而且和其频率(即对工频电压的调幅频率)、照明灯具的性能以及人的主观视感因素有关[2]。

随着电力系统冲击性负荷的增加,电压闪变已成为衡量电能质量的主要指标之一。

为了抑制和治理电压闪变,电网已经投入了一定的补偿设备。

这些设备的研制和整定均需要准确详细的闪变参数,以提供正确的治理决策,因此对电压闪变实时监测,即准确测量短时间闪变值Pst,长时间闪变值Plt是治理电压闪变的基础[3-4]。

国际电工委员会标准IEC6100-4-15[5]和国标GB1232622000[6]给出了完整的电压闪变测试系统结构框图,以及有关反映人脑对频率选择特性的传递函数,根据该框图可以设计符合IEC标准的闪变测试系统。

DspBuilder使用讲解

第9章 DDS设计

数据线位宽

相 位 字 输 入同 步 寄存器

N

频 率 字 输 入同 步 N 寄存器

clk 系统时钟

N

M

M

寄存器

相位调制器 相位累加器

正 弦 ROM 查找表

正弦信号输出 D/A

余 弦 ROM 查找表

余弦信号输出 D/A

图9-2 正交信号发生器

第9章 DDS设计

幅度调制在很多场合是需要的。我们改进基本DDS 结构,在正弦ROM表后、D/A前放置一个幅度控制模 块,一般采用乘法器来实现。如图9-3。

下面开始仿真。图9-6显示了仿真结果。

第9章 DDS设计

图9-6 仿真结果

第9章 DDS设计

9.3 FSK调制器设计

第9章 DDS设计

9.1 DDS的基本原理

我们知道,对于正弦信号发生器,它的输出可以 用下式来描述:

Sout Asint Asin(2πfoutt).

(9-1)

第9章 DDS设计

其中Sout是指该信号发生器的输出信号波形,fout指 输出信号对应的频率。上式的表述对于时间t是连续的, 为了用数字逻辑实现该表达式,必须进行离散化处理。 用基准时钟clk进行抽样,令正弦信号的相位:

“++” 选择“Pipeline” 参数“Clock Phase Selection”设为“1”

第9章 DDS设计

BusConversion2模块:(BusConversion) 库:Altera DSP Builder中Bus Manipulation库 参数“Input Bus Type”设为“signed Integer” 参数“Input [number of bits].[]”设为32 参数“Output Bus Type”设为“Signed Integer” 参数“Output [number of bits].[]”设为“10” 参数“Input Bit Connected to Output MSB”设为“31” 参数“Input Bit Connected to Output LSB”设为“22” 使用“Round”

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

HDL仿真 (ModelSim)

生成编程文件 (.pof,.sof)

下载至硬件

图3-1 基于Matlab、DSP Builder、 QuartusII等工具

KX

康芯科技

一、 正弦信号调制电路设计(实例分析)

图3-2 正弦信号调制电路原理图

KX

康芯科技

二、 建立设计模型

1、打开Matlab环境

图3-3 正弦波发生模块原理图

KX

康芯科技

3.2 DSP Builder层次化设计

图3-49 修改子系统名

KX

康芯科技

3.2 DSP Builder层次化设计

图3-50 修改SubSystem的端口

KX

康芯科技

3.2 DSP Builder层次化设计

图3-51 顶层图的改变

KX

康芯科技

3.2 DSP Builder层次化设计

图3-52 含subsystem的subsint模型

KX

康芯科技

3.3 基于DSP Builder的DDS设计

3.3.1 DDS模块设计

图3-57 DDS系统

KX

康芯科技

直接数字合成器DDS 原理

1. DDS算法原理

S out A sin t A sin(2π f out t )

2f out t

KX

康芯科技

3.1基于 MATLAB/DSP Builder的DSP模块设计

Matlab Simulink 建立模型 Simulink 模型仿真

mdl转成 vhdl 自动流程 综合 (Quartus II, LeonardoSpectrum, Synplify) ATOM Netlist产生 Quartus II Quartus II 手动流程 综合 (Quartus II, LeonardoSpectrum, Synplify)

图3-26 无符号整数Signed Integer输出电路

KX

康芯科技

3.2 DSP Builder层次化设计

图3-46 准备建立subsystem

KX

康芯科技

3.2 DSP Builder层次化设计

图3-47 建立subsystem后

KX

康芯科技

3.2 DSP Builder层次化设计

图3-48 subsin/subsystem子系统图

KX

康芯科技

KX

康芯科技

直接数字合成器DDS原理

3. DDS的输出频率 fout

f out

其中:

B N f clk 2

(8-7)

BΔθ是频率输入字

fclk是系统基准时钟的频率值 N是相位累加器的数据位宽,也是频率输入字的数据位宽。

KX

康芯科技

直接数字合成器DDS原理

4. DDS的频率分辨率Δf

f Δfout

KX

康芯科技

2. 新建模型文件

图3-4 建立新模型

KX

康芯科技

9.2 正弦信号发生器设计

3、了解simulink库管理器

图9-5 simulink库 管理器

KX

康芯科技

3、放置SignalCompilder---控制部件

图3-6放置SignalCompiler

KX

康芯科技

4、放置Increment Decrement 模块 —阶梯信号发生器

KX

康芯科技

Altera DSP Builder--〉I0 & Bus库

9、放置输出端口OUTPUT

KX

康芯科技

三、Matlab模型仿真

1、加入仿真激励模块

常用的激励模块有:步进(Step), 正弦波(Sine Wave),脉冲发生 器(Pulse Generator)

KX

康芯科技

2、添加波形观察模块

康芯科技

Amp模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“10”

DDSout模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“10”

KX

康芯科技

BusConversion2模块:(BusConversion) 库:Altera DSP Builder中IO & Bus库 参数“Input Bus Type”设为“signed Integer” 参数“Input [number of bits].[]”设为32 参数“Output Bus Type”设为“Signed Integer” 参数“Output [number of bits[.[]”设为“10” 参数“Input Bit Connected to Output MSB”设为“31” 参数“Input Bit Connected to Output LSB”设为“22” 使用“Round” Product模块:(Product) 库:Altera DSP Builder中Arithemtic库 参数“Pipeline”设为“2” 参数“Clock Phase Selection”设为“1” 不选择“Use LPM”

KX

康芯科技

图9-10 LUT模块

KX

康芯科技

6.放置Delay模块

Altera DSP Builder--〉Storage 库

图3-12 Delay模块及其参数设置窗

KX

康芯科技

7、放置乘法器Product模块

Altera DSP Builder--〉Arithmetic库

图3-14 设置乘法单元

f clk N 2

(8-8)

Δf或称频率最小步进值,可用频率输入值步进一个最小 间隔对应的频率输出变化量来衡量。

KX

康芯科技

直接数字合成器DDS原理

5. DDS的频率输入字BΔθ

B

f out 2 f clk

N

(8-9)

注意BΔθ要取整,有时会有误差

KX

康芯科技

直接数字合成器DDS原理

k 1 N 2 2π

(8-5)

B k 1

(8-6)

KX

康芯科技

直接数字合成器DDS原理

2. DDS基本结构

相位字输入

数据线位宽

同步 寄存器

N N M 寄存器 M 正弦ROM 查找表

频率字输入

同步 寄存器

N

D/A

正弦信号输出

相位累加器 clk 系统时钟

相位调制器

图3-58 基本DDS结构

6. DDS的特点:

● DDS的频率分辨率在相位累加器的位数N足够大时,理论

上可以获得相应的分辨精度,这是传统方法难以实现的。

● DDS是一个全数字结构的开环系统,无反馈环节,因此速度

极快,一般在毫微秒量级。

● DDS的相位误差主要依赖于时钟的相位特性,相位误差小。

另外,DDS的相位是连续变化的,形成的信号具有良好的频 谱,这是传统的直接频率合成方法无法实现的。

Δ 2π f out Tclk 2π f out f clk

(8-1)

(8-2)

(8-3)

KX

康芯科技

直接数字合成器DDS原理

1. DDS算法原理

BΔ f out N f clk 2

BΔ

f out 2 f clk

N

(8-4)

Sout Asin( k 1

2π Δ ) Asin N Bk 1 BΔ Af sin Bk 1 BΔ 2

Phaseword模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“32”

KX

3.3.2 DDS模块设计

KX

康芯科技

4、启动仿真

图3-24 有符号输出件MDL转换成VHDL

通过SignalCompilder控制部件启动实现: 模型文件的转换(Covert MDL to VHDL) 综合(Synthesis)--网表文件 适配(QuartusII)—编辑文件 编辑器件(Program Device)

KX

康芯科技

五、使用ModelSim进行RTL级仿真

图3-36 准备执行tcl文件

KX

康芯科技

9.2 正弦信号发生器设计

9.2.4 使用ModelSim进行RTL级仿真

图3-37 ModelSim仿真 结果

KX

康芯科技

使用ModelSim进行RTL级仿真

图3-38 ModelSim的信号设置

KX

KX

9.2.5使用QuartusII实现时序仿真

康芯科技

图3-42 QuartusII工程VHDL程序实体

KX

康芯科技

9.2.5使用QuartusII实现时序仿真

图3-43 打开QuartusII工程的vec仿真激励文件

KX

康芯科技

3.2 DSP Builder层次化设计

设计成无符号数据输出:

Delay模块:(Delay) 库:Altera DSP Builder中Storage库 参数“Depth”设为“1” 参数“Clock Phase Selection”设为“1”