定点除法vhdl源代码

VHDL源代码

VHDL源代码:library ieee; --显示器彩条发生器use VGA isport(clk,mode :in std_logic; --扫描时钟/显示模式选择时钟d,hs,vs,r,g,b:out std_logic); --行,场同步/红,绿,蓝end VGA;architecture a of VGA issignal hs1,vs1,fclk,cclk,divide_clk,dly: std_logic;signal mmode :std_logic_vector(1 downto 0); --方式选择signal cnt :std_logic_vector(2 downto 0);signal fs :std_logic_vector(3 downto 0);signal cc :std_logic_vector(4 downto 0); --行同步/横彩条生成 signal ll :std_logic_vector(8 downto 0); --长同步/竖彩条生成 signal grbh :std_logic_vector(3 downto 1); --X 横彩条signal grby :std_logic_vector(3 downto 1); --Y 竖彩条signal grbx :std_logic_vector(3 downto 1); --文字signal grbt :std_logic_vector(3 downto 1); --图案signal grbp :std_logic_vector(3 downto 1);signal grb :std_logic_vector(3 downto 1);signal x :integer range 0 to 800;signal x1: integer range 0 to 800;signal y1: integer range 0 to 600;signal x2: integer range 0 to 800;signal x3: integer range 0 to 800;signal x4: integer range 0 to 800;signal x5: integer range 0 to 800;signal x7: integer range 0 to 800;signal x8: integer range 0 to 800;signal x9: integer range 0 to 800;signal x10: integer range 0 to 800;signal x11: integer range 0 to 800;signal y2: integer range 0 to 600;signal y3: integer range 0 to 600;signal y4: integer range 0 to 600;signal y5: integer range 0 to 600;signal y6: integer range 0 to 600;signal c: integer range 0 to 30;begingrb(3)<=(grbp(3) xor mode) and hs1 and vs1;grb(2)<=(grbp(2) xor mode) and hs1 and vs1;grb(1)<=(grbp(1) xor mode) and hs1 and vs1;process(mode)beginif mode'event and mode='1' thenif mmode="11" thenmmode<="00";elsemmode<=mmode+1;end if;end if;end process; --四种模式process (mmode)beginif mmode="00" then grbp<=grbx;elsif mmode="01" then grbp<=grbh; --选择横彩条 elsif mmode="10" then grbp<=grby; --选择竖彩条elsif mmode="11" then grbp<=grbh xor grby; --选择棋盘格 else grbp<="000";end if;end process;process(clk) --3/4分频 beginif clk'event and clk='1' thencnt<=cnt+3;dly<=cnt(2);end if;--if cnt<3 then-- divide_clk<='0';--elsif cnt<5 then-- divide_clk<='1';--else-- cnt<="000";--end if;end process;divide_clk<=(cnt(2) xor dly) and clk;process(divide_clk) --13分频beginif divide_clk'event and divide_clk='1' thenif fs=12 thenfs<="0000";elsefs<=fs+1;end if;end if;end process;process(fclk)beginif fclk'event and fclk='1' thenif cc=29 thencc<="00000";elsecc<=cc+1;end if;end if;end process;d<=fclk;process(cclk)beginif cclk'event and cclk='1' thenif ll=481 thenll<="000000000";elsell<=ll+1;end if;end if;end process;process(cc,ll)beginif cc>23 then --行同步hs1<='0';elsehs1<='1';end if;if ll>479 then --长同步 vs1<='0';elsevs1<='1';end if;end process;process(clk)beginif clk'event and clk='1' thenif hs1='0' thenx<=0;elsex<=x+1;end if;end if;end process;process(x,ll,cc,hs1,vs1)variable s1: integer range 0 to 3;beginif cc<3 then grbh<="111"; --竖彩条 elsif cc<6 then grbh<="110";elsif cc<9 then grbh<="101";elsif cc<12 then grbh<="100";elsif cc<15 then grbh<="011";elsif cc<18 then grbh<="010";elsif cc<21 then grbh<="001";else grbh<="000";end if;if ll<60 then grby<="111"; --横彩条 elsif ll<120 then grby<="110";elsif ll<180 then grby<="101";elsif ll<240 then grby<="100";elsif ll<300 then grby<="011";elsif ll<360 then grby<="010";elsif ll<420 then grby<="001";else grby<="000";end if;if x=4 thengrbx<="100";elsif x=180 thengrbx<="001";elsegrbx<="000";end if;if ll>20 and ll<24 thenif x<110 thengrbx<="100";end if;end if;if ll>30 and ll<33 thenif x<80 thengrbx<="100";end if;end if;if ll>445 and ll<449 thenif x>90 thengrbx<="001";end if;end if;if ll>437 and ll<440 thenif x>100 thengrbx<="001";end if;end if;--"湖"if ll>89 and ll<94 thenif x=100 or x=103 or x=106 or x=107 or x=108 then grbx<="110";end if;end if;if ll>93 and ll<98 thenif x=102 or x=103 or x=104 or x=106 or x=108 then grbx<="110";end if;end if;if ll>97 and ll<102 thenif x=100 or x=103 or x=106 or x=107 or x=108 then grbx<="110";end if;end if;if ll>101 and ll<106 thenif x=102 or x=103 or x=104 or x=106 or x=108 thengrbx<="110";end if;end if;if ll>105 and ll<110 thenif x=100 or x=102 or x=104 or x=106 or x=107 or x=108 then grbx<="110";end if;end if;if ll>109 and ll<114 thenif x=100 or x=102 or x=103 or x=104 or x=106 or x=108 then grbx<="110";end if;end if;if ll>113 and ll<118 thenif x=106 thengrbx<="110";end if;end if;--"南"if ll>121 and ll<126 thenif x=104 thengrbx<="110";end if;end if;if ll>125 and ll<130 thenif x>99 and x<109 thengrbx<="110";end if;if ll>129 and ll<134 thenif x=104 thengrbx<="110";end if;end if;if ll>133 and ll<138 thenif x>99 and x<109 thengrbx<="110";end if;end if;if ll>137 and ll<142 thenif x=100 or x=108 thengrbx<="110";end if;end if;if ll>141 and ll<146 thenif x=100 or x=103 or x=105 or x=108 thengrbx<="110";end if;end if;if ll>145 and ll<150 thenif x=100 or x=102 or x=103 or x=104 or x=105 or x=106 or x=108 then grbx<="110";end if;end if;if ll>149 and ll<154 thenif x=100 or x=104 or x=108 thengrbx<="110";end if;if ll>153 and ll<158 thenif x=100 or x=102 or x=103 or x=104 or x=105 or x=106 or x=108 thengrbx<="110";end if;end if;if ll>157 and ll<162 thenif x=100 or x=104 or x=108 thengrbx<="110";end if;end if;--"大"if ll>165 and ll<170 thenif x=103 or x=104 thengrbx<="110";end if;end if;if ll>169 and ll<174 thenif x=103 or x=104 thengrbx<="110";end if;end if;if ll>173 and ll<178 thenif x=100 or x=101 or x=102 or x=103 or x=104 or x=105 or x=106 or x=107 or x=108 thengrbx<="110";end if;end if;if ll>177 and ll<182 thenif x=103 or x=104 thengrbx<="110";end if;end if;if ll>181 and ll<186 thenif x=103 or x=104 thengrbx<="110";end if;end if;if ll>185 and ll<190 thenif x=103 or x=105 thengrbx<="110";end if;end if;if ll>189 and ll<194 thenif x=102 or x=103 or x=106 thengrbx<="110";end if;end if;if ll>193 and ll<198 thenif x=101 or x=102 or x=107 thengrbx<="110";end if;end if;if ll>197 and ll<202 thenif x=100 or x=101 or x=107 or x=108 then grbx<="110";end if;end if;--"学"if ll>205 and ll<210 thenif x=102 or x=104 or x=106 thengrbx<="110";end if;end if;if ll>209 and ll<214 thenif x=100 or x=101 or x=102 or x=103 or x=104 or x=105 or x=106 or x=107 or x=108 thengrbx<="110";end if;end if;if ll>213 and ll<218 thenif x=100 or x=108 thengrbx<="110";end if;end if;if ll>217 and ll<222 thenif x=102 or x=103 or x=104 or x=105 or x=106 thengrbx<="110";end if;end if;if ll>221 and ll<226 thenif x=105 thengrbx<="110";end if;end if;if ll>225 and ll<230 thenif x=104 thengrbx<="110";end if;end if;if ll>229 and ll<234 thenif x=100 or x=101 or x=102 or x=103 or x=104 or x=105 or x=106 or x=107 or x=108 thengrbx<="110";end if;end if;if ll>233 and ll<238 thenif x=104 thengrbx<="110";end if;end if;if ll>237 and ll<242 thenif x=104 thengrbx<="110";end if;end if;if ll>241 and ll<245 thenif x=103 or x=104 thengrbx<="110";end if;end if;if vs1'event and vs1='1' thenif c=20 thenc<=0;case s1 iswhen 0 =>if x1=120 thens1:=1;elsex1<=x1+1 ; end if;when 1 =>if y1=350 thens1:=2;elsey1<=y1+1; end if;when 2 =>if x1=35 thens1:=3;elsex1<=x1-1; end if;when 3 =>if y1=280 thens1:=0;elsey1<=y1-1; end if;end case;elsec<=c+1;end if;end if;--"HU NAN DA XUE"x2<=x1+1;x3<=x1+2;x4<=x1+3;x5<=x1+5;x7<=x1+7;x8<=x1+8;x9<=x1+9;x10<=x1+10;x11<=x1+11;--y1<=250;y2<=y1+4;y3<=y1+8;y4<=y1+12;y5<=y1+16;y6<=y1+20;if ll>=y1 and ll<y2 thenif x=x1 or x=x5 or x=x7 or x=x8 or x=x11 thengrbx<="101";end if;end if;if ll>=y2 and ll<y3 thenif x=x1 or x=x5 or x=x7 or x=x8 or x=x9 or x=x11 then grbx<="101";end if;end if;if ll>=y3 and ll<y4 thenif x=x1 or x=x2 or x=x3 or x=x4 or x=x5 or x=x7 or x=x9 or x=x11 then grbx<="101";end if;end if;if ll>=y4 and ll<y5 thenif x=x1 or x=x5 or x=x7 or x=x10 or x=x11 thengrbx<="101";end if;end if;if ll>=y5 and ll<y6 thenif x=x1 or x=x5 or x=x7 or x=x10 or x=x11 thengrbx<="101";end if;end if;if ll>100 and 11<150 then --图案设计if ll>121 and ll<126 thenif x>43 and x<57 thengrbx<="100";end if;elsif x=50 thengrbx<="100";end if;end if;if ll>150 and 11<200 thenif ll>171 and ll<176 thenif x>60 and x<74 thengrbx<="010";end if;elsif x=67 thengrbx<="010";end if;end if;if ll>200 and 11<250 then if ll>221 and ll<226 then if x>74 and x<88 then grbx<="001";end if;elsif x=81 thengrbx<="001";end if;end if;end process;fclk<=fs(2);cclk<=cc(4);hs<= not hs1;vs<= not vs1;g<=grb(3);r<=grb(2);b<=grb(1);end a;。

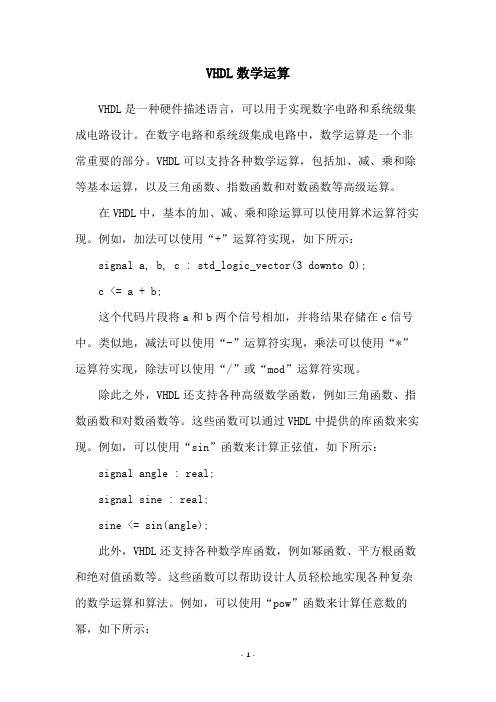

VHDL数学运算

VHDL数学运算VHDL是一种硬件描述语言,可以用于实现数字电路和系统级集成电路设计。

在数字电路和系统级集成电路中,数学运算是一个非常重要的部分。

VHDL可以支持各种数学运算,包括加、减、乘和除等基本运算,以及三角函数、指数函数和对数函数等高级运算。

在VHDL中,基本的加、减、乘和除运算可以使用算术运算符实现。

例如,加法可以使用“+”运算符实现,如下所示:signal a, b, c : std_logic_vector(3 downto 0);c <= a + b;这个代码片段将a和b两个信号相加,并将结果存储在c信号中。

类似地,减法可以使用“-”运算符实现,乘法可以使用“*”运算符实现,除法可以使用“/”或“mod”运算符实现。

除此之外,VHDL还支持各种高级数学函数,例如三角函数、指数函数和对数函数等。

这些函数可以通过VHDL中提供的库函数来实现。

例如,可以使用“sin”函数来计算正弦值,如下所示:signal angle : real;signal sine : real;sine <= sin(angle);此外,VHDL还支持各种数学库函数,例如幂函数、平方根函数和绝对值函数等。

这些函数可以帮助设计人员轻松地实现各种复杂的数学运算和算法。

例如,可以使用“pow”函数来计算任意数的幂,如下所示:signal base : real;signal exponent : integer;signal result : real;result <= pow(base, exponent);总之,VHDL的数学运算功能非常强大,可以帮助设计人员轻松地实现各种数字电路和系统级集成电路的数学运算和算法。

设计人员应该熟练掌握VHDL的数学运算功能,以便能够高效地进行设计和开发工作。

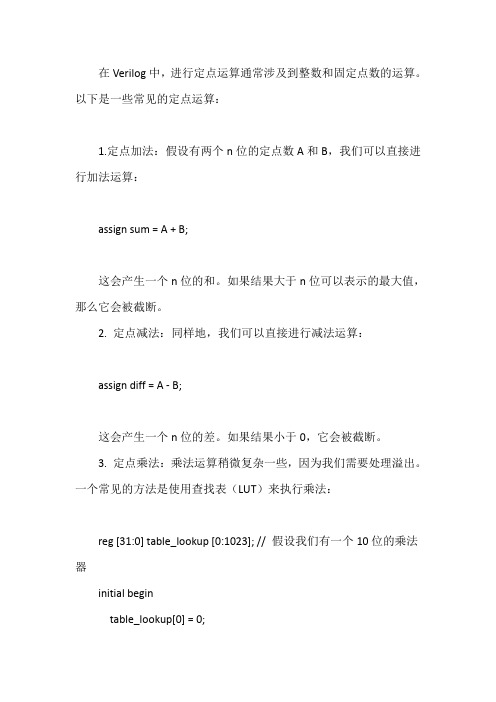

verilog定点运算

在Verilog中,进行定点运算通常涉及到整数和固定点数的运算。

以下是一些常见的定点运算:1.定点加法:假设有两个n位的定点数A和B,我们可以直接进行加法运算:assign sum = A + B;这会产生一个n位的和。

如果结果大于n位可以表示的最大值,那么它会被截断。

2. 定点减法:同样地,我们可以直接进行减法运算:assign diff = A - B;这会产生一个n位的差。

如果结果小于0,它会被截断。

3. 定点乘法:乘法运算稍微复杂一些,因为我们需要处理溢出。

一个常见的方法是使用查找表(LUT)来执行乘法:reg [31:0] table_lookup [0:1023]; // 假设我们有一个10位的乘法器initial begintable_lookup[0] = 0;table_lookup[1] = 1;for (int i = 2; i <= 1023; i = i + 1) begintable_lookup[i] = 2 * table_lookup[i-1] + (i >= A & i >= B); // 假设A和B是非负整数endendassign product = table_lookup[A * B]; // 假设A和B是非负整数,并且A * B不会超过10234.定点除法:除法运算同样复杂,并且需要处理除以零的情况。

一个常见的方法是使用查找表来执行除法:reg [31:0] table_lookup [0:1023]; // 假设我们有一个10位的除法器initial begintable_lookup[0] = 0;table_lookup[1] = 1;for (int i = 2; i <= 1023; i = i + 1) begintable_lookup[i] = table_lookup[i-1] + (i >= A & i >= B); // 假设A和B是非负整数,并且A > Bendendassign quotient = table_lookup[A / B]; // 假设A和B是非负整数,并且A > B,并且B不为零注意:这些代码示例假设我们正在处理32位整数,并且我们有一个10位的乘法和除法器。

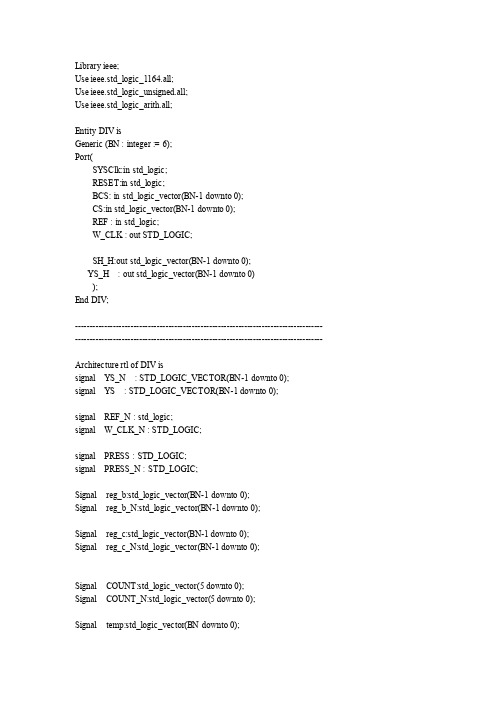

VHDL编写的除法器,位数可调,可以进行浮点(小数)运算

Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity DIV isGeneric(BN:integer:=6);Port(SYSClk:in std_logic;RESET:in std_logic;BCS:in std_logic_vector(BN-1downto0);CS:in std_logic_vector(BN-1downto0);REF:in std_logic;W_CLK:out STD_LOGIC;SH_H:out std_logic_vector(BN-1downto0);YS_H:out std_logic_vector(BN-1downto0));End DIV;--------------------------------------------------------------------------------------------------------------------------------------------------------------------------Architecture rtl of DIV issignal YS_N:STD_LOGIC_VECTOR(BN-1downto0);signal YS:STD_LOGIC_VECTOR(BN-1downto0);signal REF_N:std_logic;signal W_CLK_N:STD_LOGIC;signal PRESS:STD_LOGIC;signal PRESS_N:STD_LOGIC;Signal reg_b:std_logic_vector(BN-1downto0);Signal reg_b_N:std_logic_vector(BN-1downto0);Signal reg_c:std_logic_vector(BN-1downto0);Signal reg_c_N:std_logic_vector(BN-1downto0);Signal COUNT:std_logic_vector(5downto0);Signal COUNT_N:std_logic_vector(5downto0);Signal temp:std_logic_vector(BN downto0);Signal temp_n:std_logic_vector(BN downto0);signal PLUS:std_logic_vector(BN downto0);signal PLUS_N:std_logic_vector(BN downto0);signal STATE:STD_LOGIC;signal STA TE_N:STD_LOGIC;--signal REG_B_N:STD_LOGIC_VECTOR(BN-1downto0);signal SH:STD_LOGIC_VECTOR(BN-1downto0); signal SH_N:STD_LOGIC_VECTOR(BN-1downto0);Begin--------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenCOUNT<=(others=>'0');elsif(SYSCLK'event and SYSCLK='1')thenCOUNT<=COUNT_N;end if;end process;process(STA TE,COUNT)beginif STATE='1'thenCOUNT_N<=COUNT+1;elseCOUNT_N<=(others=>'0');end if;end process;--------------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenSTATE<='0';elsif(SYSCLK'event and SYSCLK='1')thenSTATE<=STATE_N;end if;end process;process(PRESS,COUNT,STA TE)beginif PRESS='1'thenSTA TE_N<='1';elsif COUNT=BN thenSTA TE_N<='0';elseSTA TE_N<=STATE;end if;end process;--------------------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenREF_N<='0';elsif(SYSCLK'event and SYSCLK='1')thenREF_N<=REF;end if;end process;process(SYSCLK,RESET)beginif RESET='0'thenPRESS<='0';elsif(SYSCLK'event and SYSCLK='1')thenPRESS<=PRESS_N;end if;end process;process(REF,REF_N)beginif REF='0'and REF_N='1'thenPRESS_N<='1';elsePRESS_N<='0';end if;end process;------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenREG_B<=(others=>'0');elsif(SYSCLK'event and SYSCLK='1')thenREG_B<=REG_B_N;end if;end process;process(REF,STA TE,BCS,REG_B,COUNT)beginif REF='1'thenREG_B_N<=BCS;elsif STATE='1'thenREG_B_N<=REG_B(BN-2downto0)&'0';elseREG_B_N<=REG_B;end if;end process;----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenREG_C<=(others=>'0');elsif(SYSCLK'event and SYSCLK='1')thenREG_C<=REG_C_N;end if;end process;process(REF,REG_C,CS)beginif REF='1'thenREG_C_N<=CS;elseREG_C_N<=REG_C;end if;end process;--------------------------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenTEMP<=(others=>'0');elsif(SYSCLK'event and SYSCLK='1')thenTEMP<=TEMP_N;end if;end process;process(STA TE,PLUS,REG_B,TEMP)beginif STATE='1'thenTEMP_N<=PLUS(BN-1downto0)®_B(BN-1);elseTEMP_N<=TEMP;end if;end process;------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------process(STA TE,TEMP,REG_C,PLUS)beginif STATE='1'thenif TEMP<REG_C thenPLUS<=TEMP;elsePLUS<=TEMP-REG_C;end if;elsePLUS<=(others=>'0');end if;end process;--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenSH<=(others=>'0');elsif(SYSCLK'event and SYSCLK='1')thenSH<=SH_N;end if;end process;process(TEMP,REG_C,SH,STA TE)beginif STATE='1'thenif TEMP<REG_C thenSH_N<=SH(BN-2downto0)&'0';elseSH_N<=SH(BN-2downto0)&'1';end if;elseSH_N<=SH;end if;end process;------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenW_CLK<='0';elsif SYSCLK'event and SYSCLK='1'thenW_CLK<=W_CLK_N;end if;end process;process(COUNT)beginif COUNT=(BN+1)thenW_CLK_N<='1';elseW_CLK_N<='0';end if;end process;----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------process(SYSCLK,RESET)beginif RESET='0'thenYS<=(others=>'0');elsif SYSCLK'event and SYSCLK='1'thenYS<=YS_N;end if;end process;process(COUNT,TEMP,YS)beginif COUNT=BN thenYS_N<=TEMP(BN-1downto0);elseYS_N<=YS;end if;end process;------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------YS_H<=YS;SH_H<=SH;----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------end rtl;。

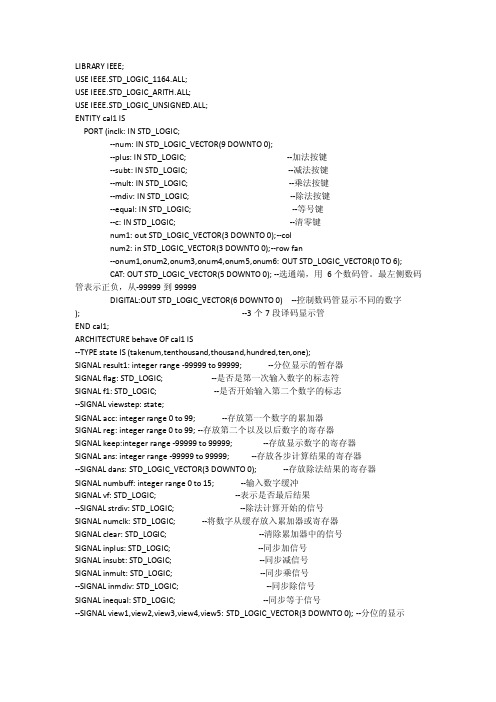

VHDL简易计算器代码

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY cal1 ISPORT (inclk: IN STD_LOGIC;--num: IN STD_LOGIC_VECTOR(9 DOWNTO 0);--plus: IN STD_LOGIC; --加法按键--subt: IN STD_LOGIC; --减法按键--mult: IN STD_LOGIC; --乘法按键--mdiv: IN STD_LOGIC; --除法按键--equal: IN STD_LOGIC; --等号键--c: IN STD_LOGIC; --清零键num1: out STD_LOGIC_VECTOR(3 DOWNTO 0);--colnum2: in STD_LOGIC_VECTOR(3 DOWNTO 0);--row fan--onum1,onum2,onum3,onum4,onum5,onum6: OUT STD_LOGIC_VECTOR(0 TO 6);CAT: OUT STD_LOGIC_VECTOR(5 DOWNTO 0); --选通端,用6个数码管。

最左侧数码管表示正负,从-99999到99999DIGITAL:OUT STD_LOGIC_VECTOR(6 DOWNTO 0) --控制数码管显示不同的数字); --3个7段译码显示管END cal1;ARCHITECTURE behave OF cal1 IS--TYPE state IS (takenum,tenthousand,thousand,hundred,ten,one);SIGNAL result1: integer range -99999 to 99999; --分位显示的暂存器SIGNAL flag: STD_LOGIC; --是否是第一次输入数字的标志符SIGNAL f1: STD_LOGIC; --是否开始输入第二个数字的标志--SIGNAL viewstep: state;SIGNAL acc: integer range 0 to 99; --存放第一个数字的累加器SIGNAL reg: integer range 0 to 99; --存放第二个以及以后数字的寄存器SIGNAL keep:integer range -99999 to 99999; --存放显示数字的寄存器SIGNAL ans: integer range -99999 to 99999; --存放各步计算结果的寄存器--SIGNAL dans: STD_LOGIC_VECTOR(3 DOWNTO 0); --存放除法结果的寄存器SIGNAL numbuff: integer range 0 to 15; --输入数字缓冲SIGNAL vf: STD_LOGIC; --表示是否最后结果--SIGNAL strdiv: STD_LOGIC; --除法计算开始的信号SIGNAL numclk: STD_LOGIC; --将数字从缓存放入累加器或寄存器SIGNAL clear: STD_LOGIC; --清除累加器中的信号SIGNAL inplus: STD_LOGIC; --同步加信号SIGNAL insubt: STD_LOGIC; --同步减信号SIGNAL inmult: STD_LOGIC; --同步乘信号--SIGNAL inmdiv: STD_LOGIC; --同步除信号SIGNAL inequal: STD_LOGIC; --同步等于信号--SIGNAL view1,view2,view3,view4,view5: STD_LOGIC_VECTOR(3 DOWNTO 0); --分位的显示SIGNAL cou: STD_LOGIC_VECTOR(1 DOWNTO 0); --用力记忆是第几次--计算的信号SIGNAL clk_gg: STD_LOGIC_VECTOR(11 DOWNTO 0); --用于产生分频时钟的信号--SIGNAL CNT : INTEGER RANGE 0 TO 50000;--分频用SIGNAL clk: STD_LOGIC; --分频后的时钟信号--signal ko : integer range 0 to 15;SIGNAL CAT0:INTEGER RANGE 0 TO 10; --数码管显示5位数,共有5个CAT选通端SIGNAL CAT1:INTEGER RANGE 0 TO 10;SIGNAL CAT2:INTEGER RANGE 0 TO 10;SIGNAL CAT3:INTEGER RANGE 0 TO 10;SIGNAL CAT4:INTEGER RANGE 0 TO 10;TYPE TIME_TYPE IS (T1,T2,T3,T4,T5,T6);SIGNAL TIME1:TIME_TYPE;--COMPONENT numdecoder IS --引用数字按键的译码电路--PORT ( reset: IN STD_LOGIC;--inclk: IN STD_LOGIC;--innum: IN STD_LOGIC_VECTOR(9 DOWNTO 0);--outnum: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);--outflag: OUT STD_LOGIC );--END COMPONENT;component keyboard ISPORT(--clk:in std_logic; ---时钟信号--row_scan :out STD_LOGIC_vector(3 downto 0); ---行扫描输出信号--col_scan :in std_logic_vector(3 downto 0);---列扫描输入信号--key_output :out std_logic_vector(3 downto 0);--key_down :out std_logic;--keyout :out integer range 0 to 15;--SYS_CLK : in std_logic;-- KEY_ROW : in std_logic_vector(3 downto 0); --4*4键盘扫描4输入--KEY_COL : out std_logic_vector(3 downto 0); --4*4键盘扫描4输出--KEY_DATA : out std_logic_vector(3 downto 0); --输出键值,-- KEY_READY : out std_logicKEY_CLK : in std_logic;KEY_ROW : in std_logic_vector(3 downto 0); --4*4键盘扫描4输入KEY_COL : out std_logic_vector(3 downto 0); --4*4键盘扫描4输出--KEY_DATA : out std_logic_vector(3 downto 0); --输出键值,--KEY_READY : out std_logicKEY_DOWN :out std_logic;KEY_OUT :out integer range 0 to 15);end component;--COMPONENT vdecode IS --引用7段译码器--PORT(indata:IN STD_LOGIC_VECTOR(3 DOWNTO 0);-- outdata:OUT STD_LOGIC_VECTOR(0 TO 6));--END COMPONENT;--COMPONENT diver IS --引用除法器--PORT( a: IN STD_LOGIC_VECTOR(7 DOWNTO 0);-- b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);-- clk: IN STD_LOGIC;--str: IN STD_LOGIC;--s: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);-- y: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--);--END COMPONENT;BEGIN--inum1: numdecoder port map(c,clk,num,numbuff,numclk);--inum2:keyboard44 port map(clk,num1,num2,numbuff,numclk,ko);inum2:keyboard port map(inclk,num2,num1,numclk,numbuff);clock: PROCESS(inclk,numbuff) --进程clock用于产生分频的时钟,使得12位向量clk_gg不断加1,然后输出12位中的某一位BEGINIF inclk'EVENT AND inclk='1' thenclk_gg(11 DOWNTO 0)<=clk_gg(11 DOWNTO 0)+1;END IF;END PROCESS clock;clk<=clk_gg(11);pacecal: PROCESS(numbuff,clk)BEGINIF (rising_edge(clk) and numbuff=15) theninplus<='0';insubt<='0';inmult<='0';--inmdiv<='0';ELSIF clk'EVENT AND clk='1' thenIF numbuff=10 theninplus<='1'; insubt<='0';inmult<='0';--inmdiv<='0';ELSIF numbuff=11 theninplus<='0';insubt<='1';inmult<='0';--inmdiv<='0';ELSIF numbuff=12 theninplus<='0';insubt<='0';inmult<='1';--inmdiv<='0';-- ELSIF mdiv='1' then-- inplus<='0';insubt<='0';inmult<='0';inmdiv<='1';END IF;END IF;END PROCESS pacecal;ctrflag: PROCESS(numbuff,clk) --用于产生flag信号BEGINIF (rising_edge(clk) and numbuff=15) thenflag<='0';ELSIF clk'EVENT AND clk='1' thenIF inplus='1' OR insubt='1' OR inmult='1' --OR inmdiv='1'THENflag<='1';ELSE flag<='0';END IF;END IF;END PROCESS ctrflag;ctrfirstnum: PROCESS(numbuff,numclk) --用于输入第一个运算数BEGINIF ( numbuff=15) thenacc<=0;ELSIF numclk'EVENT AND numclk='1' thenIF flag='0' thenacc<=acc*10+numbuff;END IF;END IF;END PROCESS ctrfirstnum;ctrsecondnum:PROCESS(numbuff,clear,numclk) --用于输入第二个以后的运算数字BEGINIF ( numbuff=15 OR clear='1')THENreg<=0;f1<='0';ELSIF numclk'event AND numclk='1'THENIF flag='1'THENf1<='1';reg<=reg*10+numbuff;END IF;END IF;END PROCESS ctrsecondnum;ctrclear: PROCESS(numbuff,clk) --用于产生clear信号为什么c和clear不同步反BEGINIF (numbuff=15)thenclear<='0';ELSIF clk'EVENT AND clk='1' thenIF numbuff=10 or numbuff=11 or numbuff=12 thenclear<='1';ELSE clear<='0';END IF;END IF;END PROCESS ctrclear;ctrinequal:PROCESS(numbuff,clk) --用于产生inequal信号BEGINIF (numbuff=15) theninequal<='0';ELSIF clk'EVENT AND clk='1' thenIF numbuff=10 or numbuff=11 or numbuff=12 or numbuff=14 theninequal<='1';ELSE inequal<='0';END IF;END IF;END PROCESS ctrinequal;ctrcou: process (numbuff,inequal) --用于产生cou信号什么意思?BEGINIF (numbuff=15 )thencou<="00";ELSIF inequal'EVENT and inequal='1'thenIF cou="10" thencou<=cou;ELSE cou<=cou+1;END IF;END IF;END PROCESS ctrcou;ctrcal: PROCESS (numbuff,inequal) --用于实现运算BEGINIF ( numbuff=15 ) thenans<=0;--strdiv<='0';ELSIF inequal'EVENT and inequal='1' thenIF flag='1' thenIF inplus='1' thenIF cou="10" thenans<=ans+reg;ELSE ans<=acc+reg;END IF;ELSIF insubt='1'THENIF cou="10"THENans<=ans-reg;ELSE ans<=acc-reg;END IF;ELSIF inmult='1' then--IF acc<="1111111" AND reg<="1111111" then--将乘数和被乘数限制在4位二进制数范围内IF cou="10" thenans<=ans*reg;ELSE ans<=acc*reg;END IF;--ELSE ans<=0;-- END IF;--ELSIF inmdiv='1'THEN--strdiv<='1';END IF;--else strdiv<='0';END IF;END IF;END PROCESS ctrcal;--d1:diver PORT MAP (acc,reg(3 DOWNTO 0),clk,strdiv,dans);--将除法结果放在dans中ctrvf: PROCESS(numbuff,clk) --用来产生vf信号BEGINIF (rising_edge(clk) and numbuff=15) thenvf<='0';ELSIF (rising_edge(clk) and numbuff=14) thenvf<='1';END IF;END PROCESS ctrvf;ctrkeep: process(numbuff,clk) --用于控制keep寄存器BEGINIF (numbuff=15) then --keep寄存器清零keep<=0;ELSIF clk'EVENT AND clk='1' thenIF flag='0' then --输入第二个数以前keep中存放acc中的数keep<=acc;ELSIF flag='1' AND f1='1' AND vf='0' then--输入第二个数以前keep中存放reg中的数keep<=reg;ELSIF flag='1' AND f1='0'AND vf='0'AND cou="10" then--keep中存放ans中的内容keep<=ans;ELSIF flag='1'and vf='1'then --最终的计算结果-- IF inmdiv='0'THENkeep<=ans;-- ELSE-- keep(3 DOWNTO 0)<=dans;--END IF;END IF;END IF;END PROCESS ctrkeep;ctrview:PROCESS(numbuff,clk)BEGINIF (rising_edge(clk) and numbuff=15) THENcat4<=0; cat3<=0;cat2<=0;cat1<=0;cat0<=0;ELSIF clk'EVENT AND clk='1'THENif(keep<0)then result1<=abs(keep);else result1<=keep;end if;if(result1>99999 )then cat4<=10; cat3<=10;cat2<=10;cat1<=10;cat0<=10;end if;if(result1>=90000 and result1<=99999)then cat4<=9;elsif(result1>=80000 and result1<90000)then cat4<=8;elsif(result1>=70000 and result1<80000)then cat4<=7;elsif(result1>=60000 and result1<70000)then cat4<=6;elsif(result1>=50000 and result1<60000)then cat4<=5;elsif(result1>=40000 and result1<50000)then cat4<=4;elsif(result1>=30000 and result1<40000)then cat4<=3;elsif(result1>=20000 and result1<30000)then cat4<=2;elsif(result1>=10000 and result1<20000)then cat4<=1;elsif(result1<10000 )then cat4<=0;end if;if((result1-cat4*10000)>=9000 and (result1-cat4*10000)<10000)then cat3<=9;elsif((result1-cat4*10000)>=8000 and (result1-cat4*10000)<9000)then cat3<=8;elsif((result1-cat4*10000)>=7000 and (result1-cat4*10000)<8000)then cat3<=7;elsif((result1-cat4*10000)>=6000 and (result1-cat4*10000)<7000)then cat3<=6;elsif((result1-cat4*10000)>=5000 and (result1-cat4*10000)<6000)then cat3<=5;elsif((result1-cat4*10000)>=4000 and (result1-cat4*10000)<5000)then cat3<=4;elsif((result1-cat4*10000)>=3000 and (result1-cat4*10000)<4000)then cat3<=3;elsif((result1-cat4*10000)>=2000 and (result1-cat4*10000)<3000)then cat3<=2;elsif((result1-cat4*10000)>=1000 and (result1-cat4*10000)<2000)then cat3<=1;elsif((result1-cat4*10000)<1000)then cat3<=0;end if;if((result1-cat4*10000-cat3*1000)>=900and (result1-cat4*10000-cat3*1000)<1000)then cat2<=9;elsif((result1-cat4*10000-cat3*1000)>=800and (result1-cat4*10000-cat3*1000)<900)then cat2<=8;elsif((result1-cat4*10000-cat3*1000)>=700and (result1-cat4*10000-cat3*1000)<800)then cat2<=7;elsif((result1-cat4*10000-cat3*1000)>=600and (result1-cat4*10000-cat3*1000)<700)then cat2<=6;elsif((result1-cat4*10000-cat3*1000)>=500and (result1-cat4*10000-cat3*1000)<600)thencat2<=5;elsif((result1-cat4*10000-cat3*1000)>=400and (result1-cat4*10000-cat3*1000)<500)then cat2<=4;elsif((result1-cat4*10000-cat3*1000)>=300and (result1-cat4*10000-cat3*1000)<400)then cat2<=3;elsif((result1-cat4*10000-cat3*1000)>=200and (result1-cat4*10000-cat3*1000)<300)then cat2<=2;elsif((result1-cat4*10000-cat3*1000)>=100and (result1-cat4*10000-cat3*1000)<200)then cat2<=1;elsif((result1-cat4*10000-cat3*1000)<100) then cat2<=0;end if;if((result1-cat4*10000-cat3*1000-cat2*100)>=90and(result1-cat4*10000-cat3*1000-cat2*100)<100)then cat1<=9;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=80and(result1-cat4*10000-cat3*1000-cat2*100)<90)then cat1<=8;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=70and(result1-cat4*10000-cat3*1000-cat2*100)<80)then cat1<=7;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=60and(result1-cat4*10000-cat3*1000-cat2*100)<70)then cat1<=6;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=50and(result1-cat4*10000-cat3*1000-cat2*100)<60)then cat1<=5;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=40and(result1-cat4*10000-cat3*1000-cat2*100)<50)then cat1<=4;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=30and(result1-cat4*10000-cat3*1000-cat2*100)<40)then cat1<=3;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=20and(result1-cat4*10000-cat3*1000-cat2*100)<30)then cat1<=2;elsif((result1-cat4*10000-cat3*1000-cat2*100)>=10and(result1-cat4*10000-cat3*1000-cat2*100)<20)then cat1<=1;elsif((result1-cat4*10000-cat3*1000-cat2*100)<10)then cat1<=0;end if;cat0<=result1-cat4*10000-cat3*1000-cat2*100-cat1*10;end if;END PROCESS ctrview;--v1:vdecode PORT MAP (view1,onum1); --7段译码显示百位--v2:vdecode PORT MAP (view2,onum2); --7段译码显示十位--v3:vdecode PORT MAP (view3,onum3); --7段译码显示个位--v4:vdecode PORT MAP (view4,onum4); --7段译码显示十位--v5:vdecode PORT MAP (view5,onum5); --7段译码显示个位xianshi:PROCESS(clk,time1,cat4,cat3,cat2,cat1,cat0)beginIF rising_edge(clk) THENif(keep>=0)thenCASE TIME1 ISWHEN T1 =>CAT <= "101111";CASE CAT4 ISWHEN 0=> DIGITAL <= "1111110";WHEN 1=> DIGITAL <= "0110000";WHEN 2=> DIGITAL <= "1101101";WHEN 3=> DIGITAL <= "1111001";WHEN 4=> DIGITAL <= "0110011";WHEN 5=> DIGITAL <= "1011011";WHEN 6=> DIGITAL <= "1011111";WHEN 7=> DIGITAL <= "1110000";WHEN 8=> DIGITAL <= "1111111";WHEN 9=> DIGITAL <= "1111011";WHEN 10=> DIGITAL <="1001111";END CASE;TIME1 <= T2;WHEN T2 =>CAT <= "110111";CASE CAT3 ISWHEN 0=> DIGITAL <= "1111110";WHEN 1=> DIGITAL <= "0110000";WHEN 2=> DIGITAL <= "1101101";WHEN 3=> DIGITAL <= "1111001";WHEN 4=> DIGITAL <= "0110011";WHEN 5=> DIGITAL <= "1011011";WHEN 6=> DIGITAL <= "1011111";WHEN 7=> DIGITAL <= "1110000";WHEN 8=> DIGITAL <= "1111111";WHEN 9=> DIGITAL <= "1111011";WHEN 10=> DIGITAL <="1000110";END CASE;TIME1 <= T3;WHEN T3 =>CAT <= "111011";CASE CAT2 ISWHEN 0=> DIGITAL <= "1111110";WHEN 1=> DIGITAL <= "0110000";WHEN 2=> DIGITAL <= "1101101";WHEN 3=> DIGITAL <= "1111001"; WHEN 4=> DIGITAL <= "0110011"; WHEN 5=> DIGITAL <= "1011011"; WHEN 6=> DIGITAL <= "1011111"; WHEN 7=> DIGITAL <= "1110000"; WHEN 8=> DIGITAL <= "1111111"; WHEN 9=> DIGITAL <= "1111011"; WHEN 10=> DIGITAL <="1000110"; END CASE;TIME1 <= T4;WHEN T4 =>CAT <= "111101";CASE CAT1 ISWHEN 0=> DIGITAL <= "1111110"; WHEN 1=> DIGITAL <= "0110000"; WHEN 2=> DIGITAL <= "1101101"; WHEN 3=> DIGITAL <= "1111001"; WHEN 4=> DIGITAL <= "0110011"; WHEN 5=> DIGITAL <= "1011011"; WHEN 6=> DIGITAL <= "1011111"; WHEN 7=> DIGITAL <= "1110000"; WHEN 8=> DIGITAL <= "1111111"; WHEN 9=> DIGITAL <= "1111011"; WHEN 10=> DIGITAL <= "1111110"; END CASE;TIME1 <= T5;WHEN T5 =>CAT <= "111110";CASE CAT0 ISWHEN 0=> DIGITAL <= "1111110"; WHEN 1=> DIGITAL <= "0110000"; WHEN 2=> DIGITAL <= "1101101"; WHEN 3=> DIGITAL <= "1111001"; WHEN 4=> DIGITAL <= "0110011"; WHEN 5=> DIGITAL <= "1011011"; WHEN 6=> DIGITAL <= "1011111"; WHEN 7=> DIGITAL <= "1110000"; WHEN 8=> DIGITAL <= "1111111"; WHEN 9=> DIGITAL <= "1111011"; WHEN 10=> DIGITAL <="1000110"; END CASE;TIME1 <= T1;WHEN OTHERS => TIME1 <= T1;END CASE;elsif(keep<0)thenCASE time1 ISWHEN t1 =>cat <= "101111";CASE cat4 ISWHEN 0=> digital <= "1111110";WHEN 1=> digital <= "0110000";WHEN 2=> digital <= "1101101";WHEN 3=> digital <= "1111001";WHEN 4=> digital <= "0110011";WHEN 5=> digital <= "1011011";WHEN 6=> digital <= "1011111";WHEN 7=> digital <= "1110000";WHEN 8=> digital <= "1111111";WHEN 9=> digital <= "1111011";WHEN 10=> DIGITAL <="1001111";END CASE;time1 <= t2;WHEN t2 =>cat <= "110111";CASE cat3 ISWHEN 0=> digital <= "1111110";WHEN 1=> digital <= "0110000";WHEN 2=> digital <= "1101101";WHEN 3=> digital <= "1111001";WHEN 4=> digital <= "0110011";WHEN 5=> digital <= "1011011";WHEN 6=> digital <= "1011111";WHEN 7=> digital <= "1110000";WHEN 8=> digital <= "1111111";WHEN 9=> digital <= "1111011";WHEN 10=> DIGITAL <="1000110";end case;time1 <= t3;WHEN t3 =>cat <= "111011";CASE cat2 ISWHEN 1=> digital <= "0110000"; WHEN 2=> digital <= "1101101"; WHEN 3=> digital <= "1111001"; WHEN 4=> digital <= "0110011"; WHEN 5=> digital <= "1011011"; WHEN 6=> digital <= "1011111"; WHEN 7=> digital <= "1110000"; WHEN 8=> digital <= "1111111"; WHEN 9=> digital <= "1111011"; WHEN 10=> DIGITAL <="1000110"; END CASE;time1 <= t4;WHEN t4 =>cat <= "111101";CASE cat1 ISWHEN 0=> digital <= "1111110"; WHEN 1=> digital <= "0110000"; WHEN 2=> digital <= "1101101"; WHEN 3=> digital <= "1111001"; WHEN 4=> digital <= "0110011"; WHEN 5=> digital <= "1011011"; WHEN 6=> digital <= "1011111"; WHEN 7=> digital <= "1110000"; WHEN 8=> digital <= "1111111"; WHEN 9=> digital <= "1111011"; WHEN 10=> DIGITAL <= "1111110"; END CASE;time1 <= t5;WHEN t5 =>cat <= "111110";CASE cat0 ISWHEN 0=> digital <= "1111110"; WHEN 1=> digital <= "0110000"; WHEN 2=> digital <= "1101101"; WHEN 3=> digital <= "1111001"; WHEN 4=> digital <= "0110011"; WHEN 5=> digital <= "1011011"; WHEN 6=> digital <= "1011111"; WHEN 7=> digital <= "1110000"; WHEN 8=> digital <= "1111111"; WHEN 9=> digital <= "1111011";END CASE;time1 <= t6;when t6=>cat<="011111";digital<="0000001";time1<=t1;WHEN OTHERS => time1 <= t1;END CASE;end if;--end if;--end process;--end lz;end if;end process;END behave;。

vhdl各种实验程序代码

1.三与门library ieee;use ieee.std_logic_1164.all;entity yumen isport(a,b,c : in std_logic;f : out std_logic);end yumen;architecture and3_1 of yumen isbeginf<=a and b and c;end architecture and3_1;2.三八译码器library ieee;use ieee.std_logic_1164.all;entity jg isport(a,b,c,g1,g2a,g2b:in std_logic;y:out std_logic_vector(7 downto 0));end entity jg;architecture rt1 of jg issignal indata:std_logic_vector(2 downto 0); beginindata<=c&b&a;process(indata,g1,g2a,g2b)isbeginif(g1='1' and g2a='0' and g2b='0')then case indata iswhen"000"=>y<="11111110"; when"001"=>y<="11111101"; when"010"=>y<="11111011"; when"011"=>y<="11110111"; when"100"=>y<="11101111"; when"101"=>y<="11011111"; when"110"=>y<="10111111"; when"111"=>y<="01111111";when others=>y<="xxxxxxxx";end case;elsey<="11111111";end if;end process;end rt1; 3.同步复位/置位、下降沿触发的d触发器ibrary ieee;use ieee.std_logic_1164.all;entity adff isport(clk,d,r,s:in std_logic;q:out std_logic);end adff;architecture rtl of adff issignal q_temp,qb_temp:std_logic;beginprocess(clk,r,s)beginif(clk'event and clk='0')thenif(r='0' and s='1')thenq_temp<='1';if(r='1' and s='0')thenq_temp<='0';elseq_temp<=d;end if;end if;end if;end process;q<=q_temp;end rtl;4.异步复位/置位、上升沿触发的d发器ibrary ieee;use ieee.std_logic_1164.all;entity adff isport(clk,d,r,s:in std_logic;q:out std_logic);end adff;architecture rtl of adff issignal q_temp,qb_temp:std_logic;beginprocess(clk,r,s)beginif(r='0' and s='1')thenq_temp<='1';elsif(r='1' and s='0')thenq_temp<='0';elsif(clk'event and clk='1')thenq_temp<=d;end if;end process;q<=q_temp;end rtl;5.四分频器ibrary ieee;use ieee.std_logic_1164.all;entity one isport( clk1:in std_logic;clk4:out std_logic);end one;architecture one1 of one issignal data1:integer range 0 to 10;signal q1:std_logic;beginprocess(clk1)beginif rising_edge(clk1) thenif(data1=1) thendata1<=0;q1<=not q1;elsedata1<=data1+1;end if;end if;clk4<=q1;end process;end architecture one1;6.四选一library ieee;use ieee.std_logic_1164.all;entity mux4 isport(input:in std_logic_vector(3 downto 0); a,b:in std_logic;y : out std_logic);end mux4 ;architecture rtl of mux4 issignal sel:std_logic_vector(1 downto 0); beginsel<=b & a;process (input,sel)beginif (sel="00") theny <= input(0);elsif (sel="01") theny <= input(1);elsif (sel="10") theny <= input(2);elsey <= input(3);end if;end process;end rtl; 7.五分频器use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fenpin5 isport (rst,clkin :in std_logic;clkout:out std_logic);end fenpin5;architecture rtl of fenpin5 issignal count1,count2: std_logic_vector(7 downto 0);signal tmp,tmp1,tmp2: std_logic;begintmp<=tmp1 and tmp2;clkout<=tmp xor tmp1;process(clkin,rst)beginif rst ='1'thencount1 <= "00000000";tmp1<= '0';elsif clkin'event and clkin='1' thenif count1 = "00000100" thencount1 <= "00000000";elsecount1 <= count1 + 1;if count1 < "00000010" thentmp1<= '0';elsetmp1<= '1';end if;end if;end if;end process;end rtl;8.moore状态机library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity moore isport (rst,clk,x:in std_logic; op:out std_logic);end moore;architecture a of moore is type state is (s0,s1,s2,s3); signal st: state;beginstate_comp: process(rst,clk) beginif rst='1' thenst <= s0;elsif rising_edge(clk) then case st iswhen s0 =>if x = '0' thenst <= s0;elsest <= s1;end if;op <= '1';when s1 =>if x = '0' thenst <= s3;elsest <= s2;end if;op <= '1';when s2=>if x = '0' thenst <= s2;elsest <= s3;end if;op <= '1';when s3=>if x = '0' thenst <= s3;elsest <= s0;end if;op <= '0';end case;end if; 9.mealy状态机library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity mealy isport (rst,clk,x:in std_logic; op:out std_logic);end mealy;architecture a of mealy istype state is (s0,s1,s2,s3); signal st : state;beginstate_comp: process(rst,clk) beginif rst='1' thenst <= s0;elsif rising_edge(clk) then case st iswhen s0 =>if x = '0' thenst <= s0; op <= '0';elsest <= s1; op <= '1';end if;when s1 =>if x = '0' thenst <= s3; op <= '1';elsest <= s2; op <= '1';end if;when s2 =>if x = '0' thenst <= s2; op <= '0';elsest <= s3; op <= '1';end if;when s3 =>if x = '0' thenst <= s3; op <= '0';elsest <= s0; op <= '0';end if;end case;end if;end process state_comp;end a10.全加器library ieee;use ieee.std_logic_1164.all;entity full_adder isport (a,b,cin:in std_logic;s,co:out std_logic);end full_adder;architecture full1 of full_adder issignal tmp1,tmp2,tmp3:std_logic;begintmp1 <= a xor b;tmp2 <= a and b;tmp3 <= tmp1 and cin;s <= tmp1 xor cin;co <= tmp2 or tmp3;end full1;11.同步12进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity count12en isport (clk,clr, en :in std_logic;qa,qb,qc,qd:out std_logic);end count12en;architecture rtl of count12en issignal count_4:std_logic_vector(3 downto 0); beginqa<=count_4(0);qb<=count_4(1);qc<=count_4(2);qd<=count_4(3);process (clr,clk)beginif(clr='1') thencount_4<="0000";elsif (clk'event and clk ='1') thenif(en='1') thenif (count_4="1011") thencount_4<="0000";elsecount_4<=count_4+'1';end if;end if;end if;end process;end rtl; 12.优先编码器library ieee;use ieee.std_logic_1164.all;entity priority_encoder isport(input:in std_logic_vector(7 downto 0); y : out std_logic_vector(2 downto 0));end priority_encoder;architecture rtl of priority_encoder is beginp1: process (input)beginif ( input(0) ='0') theny <= "111";elsif (input(1) ='0') theny <= "110";elsif (input(2) ='0') theny <= "101";elsif (input(3) ='0') theny <= "100";elsif (input(4) ='0') theny <= "011";elsif (input(5) ='0') theny <= "010";elsif (input(6) ='0') theny <= "001";elsey <= "000";end if;end process p1;end rtl;。

vhdl语言的除法用法 -回复

vhdl语言的除法用法-回复问题:VHDL语言的除法用法。

引言:VHDL(VHSIC Hardware Description Language)是一种用于描述和设计数字电路的硬件描述语言。

它允许工程师使用基于文本的编程语言来描述硬件系统的行为和结构。

VHDL提供了丰富的语法和功能,可以用于实现各种电路设计中的数学运算,包括除法运算。

在本文中,我们将详细介绍VHDL语言中除法的用法,并提供一步一步的指导。

一、VHDL除法运算的语法:在VHDL中,进行除法运算的语法是通过使用除法运算符“/”来实现的。

一般的除法运算形式为“被除数/ 除数= 商”,这是VHDL中执行除法运算的基础形式。

二、VHDL除法运算的数据类型:在VHDL中,除法运算可以在不同的数据类型之间进行。

常见的数据类型包括整型(integer)、浮点型(real)等。

三、VHDL除法运算的实例:为了更好地理解VHDL中除法运算的用法,我们来看一个简单的实例。

假设我们要计算两个32位无符号整数的除法运算。

首先,我们需要声明两个32位无符号整数类型的输入信号A和B,以及一个32位无符号整数类型的输出信号Q(商):signal A, B : unsigned(31 downto 0);signal Q : unsigned(31 downto 0);然后,我们可以通过使用VHDL的除法运算符“/”来进行除法运算:Q <= A / B;最后,我们需要在VHDL程序中引入相关的包(libraries):library ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;四、VHDL除法运算的注意事项:在进行VHDL除法运算时,我们需要注意以下几个要点。

1. 被除数和除数的类型必须匹配,即它们必须是相同的数据类型。

如果不匹配,我们需要进行类型转换操作。

2. 在进行整数类型的除法运算时,需要使用整数类型的除法运算符“/”。

verilog 补码定点数除法

verilog 补码定点数除法

Verilog是一种硬件描述语言,用于描述数字电路。

补码定点

数除法是数字电路中常见的运算,可以通过Verilog来实现。

在Verilog中,补码定点数除法可以通过多种方法来实现,其

中一种常见的方法是使用移位和减法来模拟除法运算。

下面我将从

多个角度来讨论如何在Verilog中实现补码定点数除法。

首先,补码定点数除法的基本原理是将被除数和除数转换为补

码表示,然后进行除法运算,最后根据需要进行舍入或截断操作。

在Verilog中,我们可以使用模块化的方式来实现补码定点数除法,将整个除法过程分解为多个子模块,分别实现补码转换、除法运算、舍入和截断等操作。

其次,补码定点数除法的关键在于如何进行除法运算。

在

Verilog中,我们可以使用循环或者递归的方式来实现除法运算,

通过多次减法和移位来逼近商。

同时,我们还需要考虑除数为0的

情况,需要在Verilog代码中添加相应的异常处理逻辑。

另外,在Verilog中实现补码定点数除法时,还需要考虑到数

据宽度、符号位处理、溢出和舍入等问题。

我们需要根据具体的需求来设计合适的Verilog代码,确保实现的除法运算能够满足设计要求。

总的来说,补码定点数除法在Verilog中的实现涉及到补码转换、除法运算、舍入和截断等多个方面,需要综合考虑数据表示、运算精度和性能等因素。

在实际设计中,需要根据具体的应用场景和需求来选择合适的实现方法,保证Verilog代码能够正确、高效地实现补码定点数除法运算。