ModelSim使用的一点心得体会

ModelSim使用的一点心得- -

ModelSim使用的一点心得- -1、至今还没有弄明白为什么要用ModelSim,因为看波形Quartus II自带的工具就可以了啊。

2、我刚刚接触modelsim,我想大多数菜鸟跟我一样,看过如何使用ModelSim的介绍,说句实话,那些介绍写的都太过简单,仿佛大家都不屑写上一些比较“弱智”的步骤,恰恰就是这些看似累赘的步走,难为我好久。

教程上都写道,modelsim的简单使用方法如下:建立库- 影射库到物理目录- 编译代码- 启动仿真。

首先建立库就叫我头晕。

库的概念用在这儿实在不合适,把我吓坏了,也就没心思看下一步了。

在我看来,教程应该这么写:<1> 建立一个目录modelsimStudy。

用任何文本编辑器编辑一个简单的例子程序,比如计数器counter.vhd。

有clk、ena、reset输入,cnt作为输出。

<2> 打开Modelsim,首先create project,工程名随意取了,比如命名为test,目录设在modelsimStudy下,默认的库work不变(这样就不用管什么建立库之类的东西了)。

然后add existing file,把counter.vhd加入当前工程。

<3> 编译这个文件,通过之后,work下面会出现counter这个实体。

然后选中它,右键,simulate(左键双击也可)。

<4> ModelSim有很多窗口(新手就怕这个),一开始只要选择view下面的objects 和wave窗口就行了。

旧版的signal窗口在6.0的版本改名为Objects(这个我是摸索了好久才发现的,是不是太笨了?)。

wave窗口刚打开时是空的,需要在objects窗口的add -> wave -> signals in region。

这时,wave上就有clk\ ena \ reset等信号了。

<5> 我们给clk来个输入激励,在object窗口中选中clk,右键选clock,给它定义个时钟。

matlab学习心得体会(精选18篇)

matlab学习心得体会(精选18篇)matlab学习篇1matlab中有丰富的图形处理能力,提供了绘制各种图形、图像数据的函数。

他提供了一组绘制二维和三维曲线的函数,他们还可以对图形进行旋转、缩放等操作。

matlab内部还包含丰富的数学函数和数据类型,使用方便且功能非常强大。

本学期通过对matlab的系统环境,数据的各种运算,矩阵的分析和处理,程序设计,绘图,数值计算及符号运算的学习,初步掌握了matlab的实用方法。

通过理论课的讲解与实验课的操作,使我在短时间内学会使用matlab,同时,通过上机实验,对理论知识的复习巩固实践,可以自己根据例题编写设计简单的程序来实现不同的功能,绘制出比较满意的二维三维图形,在实践中找到乐趣。

matlab是一个实用性很强,操作相对容易,比较完善的工具软件,使用起来比较方便,通过操作可以很快看到结果,能够清晰的感觉到成功与失败,虽然课程中也会出现一些小问题,但是很喜欢这门课程。

matlab学习心得体会篇2MATLAB中有丰富的图形处理能力,提供了绘制各种图形、图像数据的函数。

他提供了一组绘制二维和三维曲线的函数,他们还可以对图形进行旋转、缩放等操作。

MATLAB内部还包含丰富的数学函数和数据类型,使用方便且功能非常强大。

本学期通过对MATLAB的系统环境,数据的各种运算,矩阵的分析和处理,程序设计,绘图,数值计算及符号运算的学习,初步掌握了MATLAB的实用方法。

通过理论课的讲解与实验课的操作,使我在短时间内学会使用MATLAB,同时,通过上机实验,对理论知识的复习巩固实践,可以自己根据例题编写设计简单的程序来实现不同的功能,绘制出比较满意的二维三维图形,在实践中找到乐趣。

MATLAB是一个实用性很强,操作相对容易,比较完善的工具软件,使用起来比较方便,通过操作可以很快看到结果,能够清晰的感觉到成功与失败,虽然课程中也会出现一些小问题,但是很喜欢这门课程。

matlab学习心得体会篇3这是我在学习的过程中的一些技巧,或许对你有帮助,可能字数不你能满足你的要求,但是绝对是精华。

modelsim调试技巧

modelsim调试技巧ModelSim是一款流行的电子设计自动化(EDA)工具,广泛应用于集成电路、通信系统和消费电子产品的仿真和调试。

本文将介绍ModelSim的一些调试技巧,帮助您更高效地进行仿真和调试。

一、设置仿真环境1. 启动ModelSim,创建一个新的工程或打开已有的工程。

2. 配置仿真参数,如仿真时钟频率、时序约束等。

3. 编写测试向量或测试脚本,用于验证设计的正确性。

二、常用调试技巧1. 实时监测:在仿真过程中,可以使用实时监测功能来观察仿真波形,以便快速发现设计中的问题。

可以使用“实时监测”工具栏中的相关按钮或命令。

2. 断点设置:在需要调试的代码行设置断点,以便在运行到该行时暂停仿真,从而方便查看该行执行前后的变量值和状态。

可以使用“断点”工具栏中的相关按钮或命令来设置断点。

3. 变量观察:在仿真过程中,可以使用“变量观察”功能来观察设计中的变量值。

可以在仿真波形窗口中双击需要观察的变量,将其添加到“变量观察”列表中。

4. 波形分析:ModelSim提供了强大的波形分析功能,可以帮助您分析仿真波形的异常情况,如信号过冲、下冲等。

可以使用“波形分析”工具栏中的相关按钮或命令来进行波形分析。

5. 脚本调试:如果您的测试脚本中有错误,可以使用ModelSim 的脚本调试功能来逐行执行脚本,并查看每行执行前后的变量值和状态,以便找到错误位置。

可以使用“脚本调试”工具栏中的相关按钮或命令来进行脚本调试。

三、高级调试技巧1. 仿真结果分析:通过分析仿真结果,可以发现设计中的潜在问题。

可以使用ModelSim提供的各种分析工具和报告功能,如时序分析、功耗分析等,来帮助您更好地理解仿真结果。

2. 多平台仿真:ModelSim支持与Xilinx、Intel等厂商的多种硬件平台进行联合仿真,以便更好地验证设计的兼容性和可靠性。

通过多平台仿真,您可以更快地发现设计中的潜在问题。

3. 自动测试生成:ModelSim提供了自动测试生成功能,可以根据设计的结构和行为自动生成测试向量或测试脚本。

一个Modelsim的demo,给你启示

写在前面的话学过MCU设计的朋友都知道,系统调试是多么的重要。

而对于FPGA设计来说,仿真确实最重要的。

一个完整的项目,必须有完整的仿真平台。

有朋友说,按键仿真模型没法搞。

我只能说,你并不了解硬件及处理按键的工作原理,如果你知道。

按键仿真模型很容就可以做开始学习VERIlOG HDL的朋友是不是很乏味,因为不知道课文中的代码是否正常工作,实际工作会是怎么样子的。

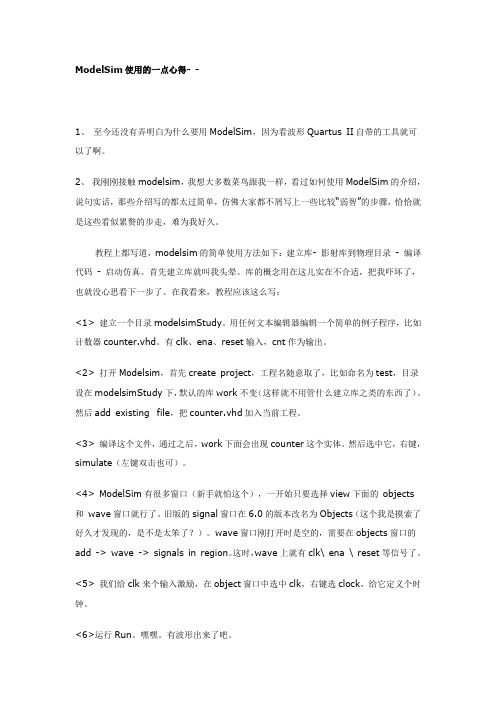

今天给大家讲解的是一个Modelsim仿真的DEMO这里开始吧设计中包含3个文件:1.工程设计文件(可综合执行成硬件电路文件):demo_test.v2.仿真平台文件(不可综合执行成硬件电路文件):testbench_demo_test.sv (这里的文件后缀可以是.v)3.Modelsim执行脚本文件:run.do各文件代码如下图:图1图2图3其中图1为demo_test.v图2为testbench_demo_test.sv图3为run.do启动仿真平台A. 把三个文件放置到同一个目录下,该目录的路径必须是纯英文或有短下划线(关于这点自己注意),B. 启动Modelsim;C. 制定Modelsim的直接目录,File -> Change Directory. 指定到A指向的目录。

D.在Transcript框中输入:do run.do 回车E.等待波形结果.在熟悉"启动仿真平台"后,F.开始分析代码,这个自己把握。

接下来G1或者G2G1.分析脚本文件run.do. 查看"启动仿真平台"A指向目录产生的文件或文件夹,简单了解脚本实现方式.G2.在代码相应位置输入课文中的一些例子。

再次启动仿真平台H.进入高级设计阶段。

常见问题一个必须要提醒的问题:经常听到有人问这么一个问题,而且有时还碰到一些工作一年的朋友也问:为什么我的信号一直是高阻状态?对于仿真而言,所有信号如何没有赋值,软件认为该信号就为高阻状态,比如以下代码initial beignforever #10 clk = ~clk;end设计者意图很明显:生成一个周期为20个刻度的时钟。

modelsim的理解

Modelsim 仿真软件的学习及理解一软件简介Modelsim仿真工具支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化,具备强大的模拟仿真功能,在设计、编译、仿真、测试、调试开发过程中,有一整套工具供你使用,而且操作起来极其灵活,可以通过菜单、快捷键和命令行的方式进行工作。

ModelSim的窗口管理界面让用户使用起来很方面,它能很好的与操作系统环境协调工作。

ModelSim 的一个很显著的特点就是它具备命令行的操作方式。

二功能介绍Modelsim的主要功能包括:对设计文件的设计、编译和仿真。

设计文件的设计:在Modelsim软件打开之后,在把库和工程建立好的前提下,编译设计文件,编译设计文件时遵循verilog的编程规则,语法方面注意关键字的用法,编译设计文件包括两个部分:设计文件源代码的编译和测试代码的编译,测试代码编写时注意函数的调用,尤其是端口的对应,包括名称对应和位置对应,同时还应该注意激励信号的设定,此时应该注意时钟的延时是否是惯性延时。

文件的编译:文件的编译的主要目的是:检查程序语言的语法错误,在编译过程中可以通过两种方法实现:工具按钮的编译法和指令输入的编译法,工具按钮编译法适合于初学者,而指令输入法适合于编程经验较足的编程人员。

编译的过程也就是第一轮检查程序代码的过程,通过编译,软件会以指令的形式在输出脚本框中显示出来,通过显示的错误信息,编程人员会再较短的时间内找处错误代码,及时修改,提高了编程的效率和准确性。

文件的仿真:文件的仿真即就是在写好的源代码和测试代码的基础上,给程序一定的激励信号,在激励信号的基础上观察源代码波形图的变化,是否符合设计初衷,是否满足设计的时序逻辑和组合逻辑的要求。

MatLab实习心得体会2篇

MatLab实习心得体会 (3)MatLab实习心得体会 (3)精选2篇(一)在进行MatLab实习的过程中,我学到了很多关于MatLab的知识和技巧,也锻炼了自己的解决问题的能力。

以下是我在实习过程中的一些心得体会:1. 熟练掌握基本语法:MatLab有很多基本的函数和语法,熟练掌握这些基本知识对于编写代码至关重要。

在实习过程中,我花了很多时间学习和练习MatLab的基本语法,以确保我能够正确地使用各种函数和语句。

2. 学会使用文档和资源:MatLab有非常丰富的文档和资源库,可以帮助我们快速解决问题。

在实习过程中,我学会了如何使用MatLab的文档和资源库,并从中获取并应用相关知识。

3. 编写模块化的代码:编写模块化的代码可以使代码更加清晰和可读,也方便后续的调试和维护。

在实习过程中,我尽量将代码分解为不同的功能模块,并使用函数和脚本文件将它们组织起来。

4. 遇到问题要善于查找解决方案:在实习过程中,我遇到了很多问题,有些问题在课堂上并没有涉及到。

在解决这些问题的过程中,我学会了如何善用搜索引擎和MatLab 的社区论坛,通过查找解决方案,我能够更快地解决问题。

5. 多做实践练习:实践是学习MatLab最有效的方法之一。

在实习过程中,我尽量多做一些实践练习,通过实际操作来加深对MatLab的理解和掌握。

总的来说,MatLab实习不仅让我学到了很多关于MatLab的知识和技巧,也使我对编程和问题解决能力有了更深入的认识和提高。

通过实习,我能够更加独立地解决问题,并且对MatLab的应用范围也有了更清晰的认识。

MatLab实习心得体会 (3)精选2篇(二)在MatLab实习期间,我学到了很多关于编程和数据分析方面的知识和技能。

通过实践操作和与同事的合作,我更深入地理解了MatLab的各种功能和用法。

首先,我学会了如何使用MatLab进行数据处理和分析。

我学习了如何导入、清洗和处理数据,以及如何应用不同的统计分析方法来解读数据。

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。

为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。

一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。

首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSim后仿真的问题,那就可能是软件版本的问题。

1, ModelSim Se 6.1b2, Synplify Pro 7.5.13, ISE 5.2i (这个是老了点)4, WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

我的邮箱是****************。

有空大家多交流。

一、为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

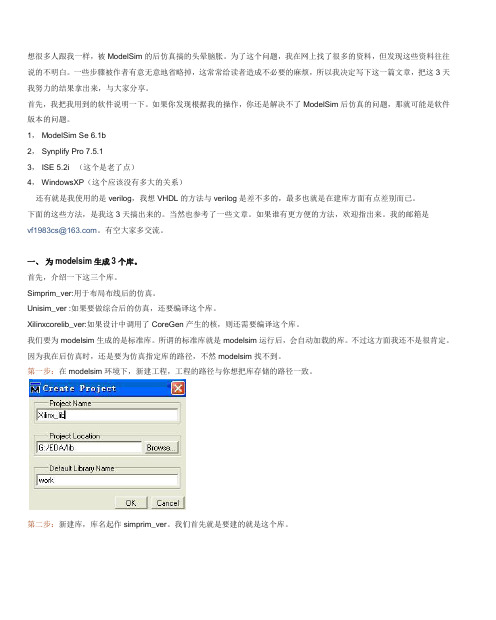

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

Modelsim仿真流程-经验总结

Modelsim仿真流程-经验总结1.Modelsim简介略。

2.modelsim仿真流程:modelsim基本的仿真流程包括建立库、建立工程并编译、仿真、调试、但在libero环境中运行modelsim时,软件自动映射库和生成工程文件。

其中功能仿真、综合仿真以及后仿真分别映射presynth、postsynth和postlayout库。

基本流程是:建立工作库→编译源代码→启动仿真→分析、调试。

2.1建立库并映射在modelsim中,任何使用VHDL、Verilog HDL、SystemC等语言实现的设计,都被编译到一个库中。

♥方法一:File>New>Library选择新建并映射到该库;♥方法二:在modelsim>提示符下运行命令vlib work2-建立库,vmap work work2-建立映射库;2.2建立工程Modelsim仿真需要建立自己的工程,同时modelsim还提供了文件夹管理工程的功能。

♥step1:File>New>project,并指定库文件名;♥step2:新建文件或导入文件;2.3编译文件建立好工程后,使用compile功能对源文件进行编译。

Libero环境启动modelsim时,系统执行run.do脚本文件自动编译源文件。

♥鼠标右击文件,选择compile All对所有的工程文件执行编译操作;♥启动仿真,使用simulation>start simulation>选择design选项卡功能使modelsim进入仿真状态,之后可以运行仿真。

在libero环境下,运行modelsim直接从运行仿真这一步骤开始。

♥运行仿真可以设置仿真时间或选择仿真全部♥tcl命令:do run.do –当设计修改后,使用此命令重新导入设计;Do wave.do-打开波形列表文件,或者向当前波形添加列表;Restart-复位当前仿真,从0时刻重新仿真;Run 1ms-运行仿真1ms时间;Run all-运行全部的仿真;在libero环境下,可以自己编写脚本文件代替run.do文件,在项目比较大的情况下可以大大简化仿真的操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ModelSim使用的一点心得- -1、至今还没有弄明白为什么要用ModelSim,因为看波形Quartus II自带的工具就可以了啊。

2、我刚刚接触modelsim,我想大多数菜鸟跟我一样,看过如何使用ModelSim的介绍,说句实话,那些介绍写的都太过简单,仿佛大家都不屑写上一些比较“弱智”的步骤,恰恰就是这些看似累赘的步走,难为我好久。

教程上都写道,modelsim的简单使用方法如下:建立库- 影射库到物理目录- 编译代码- 启动仿真。

首先建立库就叫我头晕。

库的概念用在这儿实在不合适,把我吓坏了,也就没心思看下一步了。

在我看来,教程应该这么写:<1> 建立一个目录modelsimStudy。

用任何文本编辑器编辑一个简单的例子程序,比如计数器counter.vhd。

有clk、ena、reset输入,cnt作为输出。

<2> 打开Modelsim,首先create project,工程名随意取了,比如命名为test,目录设在modelsimStudy下,默认的库work不变(这样就不用管什么建立库之类的东西了)。

然后add existing file,把counter.vhd加入当前工程。

<3> 编译这个文件,通过之后,work下面会出现counter这个实体。

然后选中它,右键,simulate(左键双击也可)。

<4> ModelSim有很多窗口(新手就怕这个),一开始只要选择view下面的objects 和wave窗口就行了。

旧版的signal窗口在6.0的版本改名为Objects(这个我是摸索了好久才发现的,是不是太笨了?)。

wave窗口刚打开时是空的,需要在objects窗口的add -> wave -> signals in region。

这时,wave上就有clk\ ena \ reset等信号了。

<5> 我们给clk来个输入激励,在object窗口中选中clk,右键选clock,给它定义个时钟。

<6>运行Run。

嘿嘿。

有波形出来了吧。

3、2中的例子绝对适合刚刚接触modelsim的新手,有了这个体会之后,结合书上的教程,理解库以及modelsim的各个窗口用途就比较容易了。

然后再尝试结合Quartus使用。

4、Quartus中,选中modelsim作为仿真工具之后,在Quartus目录下会生成一个si mulation文件夹,下面有个modelsim。

完成编译之后,在这个目录下面生成了供mode lsim使用的库和时序文件。

如果选中了编译之后自动调用modelsim,我的做法是用Qua rtus编辑波形文件,然后导出作为激励文件。

或者,自行打开modelsim,然后选择改变目录,把目录指向Quartus生成的modelsim目录。

新建工程,把Quartus下的vhdl以及激励文件添加进来,进行仿真。

5、Modelsim仿真cyclone PLL的问题。

我也遇到过,出现什么fatal error。

解决方法:** Simulation property -> Design Tab -> Resolution 应该设为pssimulation -> start simulation -> Design , 那个resolution非常不显眼,认真找,它的默认值是default,改为ps就行了。

ps:Quartus中把不用的管脚设成高阻态:assignment -> device -> pin&device里面设置。

ModelSim的简要使用方法在这一章里通过一些课程来简单介绍ModelSim的使用方法,更多的需要在实际应用中熟练和掌握。

第一课 Create a Project第一次打开ModelSim会出现Welcome to ModelSim对话框,选取Create a 1. Project,或者选取File\New\Project,然后会打开Create Project对话框。

2.在Create Project对话框中,填写test作为Project Name;选取路径Project Location作为Project文件的存储目录;保留Default Library N ame设置为work。

3.选取OK,会看到工作区出现Project and Library Tab。

4.下一步是添加包含设计单元的文件,在工作区的Project page中,点击鼠标右键,选取Add File to Project。

5.在这次练习中我们加两个文件,点击Add File to Project对话框中的Browse按钮,打开ModelSim安装路径中的example目录,选取counter.v 和tcounter.v,再选取Reference from current location,然后点击OK。

6.在工作区的Project page中,单击右键,选取Compile All。

7.两个文件编译了,鼠标点击Library Tab栏,将会看到两个编译了的设计单元列了出来。

看不到就要把Library的工作域设为work。

8.最后一不是导入一个设计单元,双击Library Tab中的counter,将会出现Sim Tab,其中显示了counter设计单元的结构。

也可以Design\Load desi gn来导入设计。

到这一步通常就开始运行仿真和分析,以及调试设计,不过这些工作在以后的课程中来完成。

结束仿真选取Design \ End Simulation,结束Project选取File \ Close \ Project。

第三课 Basic verilog Simulation1.新建一个目录,并设置该目录为当前工作目录,通过从该目录调用Mode lSim或是选取File\Change Directory命令来完成。

2.拷贝example目录中verilog文件到当前目录下。

在你编译verilog文件前,你需要在新目录下生成一个设计库。

如果你仅仅熟悉解释性verilog仿真器,诸如Cadence Verilog-XL,那么对于你来说这是一个新的方法。

因为Mod elSim是一个编译性Verilog仿真器,对于编译它需要一个目标设计库。

如果需要的话,ModelSim能够编译VHDL和Verilog代码到同一个库中。

3.在编译任何HDL代码前,要建立一个设计库来存放编译结果。

选取Desi gn \ Create a New Library生成一个新的设计库。

确定选取Create: a new l ibrary and a logical mapping to it,在Library Name域中键入work,然后选取OK。

这就在当前目录中建立了一个子目录,即你的设计库。

ModelSim在这个目录中保存了名为_info的特殊文件。

4.下面你将编译Verilog设计。

这个设计例子由两个Verilog源文件组成,每一个都包含一个唯一的模块。

文件counter.v包含一个名为counter的模块,它执行一个简单的八位加法计数器。

另一个文件tcounter.v是一个测试台模块(test_counter),通常用来校验c ounter。

在仿真下,你可以看到这两个文件,通过一个被测试台例示了的模块c ounter的一个简单的实例(名为dut的实例),来层次化的设置了。

稍候你将有机会看一下这个代码的结构,现在,你需要编译两个文件到work设计库。

5.通过选取工具条中的Compile按钮来编译两个文件。

( PROMPT : vlog counter.v tcounter.v )这就打开了Compile HDL Source Files对话框。

选取两个文件后,选择Compile,编译完成后选取Done。

6.选取工具条中的Load Design按钮开始仿真。

( PROMPT : vsim test_counter )Load Design对话框允许你从指定的库中选取一个设计单元仿真。

你也可以为仿真选取Simulation Resolution限制,缺省的库是work,缺省的Simu lation Resolution是1ns。

7.选取test_counter,点击Load接受这些设置。

8.通过在主窗口下的vsim提示符下敲入下述命令来调出Signals、List a nd Wave window: view signals list wave (MENU: View\1.为了列示顶级( top-level )信号,移动鼠标到Signals window,选取V iew\List\Signals in Region。

( Prompt : add list /test_counter/* )2.现在向Wave window添加信号。

在Signals window选取Edit\Select A ll选择三个信号,拖动三个信号到Wave window的路径名或是数值窗格的任一个中。

HDL条目也能够从一个窗口拷贝到另一个窗口(或者是在Wave and List windo w内部),通过Edit \ Copy和Edit \ Paste菜单命令。

也能删除选取的条目Edit \ Delete。

3.下面打开Source window,选取View \ Source( Prompt : view source )4.导入设计的时候会在工作去开出一个新的Sim Tab栏。

这个Structure Pane展示了设计的层次结构。

你可以点即“+”(expand)或“-”(contract)来观察。

5.点击其中的Function increment可以注意到其他窗口是怎么适当的自动更新的。

明确地说,Source window显示了你在Structure window所选的层次水平的Verilog代码.在这种方式下使用Structure Pane类似于解释性Verilo g的范围命令。

现在,点击Structure Pane的顶层线,确定test_counter模块显示在Source window。

1.Run运行100ns,缺省设置。

(PROMPT: run ) (MENU: Run\Run 100ns)2.设置Run Length为500ns,然后Run。

在仿真运行了600ns,在工作取底部状态栏可以看到这些信息。

3.上个命令使仿真器前进了500ns,也可以设置仿真器推进的时间run @ 3000际仿真器向前推进了2400ns(3000-600)4.选取主窗口Run All。

(PROMPT: run -all ) (MENU: Run\Run -All)5.选取Break中断运行。