ModelSim_使用(原创)

ModelSim安装与使用

主要内容

ModelSim 10.2c安装方法 ModelSim 10.2c使用简介

MODELSIM安装方法

1. 准备ModelSim安装文件:

请注意对应32bit与64bit系统.

MODELSIM安装方法

2. 以32bit系统为例, 运行ModelSim安装 文件:

THANKS!

MODELSIM使用简介

• 将rtl与testbench放置到project目录中:

MODELSIM使用简介

• 在ModelSim中建立project:

– File -> New -> Project, 并输入project名字与之前保存RTL与TB 的路径

MODELSIM使用简介

加入已有的RTL与TB文件

MODELSIM使用简介

点击View -> Wave打开波形窗口

MODELSIM使用简介

在Object窗口中选中所需的信号,右击选择 Add Wave加入:

MODELSIM使用简介

点击Simulate -> Run -> Run All, 并查看 波形

也可选择其他run选项,下方Transcript中可看到仿真输出结果

6. 按个人喜好选择是否创建桌面图标:

MODELSIM安装方法

7. 点击 Yes 将ModelSim可执行文件加入环 境变量PATH之中,以便通过直接命令行调用:

MODELSIM安装方法

8. 点击 No ,不安装安全密钥(加密狗)驱动:

MODELSIM安装方法

9. 点击 Done 完成安装向导:

MODELSIM使用简介

Project窗口右击加入的文件:

Modelsim使用说明

Modelsim 使用简明指南1 前言作为一种简单易用,功能强大的逻辑仿真工具,Modelsim 具有广泛的应用。

这里对ModelSim 作一个入门性的简单介绍。

首先介绍ModelSim 的代码仿真,然后介绍门级仿真和时序验证。

和时序验证。

2 代码仿真在完成一个设计的代码编写工作之后,可以直接对代码进行仿真,检测源代码是否符合功能要求。

这时,仿真的对象为HDL 代码,比较直观,速度比较快,可以进行与软件相类似的多种手段的调试(如单步执行等)。

在设计的最初阶段发现问题,在设计的最初阶段发现问题,可以节省大量的精力。

可以节省大量的精力。

2.1 代码仿真需要的文件1.设计HDL 源代码:源代码:新建一个“文本文档”文件,在记事本中输入HDL 源代码,使用V erilog 语言编程。

语言编程。

2.测试激励代码:.测试激励代码:在同一个文件中,根据设计要求输入/输出的激励程序,由于不需要进行综合,书写具有很大的灵活性。

有很大的灵活性。

3.保存该文件后退出,然后重命名该文件,.保存该文件后退出,然后重命名该文件,使该文件后缀名由使该文件后缀名由.txt 变为.v 。

如:t81.v 。

4. 该文件保存在你所建立的工作目录中,如:D\VLSItext\t1如果要修改该文件,仍然可以选择用仍然可以选择用记事本记事本打开编辑再保存,记事本相当于是一源代码输入软件。

输入软件。

注:所有的文件名及目录名均要求是英文,无中文字符。

2.2 代码仿真步骤1.建立工程:在ModelSim 中建立Project 。

如图2.1所示,点击File ðNew ðProject ,得到Creata Project 的弹出窗口,如图2.2所示。

在Project Name 栏中填写你的项目名字,建议和你的顶层文件名字一致,如t81。

Project Location 是你的项目目录,你可通过Brose 按钮来选择或改变,建议项目目录选择为你所保存源代码的目录,如:D\VLSItext\t1。

Modelsim_6.0_使用教程

Modelsim 6.0 使用教程1. Modelsim简介Modelsim仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。

但是它也有缺点,就是它里面所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到modelsim就可以用,它假设使用者对当前操作的前期准备工作都已经很熟悉,所以初学者往往不知道如何做当前操作的前期准备。

2. 安装同许多其他软件一样,Modelsim SE同样需要合法的License,通常我们用Kengen产生license.dat。

⑴.解压安装工具包开始安装,安装时选择Full product安装。

当出现Install Hardware SecurityKey Driver时选择否。

当出现Add Modelsim To Path选择是。

出现Modelsim License Wizard时选择Close。

⑵.在C盘根目录新建一个文件夹flexlm,用Keygen产生一个License.dat,然后复制到该文件夹下。

⑶.修改系统的环境变量。

右键点击桌面我的电脑图标,属性->高级->环境变量->(系统变量)新建。

按下图所示内容填写,变量值内如果已经有别的路径了,请用“;”将其与要填的路径分开。

LM_LICENSE_FILE = c:\flexlm\license.dat⑷.安装完毕,可以运行。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

modelsim使用技巧

modelsim使用技巧ModelSim是一款常用的仿真工具,用于学习、开发和测试各种数字电路和系统设计。

它提供了大量的功能,可以帮助我们更好地进行仿真、调试和性能优化。

但是,对于初学者来说,熟练使用ModelSim可能需要一些时间和实践。

在本文中,我们将介绍一些ModelSim的使用技巧,以帮助读者更好地掌握这个工具。

一、基本操作1.创建工程在ModelSim中,创建工程是第一步。

可以通过File -> New -> Project来创建一个新的工程。

在工程创建过程中,需要指定工作目录、项目名称和工具链等信息。

在创建工程后,可以右键单击仿真文件夹,并选择添加到工程来添加设计文件。

2.添加仿真文件在ModelSim中,添加仿真文件非常简单。

可以将文件拖放到仿真文件夹、使用File -> Add to Project选项或使用命令行方式添加文件。

一旦添加了仿真文件,可以使用filelist命令查看所有添加的文件。

3.编译设计在ModelSim中,编译由两个阶段组成。

第一阶段称为分析阶段,在此阶段中,设计的各个模块被分析、组合并建立数据结构。

第二阶段称为综合阶段,在此阶段中,数据结构被综合成一个整体,并生成仿真网表。

可以通过compile option来指定编译选项,比如-v库等。

4.运行仿真在ModelSim中,可以通过三种方式来运行仿真。

第一种是在命令行中使用run命令,第二种是通过菜单和工具栏选项来启动仿真,第三种是使用脚本方式启动仿真。

在仿真过程中,可以使用wave、add wave、force、release等命令来控制信号的行为。

二、ModelSim高级技巧1.波形窗口波形窗口是ModelSim中最有用的窗口之一。

可以使用Add Wave按钮打开该窗口。

在波形窗口中,可以查看所有信号的变化情况。

可以使用full view、zoom in、zoom out等选项来放大或缩小波形窗口。

modelsim详细使用教程(一看就会)

Modelsim详细使用方法很多的modelsim教程中都讲得很丰富,但忽视了对整个仿真过程的清晰解读,而且都是拿counter范例举例子,有些小白就不会迁移了。

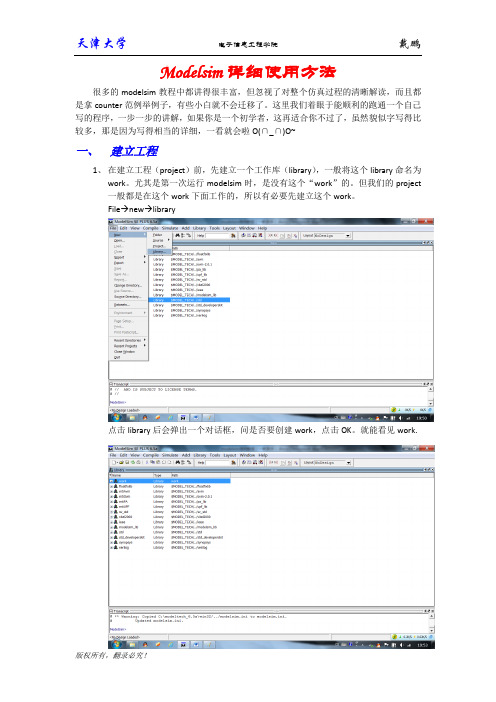

这里我们着眼于能顺利的跑通一个自己写的程序,一步一步的讲解,如果你是一个初学者,这再适合你不过了,虽然貌似字写得比较多,那是因为写得相当的详细,一看就会啦O(∩_∩)O~一、建立工程1、在建立工程(project)前,先建立一个工作库(library),一般将这个library命名为work。

尤其是第一次运行modelsim时,是没有这个“work”的。

但我们的project 一般都是在这个work下面工作的,所以有必要先建立这个work。

File→new→library点击library后会弹出一个对话框,问是否要创建work,点击OK。

就能看见work.2、如果在library中有work,就不必执行上一步骤了,直接新建工程。

File→new→project会弹出在Project Name中写入工程的名字,这里我们写一个二分频器,所以命名half_clk,然后点击OK。

会出现由于我们是要仿一个自己写的程序,所以这里我们选择Create New File。

在File Name中写入文件名(这里的file name和刚刚建立的project name可以一致也可以不一致)。

注意Add file as type 要选择成Verilog(默认的是VHDL),然后OK。

发现屏幕中间的那个对话框没有自己消失,我们需要手动关闭它,点close。

并且在project中出现了一个half_clk.V的文件,这个就是我们刚刚新建的那个file。

这样工程就建立完毕了。

二、写代码:1、写主程序:双击half_clk.v文件会出现程序编辑区,在这个区间里写好自己的程序,这里我们写一个简单的二分频的代码:module half_clk_dai(clk_in,rst,clk_out);input clk_in;input rst;output clk_out;reg clk_out;always @(posedge clk_in or negedge rst)beginif(!rst)clk_out<=0;elseclk_out<=~clk_out;endendmodule写完代码后,不能马上就编译,要先保存,否则,编译无效。

modelsim的详细使用方法

一、简介ModelSim是一款由美国Mentor Graphics公司推出的集成电路仿真软件,广泛应用于数字电路和系统设计领域。

它提供了强大的仿真和验证功能,能够帮助工程师快速高效地进行电路设计与验证工作。

本文将详细介绍ModelSim的使用方法,以帮助读者更好地掌握这一工具的操作技巧。

二、安装与配置1. 下载ModelSim安装包,并解压到指定目录2. 打开终端,进入ModelSim安装目录,执行安装命令3. 安装完成后,配置环境变量,以便在任何目录下都能够调用ModelSim程序4. 打开ModelSim,进行软件注册和授权,确保软件可以正常运行三、工程创建与管理1. 新建工程:在ModelSim主界面点击“File” -> “New” -> “Project”,输入工程名称和存储路径,选择工程类型和目标设备,点击“OK”完成工程创建2. 添加文件:在工程目录下右键点击“Add Existing”,选择要添加的源文件,点击“OK”完成文件添加3. 管理工程:在ModelSim中可以方便地对工程进行管理,包括文件的增删改查以及工程参数的设置等四、代码编写与编辑1. 在ModelSim中支持Verilog、VHDL等多种硬件描述语言的编写和编辑2. 在ModelSim主界面点击“File” -> “New” -> “File”,选择要新建的文件类型和存储位置,输入文件名称,点击“OK”完成文件创建3. 在编辑器中进行代码编写,支持代码高亮、自动缩进、语法检查等功能4. 保存代码并进行语法检查,确保代码符合规范,没有错误五、仿真与调试1. 编译工程:在ModelSim中进行代码编译,生成仿真所需的可执行文件2. 设置仿真参数:在“Simulation”菜单下选择“S tart Simulation”,设置仿真时钟周期、输入信号等参数3. 运行仿真:点击“Run”按钮,ModelSim将开始对设计进行仿真,同时显示波形图和仿真结果4. 调试设计:在仿真过程中,可以通过波形图和仿真控制面板对设计进行调试,查找并解决可能存在的逻辑错误六、波形查看与分析1. 查看波形:在仿真过程中,ModelSim会生成相应的波形文件,用户可以通过“Wave”菜单查看波形并进行波形分析2. 波形操作:支持波形的放大、缩小、平移、选中等操作,方便用户对波形进行分析和观察3. 波形保存:用户可以将波形结果保存为图片或文本文件,以便日后查阅和分析七、性能优化与验证1. 时序优化:在设计仿真过程中,可以通过观察波形和性能分析结果,对设计进行优化,提高设计的时序性能2. 逻辑验证:通过对仿真的结果进行逻辑验证,确保设计符合预期的逻辑功能3. 时序验证:对设计的时序性能进行验证,确保信号传输和时钟同步的正确性八、项目输出与文档整理1. 输出结果:在仿真和验证完成后,可以将仿真结果、波形图和性能分析结果输出为文本文件或图片,方便后续的文档整理和报告撰写2. 结果分析:对仿真结果和验证结果进行详细的分析,确定设计的性能和功能是否符合设计要求3. 文档整理:根据仿真和验证结果,进行文档整理和报告撰写,为后续的设计和优化工作提供参考九、总结与展望ModelSim作为一款专业的集成电路仿真软件,具有着强大的功能和丰富的特性,可以帮助工程师进行电路设计与验证工作。

modelsim使用方法

modelsim使用方法ModelSim 是一种功能强大的硬件描述语言 (HDL) 模拟工具,支持VHDL和Verilog,可用于设计和验证数字系统。

本文将介绍如何使用ModelSim。

**安装 ModelSim****创建项目**在启动 ModelSim 后,首先需要创建一个新的项目。

选择 "File" 菜单,然后选择 "New" -> "Project"。

在打开的对话框中,选择项目的文件夹和项目名称,然后点击 "OK"。

**添加设计文件和测试文件**在项目中,您需要添加设计文件和测试文件。

选择 "Project" 菜单,然后选择 "Add to Project" -> "Add Files". 在打开的对话框中,选择您的设计文件 (VHDL 或 Verilog) 和测试文件,然后点击 "OK"。

**设置仿真**在编译代码之后,下一步是设置仿真选项。

选择 "Simulate" 菜单,然后选择 "Start Simulation"。

在打开的对话框中,选择您的顶层模块。

您还可以选择以 GUI 模式还是批处理模式运行仿真。

在设置仿真之前,您可以添加信号波形文件以在仿真过程中显示波形。

选择 "Simulate" -> "Wave" -> "Add Waveform". 然后,选择信号波形文件 (.do 或 .vcd),并点击 "OK"。

**运行仿真**设置仿真选项后,您可以开始执行仿真。

通过选择 "Simulate" -> "Run",可以运行单步或连续仿真。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ModleSim-Altera 使用流程:

通过quatusll 打开modlesim 的方法

配置生成仿真文件环境

1.Assignments -- settings

2.EDA Tool Settings --simulation -- Tool Name: ModleSim-Altera

3. Format For output netlist --Verilog HDL

4.Time scale : 1ps 也可以指定别的量级

5.output directory :指定测试文件模板生成路径该路径是相对路径

生成仿真文件

1. 生成仿真文件模板:Processing -- Start --Start Tesst Bench Template Writer --提示生成成功

(会在工程文件 modelsim 下的目录找到后缀名为 vt 的 文件)

2. 根据自己想要的条件对模板进行编辑。

配置仿真环境 (指定那个是仿真文件)

0.首先复制一下 仿真 文件 module 关键字后面的 模块名 比如 module key_vlg_tst().. 复制 key_vlg_tst

1.Assignments -- settings

2.EDA Tool Settings -- simulation --NativeLink settings --Compile test bench --点击 后方 test benches

3. new

4.Test bench name :key_vlg_tst(刚才赋值的仿真模块名) | Top level module in test bench : key_vlg_tst(一样)

5.勾选 use est bench to pergorm VHDL timing simulaion -- Design instance name in test bench :填写 i1

6.file name --浏览 找到上面创建的仿真文件 --add

进行仿真

Tool -- Run EDA Simulation Too -- EDA RTL Simulation 稍微等一下 就可以看见相应的仿真波形图。

通过modlesim 打开 test bench 进行仿真的方法

1. 通过trascript 栏中 cd 到我的工程目录下面 比如:cd E:/icore3/icore3_fpga/mytest2/simulation

注意: 在modlesim 中用 / 作为分隔符

2. 新建立一个文件夹 mkdir test :这个时候就会出现一个test 文件夹 可以通过 ls -l

3. file - new project -- project name: work 随便选 比如 work

4. add Existing file -- 添加你想要进行仿真的test bench 文件 一般将该文件放在 放在 src 文件下 ,以顶层_tb 的方式进行命名。

比如有一个 顶层为key.v 文件 那么我会在放同一个目录下面 命名一个 key_tb.v 文件写test bench -- OK -- close 注 :在进行这一步的时候 你已经写好test bench 了

5.右键添加的 .v 文件 然后进行编译 ,看报错情况并进行修改,双击错误的地方,可以查看错误的位置和信息,最后compile all 通过方可停止。

w a j a

6. simulation -- start simulation --work --key_tb (选中的是test bench )-- 不要勾选 Enable Option

7. 将需要进行仿真的信号 选中 --add wave

8. Transcript -- run 1ms

do 文件的编写: 注释用#

quit -sim //退出当前程序的仿真 是 退出当前的仿真 不是关闭modlesim vlib work //新建一个库 库的名字叫做work vmap work work #将work 映射到 work 中去vlog ../scr/pll_1.v ..标示上一级目录 将pll_1.v 添加进来vlog ../scr/dds_sin_rom.v 将dds_sin_rom 也添加进来vlog ../scr/dds_cos_rom.v

vlog ../scr/dds_phas_acc.v

vlog ../scr/dds_cos_sin_block.v

vlog ../scr/dds_cos_sin_block_tb.v

#下面这句话 前半句是添加库 -novopt 不要优化 vsim -L D:/setup/modeltech_6.5/modeltech_6.5/altera/alter_lib -novopt work.dds_cos_sin_bloc_tb w a j a

do wave.do 执行之前保存的图形

run 20ms

注:restart 命令 :我们希望从新从零开始 进行仿真 那么命令是 restart -f test bench 的编写

w a j

a。