ModelSim使用的一点心得

ModelSim使用的一点心得- -

ModelSim使用的一点心得- -1、至今还没有弄明白为什么要用ModelSim,因为看波形Quartus II自带的工具就可以了啊。

2、我刚刚接触modelsim,我想大多数菜鸟跟我一样,看过如何使用ModelSim的介绍,说句实话,那些介绍写的都太过简单,仿佛大家都不屑写上一些比较“弱智”的步骤,恰恰就是这些看似累赘的步走,难为我好久。

教程上都写道,modelsim的简单使用方法如下:建立库- 影射库到物理目录- 编译代码- 启动仿真。

首先建立库就叫我头晕。

库的概念用在这儿实在不合适,把我吓坏了,也就没心思看下一步了。

在我看来,教程应该这么写:<1> 建立一个目录modelsimStudy。

用任何文本编辑器编辑一个简单的例子程序,比如计数器counter.vhd。

有clk、ena、reset输入,cnt作为输出。

<2> 打开Modelsim,首先create project,工程名随意取了,比如命名为test,目录设在modelsimStudy下,默认的库work不变(这样就不用管什么建立库之类的东西了)。

然后add existing file,把counter.vhd加入当前工程。

<3> 编译这个文件,通过之后,work下面会出现counter这个实体。

然后选中它,右键,simulate(左键双击也可)。

<4> ModelSim有很多窗口(新手就怕这个),一开始只要选择view下面的objects 和wave窗口就行了。

旧版的signal窗口在6.0的版本改名为Objects(这个我是摸索了好久才发现的,是不是太笨了?)。

wave窗口刚打开时是空的,需要在objects窗口的add -> wave -> signals in region。

这时,wave上就有clk\ ena \ reset等信号了。

<5> 我们给clk来个输入激励,在object窗口中选中clk,右键选clock,给它定义个时钟。

Multisim使用心得(1)

Multisim使用心得8月19日—8月20日Multisim——NI出品的一款功能强大的电子线路仿真软件,它不仅可以仿真弱电电子,也可以仿真强电,还可以仿真射频微波和FPGA。

以前在学校的时候我就用它验证过不少电路设计,感觉挺不错的,并且仿真的数据也很准确(这个主要跟SPICE模型的精确度有关)。

记得刚开始使用它的时候,有很多次仿真结果与实际差很多,也忍不住会骂NI,这么垃圾的东西也拿出来卖啊,谁要是相信他了,结果肯定是死的很惨,呵呵。

虽然刚开始给我的感觉很不好,但是那时手头也没有比较好的电路仿真软件,先凑合着用吧,等发现更好的再替换它。

现在回头想想,NI挺冤的,经过这么长一段时间的使用和查资料解决相关问题,我终于明白了网上一个前辈说的话,软件本身很不错,但是能不能得到比较精确的结果在于用的人,你会不会使用它。

呵呵,事实确实如此。

Multisim是EWB的升级版,早先的时候,很多电子工程师热衷于使用EWB 来辅助设计,但是牵涉到具体器件上后,EWB就有点力不从心了,Multisim却包含了许多具体的元器件,使用者可以在里面找到相关的型号,然后开始验证自己的设计是否正确合理。

但是有一个问题也会随之而来,就是设计人员在设计电路的时候不会从Mulitisim中去查找合适的元件,而是根据要求与指标先查找合适的元件,然后再去验证自己的正确性,这样一来,就会有许多元件可能在Multisim中找不到,查找Multisim中相同参数的元件又很麻烦,怎么办呢?幸好Multisim可以创建仿真元件模型,否则的话,我们设计出来的东西就只有实际搭出来验证了,这样就会浪费很大的人力物力财力。

下面我就说一下仿真模型的创建步骤。

首先要准备好器件的Pspice模型,这是最重要的,没有这个东西免谈,当然Spice高手除外。

下面就可以利用Multisim的元件向导功能制作自己的仿真元件模型了。

接下来我们以OP07(通用运放)为例介绍一下Multisim创建仿真模型的具体步骤。

modelsim调试技巧

modelsim调试技巧ModelSim是一款流行的电子设计自动化(EDA)工具,广泛应用于集成电路、通信系统和消费电子产品的仿真和调试。

本文将介绍ModelSim的一些调试技巧,帮助您更高效地进行仿真和调试。

一、设置仿真环境1. 启动ModelSim,创建一个新的工程或打开已有的工程。

2. 配置仿真参数,如仿真时钟频率、时序约束等。

3. 编写测试向量或测试脚本,用于验证设计的正确性。

二、常用调试技巧1. 实时监测:在仿真过程中,可以使用实时监测功能来观察仿真波形,以便快速发现设计中的问题。

可以使用“实时监测”工具栏中的相关按钮或命令。

2. 断点设置:在需要调试的代码行设置断点,以便在运行到该行时暂停仿真,从而方便查看该行执行前后的变量值和状态。

可以使用“断点”工具栏中的相关按钮或命令来设置断点。

3. 变量观察:在仿真过程中,可以使用“变量观察”功能来观察设计中的变量值。

可以在仿真波形窗口中双击需要观察的变量,将其添加到“变量观察”列表中。

4. 波形分析:ModelSim提供了强大的波形分析功能,可以帮助您分析仿真波形的异常情况,如信号过冲、下冲等。

可以使用“波形分析”工具栏中的相关按钮或命令来进行波形分析。

5. 脚本调试:如果您的测试脚本中有错误,可以使用ModelSim 的脚本调试功能来逐行执行脚本,并查看每行执行前后的变量值和状态,以便找到错误位置。

可以使用“脚本调试”工具栏中的相关按钮或命令来进行脚本调试。

三、高级调试技巧1. 仿真结果分析:通过分析仿真结果,可以发现设计中的潜在问题。

可以使用ModelSim提供的各种分析工具和报告功能,如时序分析、功耗分析等,来帮助您更好地理解仿真结果。

2. 多平台仿真:ModelSim支持与Xilinx、Intel等厂商的多种硬件平台进行联合仿真,以便更好地验证设计的兼容性和可靠性。

通过多平台仿真,您可以更快地发现设计中的潜在问题。

3. 自动测试生成:ModelSim提供了自动测试生成功能,可以根据设计的结构和行为自动生成测试向量或测试脚本。

一个Modelsim的demo,给你启示

写在前面的话学过MCU设计的朋友都知道,系统调试是多么的重要。

而对于FPGA设计来说,仿真确实最重要的。

一个完整的项目,必须有完整的仿真平台。

有朋友说,按键仿真模型没法搞。

我只能说,你并不了解硬件及处理按键的工作原理,如果你知道。

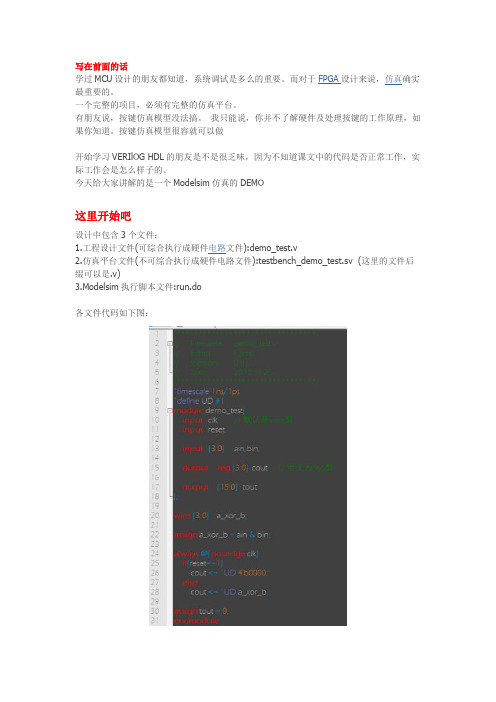

按键仿真模型很容就可以做开始学习VERIlOG HDL的朋友是不是很乏味,因为不知道课文中的代码是否正常工作,实际工作会是怎么样子的。

今天给大家讲解的是一个Modelsim仿真的DEMO这里开始吧设计中包含3个文件:1.工程设计文件(可综合执行成硬件电路文件):demo_test.v2.仿真平台文件(不可综合执行成硬件电路文件):testbench_demo_test.sv (这里的文件后缀可以是.v)3.Modelsim执行脚本文件:run.do各文件代码如下图:图1图2图3其中图1为demo_test.v图2为testbench_demo_test.sv图3为run.do启动仿真平台A. 把三个文件放置到同一个目录下,该目录的路径必须是纯英文或有短下划线(关于这点自己注意),B. 启动Modelsim;C. 制定Modelsim的直接目录,File -> Change Directory. 指定到A指向的目录。

D.在Transcript框中输入:do run.do 回车E.等待波形结果.在熟悉"启动仿真平台"后,F.开始分析代码,这个自己把握。

接下来G1或者G2G1.分析脚本文件run.do. 查看"启动仿真平台"A指向目录产生的文件或文件夹,简单了解脚本实现方式.G2.在代码相应位置输入课文中的一些例子。

再次启动仿真平台H.进入高级设计阶段。

常见问题一个必须要提醒的问题:经常听到有人问这么一个问题,而且有时还碰到一些工作一年的朋友也问:为什么我的信号一直是高阻状态?对于仿真而言,所有信号如何没有赋值,软件认为该信号就为高阻状态,比如以下代码initial beignforever #10 clk = ~clk;end设计者意图很明显:生成一个周期为20个刻度的时钟。

关于simulink,modelsim仿真的小结

MODELSIM学习笔记(二)Dsp Builder设计初步的小结杨森Sept 2015现在使用的软件版本分别是 quartusii 11.0 ,modelsim 10.0c, matlab 2010b ,关于软件的安装以及相互之间的关联,做一个简要的说明。

主要需要注意的是,1.必须在安装dsp builder之前安装matlab;2.dsp破解后(若不破解,simulink中的dsp的库文件不能使用),设置环境变量;3.dsp builder破解过程会生成一个license,这个和之后安装的modelsim生成的license需要共用一个环境变量,所以,可以把两个license合并(把其中一个拷到另外一个最后面);软件相互之间能够关联非常重要,否则后面会出现很多意想不到的问题。

我一开始是按照“EDA技术与VHDL(第三版潘松著)”一书中第九章dsp builder设计初步来做的,课本里说使用tcl脚本文件,不知道是不是由于软件版本的原因,根本无法产生想要的结果,故花了一周左右的时间研究modelsim的使用方法。

在这过程中,出现了各种各样的bug,在崩溃的边缘,最后还是依靠各种网络上的资源片段,一个一个warning和error的调试,最终把所有的仿真给做出来了。

我之所以这么执着于仿真,是因为我后期需要做一个FIR的滤波,在simulink中来做,非常的方便,但是,若不进行rtl级仿真和时序仿真,根本不知道转换过来的vhdl代码能不能使用,这是闲话哈,好了,开始我们的操作过程中遇到的问题的详述吧。

本文主要是关于modelsim的RTL级仿真,后面还会陆续有关于时序仿真的教程,如果有童鞋遇到的难题,可以相互讨论一下,我的联系方式:邮箱:senyangah@主要的过程1.完成一个例程其实很多软件都一个共性,那就是,看再多的例程都不如亲手完成一个设计.网上关于各种初级教程有很多,但是,大多数情况是,你跟着教程一步一笔的去做,根本出现不了你想要的结果,我选择了2个稍微比较好一点的教程,并且里面出现的一些小的bug都已经通过注释给讲明了怎么改.本来我也是打算自己写一个教程,一步一步的把操作步骤写下来,但是我发现,首先就是完全没必要啊,网上给的教程的大致过程都是对的,其次就是这个太耗时间了,所以原谅我的偷懒哈,附件中的教程2和教程3,都是可以仿真成功的,大家跟着做就行啦~其中教程2是使用的自动编译,从quartus中直接启动modelsim,教程3是手动编译,第一个例子是使用vism的命令进行操作的,虽然很繁琐,但是对于初学者来说,了解各个参数的设置是很好的,后面的例程通过编写testbench来进行仿真,这种方式是我们以后进行仿真的主要模式.2.Testbench的编写因为本文主要是围绕着simulink生成的vhdl的modelsim仿真来编写的,所以,我们主要介绍的是怎样使用vhdl来编写testbench,附件中教程4,就是用vhdl来编写testbench,以后我们每次需要编写testbench的时候,就先通过quartus来生成一个testbench模板,然后按照教程4中的模板进行各个参数的设置.关于怎么生成testbench的模板,教程2中有说明.3.关于library的添加如果代码是我们编出来的,那么在用modelsim进行仿真的时候,无需添加任何的library,但是若使用到IP核(比方说product模块吧),则需要添加library,原因可以问度娘哈.关于怎么添加library,教程5非常的好用,这里面有几个主要的关键点需要注意:1.教程5的前几个库添加的时候,一定要注意每个VHD文件添加的顺序,比方说:先添加altera_mf_components.vhd后ALTERA_MF.vhd,一个一个的添加,如果一下子全部的话,会有报错。

modelsim的理解

Modelsim 仿真软件的学习及理解一软件简介Modelsim仿真工具支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化,具备强大的模拟仿真功能,在设计、编译、仿真、测试、调试开发过程中,有一整套工具供你使用,而且操作起来极其灵活,可以通过菜单、快捷键和命令行的方式进行工作。

ModelSim的窗口管理界面让用户使用起来很方面,它能很好的与操作系统环境协调工作。

ModelSim 的一个很显著的特点就是它具备命令行的操作方式。

二功能介绍Modelsim的主要功能包括:对设计文件的设计、编译和仿真。

设计文件的设计:在Modelsim软件打开之后,在把库和工程建立好的前提下,编译设计文件,编译设计文件时遵循verilog的编程规则,语法方面注意关键字的用法,编译设计文件包括两个部分:设计文件源代码的编译和测试代码的编译,测试代码编写时注意函数的调用,尤其是端口的对应,包括名称对应和位置对应,同时还应该注意激励信号的设定,此时应该注意时钟的延时是否是惯性延时。

文件的编译:文件的编译的主要目的是:检查程序语言的语法错误,在编译过程中可以通过两种方法实现:工具按钮的编译法和指令输入的编译法,工具按钮编译法适合于初学者,而指令输入法适合于编程经验较足的编程人员。

编译的过程也就是第一轮检查程序代码的过程,通过编译,软件会以指令的形式在输出脚本框中显示出来,通过显示的错误信息,编程人员会再较短的时间内找处错误代码,及时修改,提高了编程的效率和准确性。

文件的仿真:文件的仿真即就是在写好的源代码和测试代码的基础上,给程序一定的激励信号,在激励信号的基础上观察源代码波形图的变化,是否符合设计初衷,是否满足设计的时序逻辑和组合逻辑的要求。

ModelSim使用的一点心得体会

ModelSim使用的一点心得- -1、至今还没有弄明白为什么要用ModelSim,因为看波形Quartus II自带的工具就可以了啊。

2、我刚刚接触modelsim,我想大多数菜鸟跟我一样,看过如何使用ModelSim的介绍,说句实话,那些介绍写的都太过简单,仿佛大家都不屑写上一些比较“弱智”的步骤,恰恰就是这些看似累赘的步走,难为我好久。

教程上都写道,modelsim的简单使用方法如下:建立库- 影射库到物理目录- 编译代码- 启动仿真。

首先建立库就叫我头晕。

库的概念用在这儿实在不合适,把我吓坏了,也就没心思看下一步了。

在我看来,教程应该这么写:<1> 建立一个目录modelsimStudy。

用任何文本编辑器编辑一个简单的例子程序,比如计数器counter.vhd。

有clk、ena、reset输入,cnt作为输出。

<2> 打开Modelsim,首先create project,工程名随意取了,比如命名为test,目录设在modelsimStudy下,默认的库work不变(这样就不用管什么建立库之类的东西了)。

然后add existing file,把counter.vhd加入当前工程。

<3> 编译这个文件,通过之后,work下面会出现counter这个实体。

然后选中它,右键,simulate(左键双击也可)。

<4> ModelSim有很多窗口(新手就怕这个),一开始只要选择view下面的objects 和wave窗口就行了。

旧版的signal窗口在6.0的版本改名为Objects(这个我是摸索了好久才发现的,是不是太笨了?)。

wave窗口刚打开时是空的,需要在objects窗口的add -> wave -> signals in region。

这时,wave上就有clk\ ena \ reset等信号了。

<5> 我们给clk来个输入激励,在object窗口中选中clk,右键选clock,给它定义个时钟。

modelsim时序仿真最低时间间隔

modelsim时序仿真最低时间间隔

当我们进行数字电路设计时,时序仿真是必不可少的一步。

而在进行时序仿真时,我们需要注意一个重要的参数,即仿真的最低时间间隔。

在ModelSim中,最低时间间隔是指仿真时刻的最小精度,也就是仿真的时间分辨率。

这个参数的设置对于仿真结果的准确性和精度至关重要。

在进行时序仿真时,我们需要考虑到电路中各个信号的传输延迟和时序关系。

如果时间间隔设置得过大,仿真结果可能会出现误差,无法准确反映电路的真实行为。

而如果时间间隔设置得过小,不仅会增加仿真的计算量,还可能导致仿真时间过长,甚至无法完成仿真。

所以,在设置最低时间间隔时,我们需要根据电路的复杂程度和仿真的需求来进行选择。

一般来说,对于大多数数字电路设计,设置一个合适的最低时间间隔就能够满足仿真需求。

在实际操作中,我们可以根据经验来选择一个合适的时间间隔,然后通过观察仿真结果的准确性和稳定性来进行调整。

总的来说,时序仿真的最低时间间隔对于仿真结果的准确性和精度有着重要的影响。

合理设置最低时间间隔可以提高仿真的效率和准确性,从而更好地验证和优化数字电路设计。

在使用ModelSim进行时序仿真时,我们应该根据电路的特点和仿真需求来选择合适的时间间隔,以获得准确而高效的仿真结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ModelSim使用的一点心得- -1、至今还没有弄明白为什么要用ModelSim,因为看波形Quartus II自带的工具就可以了啊。

2、我刚刚接触modelsim,我想大多数菜鸟跟我一样,看过如何使用ModelSim的介绍,说句实话,那些介绍写的都太过简单,仿佛大家都不屑写上一些比较“弱智”的步骤,恰恰就是这些看似累赘的步走,难为我好久。

教程上都写道,modelsim的简单使用方法如下:建立库- 影射库到物理目录- 编译代码- 启动仿真。

首先建立库就叫我头晕。

库的概念用在这儿实在不合适,把我吓坏了,也就没心思看下一步了。

在我看来,教程应该这么写:<1> 建立一个目录modelsimStudy。

用任何文本编辑器编辑一个简单的例子程序,比如计数器counter.vhd。

有clk、ena、reset输入,cnt作为输出。

<2> 打开Modelsim,首先create project,工程名随意取了,比如命名为test,目录设在modelsimStudy下,默认的库work不变(这样就不用管什么建立库之类的东西了)。

然后add existing file,把counter.vhd加入当前工程。

<3> 编译这个文件,通过之后,work下面会出现counter这个实体。

然后选中它,右键,simulate(左键双击也可)。

<4> ModelSim有很多窗口(新手就怕这个),一开始只要选择view下面的objects 和wave窗口就行了。

旧版的signal窗口在6.0的版本改名为Objects(这个我是摸索了好久才发现的,是不是太笨了?)。

wave窗口刚打开时是空的,需要在objects窗口的add -> wave -> signals in region。

这时,wave上就有clk\ ena \ reset等信号了。

<5> 我们给clk来个输入激励,在object窗口中选中clk,右键选clock,给它定义个时钟。

<6>运行Run。

嘿嘿。

有波形出来了吧。

3、2中的例子绝对适合刚刚接触modelsim的新手,有了这个体会之后,结合书上的教程,理解库以及modelsim的各个窗口用途就比较容易了。

然后再尝试结合Quartus使用。

4、Quartus中,选中modelsim作为仿真工具之后,在Quartus目录下会生成一个si mulation文件夹,下面有个modelsim。

完成编译之后,在这个目录下面生成了供mode lsim使用的库和时序文件。

如果选中了编译之后自动调用modelsim,我的做法是用Qua rtus编辑波形文件,然后导出作为激励文件。

或者,自行打开modelsim,然后选择改变目录,把目录指向Quartus生成的modelsim目录。

新建工程,把Quartus下的vhdl以及激励文件添加进来,进行仿真。

5、Modelsim仿真cyclone PLL的问题。

我也遇到过,出现什么fatal error。

解决方法:** Simulation property -> Design Tab -> Resolution 应该设为pssimulation -> start simulation -> Design , 那个resolution非常不显眼,认真找,它的默认值是default,改为ps就行了。

ps:Quartus中把不用的管脚设成高阻态:assignment -> device -> pin&device里面设置。

ModelSim的简要使用方法在这一章里通过一些课程来简单介绍ModelSim的使用方法,更多的需要在实际应用中熟练和掌握。

第一课 Create a Project第一次打开ModelSim会出现Welcome to ModelSim对话框,选取Create a 1. Project,或者选取File\New\Project,然后会打开Create Project对话框。

2.在Create Project对话框中,填写test作为Project Name;选取路径Project Location作为Project文件的存储目录;保留Default Library Name 设置为work。

3.选取OK,会看到工作区出现Project and Library Tab。

4.下一步是添加包含设计单元的文件,在工作区的Project page中,点击鼠标右键,选取Add File to Project。

5.在这次练习中我们加两个文件,点击Add File to Project对话框中的B rowse按钮,打开ModelSim安装路径中的example目录,选取counter.v和tc ounter.v,再选取Reference from current location,然后点击OK。

6.在工作区的Project page中,单击右键,选取Compile All。

7.两个文件编译了,鼠标点击Library Tab栏,将会看到两个编译了的设计单元列了出来。

看不到就要把Library的工作域设为work。

8.最后一不是导入一个设计单元,双击Library Tab中的counter,将会出现Sim Tab,其中显示了counter设计单元的结构。

也可以Design\Load design 来导入设计。

到这一步通常就开始运行仿真和分析,以及调试设计,不过这些工作在以后的课程中来完成。

结束仿真选取Design \ End Simulation,结束Project选取File \ Close \ Project。

第三课 Basic verilog Simulation1.新建一个目录,并设置该目录为当前工作目录,通过从该目录调用Model Sim或是选取File\Change Directory命令来完成。

2.拷贝example目录中verilog文件到当前目录下。

在你编译verilog文件前,你需要在新目录下生成一个设计库。

如果你仅仅熟悉解释性verilog仿真器,诸如Cadence Verilog-XL,那么对于你来说这是一个新的方法。

因为Model Sim是一个编译性Verilog仿真器,对于编译它需要一个目标设计库。

如果需要的话,ModelSim能够编译VHDL和Verilog代码到同一个库中。

3.在编译任何HDL代码前,要建立一个设计库来存放编译结果。

选取Desig n \ Create a New Library生成一个新的设计库。

确定选取Create: a new li brary and a logical mapping to it,在Library Name域中键入work,然后选取OK。

这就在当前目录中建立了一个子目录,即你的设计库。

ModelSim在这个目录中保存了名为_info的特殊文件。

4.下面你将编译Verilog设计。

这个设计例子由两个Verilog源文件组成,每一个都包含一个唯一的模块。

文件counter.v包含一个名为counter的模块,它执行一个简单的八位加法计数器。

另一个文件tcounter.v是一个测试台模块(test_counter),通常用来校验c ounter。

在仿真下,你可以看到这两个文件,通过一个被测试台例示了的模块c ounter的一个简单的实例(名为dut的实例),来层次化的设置了。

稍候你将有机会看一下这个代码的结构,现在,你需要编译两个文件到work设计库。

5.通过选取工具条中的Compile按钮来编译两个文件。

( PROMPT : vlog counter.v tcounter.v )这就打开了Compile HDL Source Files对话框。

选取两个文件后,选择Compile,编译完成后选取Done。

6.选取工具条中的Load Design按钮开始仿真。

( PROMPT : vsim test_counter )Load Design对话框允许你从指定的库中选取一个设计单元仿真。

你也可以为仿真选取Simulation Resolution限制,缺省的库是work,缺省的Simula tion Resolution是1ns。

7.选取test_counter,点击Load接受这些设置。

8.通过在主窗口下的vsim提示符下敲入下述命令来调出Signals、List an d Wave window: view signals list wave (MENU: View\1.为了列示顶级( top-level )信号,移动鼠标到Signals window,选取Vi ew\List\Signals in Region。

( Prompt : add list /test_counter/* )2.现在向Wave window添加信号。

在Signals window选取Edit\Select Al l选择三个信号,拖动三个信号到Wave window的路径名或是数值窗格的任一个中。

HDL条目也能够从一个窗口拷贝到另一个窗口(或者是在Wave and List windo w内部),通过Edit \ Copy和Edit \ Paste菜单命令。

也能删除选取的条目Edit \ Delete。

3.下面打开Source window,选取View \ Source( Prompt : view source )4.导入设计的时候会在工作去开出一个新的Sim Tab栏。

这个Structure P ane展示了设计的层次结构。

你可以点即“+”(expand)或“-”(contract)来观察。

5.点击其中的Function increment可以注意到其他窗口是怎么适当的自动更新的。

明确地说,Source window显示了你在Structure window所选的层次水平的Verilog代码.在这种方式下使用Structure Pane类似于解释性Verilo g的范围命令。

现在,点击Structure Pane的顶层线,确定test_counter模块显示在Source window。

1.Run运行100ns,缺省设置。

(PROMPT: run ) (MENU: Run\Run 100ns)2.设置Run Length为500ns,然后Run。

在仿真运行了600ns,在工作取底部状态栏可以看到这些信息。

3.上个命令使仿真器前进了500ns,也可以设置仿真器推进的时间run @ 3000际仿真器向前推进了2400ns(3000-600)4.选取主窗口Run All。