ModelSim用户手册

modelsim使用指南.

执行仿真 (UI)

选择 timesteps数量就 可以执行仿真

Restart – 重装任何已改动 的设计元素并把仿真时间设 为零 COM) restart

38

run 命令参数

可选的参数

– -<timesteps> <time_unit> • 指定运行的timesteps数量 • 单位可用{fs, ps, ns, ms, sec}

用户界面 (UI)

– 能接受菜单输入和命令行输入 – 课程主要讨论

批处理模式

– 从DOS或UNIX命令行运行批处理文件 – 不讨论

13

基本仿真步骤

1 Ö 建立库

2 Ö 映射库到物理目录

3 Ö 编译源代码 - 所有的HDL代码必须被编译 - Verilog和VHDL是不同的

4 Ö 启动仿真器 5 Ö 执行仿真

UI) Design -> Compile Cmd) vlog -work <library_name> <file1>.v <file2>.v

– 文件按出现的顺序被编译 – 文件的顺序或者编辑的顺序不重要

支持增量式编译 缺省编译到work库

– 例如. vlog my_design.v

– -sdfmin | -sdftyp | -sdfmax <instance>=<sdf_filename> • 注释SDF文件 • 可选项 • 使用实例名也是可选项; 如果没有使用, SDF用于顶级

36

5 Ö 执行仿真

UI) Run COM) run <time_step> <time_units> 按timesteps指定的时间长度执行仿真

ModelSim使用说明

ModelSim使用说明

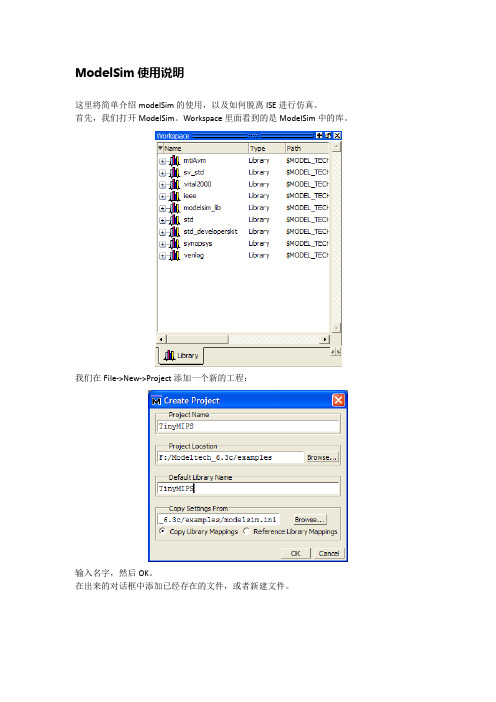

这里将简单介绍modelSim的使用,以及如何脱离ISE进行仿真。

首先,我们打开ModelSim。

Workspace里面看到的是ModelSim中的库。

我们在File->New->Project添加一个新的工程:

输入名字,然后OK。

在出来的对话框中添加已经存在的文件,或者新建文件。

这里我们添加了之前各个模块的文件,Top文件,这里选择将文件保留在原位置:

并新建了一个test.v的测试用例。

在该例中,#50表示在上一句之后延时50个Cycles,一个Cycle的时间为`timescale 1ns/1ps 中的1ns。

而Always #50 clk=~clk;则创建了一个周期100ns的时钟。

在Workspace的Project中,右键选择Project Settings:

将File Type改为Verilog。

在Workspace的Project中,右键选择Add To Project->Simulation Configuration:

选择TipyMIPS下的test,并钩掉优化。

保存

在菜单View中,选择Wave,即可开始仿真。

当更改源代码后,只需重新编译。

然后Restart即可点击Run重新仿真。

上图中的Runtime Options可以更改Run一次的时间,如下:。

Modelsim仿真新手入门最详细教程

Modelsim仿真新⼿⼊门最详细教程2021年11⽉15⽇00 安装包/版本我是提前在⽹上下好的(但这⼀点也给我的实验造成了“⿇烦”),⽤的是Modelsim SE-64 2020.4版本的,学校实验室的似乎不同。

但最终没有太⼤影响。

01 配置环境步骤学校有⼀个⽂档,在机房电脑照做就⾏。

我因为是⾃⼰下载的,配置与机房软件有所不同,所以⼜平添了很多⿇烦。

01-0 verilog⽂件这个代码可以在很多地⽅编写:Visual Studio Code⾥有Verilog的插件;还可以有更强⼤的语⾔编辑器:Nodepad++。

这⾥我使⽤的是Nodepad++,因为看上去专业⼀点。

Nodepad++的页⾯效果如图:其实第⼀次上机,⽼师会给⼤家⽰例⽂件(包括设计代码与测试代码),跑出来⽰例波形就⾏。

01-1 具体步骤1. 新建⼀个⽤于安放project的⽂档,放在哪⾥都⾏。

把前⾯做出的.v⽂件添加到这个⽂档。

留意⼀下路径。

2. 打开modelsim,在jumpstart中create a new project。

3. 在弹出的提⽰框⾥browse,找到刚才的⽂件夹。

选中。

填写project 名,注意要与.v⽂件⾥的module名保持⼀致。

点击ok。

4. 进⼊页⾯后会是这样⼦:注意此处两个⽂件后⾯应当都有问号,代表没有编译。

先逐个右击⽂件add to this project确保加⼊。

5. 在上⽅提⽰栏中complie->compile all。

稍等些许会看到⽂件后问号全部变为对勾,表⽰代码编译通过,没有问题。

如果此步出错则代表代码有bug。

在下⾯的Transcript中上翻查找错误。

6. 点击上⽅Simulate->start simulation。

由于注意与实验室不同的,选中下⾯的Enable optimization,再在右侧Optimization Options中的Visibility中选中Apply full visibility....7. 接着在work⾥找到测试代码的⽂件,选中。

《电子设计自动化》实验手册modelsim篇

1.Modelsim使用教程

在file name中填写fenpin,add file as type选择Verilog就行,如果你想用别的语 言编写,选择相对应的语言类型就行。点ok。

1.Modelsim使用教程

将波形 保存为图片 。 1. 可以直 接截图保存 图片; 2. 在波形界面点击 fileexport-image,输入保存的名字即可保存。

下面的几个实验有的给出了测试的代码,有的没有给出。因此,为了完成这几个实验, 请同学们自主完成测试代码的编写,进而完成编译、仿真,最终获得正确的仿真波形。

5)其它:10分;总体映象分,态度是否认真,实验感想等是否真实深刻。

6)还需要提交每次实验的电子材料和期末测试的电子材料。文件夹命名规则:学号+ 姓名+实验*(期末),文件夹下需要有Verilog代码,testbench代码,仿真波形 .wlf 和.do文件,波形export图片。

实验1:计数器

1.Modelsim使用教程

提示有错误,tb文件后面的问号变成差号。双击transcript界面的红色字体,弹出一 个界面,显示错误的具体位置及提示。

1.Modelsim使用教程

该错误是include包含文件应该用英文的双引号,而不是中文的双引号。或者注释掉 改行,保存后再重新编译。tb文件后面的差号变成对号,表示编译通过。

实验2:全加器

module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule

ModelSim用户手册

我们假设您已经非常熟悉您的操作系统。

您应该很熟悉您图形界面的窗口操作功能:不是开放WINDOWS,OSF/MOTIF,就是Microsoft Windows NT/95/98/2000,我们也假定您具有VHDL和VERILOG的应用知识。

尽管ModelSim是一款非常卓越的面向HDL概念学习和实践的工具,但这个文档不是为这个目的而编写的。

ModelSim SE/EE Tutorial

在线PDF格式

从ModelSim的HELP菜单中找SE/EE

Documentation组,或者在光盘路径\modeltech\docs目录中找se_man.pdf文件。也可以从我们的网站中获得。

ModelSim SE/EEUser’s Manual(用户手册)

ModelSim SE/EEQuick Guide(命令和特性的快速查找资料)

纸介质

向ModelSim公司索取

在线PDF格式

从ModelSim的HELP菜单(选择SE/EE

Documentation > SE/EEQuick Guide),或者在路径\modeltech\docs目录中找se_guide.pdf文件。也可以从我们的网站中获得。

SPARC(SUN公司的工作站系统)是SPARC国际公司的商标。

Sun Microsystems,Sun, SunOS 和 OpenWindows 是Sun

Model Technology公司版权受保护,Model Technology公司授权用户可以打印在线文档(只能用于内部商业目的)。

2000年3月出版

Documentation组,或者在光盘路径\modeltech\docs目录中找se_cmds.pdf文件。也可以在安装完成后的硬盘中找到。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

ModelSim新手使用手册

ModelSim最基本的操作,初次使用ModelSim的同学,可以看看,相互学习。

无论学哪种语言,我都希望有个IDE来帮助我创建一个工程,管理工程里的文件,能够检查我编写代码的语法错误,能够编译运行出现结果,看看和预期的结果有没有出入,对于Verilog语言,我用过Altera的Quartus II,Xilinx的ISE,还有ModelSim(我用的是Altera 官网的ModelSim_Altera),甚至MAXPlus II,不过感觉这软件太老了,建议还是前三者吧。

学Verilog,找一本好书很重要,参考网友的建议,我也买了一本夏宇闻老师的《Verilog 数字系统设计教程》,用Quartus II来编写代码,个人觉得它的界面比ISE和ModelSim友好,我一般用它编写代码综合后自动生成testbench,然后可以直接调用ModelSim仿真,真的很方便,但学着学着,发现夏老师书里的例子很多都是不可综合的,比如那些系统命令,导致很多现象都发现不了,偶然间我直接打开了ModelSim,打开了软件自带的英文文档,步骤是:Help ->PDF Documentation->Tutorial如下所示:打开文档的一部分目录:往下读发现其实ModelSim可以直接创建工程,并仿真的。

下面以奇偶校验为例叙述其使用过程(当然前提是你在Altera官网下载了ModelSim并正确安装了)。

1.打开软件,新建一个工程,并保存到自定义的目录中(最好别含中文路径)2.点击Project,弹出窗口问是否关闭当前工程,点击Yes,接着又弹出如下窗口我个人的习惯是把Project Name和Default Library Name写成一样,自己定义Project Location。

又弹出如下窗口:3.点击Close(我的版本不能Create New File,其实新建好了工程一样可以新建.v文件),然后点击屏幕下方的Project标签:如果一开始不是如上图所示的界面,那么可以点击如下图所示红色标记的按键变成上图界面:4.在屏幕空白处右击鼠标,出现如下窗口:5.现在可以选New File或者Existing File(首先你已经编写好了)。

modelism简明操作指南

第一章介绍ModelSim的简要使用方法第一课 Create a Project1.第一次打开ModelSim会出现Welcome to ModelSim对话框,选取Create a Project,或者选取File\New\Project,然后会打开Create Project对话框。

2.在Create Project对话框中,填写test作为Project Name;选取路径Project Location作为Project文件的存储目录;保留Default Library Name设置为work。

3.选取OK,会看到工作区出现Project and Library Tab。

4.下一步是添加包含设计单元的文件,在工作区的Project page中,点击鼠标右键,选取Add File to Project。

5.在这次练习中我们加两个文件,点击Add File to Project对话框中的Browse 按钮,打开ModelSim安装路径中的example目录,选取counter.v和tcounter.v,再选取Reference from current location,然后点击OK。

6.在工作区的Project page中,单击右键,选取Compile All。

7.两个文件编译了,鼠标点击Library Tab栏,将会看到两个编译了的设计单元列了出来。

看不到就要把Library的工作域设为work。

8.最后一不是导入一个设计单元,双击Library Tab中的counter,将会出现Sim Tab,其中显示了counter设计单元的结构。

也可以Design\Load design 来导入设计。

到这一步通常就开始运行仿真和分析,以及调试设计,不过这些工作在以后的课程中来完成。

结束仿真选取Design \ End Simulation,结束Project选取File \ Close \ Project。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MODEL SIM 5.4版使用指南世界上最流行的VHDL语言模拟器ModelSim /VHDL, ModelSim /VLOG, ModelSim /LNL, 和ModelSim /PLUS是由Model Technology开发,未经授权不得拷贝,复制,没有Model Technology 公司的书面许可不得进行其他任何形式的复制。

本手册上对程序的描述是经过许可的,未经允许不得使用和拷贝。

最终用户可以打印随产品附送的联机文件。

通过购买许可证可以获得数字和拷贝的打印权。

Microsystems公司的注册商标。

其他商标和注册商标都是其拥有者的财产ModelSim 是Model Technology公司的注册商标。

PostScript是Adobe Systems公司的注册商标。

UNIX是AT&T公司在美国和其他国家的注册商标。

FLEXlm是Globetrotter软件公司的商标。

IBM, AT,PC,ATX和RISC System/6000是IBM公司的商标。

Windows,Microsoft,和MS-DOS是Microsoft公司的注册商标。

OSF/Motif是OSF公司的商标。

SPARC(SUN公司的工作站系统)是SPARC国际公司的商标。

Sun Microsystems,Sun, SunOS 和 OpenWindows 是SunModel Technology公司版权受保护,Model Technology公司授权用户可以打印在线文档(只能用于内部商业目的)。

2000年3月出版Model Technology公司地址:10450 SW Nimbus Avenue / Bldg. R-BPortland OR 97223-4347 USA电话: 503-641-1340传真: 503-526-5410e-mail: support@, sales@主页: 目录介绍 5前言 9第一章创建一个项目 1-11第二章 VHDL基础 2-19第四章批模式仿真的运行 4-41第五章在启动中执行指令 5-45第六章 Tcl/Tk 和 ModelSim 6-47第七章 Verilog 基础 7-63第八章 VHDL/Verilog的混合仿真 8-81第九章基于性能分析器的仿真 9-91第十章基于代码覆盖的仿真 10-107第十一章查找名字与值 11-115第十二章波形窗口的使用 12-119技术支持,资料更新,和许可证 127软件认证协议 135索引 141介绍本章内容软件环境ModelSim的图形界面支持的标准假设索引软件环境这些文件支持ModelSim SE/EE 5.4的UNIX版,Microsoft Windows NT 4.0版, 和Windows 95/98/2000版。

如果你使用的是ModelSim软件的后续版本,请点击软件附带的README文件。

任何追加的信息都在那里。

虽然这些文件适用于VHDL和Verilog,但是即使你的设计只限于一种硬件描述语言,你也会发现这些文件是非常有用的参考。

ModelSim的图形界面当你的操作系统提供windows管理结构,那么ModelSim的控制就具有windows的特征,像菜单,按钮,和滚动条。

还有一些界面支持如下操作系统:* SPARCstation with OpenWindows, OSF/Motif, 或 CDE* IBM RISC System/6000 with OSF/Motif* Hewlett-Packard HP 9000 Series 700 with HP VUE, OSF/Motif, 或CDE* Linux (Red Hat v. 6.0 or later) with KDE 或 GNOME* Microsoft Windows NT and Windows 95/98/2000因为ModelSim的图形界面是以Tcl/TK为基础的,你也可以使用工具建立你自己的仿真环境.你很容易就能实现优化配置,命令仿真的可变优化.图形界面的命令可以让你改变和替换原有的windows菜单,菜单操作和按钮.支持的标准Model Sim VHDL 支持IEEE 1076-1987, 1076-1993 VHDL标准,支持 VHDL互用性的1164-1993标准多值逻辑系统和1076.2-1996标准的 VHDL精确包标准用Model Sim开发的任何设计都与其他的VHDL系统兼容,其都符合IEEE 标准 1076 1987 或 1076-1993.。

Model Sim Verilog是基于IEEE标准1364-1995的标准硬件描述语言。

(Model Sim 5.2e不支持PL12.0的VP1程序) 开放的Verilog V2.0国际版应用也很广泛 ModelSim PE 和EE版支持 PLI(程序设计语言界面)和VCD(值跳变) 另外,所有的产品都支持SDF 1.0 到 3.0, VITAL 2.2b, 和VITAL’95 –IEEE 1076.4-1995. 假设我们假设您已经非常熟悉您的操作系统。

您应该很熟悉您图形界面的窗口操作功能:不是开放WINDOWS,OSF/MOTIF,就是Microsoft Windows NT/95/98/2000,我们也假定您具有VHDL和VERILOG的应用知识。

尽管Mode lSim是一款非常卓越的面向HDL概念学习和实践的工具,但这个文档不是为这个目的而编写的。

建议非常欢迎您来电,来函,传真,或EMAIL提出任何有关本手册和Mode lSim 软件的意见和问题Model Technology Incorporated10450 SW Nimbus Avenue, Bldg. R-BPortland, OR 97223-4347 USA电话: 503-641-1340传真: 503-526-5410email: manuals@网址: 索引Mode lSim 的文件通过我们的网站/resources/ index.html下载,前言在您学习这些课程之前我们会给您提供详细的介绍。

您将决定通过最好的方式在您的操作系统中创建目录,拷贝文件和执行程序。

(当您用Mode lSi m的图形界面来进行仿真的话,这种界面对所有的应用平台来说都是一致的)另外,您可以在Mode lSi m的用户手册和命令参考中找到详细的VHDL,Verilog, 和兼容VHDL/Verilog仿真的资料。

(看“索引”)实例引导WINDOWS的路径解析器————当您尝试这个实例时,可在你的操作系统上使用解析器命令,按钮和菜单等效方法课程中的大部分步骤都是要通过按钮和菜单的选册来实现的。

适当的时候,在步骤中,VSIM命令行(PROMPT:*提示符号,DOS*),或者菜单模式(MENU:)其中括号中的选择是等效的。

这个例子说明3种run –all命令的操作方法,一种是按钮,一种是提示光标(DOS命令),还有一种是菜单选择。

拖和拉拖和拉操作允许你在窗口中拷贝和移动信号。

如果拖和拉操作作为课程的一个步骤来讲,他就跟MENUS(菜单模式)和PROMPTS(提示光标模式)非常类似了。

命令的历史记录这一课的工作,你要把注意力集中在主记录窗口上。

按钮和菜单选择对命令的调用都记录在那里。

你可以通过移动箭头来查看这些命令的历史记录。

或者用一种捷径,既通过Mode lSi m/VSIM的PROMPT(提示光标模式,DOS)来查看命令的历史记录在主记录器里重复命令ModelSim的主记录可以被保存下来,通过DO文件来重复执行主记录里的最终文件。

在任何时间,在仿真前或仿真中你都可以存储记录。

如果你不想存储全部的命令历史记录,你可以通过选项来清除记录(File > Clear Transcript)存储记录的的内容可以通过选择主菜单的File > Save Main As来实现,用DO命令可以重复此命令。

do <do file name>例如,如果你把一系列编译命令存储为mycompile.do (the .do 扩展名是随意可选择的),你可以用一个命令重新编译。

do mycompile.do 注意:在这个例子里PROMPT和RETURN都没有结束一个命令行。

第一章创建一个项目本章目的:·了解“欢迎到ModelSim”的对话框特征·创建一个项目(.mpf文件)欢迎到ModelSim的对话框在第一次打开ModelSim时,你将会看到欢迎到ModelSim的对话框(如果屏幕没有显示,你可以在主窗口选择Help > Enable Welcome,在下次您启动ModelSim 时就会显示正常了)从这个对话框,你能:显示快速启动菜单,这个菜单包含了对一些普通问题的解答。

运行ModelSim的认证诊断用项目创建魔法师从打草稿或拷贝一个已有的项目来创建一个新的项目打开一个已有的项目点击Done 进入ModelSim的主窗口。

创建一个项目在规范或测试的HDL设计下,一个项目提供一个实体。

最小配置情况下,有一个根目录,一个操作库,和一个会话状态,这些都存储在项目的根目录下一个a .mpf文件里。

一个项目由以下几个部分组成:HDL资源文件子目录本地库整体库的资料如果需要更多有关项目文件使用的信息,请看ModelSim的用户手册。

注意:从5.3版开始,Mode lSim 公司后缀为.mpf的扩展文件是指项目文件。

在过去的版本里modelsim.ini 文件(系统初始化文件)被作为项目文件。

1.下列其中一种方式可以启动Mode lSim在UNIX的Shell模式下键入vsim在你的Windows操作系统下,可以通过点击开始菜单里的Windows快捷图标modelsim.exe或者在DOS模式下执行文件modelsim.exe2.在Welcome to ModelSim的对话框里选Create a Project按键(如果Welcome to ModelSim的对话框没有显示,你可以在主窗口选择Help > Enable Welcome,在下次您启动ModelSim时就会显示正常了)通过从ModelSim的主窗口选择FileNew > New Project,你也可以进入创建一个新项目的对话框。

点击Create a Project 按钮打开创建一个新项目的对话框和一个项目创建魔法师。

项目创建魔法师可以在项目创建的每一个步给你提供帮助。

它提供Verilog 或VHDL资源文件种类的输入选择,然后帮你添加到项目里。

3.在创建一个新项目的对话框里,你可以选择创建一个新的草稿性的项目,或者拷贝一个存在的项目。