modelsim使用教程6.0

使用ModelSim仿真入门

1.点击 ModelSim实验 下载实验文档,保存并解压到D:盘根目录下。

2.启动 ModelSim6.0,执行 File 菜单下的 Change Directory... 命令。

在随后弹出的对话框中,选择 D:\exam 文件夹,点击“OK”按扭。

3.执行 File->New 菜单下的 Library 命令,在随后弹出的对话框上,点击“OK”按钮,建立 work 库。

4.执行 File->New 菜单下的 Project 命令,在随后弹出的对话框的 Project Name 栏,输入 counter,点击“OK”按钮。

5.点击“Use Current Ini”按钮。

6.点击“Add Existing File”图标。

在随后弹出的对话框上,通过点击“Browse...”按钮,选中 D:\exam文件夹下的 tb.v、counter.v 文件,然后点击“OK”按钮。

点击 Add Item to Project 对话框的“Close”按钮。

7.在 Workspace 窗口里,点击右键。

在弹出菜单中点击 Compile 下的 Compile All 命令。

8.在 Simulate 菜单下,点击 Start Simulation... 命令。

9.在随后弹出的对话框中,将 Design Unit 项设为 work 库下 tb 单元,将 Resolution 设为 ns,然后点击“OK”按钮。

10.执行 View->Debug Windows 菜单下的 Wave 命令,打开 Wave 窗口。

11.在 Objects 窗口下,点击右键。

在弹出菜单下,点击 Add to Wave 下的 Signals in Design 命令。

12.在 Transcript 窗口里,输入 run 10 ms 命令。

13.进入 Wave 窗口,观察各个信号的波形,是否与原设计相符。

14.在 Wave 窗口里,双击 cnt 的波形,打开 dataflow 窗口,观察各个信号传递关系。

modelsimSE6.0安装

modelsimSE6.0安装我安装的版本是Modelsim SE 6.2b ,相信其它版本也不会在安装问题上有太大的差异.如果存在,这里的方法也应该可作为一个很好的参考.1) 打开您下载到或是通过其他什么什么路径搞到的安装文件,找到Setup 文件, 双击之, 然后一路“确定” 或点“是”(选择FULL版本的较好),安装到自己选定的路径后, 它会要求你重启电脑, 这时你可以重启了.2) 重启后, 这时你就要用license 进行注册了.注册方法是这样的:注册器是一个Keygen软件来着, 你可以从网上下载到注册器(如果自己已经有的话那就自然方便了), 然后双击Keygen 这时会弹出一个对话窗口, 要求你在hostid下面的输入框里输入你的网卡号(网卡号获取方法在下面有介绍). 这时你可以在其中输入你的网卡号,也可不用理它,直接点generate, 这时你会发现生成了一个license.dat 文件,这个就是你的注册文件了.在这个文件里就有你的网卡号HOSTID后面的一串码就是你的网卡号了.3) 然后你要做的就是把这个license.dat文件复制到你的Modelsim 安装路径下的win32文件里面.(比如我的安装路径是D:\Modeltech_6.2b, 我就在D盘找个Modeltech_6.2b文件,进去后再找到win32文件,进去后把license.dat复制到这里)4) 下一步是很关键的了, 这一步你需要创建一个环境变量LM_LICENSE_FILE.创建方法如下: 在桌面左键“我的电脑” ->属性->高级->环境变量,然后在系统变量中新建一个变量,编辑用户变量中的变量名为. LM_LICENSE_FILE ,变量值即为你的license.dat的安装路径,比如我的就是D:\Modeltech_6.2b\win32\license.dat ,编辑系统变量中的变量名:CDSROOT,变量值:D:\Modeltech_6.2b\win32确定后,就可以了.5) 运行一下Modelsim,如果运行成功,没有出现什么启动不了的error 窗口,那你就大功告成了.6) 如果在第五步中,你发现老是弹出错误窗口, 显示Error: “System clock has been set back” in the MAX+PLUS II software. 这时老兄您就中彩了, 我正是为这个问题烦了好几天. 不过还好,我在网上找了到解决这个问题原因:Error: “System clock has been set back” in the MAX+PLUS IIsoftware.You receive this error message if the vendor daemon has detected one ormore system files dated in the future compared to the system clock.One possible solution is to locate the files that have an invalid date stampand to open each file and then save it so that it has the correct date/timestamp. The vendor daemon primarily looks at system files in thefollowing directories:■ C:\ (The root directory)■ The directory where your Microsoft Windows files are installed (forexample, C:\WINNT)■ Your MAX+PLUS II software directory (for exampleC:\MAXPLUS2)One way to find the affected files is to use the Windows Find utility.Search by date and specify files with a date later than today’s date. Somefiles may be hidden, so make sure that the Find utility isconfigured todisplay all files.If your MAX+PLUS II software was installed with an incorrect systemclock, you may need to perform the following steps:1. Uninstall the MAX+PLUS II software.2. Set the system clock to the current time and date.3. Restart the PC.4. Reinstall the MAX+PLUS II software in a different directory.上面说的意思是, 当你碰到这个问题时,原因是软件中的vendor daemon发现你的机子中系统文件的创建日期超前了你的电脑上的系统时钟(也就是你电脑上显示的时间).这时你的解决办法就是通过搜索文件找到这些文件,然后删掉这些文件.方法如下:进入C盘,修改文件查看方式,使你可以看到所有文件.然后点“系统任务”中的“搜索文件或文件夹”,查找所有文件和文件夹->高级选项->指定日期, 修改时间范围, 我是从当前时间搜索到2050年,通过先后选定“修改日期” “访问日期” “创建日期”,最后我搜索到了一堆2098年创建的文件和2013年创建的文件.我把这些文件统统删了. 然后卸载掉原来的Modelsim ,重启后,再次按照1 à5的步聚重新安装,这下终于搞定了.*_*以上就是我的安装过程,希望上面的东东能够给各位同仁有所帮助.*_*对了,还要介绍一下获取你的网卡号的方法:开始->所有程序->附件->命令提示符,这时就进入DOS环境下,输入ipconfig /all ,enter后就可看到一堆的输出, 仔细找一下Physical Address 后面12位码就是你的网卡号了.(也可以通过开始->运行,输入cmd, 进入DOS 环境。

modelism简明操作指南

第一章介绍ModelSim的简要使用方法第一课 Create a Project1.第一次打开ModelSim会出现Welcome to ModelSim对话框,选取Create a Project,或者选取File\New\Project,然后会打开Create Project对话框。

2.在Create Project对话框中,填写test作为Project Name;选取路径Project Location作为Project文件的存储目录;保留Default Library Name设置为work。

3.选取OK,会看到工作区出现Project and Library Tab。

4.下一步是添加包含设计单元的文件,在工作区的Project page中,点击鼠标右键,选取Add File to Project。

5.在这次练习中我们加两个文件,点击Add File to Project对话框中的Browse 按钮,打开ModelSim安装路径中的example目录,选取counter.v和tcounter.v,再选取Reference from current location,然后点击OK。

6.在工作区的Project page中,单击右键,选取Compile All。

7.两个文件编译了,鼠标点击Library Tab栏,将会看到两个编译了的设计单元列了出来。

看不到就要把Library的工作域设为work。

8.最后一不是导入一个设计单元,双击Library Tab中的counter,将会出现Sim Tab,其中显示了counter设计单元的结构。

也可以Design\Load design 来导入设计。

到这一步通常就开始运行仿真和分析,以及调试设计,不过这些工作在以后的课程中来完成。

结束仿真选取Design \ End Simulation,结束Project选取File \ Close \ Project。

ModelSim6.0SE软件的安装

ModelSim6.0软件的安装1. 点击 ModelSim6.0SE 下载 ModelSim6.0SE 安装包,保存并解压到D:盘根目录下。

2. 进入到 D:\modelsim6.0\Disk1 文件夹,双击 setup.exe 文件,启动安装向导。

3. 在安装模式对话框上,点击 Full Product 按钮。

4. 在随后弹出的版权声明对话框上点击 Next 按钮,继续。

5. 在 license 确认对话框上,点击 Yes 按钮,继续。

6. 安装路径设为: C:\Modeltech_6.0,点击 Next 按钮,继续。

7. 点击 Next 按钮,继续。

8. 当询问是否安装 Hardware Security Key 的对话框弹出时,点击 No 按钮,继续。

9. 点击是(Y) 按钮,在桌面上建立快捷方式。

10. 点击是(Y) 按钮,将软件的安装路径加入到系统环境。

11. 点击 Finish 按钮,完成主程序安装。

12. 当弹出 license 安装向导对话框时,点击 Close 按钮。

13. 进入 D:\modelsim6.0 文件夹,双击 keygen.exe 图标,启动 license 产生器。

在 license 产生器的主界面上,点击 Generate 按扭,产生 license 文件,然后点击 Exit 按钮,退出。

14. 将 D:\modelsim6.0 下的 license.dat 文件复制到 C:\Modeltech_6.0 下。

15. 在桌面上,选中“我的电脑”图标,点击鼠标右键。

在弹出菜单上,选择“属性”,进入系属性设置对话框。

选择“高级”栏目,点击“环境变量”按钮。

16. 在环境变量设置对话框上,点击用户变量栏目的“新建”按钮,新建一个环境变量。

变量名为:LM_LICENSE_FILE,变量值为:C:\Modeltech_6.0\license.dat 。

点击“确定”按钮,退出环境变量设置对话框。

Modelsim_6.0_使用教程

Modelsim 6.0 使用教程1. Modelsim简介Modelsim仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。

但是它也有缺点,就是它里面所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到modelsim就可以用,它假设使用者对当前操作的前期准备工作都已经很熟悉,所以初学者往往不知道如何做当前操作的前期准备。

2. 安装同许多其他软件一样,Modelsim SE同样需要合法的License,通常我们用Kengen产生license.dat。

⑴.解压安装工具包开始安装,安装时选择Full product安装。

当出现Install Hardware SecurityKey Driver时选择否。

当出现Add Modelsim To Path选择是。

出现Modelsim License Wizard时选择Close。

⑵.在C盘根目录新建一个文件夹flexlm,用Keygen产生一个License.dat,然后复制到该文件夹下。

⑶.修改系统的环境变量。

右键点击桌面我的电脑图标,属性->高级->环境变量->(系统变量)新建。

按下图所示内容填写,变量值内如果已经有别的路径了,请用“;”将其与要填的路径分开。

LM_LICENSE_FILE = c:\flexlm\license.dat⑷.安装完毕,可以运行。

详细介绍modelsim的使用方法

测试台

- - Verilog 或 VHDL代码 非常复杂的仿真(交互式仿真、数据量大的仿真)

force命令

- - - 简单的模块仿真 直接从命令控制台输入 .DO 文件 (宏文件)

用ModelSim作功能仿真(19)

5 执行仿真----仿真器激励

force命令

用ModelSim作功能仿真(15)

5 执行仿真(UI)

选择 timesteps数量就 可以执行仿真

Restart – 重装任何已改动 的设计元素并把仿真时间设 为零

COM) restart

用ModelSim作功能仿真(16)

5 执行仿真----run 命令参数

可选的参数 - -<timesteps> <time_unit> • 指定运行的timesteps数量 • 单位可用{fs, ps, ns, ms, sec} - -step • Steps to the next HDL statement - -continue • 继续上次在-step或断点后的仿真 - -all • 运行仿真器直到没有其他的事件

用ModelSim作时序仿真(3)

时序仿真的实现方法:

unisim库是用来对ISE中画的电 路图进行前仿真时用的。

simprim则是在作布线后的时序 仿真时用。

用ModelSim作时序仿真(4)

时序仿真的实现方法:

以Foundation为例:

Foundation所产生的netlist不包含time delay的数据, 有一个time_sim.SDF文件来存储TIMING数据。(有 的厂商的布局布线所产生的NETLIST文件已经包含有 time delay的数据). Foundation所产生的NETLIST文件默认的文件名是 time_sim.vhd(或time_sim.v) time_sim.vhd或time_sim.v文件用到新的simprim库, 因此必须在仿真前先建立。 做时序仿真,要编译time_sim.vhd或time_sim.v,以 及time_sim.SDF 加载测试文件

modelsim使用方法

modelsim使用方法ModelSim 是一种功能强大的硬件描述语言 (HDL) 模拟工具,支持VHDL和Verilog,可用于设计和验证数字系统。

本文将介绍如何使用ModelSim。

**安装 ModelSim****创建项目**在启动 ModelSim 后,首先需要创建一个新的项目。

选择 "File" 菜单,然后选择 "New" -> "Project"。

在打开的对话框中,选择项目的文件夹和项目名称,然后点击 "OK"。

**添加设计文件和测试文件**在项目中,您需要添加设计文件和测试文件。

选择 "Project" 菜单,然后选择 "Add to Project" -> "Add Files". 在打开的对话框中,选择您的设计文件 (VHDL 或 Verilog) 和测试文件,然后点击 "OK"。

**设置仿真**在编译代码之后,下一步是设置仿真选项。

选择 "Simulate" 菜单,然后选择 "Start Simulation"。

在打开的对话框中,选择您的顶层模块。

您还可以选择以 GUI 模式还是批处理模式运行仿真。

在设置仿真之前,您可以添加信号波形文件以在仿真过程中显示波形。

选择 "Simulate" -> "Wave" -> "Add Waveform". 然后,选择信号波形文件 (.do 或 .vcd),并点击 "OK"。

**运行仿真**设置仿真选项后,您可以开始执行仿真。

通过选择 "Simulate" -> "Run",可以运行单步或连续仿真。

Modelsim详细使用教程

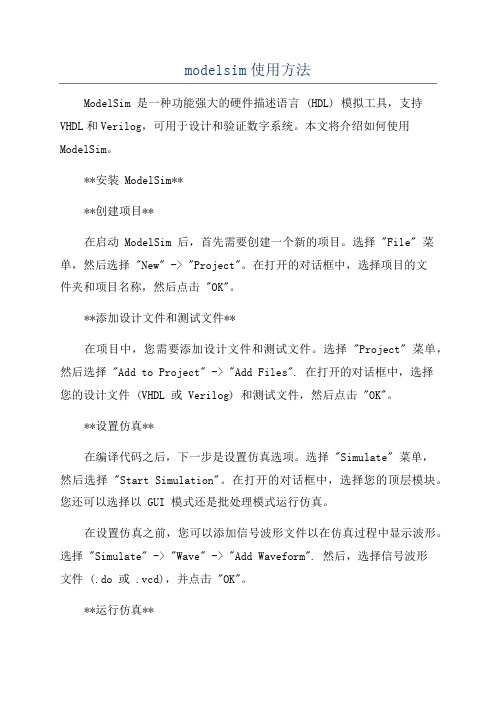

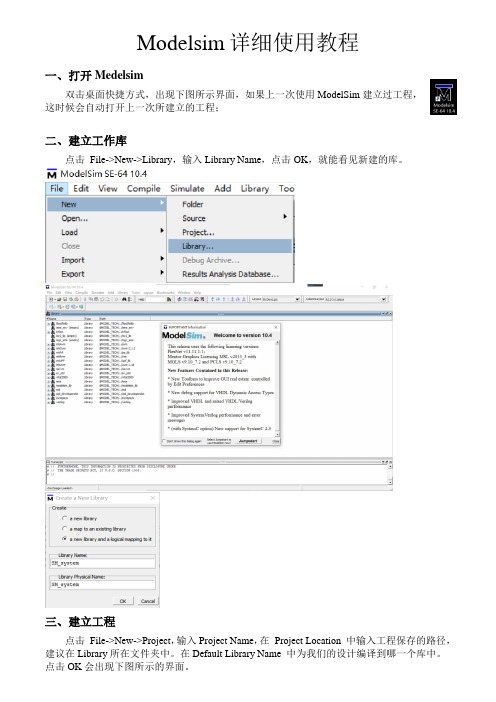

Modelsim详细使用教程一、打开Medelsim双击桌面快捷方式,出现下图所示界面,如果上一次使用ModelSim建立过工程,这时候会自动打开上一次所建立的工程;二、建立工作库点击File->New->Library,输入Library Name,点击OK,就能看见新建的库。

三、建立工程点击File->New->Project,输入Project Name,在Project Location 中输入工程保存的路径,建议在Library所在文件夹中。

在Default Library Name 中为我们的设计编译到哪一个库中。

点击OK会出现下图所示的界面。

四、为工程添加文件Create New File 为工程添加新建的文件;Add Existing File为工程添加已经存在的文件;Create Simulation为工程添加仿真;Create New Folder为工程添加新的目录。

这里我们点击Create New File,来写仿真代码。

输入File Name,再输入文件类型为Verilog (默认为VHDL,Modelsim也可以仿真System Verilog代码),Top Level表示文件在刚才所设定的工程路径下。

点击OK,并点击Close关闭Add items to the Project窗口。

这时候在Workspace窗口中出现了Project选项卡,里面有8_11.v,其状态栏有一个问号,表示未编译,双击该文件,这时候出现8_11.v的编辑窗口,可以输入我们的Verilog代码。

五、编写Verilog代码写完代码后,不能马上就编译,要先File->Save保存,否则,编译无效。

然后选择Compile->Compile All。

Transcript脚本窗口出现一行绿色字体Compile of 8_11.v was successful. 说明文件编译成功,并且该文件的状态栏显示绿色的对号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Modelsim 6.0 使用教程1. Modelsim简介Modelsim仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。

但是它也有缺点,就是它里面所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到modelsim就可以用,它假设使用者对当前操作的前期准备工作都已经很熟悉,所以初学者往往不知道如何做当前操作的前期准备。

2.安装同许多其他软件一样,Modelsim SE同样需要合法的License,通常我们用Kengen产生license.dat。

⑴.解压安装工具包开始安装,安装时选择Full product安装。

当出现InstallHardware Security Key Driver时选择否。

当出现Add Modelsim To Path选择是。

出现Modelsim License Wizard时选择Close。

⑵.在C盘根目录新建一个文件夹flexlm,用Keygen产生一个License.dat,然后复制到该文件夹下。

⑶.修改系统的环境变量。

右键点击桌面我的电脑图标,属性->高级->环境变量->(系统变量)新建。

按下图所示内容填写,变量值内如果已经有别的路径了,请用“;”将其与要填的路径分开。

LM_LICENSE_FILE = c:\flexlm\license.dat⑷.安装完毕,可以运行。

3. Modelsim仿真方法Modelsim的仿真分为前仿真和后仿真,下面先具体介绍一下两者的区别。

3.1 前仿真前仿真也称为功能仿真,主旨在于验证电路的功能是否符合设计要求,其特点是不考虑电路门延迟与线延迟,主要是验证电路与理想情况是否一致。

可综合FPGA代码是用RTL级代码语言描述的,其输入为RTL级代码与Testbench.3.2 后仿真后仿真也称为时序仿真或者布局布线后仿真,是指电路已经映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,是否存在时序违规。

其输入文件为从布局布线结果中抽象出来的门级网表、Testbench和扩展名为SDO或SDF的标准时延文件。

SDO或SDF的标准时延文件不仅包含门延迟,还包括实际布线延迟,能较好地反映芯片的实际工作情况。

一般来说后仿真是必选的,检查设计时序与实际的FPGA运行情况是否一致,确保设计的可靠性和稳定性。

3.3 Modelsim仿真的基本步骤Modelsim的仿真主要有以下几个步骤:建立库并映射库到物理目录;编译原代码(包括Testbench;执行仿真。

3.3.1 建立库在执行一个仿真前先建立一个单独的文件夹,后面的操作都在此文件下进行,以防止文件间的误操作。

然后启动Modelsim将当前路径修改到该文件夹下,修改的方法是点File->Change Directory选择刚刚新建的文件夹见下图。

仿真库是存储已编译设计单元的目录,modelsim中有两类仿真库,一种是工作库,默认的库名为work,另一种是资源库。

Work库下包含当前工程下所有已经编译过的文件。

所以编译前一定要建一个work库,而且只能建一个work库。

资源库存放work库中已经编译文件所要调用的资源,这样的资源可能有很多,它们被放在不同的资源库内。

例如想要对综合在cyclone芯片中的设计做后仿真,就需要有一个名为cyclone_ver的资源库。

映射库用于将已经预编译好的文件所在的目录映射为一个modelsim可识别的库,库内的文件应该是已经编译过的,在Workspace窗口内展开该库应该能看见这些文件,如果是没有编译过的文件在库内是看不见的。

建立仿真库的方法有两种。

一种是在用户界面模式下,点File->New->Library出现下面的对话框,选择a new library and a logical mapping to it,在Library Name内输入要创建库的名称,然后OK,即可生成一个已经映射的新库。

另一种方法是在Transcript窗口输入以下命令:vlib work/* 库名 */vmap work work/* 映射的逻辑名称 存放的物理路径 */ 如果要删除某库,只需选中该库名,点右键选择Delete即可。

需要注意的是不要在modelsim外部的系统盘内手动创建库或者添加文件到库里;也不要modelsim用到的路径名或文件名中使用汉字,因为modelsim可能无法识别汉字而导致莫名其妙的错误。

3.3.2 编写与编译测试文件在编写Testbench之前最好先将要仿真的目标文件编译到工作库中,点Compile->Compile或,将出现下面的对话框,在Library中选择工作库,在查找范围内找到要仿真的目标文件,然后点Compile和Done。

或在命令行输入vlog fulladder.v。

此时目标文件已经编译到工作库中,在Library中展开工作库会发现该文件。

当对要仿真的目标文件进行仿真时需要给文件中的各个输入变量提供激励源,并对输入波形进行的严格定义,这种对激励源定义的文件称为Testbench,即测试台文件。

下面先讲一下Testbench的产生方法。

我们可以在modelsim内直接编写Testbench,而且modelsim还提供了常用的各种模板。

具体步骤如下:⑴.执行File->New->Source->verilog,或者直接点击工具栏上的新建图标,会出现一个verilog文档编辑页面,在此文档内设计者即可编辑测试台文件。

需要说明的是在Quartus中许多不可综合的语句在此处都可以使用,而且testbench只是一个激励源产生文件,只要对输入波形进行定义以及显示一些必要信息即可,切记不要编的过于复杂,以免喧宾夺主。

⑵.Modelsim提供了很多Testbench模板,我们直接拿过来用可以减少工作量。

点View->Source->Show Language Templates然后会出现一个加载工程,接着你会发现在刚才的文档编辑窗口左边出现了一个Language Templates窗口,见下图。

展开Verilog项,双击Creat Testbench会出现一个创建向导,见下图。

选择Specify Design Unit工作库下的目标文件,点Next,出现下面对话框可以指定Testbench的名称以及要编译到的库等,此处我们使用默认设置直接点Finish。

这时在Testbench内会出现对目标文件的各个端口的定义还有调用函数接下来,设计者可以自己往Testbench内添加内容了,然后保存为.v格式即可。

按照前面的方法把Testbench文件也编译到工作库中。

3.3.3 执行仿真因为仿真分为前仿真和后仿真,下面分别说明如何操作。

⑴.前仿真前仿真,相对来说是比较简单的。

在上一步我们已经把需要的文件编译到工作库内了,现在我们只需点simulate->Start Simulation或快捷按钮会出现start simulate对话框。

点击Design标签选择Work库下的Testbench文件,然后点OK即可,也可以直接双击Testbench文件,此时会出现下面的界面。

在主界面中会多出来一个Objects窗口,里面显示Testbench里定义的所有信号引脚,在Workspace里也会多出来一个Sim标签。

右键点击fuladder_tb.v,选择Add->Add to Wave,如下图所示。

然后将出现Wave窗口,现在就可以仿真了,见下图。

形也将继续延伸,见下图.若点,则仿真一直执行,直到点才停止仿真。

也可以在命令行输入命令:run @1000则执行仿真到1000ns,后面的1000也可以是别的数值,设计者可以修改。

在下一次运行次命令时将接着当前的波形继续往后仿真。

对于复杂的设计文件,最好是自己编写testbench文件,这样可以精确定义各信号以及各个信号之间的依赖关系等,提高仿真效率。

对于一些简单的设计文件,也可以在波形窗口自己创建输入波形进行仿真。

具体方法是双击work库里的目标仿真文件fulladder.v,然后点workspace窗口中出现的sim标签,右键点击fuladder,选择Add->Add to Wave,如下图所示。

然后将出现Wave窗口。

在wave窗口中选中要创建波形的信号,如此例中的a,然后右键点击,选择Create/Modify/Wave项出现下面的窗口,在Patterns中选择输入波形的类型,然后分别在右边的窗口中设定起始时间、终止时间以及单位,再点Next出现下面的窗口,我们把初始值的HiZ改为0,然后修改时钟周期和占空比,然后点Finish.接着继续添加其他输入波形,出现下面的结果。

前面出现的红点表示该波形是可编辑的。

后面的操作与用testbench文本仿真的方法相同如果设计者只想查看指定信号的波形,可以先选中objects窗口中要观察的信号,然后点右键选择Add to Wave->Selected signals,见下图,那么在Wave窗口中只添加选中的信号。

如果要保存波形窗口当前信号的分配,可以点File->Save->Format,在出现的对话框中设置保存路径及文件名,保存的格式为.do文件。

如果是想导出自己创建的波形(在文章最后有详细的解释)可以选择File->Export Waveform在出现的对话框中选择EVCD File并进行相关设置即可,如果导入设计的波形选择File->Import ECVD即可。

在主界面中点View->Debug Windows->Dataflow可以看到会出现dataflow窗口,在objects窗口中拖一个信号到该窗口中,你会发现在dataflow窗口中出现你刚才选中信号所在的模块,如果双击模块的某一引脚,会出现与该引脚相连的别的模块或者引线,见下图。

在dataflow窗口中点View->Show Wave,会在dataflow窗口中出现一个wave窗口,双击上面窗口中的某一模块,则在下面的wave窗口中出现与该模块相连的所有信号,如果已经执行过仿真,在wave窗口中还会出现对应的波形,见下图。