ModelSim新手使用手册

Modelsim简单教程.

Modelsim入门技术文档单位:深圳大学EDA中心实验室指导老师:徐渊作者:陈战夫rshamozhihu@时间:2010-1-7说明:本文档作为EDA中心研究生modelsim入门用。

分三个章节阐述。

1.modelsim中库的编译1.自己新建一个文件夹,如D:\modelsimpro\counter,将counter.v与counter_tb.v文件拷贝到该文件夹下。

2.点击modelsim的图标,打开modelsim的界面窗口。

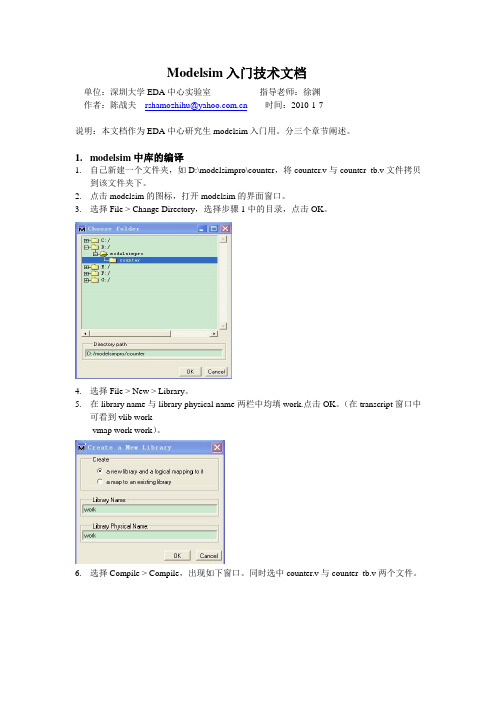

3.选择File > Change Directory,选择步骤1中的目录,点击OK。

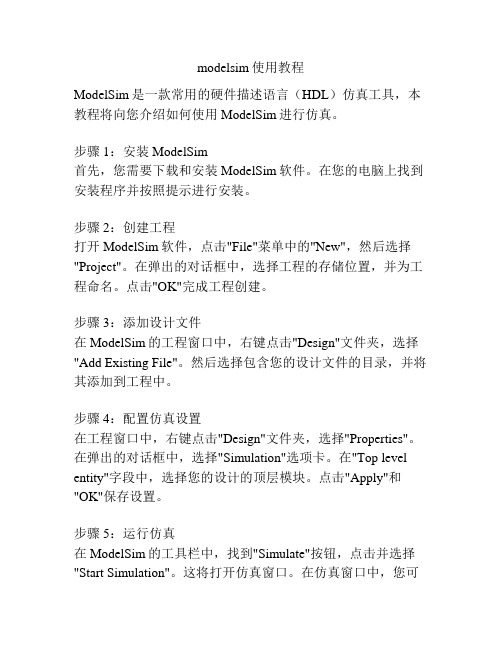

4.选择File > New > Library。

5.在library name与library physical name两栏中均填work.点击OK。

(在transcript窗口中可看到vlib workvmap work work)。

6.选择Compile > Compile,出现如下窗口。

同时选中counter.v与counter_tb.v两个文件。

7.点击compile.再点击done.8.在library标签点击work库前面的“+”号,可看到counter.v与counter_tb.v均在其目录下。

9.双击counter_tb.v可将该设计装载到本次工程库中。

10.选择View > Debug Windows >wave.将弹出波形窗口。

11.在workspace窗口下点击sim标签。

12.右击counter_tb.v,在出现的菜单中选择Add > Add to Wave。

13.在transcript窗口中VSIM>后敲入run 1000.则系统将仿真1000ns.我们可根据波形查看仿真结果。

14.在workspace窗口中点击files标签,鼠标左键双击counter.v,打开counter.v文件。

15.在第10行数字10旁鼠标左键点击一下,可出现一小红点,即断点。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

modelsim使用技巧

modelsim使用技巧ModelSim是一款常用的仿真工具,用于学习、开发和测试各种数字电路和系统设计。

它提供了大量的功能,可以帮助我们更好地进行仿真、调试和性能优化。

但是,对于初学者来说,熟练使用ModelSim可能需要一些时间和实践。

在本文中,我们将介绍一些ModelSim的使用技巧,以帮助读者更好地掌握这个工具。

一、基本操作1.创建工程在ModelSim中,创建工程是第一步。

可以通过File -> New -> Project来创建一个新的工程。

在工程创建过程中,需要指定工作目录、项目名称和工具链等信息。

在创建工程后,可以右键单击仿真文件夹,并选择添加到工程来添加设计文件。

2.添加仿真文件在ModelSim中,添加仿真文件非常简单。

可以将文件拖放到仿真文件夹、使用File -> Add to Project选项或使用命令行方式添加文件。

一旦添加了仿真文件,可以使用filelist命令查看所有添加的文件。

3.编译设计在ModelSim中,编译由两个阶段组成。

第一阶段称为分析阶段,在此阶段中,设计的各个模块被分析、组合并建立数据结构。

第二阶段称为综合阶段,在此阶段中,数据结构被综合成一个整体,并生成仿真网表。

可以通过compile option来指定编译选项,比如-v库等。

4.运行仿真在ModelSim中,可以通过三种方式来运行仿真。

第一种是在命令行中使用run命令,第二种是通过菜单和工具栏选项来启动仿真,第三种是使用脚本方式启动仿真。

在仿真过程中,可以使用wave、add wave、force、release等命令来控制信号的行为。

二、ModelSim高级技巧1.波形窗口波形窗口是ModelSim中最有用的窗口之一。

可以使用Add Wave按钮打开该窗口。

在波形窗口中,可以查看所有信号的变化情况。

可以使用full view、zoom in、zoom out等选项来放大或缩小波形窗口。

modelism简明操作指南

第一章介绍ModelSim的简要使用方法第一课 Create a Project1.第一次打开ModelSim会出现Welcome to ModelSim对话框,选取Create a Project,或者选取File\New\Project,然后会打开Create Project对话框。

2.在Create Project对话框中,填写test作为Project Name;选取路径Project Location作为Project文件的存储目录;保留Default Library Name设置为work。

3.选取OK,会看到工作区出现Project and Library Tab。

4.下一步是添加包含设计单元的文件,在工作区的Project page中,点击鼠标右键,选取Add File to Project。

5.在这次练习中我们加两个文件,点击Add File to Project对话框中的Browse 按钮,打开ModelSim安装路径中的example目录,选取counter.v和tcounter.v,再选取Reference from current location,然后点击OK。

6.在工作区的Project page中,单击右键,选取Compile All。

7.两个文件编译了,鼠标点击Library Tab栏,将会看到两个编译了的设计单元列了出来。

看不到就要把Library的工作域设为work。

8.最后一不是导入一个设计单元,双击Library Tab中的counter,将会出现Sim Tab,其中显示了counter设计单元的结构。

也可以Design\Load design 来导入设计。

到这一步通常就开始运行仿真和分析,以及调试设计,不过这些工作在以后的课程中来完成。

结束仿真选取Design \ End Simulation,结束Project选取File \ Close \ Project。

modelsim的详细使用方法

一、简介ModelSim是一款由美国Mentor Graphics公司推出的集成电路仿真软件,广泛应用于数字电路和系统设计领域。

它提供了强大的仿真和验证功能,能够帮助工程师快速高效地进行电路设计与验证工作。

本文将详细介绍ModelSim的使用方法,以帮助读者更好地掌握这一工具的操作技巧。

二、安装与配置1. 下载ModelSim安装包,并解压到指定目录2. 打开终端,进入ModelSim安装目录,执行安装命令3. 安装完成后,配置环境变量,以便在任何目录下都能够调用ModelSim程序4. 打开ModelSim,进行软件注册和授权,确保软件可以正常运行三、工程创建与管理1. 新建工程:在ModelSim主界面点击“File” -> “New” -> “Project”,输入工程名称和存储路径,选择工程类型和目标设备,点击“OK”完成工程创建2. 添加文件:在工程目录下右键点击“Add Existing”,选择要添加的源文件,点击“OK”完成文件添加3. 管理工程:在ModelSim中可以方便地对工程进行管理,包括文件的增删改查以及工程参数的设置等四、代码编写与编辑1. 在ModelSim中支持Verilog、VHDL等多种硬件描述语言的编写和编辑2. 在ModelSim主界面点击“File” -> “New” -> “File”,选择要新建的文件类型和存储位置,输入文件名称,点击“OK”完成文件创建3. 在编辑器中进行代码编写,支持代码高亮、自动缩进、语法检查等功能4. 保存代码并进行语法检查,确保代码符合规范,没有错误五、仿真与调试1. 编译工程:在ModelSim中进行代码编译,生成仿真所需的可执行文件2. 设置仿真参数:在“Simulation”菜单下选择“S tart Simulation”,设置仿真时钟周期、输入信号等参数3. 运行仿真:点击“Run”按钮,ModelSim将开始对设计进行仿真,同时显示波形图和仿真结果4. 调试设计:在仿真过程中,可以通过波形图和仿真控制面板对设计进行调试,查找并解决可能存在的逻辑错误六、波形查看与分析1. 查看波形:在仿真过程中,ModelSim会生成相应的波形文件,用户可以通过“Wave”菜单查看波形并进行波形分析2. 波形操作:支持波形的放大、缩小、平移、选中等操作,方便用户对波形进行分析和观察3. 波形保存:用户可以将波形结果保存为图片或文本文件,以便日后查阅和分析七、性能优化与验证1. 时序优化:在设计仿真过程中,可以通过观察波形和性能分析结果,对设计进行优化,提高设计的时序性能2. 逻辑验证:通过对仿真的结果进行逻辑验证,确保设计符合预期的逻辑功能3. 时序验证:对设计的时序性能进行验证,确保信号传输和时钟同步的正确性八、项目输出与文档整理1. 输出结果:在仿真和验证完成后,可以将仿真结果、波形图和性能分析结果输出为文本文件或图片,方便后续的文档整理和报告撰写2. 结果分析:对仿真结果和验证结果进行详细的分析,确定设计的性能和功能是否符合设计要求3. 文档整理:根据仿真和验证结果,进行文档整理和报告撰写,为后续的设计和优化工作提供参考九、总结与展望ModelSim作为一款专业的集成电路仿真软件,具有着强大的功能和丰富的特性,可以帮助工程师进行电路设计与验证工作。

modelsim使用方法

modelsim使用方法ModelSim 是一种功能强大的硬件描述语言 (HDL) 模拟工具,支持VHDL和Verilog,可用于设计和验证数字系统。

本文将介绍如何使用ModelSim。

**安装 ModelSim****创建项目**在启动 ModelSim 后,首先需要创建一个新的项目。

选择 "File" 菜单,然后选择 "New" -> "Project"。

在打开的对话框中,选择项目的文件夹和项目名称,然后点击 "OK"。

**添加设计文件和测试文件**在项目中,您需要添加设计文件和测试文件。

选择 "Project" 菜单,然后选择 "Add to Project" -> "Add Files". 在打开的对话框中,选择您的设计文件 (VHDL 或 Verilog) 和测试文件,然后点击 "OK"。

**设置仿真**在编译代码之后,下一步是设置仿真选项。

选择 "Simulate" 菜单,然后选择 "Start Simulation"。

在打开的对话框中,选择您的顶层模块。

您还可以选择以 GUI 模式还是批处理模式运行仿真。

在设置仿真之前,您可以添加信号波形文件以在仿真过程中显示波形。

选择 "Simulate" -> "Wave" -> "Add Waveform". 然后,选择信号波形文件 (.do 或 .vcd),并点击 "OK"。

**运行仿真**设置仿真选项后,您可以开始执行仿真。

通过选择 "Simulate" -> "Run",可以运行单步或连续仿真。

modelsim使用说明

1在quartus中设置第三方仿真工具,选择assignments-settings-eda tool settings-simulatin选择modelsim-verilog2编译工程3编译完成后会在工程目录下生成simulation-modelsim的目录,打开Wave.vo是仿真网表文件,可以用来代替设计文件;.xrf是quartus编译生成的信息文件;.sdo是工程延时信息4、加入仿真库文件:路径C:\altera\quartus50\eda\sim_lib220model.v:带有用户原语类型的quartus自带的ip核的库文件altera_mf.v:quartus自带的ip核的库文件cyclone_atoms.v:相应系列的器件库在本例中需要添加altera_mf.v,cyclone_atoms.v5、编写测试模块6、把这些文件粘贴到刚才生成的目录中7、打开modelsim8、选择file-new-project9、指定工程名称,路径,工作目录10、添加设计文件(1)(2)(3)(4)11、编译工程全部编译功能仿真12、修改wave.vo文件把延时信息注释掉//initial $sdf_annotate("WA VE_v.sdo");13、重新编译wave.vo14、选择simulate开始仿真15、选择顶层模块,然后确定16、右键选择添加信号到波形图17、在命令行中敲入run 1ms回车,开始仿真18、观察波形二进制显示十进制显示没有延时时序仿真19、把wave.vo的修改过的注释改回来,重新编译20选择simulate21、选择sdf标签22、加入.sdo文件,把下面的sdf options都选中23、选择ok进行仿真24、和功能仿真一样加入波形图,仿真25、看延时。

Modelsim详细使用教程

Modelsim详细使用教程一、打开Medelsim双击桌面快捷方式,出现下图所示界面,如果上一次使用ModelSim建立过工程,这时候会自动打开上一次所建立的工程;二、建立工作库点击File->New->Library,输入Library Name,点击OK,就能看见新建的库。

三、建立工程点击File->New->Project,输入Project Name,在Project Location 中输入工程保存的路径,建议在Library所在文件夹中。

在Default Library Name 中为我们的设计编译到哪一个库中。

点击OK会出现下图所示的界面。

四、为工程添加文件Create New File 为工程添加新建的文件;Add Existing File为工程添加已经存在的文件;Create Simulation为工程添加仿真;Create New Folder为工程添加新的目录。

这里我们点击Create New File,来写仿真代码。

输入File Name,再输入文件类型为Verilog (默认为VHDL,Modelsim也可以仿真System Verilog代码),Top Level表示文件在刚才所设定的工程路径下。

点击OK,并点击Close关闭Add items to the Project窗口。

这时候在Workspace窗口中出现了Project选项卡,里面有8_11.v,其状态栏有一个问号,表示未编译,双击该文件,这时候出现8_11.v的编辑窗口,可以输入我们的Verilog代码。

五、编写Verilog代码写完代码后,不能马上就编译,要先File->Save保存,否则,编译无效。

然后选择Compile->Compile All。

Transcript脚本窗口出现一行绿色字体Compile of 8_11.v was successful. 说明文件编译成功,并且该文件的状态栏显示绿色的对号。

modelsim使用入门(VHDL_

Quartus

这里用的是 modelsim-altera(6.6d) 版本,与 quartus II 11.0 搭配。据说 Altera 公司推出的

Quartus 软件不同版本对应不同的 modelsim,相互之间不兼容。 某些功能齐全的 modelsim 版 本可以进行两种语言的混合编程, modelsim-altera 只能支持一种语言进行编程( VHDL 或

; ca88会员登录入口 https:///dongmanmanhua ca88会员登录入口 ;

; ca88会员登录入口 https:///xiaohuajijin ca88会员登录入口 ;

; ca88会员登录入口 https:///nongyezaixian ca88会员登录入口 ;

std_logic;

div :out

std_logic);

end component;

采用 50MHZ 时钟频率

命名 div10_tb

signal clk :std_logic:='0'; signal div :std_logic:='0'; constant clk_period:time:=20 ns;

begin

u1: div10 port map (clk=>clk,div=>div);

process begin

wait for clk_period/2; clk<='1';

wait for clk_period/2; clk<='0';

end process;

end;

保存为 div10_tb.vhd 文件,见图下。

port(clk :in std_logic;

ModelSim简明使用教程

ModelSim6.1入门教程因为本人在初学Verilog 编程语言时,觉得很难上手的是使用ModelSim ,所以今天和大家交流一下,好了,闲话不多说了,我们开始吧!1,打开ModelSim 的画面如下:标准的windows 界面,最上面是菜单栏,以及菜单栏的一些快捷方式。

左边是工作空间,里面显示的是一些库文件。

右边是编辑区,最下面是交互区,可以通过命令完成所有的操作。

我们在此只讲一些基本的命令输入,以完成仿真。

2,建立工程,如图所示:单击Project 之后,画面如下:菜单快捷栏工作空间栏编辑栏仿真交互栏在图中Project Name中输入AND_2,这也是我们建立的第一个工程,路径选择如下图所示,默认库名我们用默认的work。

这一步完成之后,点击ok,如下图:单击ok后,如下图:其实应该没有右边的那个Creat Project File选择框,只有左边的Add items to the Project,呵呵,在此偷懒了。

单击Add items to the Project中的Creat New File(如果你已经写好了代码,可以通过点击Add Existing Flie添加),如下图:在File Name中输入AND_2,在Add file as type选项中选择Verilog,其他的使用默认即可。

单击ok。

在工作空间中添加了名为AND_2的文件,如图。

状态是“?”,说明没有通过编译。

其实咱还没开始写代码呢!好了,现在开始正式写代码了。

双击图中AND_2文件那一行的任何地方,就会打开右边的编辑区,和其他IDE 工具一样,使用编辑器,输入如下代码:module AND_2(clk,rst,A,B,C);input clk,rst,A,B;output C;reg C;always@(posedge clk or negedgeif(!rst)C <=1'b0;elseC <=A&B;Endmodule 输入完成后,单击保存。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ModelSim最基本的操作,初次使用ModelSim的同学,可以看看,相互学习。

无论学哪种语言,我都希望有个IDE来帮助我创建一个工程,管理工程里的文件,能够检查我编写代码的语法错误,能够编译运行出现结果,看看和预期的结果有没有出入,对于Verilog语言,我用过Altera的Quartus II,Xilinx的ISE,还有ModelSim(我用的是Altera 官网的ModelSim_Altera),甚至MAXPlus II,不过感觉这软件太老了,建议还是前三者吧。

学Verilog,找一本好书很重要,参考网友的建议,我也买了一本夏宇闻老师的《Verilog 数字系统设计教程》,用Quartus II来编写代码,个人觉得它的界面比ISE和ModelSim友好,我一般用它编写代码综合后自动生成testbench,然后可以直接调用ModelSim仿真,真的很方便,但学着学着,发现夏老师书里的例子很多都是不可综合的,比如那些系统命令,导致很多现象都发现不了,偶然间我直接打开了ModelSim,打开了软件自带的英文文档,步骤是:Help ->PDF Documentation->Tutorial如下所示:

打开文档的一部分目录:

往下读发现其实ModelSim可以直接创建工程,并仿真的。

下面以奇偶校验为例叙述其使用过程(当然前提是你在Altera官网下载了ModelSim并正确安装了)。

1.打开软件,新建一个工程,并保存到自定义的目录中(最好别含中文路径)

2.点击Project,弹出窗口问是否关闭当前工程,点击Yes,接着又弹出如下窗口

我个人的习惯是把Project Name和Default Library Name写成一样,自己定义Project Location。

又弹出如下窗口:

3.点击Close(我的版本不能Create New File,其实新建好了工程一样可以新建.v文件),然后点击屏幕下方的Project标签:

如果一开始不是如上图所示的界面,那么可以点击如下图所示红色标记的按键变成上图界面:

4.在屏幕空白处右击鼠标,出现如下窗口:

5.现在可以选New File或者Existing File(首先你已经编写好了)。

这里选择New File,写上File Name,勾选好type,这里选Verilog语言:

6.双击parity.v文件,可以进行编辑了

然后编写代码:

// **************************************************************

//目标:求一个八位二进制数的奇校验位

//作者: 杨海平江南大学物联网工程学院

//日期: 2015/4/15

//版本: V 1.0

//摘要: 奇校验是指如果一个二进制数有奇数个1,则其奇校验位为0,否则为1 // **************************************************************

module parity(rst_n,dat_i,dat_o);

input rst_n;

input[7:0] dat_i;

output dat_o;

assign dat_o = !rst_n ? 1'b0 : ^dat_i ? 1'b0 : 1'b1;

endmodule

和编写parity.v文件一样,编写测试脚本,名字为paritytst.v:

测试代码如下:

`timescale 1 ps/ 1 ps

module paritytst();

reg rst_n;

reg[7:0] dat_i;

wire dat_o;

parity i1(.rst_n(rst_n),

.dat_i(dat_i),

.dat_o(dat_o)

);

initial

begin

rst_n <= 0;

#5 rst_n <= 1;dat_i <= 8'b00110011;

#20 dat_i <= 8'b00110011;

#20 dat_i <= 8'b00100011;

#20 dat_i <= 8'b00111011;

#20 $stop;

end

endmodule

7.左击任意文件,选中它,然后右击选择编译全部

点击屏幕下方的Transcript,可以查看文件编译情况

如果出错,则出现如下提示,双击任意一段红色字段,都会弹出错误信息,帮助你修改代码

修改好了代码之后,就可以进行仿真了

点击ok,再点击屏幕下方的sim标签(新出现的)

再点击i1左边的"+"号,右击我选中的蓝色部分,

点击Add Wave,再点击屏幕下方的

出现下图界面:

全部选中它们,右击:

点击Add Wave,然后点击屏幕下方的wave:

出现如下界面:

再点击simulate:

Run all后就出现仿真图形了(在wave标签下显示,图形可用键盘上的"+","-"进行放大缩小):

ok,大功告成!!!。