Modelsim 中文

详细介绍modelsim的使用方法

ModelSim产品简介(13)

Signals 窗口

• 紧跟Structure窗口 – 显示Structure窗口的当前层HDL项的名称和 值 • 层次 - (+)可展开的, (-)已展开的 • VHDL 信号,Verilog 线网, 寄存器变量和已命名 的时间

• 可拖放到Wave和List窗口

ModelSim产品简介(14)

ModelSim产品简介(11)

Process 窗口 • 显示外部和内部的处理 • View -> Active

– 显示当前仿真众所有在执行前预定的 processes

• View -> In Region

– 显示在Structure 窗口中选定的所有 processes 的名字

ModelSim产品简介(12)

ModelSim产品简介(17)

Variables窗口

• 列出 HDL 项的名称 – VHDL – 常数, generics 和变量 – Verilog – 寄存器变量 • 到当前过程的路径被显示在左下 • 树层次 - (+)可展开的, (-)已展开的 • 可改变 – 选择HDL项改变值 • 可浏览 – 在Wave 或 List 窗口 或 log 文件的项 – 选择变量或层中的变量

ModelSim产品简介(9)

Source 窗口

ModelSim产品简介(10)

Source 窗口 • 描述

– 显示所选的HDL项的信息

• 检查

– 显示所选HDL项当前仿真值

1) 高亮信号, 变量, 常数, 线网, 或寄存器 2) 右击鼠标 (或 Object Menu -> Examine/Description)

ModelSim/XE

modelsim的.do语法

在进行 .do 语法讨论之前,首先需要了解 ModelSim 是什么,以及它的作用和特点。

ModelSim 是 Mentor Graphics 公司出品的一款功能强大的 HDL 仿真工具,广泛应用于数字电子电路设计和验证领域。

它支持 Verilog、VHDL 和 SystemVerilog 三种主流硬件描述语言,可以帮助工程师们进行仿真、调试和验证设计的正确性和功能性。

对于 .do 语法,它是 ModelSim 中常用的一种脚本语言,可以用于自动化执行一系列的仿真操作,提高工作效率和减少重复性工作。

在实际的工程项目中,合理地使用 .do 文件能够极大地简化仿真流程,并且方便地进行批量的仿真测试。

熟练掌握 .do 语法对于提高工作效率和质量是非常重要的。

下面通过几个方面来深入探讨和解析 .do 语法在 ModelSim 中的应用:1. .do 文件的基本结构和语法在编写 .do 文件时,需要了解其基本结构和语法规则。

可以用“#”表示注释,用“run”命令表示运行仿真等。

还可以在 .do 文件中引入其他 .do 文件,实现模块化的脚本编写,提高代码的重用性和可维护性。

2. .do 文件在仿真流程中的应用在实际工程项目中,通常会有多个仿真测试用例需要执行,使用 .do文件可以很方便地对这些测试用例进行批量执行。

.do 文件也可以用于设置仿真的参数,比如时钟周期、仿真时长等,从而更加灵活地进行仿真调试。

3. .do 文件与仿真结果的分析和处理除了执行仿真测试,.do 文件还可以用于对仿真结果进行分析和处理。

可以在 .do 文件中加入分析波形的命令,或者导出仿真波形和数据。

这些操作可以帮助工程师更加直观地了解设计的性能和行为。

总结回顾:通过以上的介绍和分析,我们可以看到 .do 文件在 ModelSim 中的应用非常广泛,对于提高工作效率和质量有着重要的作用。

合理地使用 .do 文件可以简化仿真流程,减少重复性工作,以及方便地进行批量的仿真测试。

Modelsim使用说明

Modelsim 使用简明指南1 前言作为一种简单易用,功能强大的逻辑仿真工具,Modelsim 具有广泛的应用。

这里对ModelSim 作一个入门性的简单介绍。

首先介绍ModelSim 的代码仿真,然后介绍门级仿真和时序验证。

和时序验证。

2 代码仿真在完成一个设计的代码编写工作之后,可以直接对代码进行仿真,检测源代码是否符合功能要求。

这时,仿真的对象为HDL 代码,比较直观,速度比较快,可以进行与软件相类似的多种手段的调试(如单步执行等)。

在设计的最初阶段发现问题,在设计的最初阶段发现问题,可以节省大量的精力。

可以节省大量的精力。

2.1 代码仿真需要的文件1.设计HDL 源代码:源代码:新建一个“文本文档”文件,在记事本中输入HDL 源代码,使用V erilog 语言编程。

语言编程。

2.测试激励代码:.测试激励代码:在同一个文件中,根据设计要求输入/输出的激励程序,由于不需要进行综合,书写具有很大的灵活性。

有很大的灵活性。

3.保存该文件后退出,然后重命名该文件,.保存该文件后退出,然后重命名该文件,使该文件后缀名由使该文件后缀名由.txt 变为.v 。

如:t81.v 。

4. 该文件保存在你所建立的工作目录中,如:D\VLSItext\t1如果要修改该文件,仍然可以选择用仍然可以选择用记事本记事本打开编辑再保存,记事本相当于是一源代码输入软件。

输入软件。

注:所有的文件名及目录名均要求是英文,无中文字符。

2.2 代码仿真步骤1.建立工程:在ModelSim 中建立Project 。

如图2.1所示,点击File ðNew ðProject ,得到Creata Project 的弹出窗口,如图2.2所示。

在Project Name 栏中填写你的项目名字,建议和你的顶层文件名字一致,如t81。

Project Location 是你的项目目录,你可通过Brose 按钮来选择或改变,建议项目目录选择为你所保存源代码的目录,如:D\VLSItext\t1。

ModelSim和QuestaSim功能简介及应用

ModelSim是工业界最优秀的语言仿真器,它提供最友好的调试环境,是作FPGA、ASIC设计的RTL级和门级电路仿真的首选。

它支持PC和UNIX、LINUX平台,是单一内核支持VHDL和Verilog混合仿真的仿真器。

它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真,编译仿真速度业界最快,编译的代码与平台无关,便于保护IP核,具有个性化的图形界面和用户接口,为用户加快调试提供强有力的手段。

全面支持VHDL和Verilog语言的IEEE 标准,以及IEEE VITAL 1076.4-95 标准,支持C语言功能调用, C的模型,基于SWIFT的SmartModel逻辑模型和硬件模型。

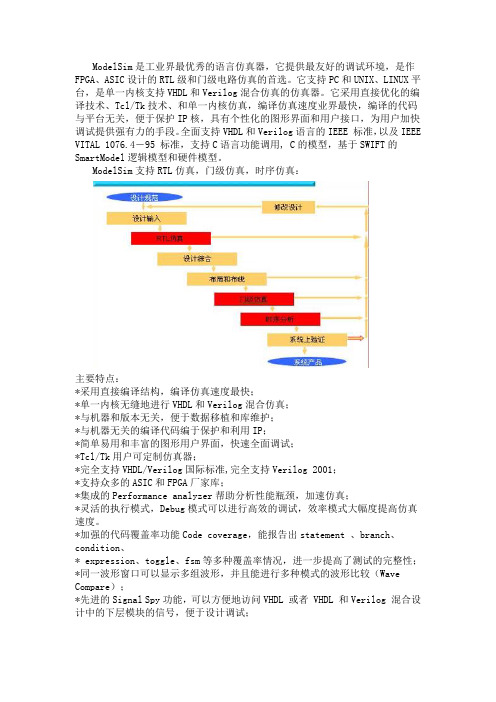

ModelSim支持RTL仿真,门级仿真,时序仿真:主要特点:*采用直接编译结构,编译仿真速度最快;*单一内核无缝地进行VHDL和Verilog混合仿真;*与机器和版本无关,便于数据移植和库维护;*与机器无关的编译代码编于保护和利用IP;*简单易用和丰富的图形用户界面,快速全面调试;*Tcl/Tk用户可定制仿真器;*完全支持VHDL/Verilog国际标准,完全支持Verilog 2001;*支持众多的ASIC和FPGA厂家库;*集成的Performance analyzer帮助分析性能瓶颈,加速仿真;*灵活的执行模式,Debug模式可以进行高效的调试,效率模式大幅度提高仿真速度。

*加强的代码覆盖率功能Code coverage,能报告出statement 、branch、condition、* expression、toggle、fsm等多种覆盖率情况,进一步提高了测试的完整性;*同一波形窗口可以显示多组波形,并且能进行多种模式的波形比较(Wave Compare);*先进的Signal Spy功能,可以方便地访问VHDL 或者 VHDL 和Verilog 混合设计中的下层模块的信号,便于设计调试;*支持加密IP;*集成的 C调试器,支持用C 语言完成测试平台和模块;支持64位的OS; ModelSim用户界面:ModelSim设计流程:ModelSim coverage验证:ModelSim Dataflow窗口QuestaSim是第一个基于标准的单核验证引擎,集成了一个HDL模拟器,一个约束求解器,一个判断引擎,功能覆盖,以及一个通用的用户界面。

ModelSim

先进功能

Complete Flow Solution for Multi-Million Gate FPGA Design 2002 – SH slide 3 Copyright 1999-2002, Mentor Graphics.

1) 高亮选中 高亮选中signal, variable, constant, wire, 或reg 2) 用鼠标器右键点击 或者 选择菜单Object -> 选择菜单 Examine/Description

Complete Flow Solution for Multi-Million Gate FPGA Design 2002 – SH

slide 12

Copyright 1999-2002, Mentor Graphics.

结构(structure)窗口

设计结构的层次化视图 – VHDL(方)- Package, component实例,generate和 block声明 – Verilog(圆)- module实例,命名的 fork,命名的begin,task和 function – 实例标号, entity/module, architecture – 作为source和signals窗口的当前 区域,更新process和variables窗 口

slide 16 Copyright 1999-2002, Mentor Graphics.

Complete Flow Solution for Multi-Million Gate FPGA Design 2002 – SH

ModelSim使用的一点心得体会

ModelSim使用的一点心得- -1、至今还没有弄明白为什么要用ModelSim,因为看波形Quartus II自带的工具就可以了啊。

2、我刚刚接触modelsim,我想大多数菜鸟跟我一样,看过如何使用ModelSim的介绍,说句实话,那些介绍写的都太过简单,仿佛大家都不屑写上一些比较“弱智”的步骤,恰恰就是这些看似累赘的步走,难为我好久。

教程上都写道,modelsim的简单使用方法如下:建立库- 影射库到物理目录- 编译代码- 启动仿真。

首先建立库就叫我头晕。

库的概念用在这儿实在不合适,把我吓坏了,也就没心思看下一步了。

在我看来,教程应该这么写:<1> 建立一个目录modelsimStudy。

用任何文本编辑器编辑一个简单的例子程序,比如计数器counter.vhd。

有clk、ena、reset输入,cnt作为输出。

<2> 打开Modelsim,首先create project,工程名随意取了,比如命名为test,目录设在modelsimStudy下,默认的库work不变(这样就不用管什么建立库之类的东西了)。

然后add existing file,把counter.vhd加入当前工程。

<3> 编译这个文件,通过之后,work下面会出现counter这个实体。

然后选中它,右键,simulate(左键双击也可)。

<4> ModelSim有很多窗口(新手就怕这个),一开始只要选择view下面的objects 和wave窗口就行了。

旧版的signal窗口在6.0的版本改名为Objects(这个我是摸索了好久才发现的,是不是太笨了?)。

wave窗口刚打开时是空的,需要在objects窗口的add -> wave -> signals in region。

这时,wave上就有clk\ ena \ reset等信号了。

<5> 我们给clk来个输入激励,在object窗口中选中clk,右键选clock,给它定义个时钟。

modelsim使用教程

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

modelsim的详细使用方法

一、简介ModelSim是一款由美国Mentor Graphics公司推出的集成电路仿真软件,广泛应用于数字电路和系统设计领域。

它提供了强大的仿真和验证功能,能够帮助工程师快速高效地进行电路设计与验证工作。

本文将详细介绍ModelSim的使用方法,以帮助读者更好地掌握这一工具的操作技巧。

二、安装与配置1. 下载ModelSim安装包,并解压到指定目录2. 打开终端,进入ModelSim安装目录,执行安装命令3. 安装完成后,配置环境变量,以便在任何目录下都能够调用ModelSim程序4. 打开ModelSim,进行软件注册和授权,确保软件可以正常运行三、工程创建与管理1. 新建工程:在ModelSim主界面点击“File” -> “New” -> “Project”,输入工程名称和存储路径,选择工程类型和目标设备,点击“OK”完成工程创建2. 添加文件:在工程目录下右键点击“Add Existing”,选择要添加的源文件,点击“OK”完成文件添加3. 管理工程:在ModelSim中可以方便地对工程进行管理,包括文件的增删改查以及工程参数的设置等四、代码编写与编辑1. 在ModelSim中支持Verilog、VHDL等多种硬件描述语言的编写和编辑2. 在ModelSim主界面点击“File” -> “New” -> “File”,选择要新建的文件类型和存储位置,输入文件名称,点击“OK”完成文件创建3. 在编辑器中进行代码编写,支持代码高亮、自动缩进、语法检查等功能4. 保存代码并进行语法检查,确保代码符合规范,没有错误五、仿真与调试1. 编译工程:在ModelSim中进行代码编译,生成仿真所需的可执行文件2. 设置仿真参数:在“Simulation”菜单下选择“S tart Simulation”,设置仿真时钟周期、输入信号等参数3. 运行仿真:点击“Run”按钮,ModelSim将开始对设计进行仿真,同时显示波形图和仿真结果4. 调试设计:在仿真过程中,可以通过波形图和仿真控制面板对设计进行调试,查找并解决可能存在的逻辑错误六、波形查看与分析1. 查看波形:在仿真过程中,ModelSim会生成相应的波形文件,用户可以通过“Wave”菜单查看波形并进行波形分析2. 波形操作:支持波形的放大、缩小、平移、选中等操作,方便用户对波形进行分析和观察3. 波形保存:用户可以将波形结果保存为图片或文本文件,以便日后查阅和分析七、性能优化与验证1. 时序优化:在设计仿真过程中,可以通过观察波形和性能分析结果,对设计进行优化,提高设计的时序性能2. 逻辑验证:通过对仿真的结果进行逻辑验证,确保设计符合预期的逻辑功能3. 时序验证:对设计的时序性能进行验证,确保信号传输和时钟同步的正确性八、项目输出与文档整理1. 输出结果:在仿真和验证完成后,可以将仿真结果、波形图和性能分析结果输出为文本文件或图片,方便后续的文档整理和报告撰写2. 结果分析:对仿真结果和验证结果进行详细的分析,确定设计的性能和功能是否符合设计要求3. 文档整理:根据仿真和验证结果,进行文档整理和报告撰写,为后续的设计和优化工作提供参考九、总结与展望ModelSim作为一款专业的集成电路仿真软件,具有着强大的功能和丰富的特性,可以帮助工程师进行电路设计与验证工作。

modelsim使用方法

modelsim使用方法ModelSim 是一种功能强大的硬件描述语言 (HDL) 模拟工具,支持VHDL和Verilog,可用于设计和验证数字系统。

本文将介绍如何使用ModelSim。

**安装 ModelSim****创建项目**在启动 ModelSim 后,首先需要创建一个新的项目。

选择 "File" 菜单,然后选择 "New" -> "Project"。

在打开的对话框中,选择项目的文件夹和项目名称,然后点击 "OK"。

**添加设计文件和测试文件**在项目中,您需要添加设计文件和测试文件。

选择 "Project" 菜单,然后选择 "Add to Project" -> "Add Files". 在打开的对话框中,选择您的设计文件 (VHDL 或 Verilog) 和测试文件,然后点击 "OK"。

**设置仿真**在编译代码之后,下一步是设置仿真选项。

选择 "Simulate" 菜单,然后选择 "Start Simulation"。

在打开的对话框中,选择您的顶层模块。

您还可以选择以 GUI 模式还是批处理模式运行仿真。

在设置仿真之前,您可以添加信号波形文件以在仿真过程中显示波形。

选择 "Simulate" -> "Wave" -> "Add Waveform". 然后,选择信号波形文件 (.do 或 .vcd),并点击 "OK"。

**运行仿真**设置仿真选项后,您可以开始执行仿真。

通过选择 "Simulate" -> "Run",可以运行单步或连续仿真。

ModelsimSETutorial的翻译

《Modelsim SE Tutorial》的翻译第1课创建一个projectproject是关于HDL设计的一个集合,它减少了与工具的交互,便于组织文件和仿真设置。

Project至少有一个work库和一个存储于.mpf文件中的会话状态。

一个project还可以包括:✧HDL源文件或对源文件的引用;✧其他文件如README文件,或其他project文件;✧本地库;✧对全局库的引用。

1.启动Modelsim用快捷图标,或从开始菜单启动,或从DOS提示符运行Modelsim.exe。

当出现Welcome画面时,单击“Close”按钮,将其关闭,则进入Modelsim 的Main窗口。

2.创建一个project在Main窗口中执行File/New/Project菜单命令,会弹出一个“Create Project”对话框,如图所示,键入Project名(这里起名为test),选择其存储路径为当前工作目录(即源文件所在目录D:\Modelsim_5.6\examples\projects\V erilog),缺省的库名为work。

单击“OK”按钮,则在Main窗口的工作区域会出现一个空白的Project窗口,并出现“Add Items to the project”对话框。

3.在Project中加入文件若源文件已存在,则单击“Add Existing File”,会弹出一个“Add file to project”对话框,单击Browse按钮选择需要加入的文件(这里选择D:\Modelsim_5.6\examples\projects\V erilog下的8位加法计数器counter.v及其测试文件tcounter.v),选中“Reference from current location”单选钮,单击“OK”。

若源文件不存在,则单击“Create New File”,或执行File/New/Sourse/V erilog 菜单命令,自行编写源程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

需要库在工作目录里没有定位 用vmap命令

21

2

映射逻辑库名

语法: vmap <logical_name> <directory_path>

UI) 从主菜单: Design -> Browse Libraries Design -> Create a New Library Cmd) 从主体的记录窗口: ModelSim> vmap my_work c:/my_design/my_lib

ModelSim 使用教程

1

典型的PLD设计流程

2

典型的PLD流程

设计规范 修改设计 设计输入 RTL仿真 设计综合 布局和布线 门级仿真 时序分析 系统上验证 系统产品

3

典型的PLD设计流程

设计输入

– 设计的行为或结构描述

– 文件按出现的顺序被编译 – Compilation order/dependencies (next slide)

‘87 VHDL是缺省的

– UI) 用Default Options 按钮设为‘93 – Cmd) 用 -93 选项(必须是第一个参数)

缺省编译到工作库

– 例如. Vcom -93 my_design.vhd

19

建立库(UI)

选择 a new library only 和 输入库名

这个命令在局部目录 建立一个库子目录

-> vlib lpm_sim

20

映射逻辑库名

必须映射一个逻辑库名到库路径(定位)

– 在库路径里的文件必须已经被编译 – 支持相对的, 绝对的, 和软件路径名

在信息上双击,引起 错误的代码在 Source 窗口被点亮

32

4

启动仿真器

UI) Design -> Load New Design Cmd) vsim -lib <library_name> <top_level_design> VHDL

– vsim top_entity top_architecture • 仿真 Entity/Architecture 对 • 也能选择一个结构

门级仿真 (ModelSim)

– 时序仿真 – 验证设计一旦编程或配置将能在目标工艺里工作 – 可能要求编辑设计

时序分析 验证合乎性能规范

– 可能要求编辑设计

版图设计

– 仿真版图设计 – 在板编程和测试器件

5

ModelSim概览

6

ModelSim 仿真工具

注意: 当库中涉及的设计单元被改变时设计单元必须重新分析。

27

VHDL Design Units Dependencies

Entity before Architecture Package Declaration before Package Body Design units must compiled before being referenced

映射现有的库(UI)

选择 a new library and a logical mapping to it a 输入库名

这个命令在局部目 录建立一个库目录 然后为它设立映射

-> vlib my_lib -> vmap my_lib my_lib

24

映射库 (UI)

RTL仿真(ModelSim)

– 功能仿真 – 验证逻辑模型(没有使用时间延迟) – 可能要求编辑设计

综合

– 把设计翻译成原始的目标工艺 – 最优化 • 合适的面积要求和性能要求

布局和布线

– 映射设计到目标工艺里指定位置 – 指定的布线资源应被使用

4

典型的PLD设计流程

IEEEpure

– 包含唯一IEEE 认可的 std_logic_1164 packages – 用于仿真加速

IEEE

– 包含预编译的Synopsys和IEEE 算法包 – 给std_logic的基本类型 – 用于仿真加速

18

vlib <library_name> 命令

22

映射现有的库(UI)

选择 a map to an existing library 和 输入库名

用这个命令可映射一个设计 单元已经预编译的库目录

浏览库目录

-> vmap lpm_sim c:/Quartus/library/lpm

23

structure结构窗口

Wave&list 波形和列表窗口 process处理窗口:

Signal&variable信号和变量窗口 dataflow数据流窗口

12

ModelSim实现方法

交互式的命令行 (Cmd)

– 唯一的界面是控制台的命令行, 没有用户界面

用户界面 (UI)

Verilog

– vsim top_level1 top_level2 • 仿真多个top级模块

33

启动仿真器 (UI)

选择仿真器的分辨率

选择库

选择顶级module 或 entity/architecture

34

启动仿真器(UI)

指定 SDF文件

建立库 缺省值是 work

<library_name> _info any_verilog_module _primary.dat _primary.vhd verilog.asm any_vhdl_unit _primary.dat <arch_name>.dat <arch_name>.asm _lock

vdir

– 显示指定库的内容 – UI) Design -> View Library Contents – Cmd) vdir -lib <library_name>

26

3

编译源代码(VHDL)

UI) Design -> Compile Cmd) vcom -work <library_name> <file1>.vhd <file2>.vhd

用Add 按钮建立一 个新的库和映射

25

其他的库命令

vdel

– 从指定的库中删除一个完整的库或者一个设计单元 – UI) Design -> Library Browser (删除库或者映射) – UI) Design -> View Library Contents (删除设计单元) – Cmd) vdel -lib <library_name> <design_unit>

使用定时值的等级的 类型 (如果不是顶级)

35

vsim 命令的参数

参数

– -t <time_unit> • 指定仿真的时间分辨率 • 单位可以是{fs, ps, ns, ms, sec, min, hr} • 如果用了 Verilog的 ‘timescale指令, 将使用整个设计中的最小的 时间精度 • 可选项(缺省是 ns) – -sdfmin | -sdftyp | -sdfmax <instance>=<sdf_filename> • 注释SDF文件 • 可选项 • 使用实例名也是可选项; 如果没有使用, SDF用于顶级

– 能接受菜单输入和命令行输入 – 课程主要讨论

批处理模式

– 从DOS或UNIX命令行运行批处理文件 – 不讨论

13

基本仿真步骤

1 2 3 建立库 映射库到物理目录 编译源代码 - 所有的HDL代码必须被编译 - Verilog和VHDL是不同的 启动仿真器 执行仿真

– 许可 Verilog 或者 VHDL,但是不同时许可

ModelSim/PLUS

– 设计者能立刻混合仿真Verilog 和 VHDL

ModelSim/SE

– 首要的版本 – PLUS的所有功能连同附加功能

8

ModelSim OEM 功能

提供完全的标准

– – – – – – ‘87 VHDL ‘93 VHDL IEEE 1364-’95 Verilog SDF 1.0 - 3.0 VITAL 2.2b VITAL ‘95

易用的界面

– 通用的平台

9

用ModelSim 仿真

10

课程安排

基本的仿真步骤 用户界面 功能仿真 Quartus输出仿真文件 时序仿真

Model 技术公司的 ModelSim

main主窗口: source源窗口

16

ModelSim 设计单元

主要

– 在一个特定的库中必须有唯 一的名字 – VHDL • Entities(实体) • Package Declarations(包 声明) • Configurations(结构) – Verilog • Modules(模块) • User Defined Primitives (用户定义原语)

4 5

14

1

建立ModelSim库

UI) 从主菜单里面: Design -> Create a New Library Cmd) 从main, 记录窗口: ModelSim> vlib <库名>

15

ModelSim 库

包含编译设计单元的目录

– VHDL 和 Verilog 都被编 work) • 包含当前被编译的设计单元 • 编译前必须建立一个working库 • 每个编译只允许一个 – Resource • 包含能被当前编译引用的设计单元 • 在编译期间允许多个 • VHDL库能通过LIBRARY和USE子句引用