Tsu Tco约束方法

建立时间、保持时间和时序约束条件

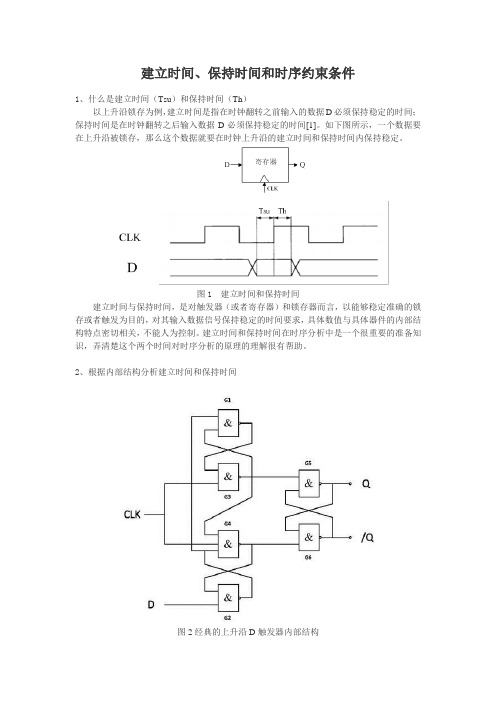

建立时间、保持时间和时序约束条件1、什么是建立时间(Tsu)和保持时间(Th)以上升沿锁存为例,建立时间是指在时钟翻转之前输入的数据D必须保持稳定的时间;保持时间是在时钟翻转之后输入数据D必须保持稳定的时间[1]。

如下图所示,一个数据要在上升沿被锁存,那么这个数据就要在时钟上升沿的建立时间和保持时间内保持稳定。

图1 建立时间和保持时间建立时间与保持时间,是对触发器(或者寄存器)和锁存器而言,以能够稳定准确的锁存或者触发为目的,对其输入数据信号保持稳定的时间要求,具体数值与具体器件的内部结构特点密切相关,不能人为控制。

建立时间和保持时间在时序分析中是一个很重要的准备知识,弄清楚这个两个时间对时序分析的原理的理解很有帮助。

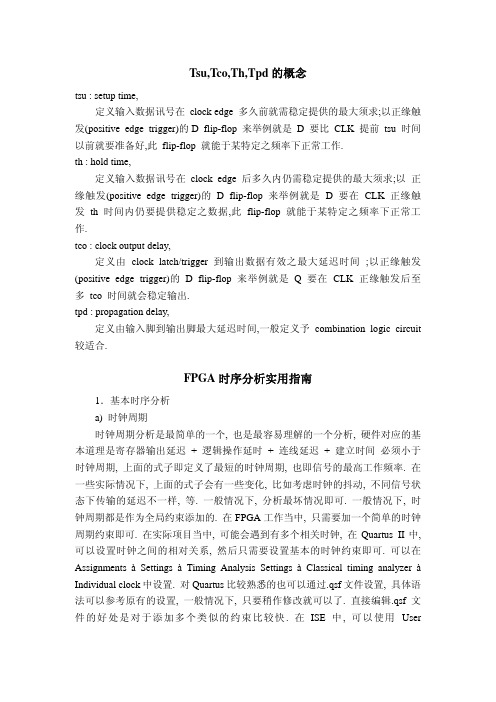

2、根据内部结构分析建立时间和保持时间图2 经典的上升沿D触发器内部结构关于为什么会有建立时间和保持时间,我曾试图从触发器或锁存器内部的结构去分析和证实,但是看了许多资料,由于触发器的内部结构有很多,所以分析方法很多,说法也很多。

下面我选两个比较经典的结构来分析一下建立时间和保持时间。

以经典边沿触发的D触发器为例子,从内部结构上分析一下D触发器建立时间和保持时间。

这个说明主要来源于EETOP的一篇帖子,其结构在维基百科的触发器词条可以得到验证。

如上图所示,这是一个上升沿触发的D触发器,需要注意的是,图中的6个与非门都是有延迟的,也就是在某一时刻输入组合逻辑的数据,在一段时间之后才能影响其输出,这是产生建立时间和保持时间要求的最根本原因。

首先,我们在假设所有的与非门的延迟为0,叙述一下这个触发器的整体工作流程。

当CLK=0时,与非门G3和G4的输出均为1,输出的1反馈到G1和G2作为输入,导致G1和G2的输出分别为D和/D,输出的D和/D又反馈到G3和G4;而G5和G6在此期间一直锁存着之前的数据,不受输入影响。

图3 CLK=0时触发器内部信号详情当CLK=1时,与非门G3和G4的输出变为/D和D,输出到G5和G6作为输入,根据锁存器的原理,G5和G6最终会稳定的输出Q和/Q。

FPGA四种路径添加时序约束方法

在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。

通常,在FPGA设计工具中都FPGA中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑。

通常,需要对这几种路径分别进行约束,以便使设计工具能够得到最优化的结果。

下面对这几种路径分别进行讨论。

1、从输入端口到寄存器:这种路径的约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。

约束名称:input delay. 约束条件的影响主要有4个因素:外部芯片的Tco,电路板上信号延迟Tpd,FPGA的Tsu, 时钟延迟Tclk. Tco的参数通常需要查外部芯片的数据手册。

计算公式:input delay = Tco+Tpd+Tsu-Tclk. FPGA的Tsu也需要查FPGA芯片的手册。

FPGA速度等级不同,这个参数也不同。

Tpd和Tclk需要根据电路板实际的参数来计算。

通常,每10cm的线长可以按照1ns来计算. 例如:系统时钟100MHz, 电路板上最大延迟2ns, 时钟最大延迟1.7ns, Tco 3ns, FPGA的Tsu为0.2ns. 那么输入延迟的值: max Input delay= 2+3+0.2-1.7=3.5ns. 这个参数的含义是指让FPGA的设计工具把FPGA的输入端口到第一级寄存器之间的路径延迟(包括门延迟和线延迟)控制在10ns-3.5ns=6.5ns 以内。

2、寄存器到寄存器:这种路径的约束是为了让FPGA设计工具能够优化FPGA内寄存器到寄存器之间的路径,使其延迟时间必须小于时钟周期,这样才能确保信号被可靠的传递。

由于这种路径只存在于FPGA内部,通常通过设定时钟频率的方式就可以对其进行约束。

对于更深入的优化方法,还可以采用对寄存器的输入和寄存器的输出加入适当的约束,来使逻辑综合器和布线器能够对某条路径进行特别的优化。

有关时序的一些重要内容

Tsu,Tco,Th,Tpd的概念tsu : setup time,定义输入数据讯号在 clock edge 多久前就需稳定提供的最大须求;以正缘触发(positive edge trigger)的D flip-flop 来举例就是 D 要比 CLK 提前 tsu 时间以前就要准备好,此 flip-flop 就能于某特定之频率下正常工作.th : hold time,定义输入数据讯号在 clock edge 后多久内仍需稳定提供的最大须求;以正缘触发(positive edge trigger)的 D flip-flop 来举例就是 D 要在 CLK 正缘触发 th 时间内仍要提供稳定之数据,此 flip-flop 就能于某特定之频率下正常工作.tco : clock output delay,定义由 clock latch/trigger 到输出数据有效之最大延迟时间;以正缘触发(positive edge trigger)的 D flip-flop 来举例就是Q 要在 CLK 正缘触发后至多 tco 时间就会稳定输出.tpd : propagation delay,定义由输入脚到输出脚最大延迟时间,一般定义予 combination logic circuit 较适合.FPGA时序分析实用指南1.基本时序分析a) 时钟周期时钟周期分析是最简单的一个, 也是最容易理解的一个分析, 硬件对应的基本道理是寄存器输出延迟 + 逻辑操作延时 + 连线延迟 + 建立时间必须小于时钟周期, 上面的式子即定义了最短的时钟周期, 也即信号的最高工作频率. 在一些实际情况下, 上面的式子会有一些变化, 比如考虑时钟的抖动, 不同信号状态下传输的延迟不一样, 等. 一般情况下, 分析最坏情况即可. 一般情况下, 时钟周期都是作为全局约束添加的. 在FPGA工作当中, 只需要加一个简单的时钟周期约束即可. 在实际项目当中, 可能会遇到有多个相关时钟, 在Quartus II中, 可以设置时钟之间的相对关系, 然后只需要设置基本的时钟约束即可. 可以在Assignments à Settings à Timing Analysis Settings à Classical timing analyzer à Individual clock中设置. 对Quartus比较熟悉的也可以通过.qsf文件设置, 具体语法可以参考原有的设置, 一般情况下, 只要稍作修改就可以了. 直接编辑.qsf文件的好处是对于添加多个类似的约束比较快. 在ISE中, 可以使用 Userconstraints à create timing constraints, 通过图形界面设置, 也可以直接编辑.ucf文件实现. 同样, 具体语法可以参考现成的文件.b) 输入setup输入数据的setup要求是初学者经常搞糊涂的一个约束. 其实Quartus和ISE 里边对输入setup的定义都非常清晰, 也即, 从外部来看, 只要满足时钟和数据一定的关系, FPGA内部可以保证不会出现亚稳态现象(即采在数据的沿上). 在Quartus中, 这个参数是Tsu, 其准确定义如下: The length of time for which data that feeds a register via its data or enable input(s) must be present at an input pin before the clock signal that clocks the register is asserted at the clock pin. 具体计算公式如下: tSU = + - . 确切的说, 这个定义应该是从外部看到的FPGA的时序要求. 比如Tsu为 0.5ns, 那么只要数据在0.5ns之前建立, 数据送入FPGA应该不会出现问题. Tsu可以是全局约束, 也可以是局部约束. 全局约束可以通过Assignments à Settings à Timing Analysis Settings à Classical timing analyzer中的Tsu来设置, 局部约束可以通过Assignment Editor来添加.在ISE中, 叫做Offset In Before或者Pad to setup, 准确定义如下: The minimum time for input signals to be stable before they can be sampled correctly on the next active clock edge. 具体计算公式为: Slack = Requirement - (Data Path - Clock Path + uncertainty)举个例子来说, 如果时序报告给出数值为 4.468ns, 那么这意味着数据必须在时钟沿之前4.468ns建立, 换而言之, 只要外部送入数据在4.468ns之前建立, FPGA内部采用不会出问题. 具体的计算方法如同Altera. Offset in Before可以是全局约束, 也可以局部约束, 在Constraint Editor可以设置.在实际使用过程中, 通常大部分情况下, 数据和时钟都是每个周期有效. 因此, 数据到底在哪个时钟周期被寄存器捕获其实并不重要, 关键是所有的相关数据(比如一个总线的数据[7:0])必须保证在一个时钟周期内采样. 因此, 如何避开会造成亚稳态以及如何使得相关的数据的Tsu尽量保持一致, 是解决数据输入FPGA的时序问题的关键. 比如, 假定输入FPGA的数据在时钟沿的1ns处发生变化, 那么Tsu应当避开这个1ns附近这个区域. 只要按照上述原则操作, 时序裕量都会是够的. 在一些特殊情况下, 比如有使能信号传递, 或者是数据的时钟周期必须严格对其, 或者是时钟抖动特别大, 则需要更加仔细的考虑时序约束.TcoTco是Clock to output的延时. 道理如同Tsu, 只不过是换个角度看问题, 即作为驱动源来看待的问题. 也是从外部观察的. 在Quartus中, 这个参数是Tco, 其准确定义如下: The maximum time required to obtain a valid output at an outputpin that is fed by a register after a clock signal transition on an input pin that clocks the register. 意思是相对于输入时钟管脚而言, 从寄存器输出的数据(到达pin)最长多长时间可以稳定. 具体的计算公式如下:tCO = + + . Tco可以是局部约束, 也可以是全局约束. 具体设置方法和Tsu 类似.在ISE中, 这个参数是Offset out after或者称为Clock to Pad, 其准确定义如下: The clock-to-output, or OFFSET OUT, delay of the FPGA is the total delay encountered from the time a clock edge arrives at the input pin of the device to the time data becomes valid at the output pin of the device. 具体计算公式为Slack = Requirement – (Clock Arrival + Clock Path + Data Path + Clock Uncertainty). Offset Out After可以为全局约束或者是局部约束, 在constraint editor工具或者直接编辑UCF文件均可设置. 下面的一个报告给出了一个示例:OFFSET = OUT 4 ns AFTER COMP "ClkIn";Largest slack: 0.667 ns; Smallest slack: 0.667 ns; Relative Skew: 0.0 ns;+-----------------------------------------------+-------------+-------------+|PAD | Slack |Relative Skew|+-----------------------------------------------+-------------+-------------+|DataOut<0> | 0.667| 0.0 |+-----------------------------------------------+-------------+-------------+即要求的Tco为4ns, 实际的Tco为3.333ns, 寄存器输出的最大延迟不超过3.33ns.在实际应用中, 还需考虑其他的一些因素, 比如时钟布线的策略, 比如星形结构, Daisy Chain结构等等. 不同的策略分析的方法有所差别, 具体的分析方法将在下篇有关FPGA芯片间通信(或着板间通信)的时序分析介绍.Altera对应的时序概念下面主要介绍Altera对应的这些时序概念和约束方法。

pcs constraint location 指令

pcs constraint location 指令"pcs constraint location" 指令是在自动布局(Autolayout)中用于设置视图之间几何关系的约束。

自动布局是苹果公司(Apple)在iOS 开发中引入的一种布局方式,通过使用约束(constraint)来简化视图的排列和调整。

在这个指令中,"pcs" 代表"position constraint set",即位置约束集,它是一组约束的集合。

"location" 则表示约束所应用的视图的位置。

该指令的作用是在Interface Builder(IB)中创建和编辑约束,以定义视图之间的关系。

例如,你可以设置两个视图之间的间距约束,如“label A 右边缘和button B 左边缘有20 点的空白空间”。

自动布局会根据所有的约束为视图计算出理想的位置和大小,从而简化了开发者手动设置视图frame 的过程。

通过使用约束,你可以更轻松地调整视图的位置和大小,以实现各种布局需求。

在Interface Builder中,你可以通过以下步骤来设置和编辑约束:1. 在Document Outline 中选择需要添加约束的视图。

2. 打开Attributes Inspector 面板,在其中找到Constraints 选项卡。

3. 点击Add New Constraint 按钮,选择所需的约束类型(如Equal Widths、Equal Height 等)。

4. 为新创建的约束设置属性,如constant、multiplier 和priority。

5. 重复以上步骤,为所需的视图添加更多的约束。

完成约束设置后,运行程序,自动布局会根据这些约束为视图计算出合适的位置和大小。

这将极大地简化你的布局工作,并提高开发效率。

Tco探秘

Tco探秘(原创)getmoon@希望大家喜欢,如果有什么不正确之处,请指出,必改。

1. 何为Tco在FPGA中,Tco有两种:(1) 触发器Tco(2) 管脚输出Tco触发器Tco由FPGA的器件速度等级,工艺决定。

一般在几百ps左右。

管脚输出Tco是指从输出触发器信号从管脚输出的延迟。

本文指讨论管脚Tco。

2. Tco的作用在FPGA和外部芯片由同步通信时,Tco是保证系统能够工作与设定频率的重要因素。

假设当前A芯片输出信号到B芯片。

为了能够使A芯片的数据达到B芯片,并且满足B芯片的setup/hold时间要求。

必须保证 ,A芯片的 Tco + B 芯片的 Tsu < T3. Tco的组成Tco的延迟有三部分组成:输出触发器的触发器Tco输出触发器输出管脚到IOE的走线延迟IOE内部延迟在这3个延迟中,触发器内部Tco非常小,只有几百个ps,相对于其他两个延迟,可以忽略不计。

4. Tco的优化为了优化Tco , quartus 提供了一个优化选项,就是“Fast Output Register“ 。

意思是使用IOE中的输出寄存器直接用于逻辑寄存器。

这样可以减少输出寄存器到pad的走线距离,达到优化Tco的目的。

另外,quartus的Tco的计算方法和前面有所不同, quartus的Tco的计算如下所示:输入时钟管脚和输出触发器时钟之间的skew触发器内部Tco触发器-> IOE -> pad延迟可以看出,3小节提到的计算方法是以输出触发器的时钟为参考的延迟。

而quartus计算的方法是以时钟输入管脚为参考。

Quartus的分析如下所示:Info: Slack time is 15 ps for clock "Clk[0]" between source register "out[3]~reg0" and destination pin "out[3]"Info: + tco requirement for source register and destination pin is 5.000 nsInfo: - tco from clock to output pin is 4.985 nsInfo: + Longest clock path from clock "Clk[0]" to source register is 2.401 nsInfo: 1: + IC(0.000 ns) + CELL(1.469 ns) = 1.469 ns; Loc. = PIN_29; Fanout = 4; CLK Node = 'Clk[0]'Info: 2: + IC(0.723 ns) + CELL(0.209 ns) = 2.401 ns; Loc. = IOC_X0_Y1_N0; Fanout = 1; REG Node = 'out[3]~reg0'Info: Total cell delay = 1.678 ns ( 69.89 % )Info: Total interconnect delay = 0.723 ns ( 30.11 % )Info: + Micro clock to output delay of source is 0.664 nsInfo: + Longest register to pin delay is 1.920 nsInfo: 1: + IC(0.000 ns) + CELL(0.000 ns) = 0.000 ns; Loc. = IOC_X0_Y1_N0; Fanout = 1; REG Node = 'out[3]~reg0'Info: 2: + IC(0.000 ns) + CELL(1.920 ns) = 1.920 ns; Loc. = PIN_59; Fanout = 0; PIN Node = 'out[3]'Info: Total cell delay = 1.920 ns ( 100.00 % )5. Tco使用分析为了分析Tco写了如下一个例子来进行分析。

FPGA约束总结

FPGA 约束文件基础建立时间:时钟有效沿到来之前的一段时间内,数据必须稳定,否则触发器锁存不住数据,这段时间称为建立时间,用Tsetup或者Tsu表示。

保持时间:时钟有效沿到来之后的一段时间内,数据也必须稳定,否则也必须稳定,否则触发器锁存不住数据。

这段时间称为保持时间用Thold或者Th表示。

亚稳态:每个触发器都有其规定的建立(setup)和保持(hold)时间参数,该参数存放在由半导体厂商所提供的工艺库中。

假如触发器由时间的上升沿触发,在这个时间参数内,输入信号时不允许发生变化的。

否则在信号的建立或保持时间内对其采样,的到的结果是不可预测的。

可能是0或1,即亚稳态。

Tco:启动寄存器内部延时,是寄存器REG1感受到有效的上升沿后,到数据真正从从REG1的Q输出之间延时;请注意:上述所谓的有效的上升沿,就是REG1.CLK,而不是CLK;所以实际的有效数据输出的时序如上图的REG1.Q;Tdata:数据从上级寄存器输出Q(经过所有其他组合逻辑以及FPGA内部走线)到下级寄存器的数据输入D之间的延时;二、物理约束物理约束需要注意什么?1.约束块不宜过大,避免浪费资源、增大路径延迟,同时也不宜过小,避免因“拥挤”增大路径延迟;2.约束块可以“重叠”放置,“重叠”部分资源共用,同时外部逻辑也可利用块内空闲资源;3.约束块需逐步放置,逐步验证;4.可通过移动布局不合理的RAM、PLL等单元位置来优化时序问题;5.块约束后时序出错,首先调整相应逻辑单元位置及块的大小和位置,必要时修改逻辑设计FPGA XDC文件(约束文件的意义)FPGA在逻辑设计完成后需要软件进行布局布线如果我们不加约束那么软件的布局布线是随机的并且在高速运行时由于延迟等因素就会出现时序出错,因此在生成bit流文件之前需要对FPGA进行约束生成一个功能实现较好的电路。

常用的约束有时钟约束引脚约束引脚电平约束时钟约束:是对外部进入FPGA的时钟进行周期占空比以及进入那个端口进行约束create_clock -period (clock period) -name (clock name) -waveform { (Traise), (Tfall) } [get_ports (clock port name)]引脚约束:是对FPGA内部逻辑端口和FPGA芯片引脚进行配置set_property PACKAGE_PIN V4 [get_ports {display_out[9]}]引脚电平约束:是对 FPGA引脚电平进行约束set_property IOSTANDARD LVCMOS33 [get_ports {display_out[9]}]电平约束 LVTTL 和LVCOMS区别3.3V LVTTL:Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。

FPGA门级结构及其时序基础资料

主题

FPGA优势

FPFGPGAA结结构构

SRAM与 Flip-Flop门级结构

FPGA设计流程

FPGA时序路径

FPGA时序基础

SRAM结构

从引脚到引脚

输入延时约束

Flip-Flop结构

从输入到寄存器

输出延时约束

从寄存器到输出

寄存器延时约束

从寄存器到寄存器

7

FPGA结构

Xilinx FPGA芯片的基本结构 8

主题

FPGA优势

FPGA结构

SSRRAAMM与与 FFlliipp--FFlloopp门门级级结结构构

FPGA设计流程

FPGA时序路径

FPGA时序基础

SRAM结构

从引脚到引脚

输入延时约束

Flip-Flop结构

从输入到寄存器

输出延时约束

从寄存器到输出

寄存器延时约束

从寄存器到寄存器

14

主题

FPGA优势

寄存器时钟端的时间差别。

3

主题

FPFGPGAA优优势 势 FPGA结构

SRAM与 Flip-Fห้องสมุดไป่ตู้op门级结构

FPGA设计流程

FPGA时序路径

FPGA时序基础

SRAM结构

从引脚到引脚

输入延时约束

Flip-Flop结构

从输入到寄存器

输出延时约束

从寄存器到输出

寄存器延时约束

从寄存器到寄存器

4

FPGA优势

这使得FPGA成为中小量产规模电路设计最廉价的实 现方法。然而,FPGA也为可编程特性付出了代价。

在MPGA(掩模可编程门阵列)和VSLI中,电路时 用金属线互联的,FPGA却一定要通过可编程开关来 连接电路,这些开关比金属线的电阻大,从而引入 的大量的分布电容和寄生电容。实现同一功能, FPGA面积也要比MPGA大得多(约10倍),速度却 是MPGA的1/3。由于FPGA市场竞争激烈,FPGA 的供应商正努力寻找更好的结构以获得速度和密度 上的优势。

约束优化方法的讲解共45页

37、我们唯一不会改正的缺点是软弱。——拉罗什福科

xiexie! 38、我这个人走得很慢,但是我从不后退。——亚伯拉罕·林肯

39、勿问成功的秘诀为何,且尽全力做你应该做的事吧。——美华纳

1、不要轻言放弃,否则对不起自己。

2、要冒一次险!整个生命就是一场冒险。走得最远的人,常是愿意 去做,并愿意去冒险的人。“稳妥”之船,从未能从岸边走远。-戴尔.卡耐基。

梦 境

3、人生就像一杯没有加糖的咖啡,喝起来是苦涩的,回味起来却有 久久不会退去的余香。

约束优化方法的讲解4、守业的最好办法就是不断的发展。 5、当爱不能完美,我宁愿选择无悔,不管来生多么美丽,我不愿失 去今生对你的记忆,我不求天长地久的美景,我只要生生世世的轮 回里有你。

40、学而不思则罔,思而不学则殆。——孔子

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Tsu/Tco 在Quartus II 的报告中有两种不同含义.

1. 片内的Tsu/Tco 是指前级触发器的Tco 和后级触发器的Tsu, 一般来说都是几百ps 级别的. 可以通过“List Paths”命令查看。

这里的Tsu/Tco 主要由器件工艺决定, 工作时在受到温度,电压的影响略有变化.(如下图所示)

2. 管脚上的Tsu/Tco 它是保证系统Famx 重要的Timing 元素(如下图示). 比如: 两个芯片之间工作在100MHZ, 因为100M 的周期为10ns, (现忽略PCB 走线的延迟), 如果某信号对FPGA 来说是输入, 那么前级芯片的Tco 加上FPGA 的Tsu 就不能够超过10ns. 如果某信号对于FPGA 来说是输出,那么FPGA 的T co 加上后级芯片的Tsu 也不能够超过10ns. 只有这样,才能够保证片间通信正常。

因此对FPGA 的管脚进行适当的Tco/Tsu 的时序约束,是至关重要的Timing 设计技巧.

管脚上的Tsu/Tco 分为以下三个部分.

1) IOE 走线的延迟. 这个延迟在管脚的Tsu/Tco 延迟中占有相当的比例,Altera 的器件为了降低Tsu/T co 在IOE 上的延迟, 专门在IOE 中设置了两种类型的触发器, 即 : Fast Input register(FPGA 的管脚为输入时,优化Tsu), Fast Output Register(FPGA 的管脚为输出时,用于优化Tco)

2)内部逻辑走线的延迟。

在Altera 的FPGA 中, 由若干个基本资源LE 构成一个LAB,比如: Stratix Gx 是10 个LE 组成一个LAB. LAB 横向和纵向排列形成阵列. 在FPGA 中,以LAB 为基本单元, 根据走线长度的不同,分为C4(表示横跨4 个LAB 的走线资源),C8,C16,R4,R8,16,R24 等不同的走线资源,不同的器件支持不同的走线资源。

3)触发器的Tsu/Tco 的需求,这里的Tsu/Tco, 这是由器件工艺决定的,最小的Tsu/Tco 的要求. 在实际的工作环境中,受温度,电压的变化有微小的变化.

前面提到:对FPGA 的管脚进行适当的Tco/Tsu 的时序约束,是至关重要的Timing 设计技巧.关键是在出了问题的时候,怎么去解决?

Quartus II 有四处可以对Tsu/Tco 进行约束.

1. 全局时序约束. 在Quartus II 中执行Assignments..Timing Setting 弹出如下界面.设计者可以根据系统Fmax 的要求去约束Tsu/Tco.

2. 执行Assignments..Assignment Editor 命令,得到如下界面.设计者可以根据本设计的

要求,对输入/输出管脚设置Tsu/Tco 的约束;也可以约束内部触发器的Tsu/Tco 的值。

(如下图所示)

3.执行Assignments.. Assignment Editor 命令,选择”All”或者”Logic Options” ,对管脚进行Ts u/Tco 的约束.

在”To” 选择对应的管脚,在Assignment Name 中选择”Fast Input Register” 来约束Tsu, 选择”Fa st Output Register” 来约束Tco. 这也是逻辑工程师通常说的: 为减少Tsu/Tco 的值,放到IOE 中.

3. 修改布线后的底层电路.

执行pilation Report 命令. 在Resource Section..Input Pins/Output Pins 中

选中对应的输入输出管脚(如下图所示).

执行Locate..Locate to Chip Editor 命令.得到如下界面.

选中的管脚在Chip Editor 中已经被HighLight( 如上图所示). 双击Highlight 的的管脚,得到下图界面.

这里的参数就是该管脚在布线后所有的参数,并不是每个参数都可以修改.比如: 对LVDS 电平标准,Curren t Strength 就不能够修改等.对于LVTTL 电平标准,Current Strength 就有2,4,8,16,24mA 可以修改. 设计者可以根据设计的需求来Enable 或者Disable Fast Input Register/Fast Output Register 属性,可以修改输入管脚到逻辑阵列的延迟和输出管脚到逻辑阵列的延迟等.

修改完成后,这时不能够再编程工程,只需要执行Processing..Start..Start Assembler 更新编程sof 文件和pof 文件即可。