全加器与全减器设计

四位二进制全加全减器

数字逻辑设计及应用课程设计组合逻辑电路课程设计四位二进制全加/全减器姓名:学号:指导教师:一、任务与要求使用74LS83构成4位二进制全加/全减器。

具体要求:1)列出真值表;2)画出逻辑图3)用Verilog HDL进行仿真二、设计思路1)原理分析:74LS83是四位二进制先行加法器,所以直接接入输入可以得到全加器,下面主要讨论四位二进制全减器的构造。

对于减法,可以作相应的代数转换编程加法,二进制减法也是如此,原理如下:这样就把减法变为了加法,而[]=,这里利用补码性质,具体实现方法就是:逐位取反并在最低权一位加上1。

在全减器中,进位输入Cin变为借位输出,所以要减去Cin,且全加器的输出端Cout为进位输出,全减器为借位输出,所以将So取反后即可得到全减器的借位输出。

在以上分析基础可知,可在全加器的基础上设计全减器。

四位二进制全加/全减器真值表如下:(因原始真值表行数太过庞大,列出部分真值的例子)真值表A3 A2 A1 A0 B3 B2 B1 B0 Co Bo S0 S1 S2 S3C/B0 0 1 0 0 1 0 1 0 1 0/1 1/1 1/0 1/1 01 0 1 1 1 1 1 0 1 1 1/1 0/1 0/0 1/1 00 1 1 0 0 0 1 1 0 0 1/0 0/0 0/1 1/1 01 1 1 1 0 0 1 1 1 0 0/1 0/1 1/0 0/0 00 0 1 0 0 1 0 1 0 1 1/1 0/1 0/0 0/0 11 0 1 1 1 1 1 0 1 1 1/1 0/1 1/0 0/0 10 1 1 0 0 0 1 1 0 0 1/0 0/0 1/1 0/0 11 1 1 1 0 0 1 1 1 0 0/1 0/0 1/1 1/1 1*表格后半部分内容,斜线前为全加结果,斜线后为全减结果*XOR门的函数为:,所以当EN=A=0时,得到F=B与第二输入相同,当EN=A=1时,F=B’与第二输入相反。

数字电子技术之全减器全加器分析

2018年数字电子技术学习总结

——全减器,全加器分析

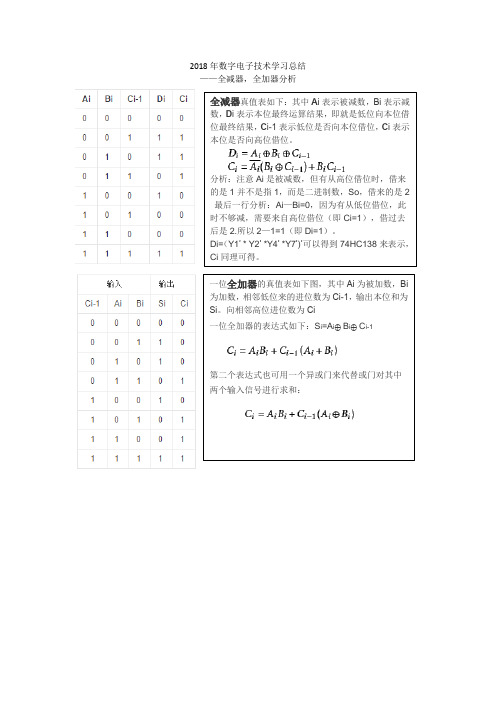

全减器

真值表如下:其中A i 表示被减数,Bi 表示减数,D i 表示本位最终运算结果,即就是低位向本位借位最终结果,C i-1表示低位是否向本位借位,C i 表示本位是否向高位借位。

分析:注意Ai 是被减数,但有从高位借位时,借来的是1并不是指1,而是二进制数,So ,借来的是2 最后一行分析:Ai

—

Bi=0,因为有从低位借位,此时不够减,需要来自高位借位(即Ci=1),借过去后是2.所以2—1=1(即Di=1)。

Di=(Y1’ * Y2’ *Y4’ *Y7’)’可以得到74HC138来表示,Ci 同理可得。

一位全加器的真值表如下图,其中Ai 为被加数,Bi 为加数,相邻低位来的进位数为Ci-1,输出本位和为Si 。

向相邻高位进位数为Ci

一位全加器的表达式如下:S i =A i ⊕B i ⊕C i-1

第二个表达式也可用一个异或门来代替或门对其中两个输入信号进行求和:。

组合逻辑课程设计4位二进制全加器全减器原创

关键字 74LS283 全加器、四位二进制、迭代电路、并行进位、串行进位、VHDL

摘要

加法器是数字系统中产生数的和的装置。加数和被加数为输入,和数与进 位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进

...

.

..

..

位为输出则为全加器。例如:为了节省资源,减法器和硬件乘法器都可以用加法 器来构成。但宽位加法器的设计是很耗资源的,因此在实际的设计和相关饿得设 计与开发中需要注意资源的利用率和进位速度两方面的问题,多位加法器的构成 主要有两种:并行进位和串行进位。并行进位加法器设有并行进位产生逻辑,运 行速度比串行进位快;串行进位是将全加器采取并行级联或菊花链式级联构成多 位加法器。加法器也是常用作计算机算术逻辑部件,执行逻辑操作、移位与指令 调用。此外还可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二 进制作运算。

1 0 0100 11011000

1 0 0101 00011010

1 0 0001 10011100

1 0 0001 10111110

1 0 1010 01000111

1 0 1010 01101001

1 0 0010 01000011

1 0 0010 01100101

... ... ... ... ... ... ... ... ... ... ... ... ... ...

完整四位全加全减器设计

四位全加全减器设计一.实验目的1熟悉在max+plus II 的环境下设计数字电路的步骤和方法2学习使用vhdl语言,进行设计数字电路的RTL级电路3通过max+plus II 软件中对自行设计的电路的仿真,加深对数字电路设计的理解。

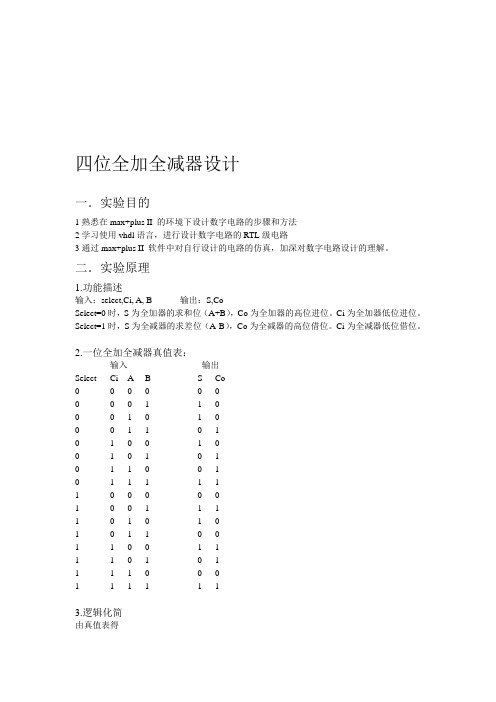

二.实验原理1.功能描述输入:select,Ci, A, B 输出:S,CoSelect=0时,S为全加器的求和位(A+B),Co为全加器的高位进位。

Ci为全加器低位进位。

Select=1时,S为全减器的求差位(A-B),Co为全减器的高位借位。

Ci为全减器低位借位。

2.一位全加全减器真值表:输入输出Select Ci A B S Co0 0 0 0 0 00 0 0 1 1 00 0 1 0 1 00 0 1 1 0 10 1 0 0 1 00 1 0 1 0 10 1 1 0 0 10 1 1 1 1 11 0 0 0 0 01 0 0 1 1 11 0 1 0 1 01 0 1 1 0 01 1 0 0 1 11 1 0 1 0 11 1 1 0 0 01 1 1 1 1 13.逻辑化简由真值表得S=A○十B○十Ci=((A○十Select)○十B○十Ci)○十SelectCo=(A○十Select)B+Ci((A○十Select)+B)=((A○十Select)○十B)Ci+(A○十Select)B对于半加器的逻辑表达式为:S=A○十B Co=AB综上,一位全加全减器可由两个半加器,两个异或门和一个或门组成。

4.毛刺的产生与消除组合逻辑电路由于输入到输出各端的延时不同,在输出端稳定之前会产生错误的输出。

在本电路中,由于低位的进位或借位传输到输出的时间比其他信号传输的延时要长,因此当低位产生进位或借位时会出现错误的输出。

一种常见的方法是利用D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输入输出信号。

由组合逻辑电路的最大延时Td为16.7ns,D触发器的时钟周期T应略大于Td,取20ns。

全加器全减器设计实验报告

全加器全减器设计实验报告1. 引言全加器和全减器是数字电路中常用的基本电路模块之一。

全加器用于将两个二进制数相加,全减器用于将两个二进制数相减。

在本实验中,我们将设计并实现一个4位的全加器和一个4位的全减器电路。

2. 原理2.1 全加器全加器是由两个半加器和一个或门组成的电路。

一个半加器用于计算两个输入位的和,另一个半加器用于计算进位值。

将两个半加器的结果和进位值通过或门进行运算,即可得到全加器的输出。

如下图所示为全加器的逻辑电路图:其中,A和B为输入信号,用于表示待相加的两个二进制数的对应位;S为输出信号,表示两个输入数的对应位相加的结果;C为进位信号,表示相加时产生的进位。

2.2 全减器全减器是由两个半减器和一个与非门组成的电路。

与全加器类似,一个半减器用于计算两个输入位的差,另一个半减器用于计算借位值。

将两个半减器的结果和借位值通过与非门进行运算,即可得到全减器的输出。

如下图所示为全减器的逻辑电路图:其中,A和B为输入信号,用于表示待相减的两个二进制数的对应位;D为输出信号,表示两个输入数的对应位相减的结果;B为借位信号,表示相减时需要借出的位。

3. 设计和实现3.1 全加器设计根据2.1中的原理,我们可以使用两个半加器和一个或门来实现一个4位的全加器电路。

根据全加器的逻辑电路图,我们可以将四个输入位(A0, A1, A2, A3)依次与另外四个输入位(B0, B1, B2, B3)连接到两个半加器中,然后将两个半加器的和(S0, S1, S2, S3)通过或门进行运算。

此外,计算进位值需要使用到四个位的与门(And)。

具体电路图如下:3.2 全减器设计根据2.2中的原理,我们可以使用两个半减器和一个与非门来实现一个4位的全减器电路。

根据全减器的逻辑电路图,我们可以将四个输入位(A0, A1, A2, A3)依次与另外四个输入位取反连接到两个半减器中,然后将两个半减器的差(D0, D1, D2, D3)通过与非门进行运算。

电子技术基础实验报告-全加减器设计

《电子技术基础实验报告》实验名称:组合逻辑电路设计1、实验名称:全加/减器设计与仿真2、实验设计要求以及内容:全加器要求两个二进制数相加时,要考虑低位进位的相加。

并输出本位计算结果和高位进位结果。

全减器是两个二进制的数进行减法运算时使用的一种运算单元,采用本位结果和借位来显示,二进制中是借一当二,所以可以使用两个输出变量的高低电平变化来实现减法运算。

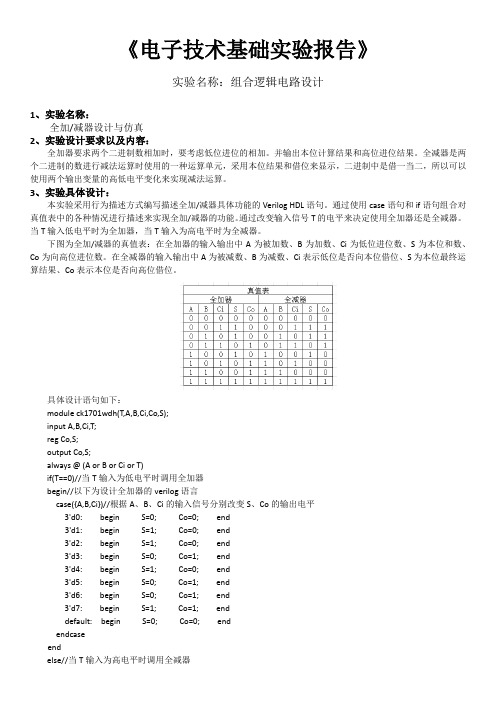

3、实验具体设计:本实验采用行为描述方式编写描述全加/减器具体功能的Verilog HDL语句。

通过使用case语句和if语句组合对真值表中的各种情况进行描述来实现全加/减器的功能。

通过改变输入信号T的电平来决定使用全加器还是全减器。

当T输入低电平时为全加器,当T输入为高电平时为全减器。

下图为全加/减器的真值表:在全加器的输入输出中A为被加数、B为加数、Ci为低位进位数、S为本位和数、Co为向高位进位数。

在全减器的输入输出中A为被减数、B为减数、Ci表示低位是否向本位借位、S为本位最终运算结果、Co表示本位是否向高位借位。

具体设计语句如下:module ck1701wdh(T,A,B,Ci,Co,S);input A,B,Ci,T;reg Co,S;output Co,S;always @ (A or B or Ci or T)if(T==0)//当T输入为低电平时调用全加器begin//以下为设计全加器的verilog语言case({A,B,Ci})//根据A、B、Ci的输入信号分别改变S、Co的输出电平3'd0: begin S=0; Co=0; end3'd1: begin S=1; Co=0; end3'd2: begin S=1; Co=0; end3'd3: begin S=0; Co=1; end3'd4: begin S=1; Co=0; end3'd5: begin S=0; Co=1; end3'd6: begin S=0; Co=1; end3'd7: begin S=1; Co=1; enddefault: begin S=0; Co=0; endendcaseendelse//当T输入为高电平时调用全减器begin//以下为设计全减器的verilog语言case({A,B,Ci})//根据A、B、Ci的输入信号分别改变S、Co的输出电平3'd0: begin S=0; Co=0; end3'd1: begin S=1; Co=1; end3'd2: begin S=1; Co=1; end3'd3: begin S=0; Co=1; end3'd4: begin S=1; Co=0; end3'd5: begin S=0; Co=0; end3'd6: begin S=0; Co=0; end3'd7: begin S=1; Co=1; enddefault: begin S=0; Co=0; endendcaseendendmodule4、输入输出设计:(按键,数码管,发光管等说明)管脚分配如下(格式:输入/输出通道名:对应引脚名→开发板上对应开关名):信号输入Input: A:PIN_J6→SW[0], B:PIN_H5→ SW[1], Ci:PIN_H6→ SW[2], T:PIN_G4→ SW[3].信号输出Output: S:PIN_J2→LEDG[1], Co:PIN_J1→ LEDG[0].SW[]为拨动开关,LEDG[]为绿色发光二极管。

最新组合逻辑课程设计4位二进制全加器全减器原创

组合逻辑电路课程设计——4位二进制全加器/全减器作者:学号:课程设计题目要求:1)使用74LS283构成4位二进制全加/全减器。

2)阐述设计思路。

3)列出真值表。

4)画出设计的逻辑图。

5)用VHDL对所画电路进行仿真。

目录摘要 (1)1总电路设计 (2)1.1硬件电路的设计 (2)1.2全加器(full-adder ) (3)1.2.1四位二级制加法器 (4)1.2.1.1串行进位加法器 (4)1.2.1.2超前进位加法器 (5)1.2.1.3超前位链结构加法器 (5)1.3全减器(full-substracter ) (5)1.4总电路设计 (6)2设计思路 (7)2.1全加器 (7)2.2全减器 (7)3真值表 (8)4逻辑图与仿真 (9)5软件程序的设计 (13)6结果分析与总结 (15)摘要加法器是数字系统中产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

例如:为了节省资源,减法器和硬件乘法器都可以用加法器来构成。

但宽位加法器的设计是很耗资源的,因此在实际的设计和相关饿得设计与开发中需要注意资源的利用率和进位速度两方面的问题,多位加法器的构成主要有两种:并行进位和串行进位。

并行进位加法器设有并行进位产生逻辑,运行速度比串行进位快;串行进位是将全加器采取并行级联或菊花链式级联构成多位加法器。

加法器也是常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

此外还可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

本文将采用4位二进制并行加法器作为折中选择,所选加法器为74LS283,74LS283是4位二进制先行进位的加法器,它只用了几级逻辑来形成和及进位输出,故由其构成4位二进制全加器;而四位全减器可以用加法器简单的改造而来,最后本文采用 VHDL对四位全加器/全减器进行仿真。

关键字74LS283全加器、四位二进制、迭代电路、并行进位、串行进位、VHDL1总电路设计1.1硬件电路的设计该4位二进制全加器以74LS283为核心,74LS283芯片引脚图如下图,本文采用先行进位方式,极大地提高了电路运行速度,下面是对4位全加器电路设计的具体分析。

全加全减器实验报告

一、实验目的1. 理解全加器和全减器的工作原理。

2. 掌握全加器和全减器的电路设计方法。

3. 通过实验验证全加器和全减器的功能。

二、实验原理全加器(Full Adder)是一种能够处理两个二进制位以及一个来自低位的进位输入的加法器。

全减器(Full Subtractor)则是一种能够处理两个二进制位以及一个来自低位的借位输入的减法器。

它们是数字电路中常用的基本单元。

三、实验器材1. 实验箱2. 逻辑门芯片3. 连接线4. 计算器四、实验步骤1. 全加器设计1.1 根据全加器的真值表,设计全加器的逻辑电路图。

1.2 利用与门、或门、非门和异或门等逻辑门,实现全加器的逻辑功能。

1.3 将设计好的电路图连接到实验箱上,进行测试。

1.4 测试全加器的功能,验证其是否能正确实现加法运算。

2. 全减器设计2.1 根据全减器的真值表,设计全减器的逻辑电路图。

2.2 利用与门、或门、非门和异或门等逻辑门,实现全减器的逻辑功能。

2.3 将设计好的电路图连接到实验箱上,进行测试。

2.4 测试全减器的功能,验证其是否能正确实现减法运算。

五、实验结果与分析1. 全加器测试结果1.1 当输入A、B和进位C(N)均为0时,输出Sum为0,进位C(N1)为0。

1.2 当输入A、B和进位C(N)均为1时,输出Sum为0,进位C(N1)为1。

1.3 当输入A为0,B为1,进位C(N)为0时,输出Sum为1,进位C(N1)为0。

1.4 当输入A为1,B为0,进位C(N)为0时,输出Sum为1,进位C(N1)为0。

1.5 当输入A为1,B为1,进位C(N)为0时,输出Sum为0,进位C(N1)为1。

1.6 当输入A为0,B为0,进位C(N)为1时,输出Sum为1,进位C(N1)为1。

1.7 当输入A为1,B为1,进位C(N)为1时,输出Sum为1,进位C(N1)为1。

通过测试结果可以看出,全加器能够正确实现加法运算。

2. 全减器测试结果2.1 当输入A、B和借位B(N)均为0时,输出差D为A,借位B(N1)为0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

学校代码:_________学号:__________Hefei University数电设计报告NUMBER OF ELECTRICAL DESIGNREPORT设计题目:全加器与全减器设计学位类别:工学学士年级专业(班级):电子信息工程1班作者姓名:汤家映(1405011019)、宋道远(1405011020)、朱亚东(1405011022)导师姓名:谭敏完成时间: 2015-5-17目录一、设计任务 (2)1.用组合逻辑电路设计1位二进制全加器与全减器 (2)2.用双8选1数据选择器74LS151设计1位二进制全加器与全减器 (2)3.用广义译码器VHDL语言设计1位二进制全加器与全减器 (2)二、设计过程 (2)1.用组合逻辑电路设计1位二进制全加器与全减器 (2)(1)进行逻辑抽象,建立真值表 (2)(2)画出卡诺图 (2)(3)画出逻辑电路 (3)2.用双8选1数据选择器74LS151设计1位二进制全加器与全减器 (3)(1)逻辑问题进行抽象,列出真值表 (3)(2)列出函数表达关系 (4)(3)用数据选择器74LS151画出逻辑电路图 (4)3.用广义译码器VHDL语言设计1位二进制全加器与全减器 (5)三、总结 (6)一、设计任务1、用组合逻辑电路设计1位二进制全加器与全减器;2、用双8选1数据选择器74LS151设计1位二进制全加器与全减器;3、用广义译码器VHDL语言设计1位二进制全加器与全减器。

二、设计过程1、用组合逻辑电路设计1位二进制全加器与全减器(1)进行逻辑抽象,建立真值表全加器与全减器真值表输入输出A B C全加器(m=0)全减器(m=1)S D S D0 0 0 0 0 0 00 0 1 1 0 1 10 1 0 1 0 1 10 1 1 0 1 0 11 0 0 1 0 1 01 0 0 1 0 1 01 0 1 0 1 0 01 1 1 1 1 1 1(说明:当m=1时为全加器A.B分别表示被减数和减数C表示低位向高位的借位数,S表示本位和值,D表示向高位的借位;当m=0时为全加器A.B分别表示两个加数C表示低位向高位的进位数,S表示本位和值,D表示向高位的进位)(2)画出卡诺图S 的卡诺图 D 的卡诺图 BC\mA 00 01 11 10 00 0 1 1 0 01 1 0 0 1 11 0 1 1 0 10 10 0 1 全加器:m=0时,C B A S ⊕⊕=,BC AC AB BC AC ABD ∙∙=++=全减器:m=1时,C B A S ⊕⊕=,BC C A B A BC C A B A D ∙∙=++=(3)画出逻辑电路根据最简逻辑表达式画出逻辑电路图VCCAINPUT VCCBINPUT VCCCINPUT VCCmINPUT NAND2inst7NAND2inst8NAND2inst9XORinstXORinst11NAND3inst12SOUTPUT DOUTPUTXORinst132、用双8选1数据选择器74LS151设计1位二进制全加器与全减器; (1)逻辑问题进行抽象,列出真值表BC\mA 00 01 11 10 00 0 0 0 0 01 0 1 0 1 11 1 1 1 1 1011全加器与全减器真值表m A B C S D0 0 0 0 0 0000110001010001101010010010101011001011111100000100111101011101101110010110100111000111111 4(说明:当m=1时为全加器A.B分别表示被减数和减数C表示低位向高位的借位数,S表示本位和值,D表示向高位的借位当m=0时为全加器A.B分别表示两个加数C表示低位向高位的进位数,S表示本位和值,D表示向高位的进位)(2)列出函数表达关系根据上面真值表,列出逻辑函数表达式(标准与或式)S mAmBCmAm++=++++m+ACBCmABBABCBCBCACAmmABCD+++AmBCm+mAm=m+++mCBmAmABCBCBAABCCCABCBA(3)用数据选择器74LS151画出逻辑电路图根据逻辑函数的标准与或式画出逻辑电路图VCC C INPUT VCCBINPUT VCCAINPUT VCCmINPUT sOUTPUT DOUTPUT MULTIP LE XE RGNC B A D5D0D1D4D3D2D6D7Y WN74151instMULTIP LE XE RGNC B A D5D0D1D4D3D2D6D7Y WN74151inst1VCCNOTinst6GND3、用广义译码器VHDL 语言设计1位二进制全加器与全减器 根据全加器与全减器的真值表编写VHDL 程序,程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY JJ ISPORT(M,A,B,C:IN STD_LOGIC; S,D: OUT STD_LOGIC); END ENTITY JJ;ARCHITECTURE one OF JJ ISSIGNAL MABC:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGINMABC<=M&A&B&C; PROCESS(MABC) BEGINCASE MABC ISWHEN"0000"=>S<='0';D<='0'; WHEN"0001"=>S<='1';D<='0'; WHEN"0010"=>S<='1';D<='0'; WHEN"0011"=>S<='0';D<='1'; WHEN"0100"=>S<='1';D<='0'; WHEN"0101"=>S<='0';D<='1'; WHEN"0110"=>S<='0';D<='1'; WHEN"0111"=>S<='1';D<='1';WHEN"1000"=>S<='0';D<='0';WHEN"1001"=>S<='1';D<='1';WHEN"1010"=>S<='1';D<='1';WHEN"1011"=>S<='0';D<='1';WHEN"1100"=>S<='1';D<='0';WHEN"1101"=>S<='0';D<='0';WHEN"1110"=>S<='0';D<='0';WHEN"1111"=>S<='1';D<='1';WHEN OTHERS=>NULL;END CASE;END PROCESS;END ARCHITECTURE one;三、总结本次关于全加器与全减器的设计是由本组三人共同合作配合完成,知道了合作完成任务的重要性。

通过这次课程设计,加强了我们思考和解决问题的能力,巩固数字逻辑电路的理论知识,进一步发现自身的优点与不足:当面对问题时我们能冷静的想出解决问题的思路,同时也会去付诸实施。

然而,在处理事情的过程中,也遇到了一些困难,我们虚心的与同学讨论,向老师请教。

总的来说,我认为这次的数电设计课程对我们来说都受益匪浅。

课程设计反映的就是一个理论到实际应用的过程,更远一点可以联系到毕业以后从学校转到踏入社会的一个过程,我们要培养和同学间的合作,自身的动脑与努力是必然的,合作可能是更为重要的,但都是以后上社会工作必不可少的。