数字式脉搏计设计与制作

脉搏测试仪的设计制作与测试

脉搏测试仪的设计制作与测试(朱开明.电子技术实训指导.清华大学出版社.2005.11 p169~171)1.设计要求检测人体脉搏,并用数字显示。

可用于医用或运动中检查每分钟脉搏跳动次数。

2.设计分析①脉搏探测器,将脉搏跳动信号转换为电信号。

②对检测的脉搏跳动信号进行放大和整形。

③对脉搏信号进行计数和显示。

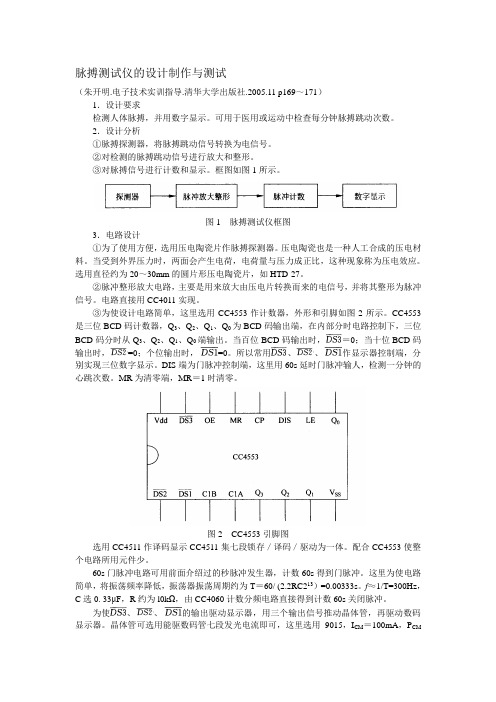

框图如图1所示。

图1 脉搏测试仪框图3.电路设计①为了使用方便,选用压电陶瓷片作脉搏探测器。

压电陶瓷也是一种人工合成的压电材料。

当受到外界压力时,两面会产生电荷,电荷量与压力成正比,这种现象称为压电效应。

选用直径约为20~30mm的圆片形压电陶瓷片,如HTD-27。

②脉冲整形放大电路,主要是用来放大由压电片转换而来的电信号,并将其整形为脉冲信号。

电路直接用CC4011实现。

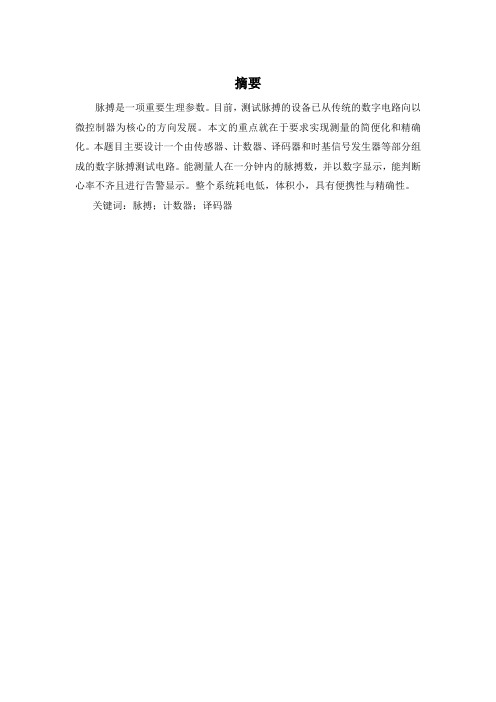

③为使设计电路简单,这里选用CC4553作计数器,外形和引脚如图2所示。

CC4553是三位BCD码计数器,Q3、Q2、Q1、Q0为BCD码输出端,在内部分时电路控制下,三位BCD码分时从Q3、Q2、Q1、Q0端输出。

当百位BCD码输出时,=0;当十位BCD码输出时,=0;个位输出时,=0。

所以常用、、作显示器控制端,分别实现三位数字显示。

DIS端为门脉冲控制端,这里用60s延时门脉冲输人,检测一分钟的心跳次数。

MR为清零端,MR=1时清零。

图2 CC4553引脚图选用CC4511作译码显示CC4511集七段锁存/译码/驱动为一体。

配合CC4553使整个电路所用元件少。

60s门脉冲电路可用前面介绍过的秒脉冲发生器,计数60s得到门脉冲。

这里为使电路简单,将振荡频率降低,振荡器振荡周期约为T=60/ (2.2RC213)=0.00333s。

f≈1/T=300Hz,C选0. 33μF,R约为l0kΩ,由CC4060计数分频电路直接得到计数60s关闭脉冲。

为使、、的输出驱动显示器,用三个输出信号推动晶体管,再驱动数码显示器。

晶体管可选用能驱数码管七段发光电流即可,这里选用9015,I CM=100mA,P CM=450mW。

数字脉搏测试仪毕业设计

摘要脉搏是一项重要生理参数。

目前,测试脉搏的设备已从传统的数字电路向以微控制器为核心的方向发展。

本文的重点就在于要求实现测量的简便化和精确化。

本题目主要设计一个由传感器、计数器、译码器和时基信号发生器等部分组成的数字脉搏测试电路。

能测量人在一分钟内的脉搏数,并以数字显示,能判断心率不齐且进行告警显示。

整个系统耗电低,体积小,具有便携性与精确性。

关键词:脉搏;计数器;译码器AbstractPulse is an important physiological parameter.At present, the test pulse equipment from the traditional digital circuit to the microcontroller as the core direction.The focus of this paper is that required to achieve a simple and accurate measurement.This topic mainly consists of sensor, counter, decoder and a time base signal generator and other components of the digital pulse testing circuit.Can be measured in one minute with the pulse number, and a digital display, can judge the heart rate and alarm display.The whole system of low power consumption, small volume, portable and precise.Key words: pulse; counter; decoder;目录摘要 (1)第一章引言 (4)第二章设计方案 (6)一设计要求及技术指标 (6)二原理方框图 (6)第三章单元电路的设计 (8)一信号检测放大与整形电路 (8)芯片CD4011 (8)二计数,译码,显示电路 (9)CD4511 (9)CD4553 (带扫描输出的三位十进制计数器) (10)三计时电路 (14)CD4060 (14)第四章总原理图及原理综述 (15)总体调试 (16)设计心得与体会 (17)参考文献: (19)致谢 (20)第一章引言在传统中医学的诊断中,“望、闻、问、切”是最基本的四个方面。

数字脉搏计课程设计报告

天津大学电力电子课程设计报告课题名称:数字脉搏计实验人:自动化1班淦智权同组人:自动化1班李得铭2014年12月25日一、设计任务及要求:设计、组装一个数字脉搏计。

(1)用十进制数字显示被测人体的脉搏每分钟跳动的次数,测量范围为20~200次/分。

(2)在短时间(5秒、15秒)内测量出每分钟的脉搏数。

(3)测量误差±4次/分。

(4)锁定每分钟的脉搏数,分别要求:①显示计数过程,并保持计数结果。

手动清零。

②不显示计数过程,锁存为计数结果。

自动清零,自启动计数。

注:5S和15S由开关控制。

二、电路设计方案及原理(一)总方案原理图:对于方案选择,由提供的PPT上的方案的原理框图,我们决定按该框图进行分析,不过在每个框图部分实现会有多种方案并进行有计划的结合实际的改造。

1、模拟信号处理(设计并仿真)对于脉搏信号的放大、滤波、整形部分采用 MultiSim或PSPICE仿真实现。

脉搏信号放大器(仿真)输入:1mV、1.2Hz输出:能够驱动CMOS数字芯片性能指标:电压增益:大于1000倍通频带:0.15Hz —30Hz仿真要完成的主要任务:功能分析、指标测量。

2、给定条件实验箱一台:直流电源、面包板、连续脉冲信号等元器件:锁相环 CD4046计数器(可预置数的4位二进制计数器) CD4526计数器(二——十进制同步加计数器) CD4518计数器/分频器(14位二进制串行计数器/分频器) CD4060译码器 74LS48数码管 LG5011AH(实验箱上74LS48已与数码管连接好)缓冲器(反相器)电阻、电容若干数电实验中常用芯片三、各单元部分设计及电路实现(一)仿真阶段对于仿真部分的要求题目要求如下:输入:1mV、1.2Hz;电压增益:大于1000倍;通频带:0.15Hz—30Hz我们采用的multisim仿真,仿真阶段有三个部分,分别是:放大,滤波及整形。

放大是要将采集到的微小的脉搏信号放大成可读取的信号;滤波是为了滤去杂波;整形是为了将正弦信号转化为方波,方便计数1、放大部分对于放大,我们用的是最基础的放大器放大方法,由于电压增益大于1000,我们决定放大3000倍,采用三个LM324器件,进行10*10*30三级放大,具体参数见下图。

电子脉搏计设计

电子脉搏计设计1 .设计思路正常人的脉搏次数是每分钟60~80次(婴儿为90~140次,老年人则为100~150次), 这种频率信号属于低频范畴.因此,脉搏计的用来测量低频信号的装置,它的基本功能要求应该是:(1).要把人体的脉搏数(振动)转换成电信号,这就需要借助传感器。

(2).对转换后的电信号要进行放大和整形处理,以保证其它电路能正常加工和处理。

(3).在很短的时间(若干秒)内,测出经放大后的电信号频率值。

总之,脉搏计的核心是要对低频信号在固定的短时间计数,最后以数字形式显示出来。

可见,脉搏计的主要组成部分是计数器和数字显示器。

2 .方案设计2.1 选用方案原理方框图:图1:原理框图3 .单元电路的设计3.1信号发生与采集脉搏传感器的作用是将脉搏信号转换为响应的电冲信号。

脉搏传感器是脉象检测系统中重要的组成部分,其性能的好坏直接影响到后置电路的处理和结果的显示。

目前典型的脉搏传感器有以下三种:光电类、压阻类和压电类。

在这三种当中目前采用最多的信号放信号发生与采是压电型传感器。

压电式传感器的工作原理是以某种物质的压电效应为基础。

这些物质在沿一定方向受到压力的或拉力的作用而发生变形时,其表面会产生电荷;若将外力去掉时,它们又重新回到不带电的状态,这种现象就称为压电效应。

而具有这种压电效应的物体称为压电材料或压电元件。

常见的压电材料有石英、钛酸钡、锆钛酸铅等。

3.1.1信号放大电路这部分电路主要完成将5mV 的正弦波输入信号放大1000倍(5V ),使其可以驱动后续的CMOS 数字电路。

采用运算放大器LM324构成的反相放大电路: 在理想条件下有i V R R V ⨯-=120运放的闭环电压增益为12R R A Vf -=,输入电阻为Rif=R1。

如果对输入电阻有要求可以先确定R1,再根据放大倍数确定R2。

为了减小输入偏置电流引起的运算误差,在同相输入端应接平衡电阻R3,且R3=R1∥R2。

图2:放大电路实际电路中拟采用三级放大,电路图如图2所示:参数选定如下:输入电阻要求不小于107欧,因而选定R1=10M 欧,第一级电路放大10倍,因而R2=100M 欧,R3=R1∥R2=9.1M 欧,第二级及第三级放大电路放大倍数仍为10倍,R5=R8=10k 欧,R7=R9=100k 欧,R4=R6=9.1k 欧。

脉搏计的设计_毕业设计说明书(论文)

信息职业技术学院毕业设计说明书(论文)设计(论文)题目: 脉搏计的设计专业: 通信技术班级: 通技06-2学号: 0620045姓名:指导教师:二OO八年十二月三十日信息职业技术学院毕业设计(论文)任务书备注:任务书由指导教师填写,一式二份。

其中学生一份,指导教师一份。

目录摘要 (1)第1章绪论 (2)1.1目的与意义 (2)1.2思想与方法 (2)第2章方案设计 (3)2.1方案比较与论证 (3)2.2方案选择 (5)第3章单元电路设计 (6)3.1放大与整形电路 (6)3.1.1传感器 (6)3.1.2放大电路 (6)3.1.3有源滤波电路 (7)3.1.4整形电路 (7)3.1.5电平转换电路 (7)3.2倍频电路 (8)3.3基准时间产生电路 (8)3.3.1秒脉冲发生器 (9)3.3.2十五分频和二分频器 (9)3.3.3基准时间产生电路 (9)3.3.4计数、译码、显示电路 (10)3.3.5控制电路 (13)总结 (14)致谢 (15)参考文献 (16)附录总电路原理图 (17)摘要本设计主要由传感器、计数器、译码器和时基信号发生器等部分组成的数字脉搏。

要求能测量人在一分钟内的脉搏数,并以数字显示,测量的脉搏数范围40~200次/分钟,适用于各个年龄及性别的人,能判断心率不齐且进行告警显示。

关键词数字脉搏测试;时基信号;发生器计数器;译码器第1章绪论1.1 目的与意义从脉搏波中提取人体的生理病理信息作为临床诊断和治疗的依据,历来都受到中外医学界的重视。

几乎世界上所有的民族都用过“摸脉”作为诊断疾病的手段。

脉搏波所呈现出的形态(波形)、强度(波幅)、速率(波速)和节律(周期)等方面的综合信息,在很大程度上反映出人体心血管系统中许多生理病理的血流特征,因此对脉搏波采集和处理具有很高的医学价值和应用前景。

但人体的生物信号多属于强噪声背景下的低频的弱信号,脉搏波信号更是低频微弱的非电生理信号,必需经过放大和后级滤波以满足采集的要求。

数字脉搏计设计报告

电子课程设计实验数字脉搏计实验报告学院:电气与自动化工程学院班级: 08级自动化X班作者姓名: XXX学号: XXX完成时间: 2010年12月24日一、设计任务及要求(1)设计一个数字脉搏计,要求用十进制数字显示被测人体脉搏每分钟跳动次数,测量范围30~160次/min。

(2)短时间内(5或15s)测出每分钟的脉搏跳动次数,误差为±4次/min。

(3)锁定每分钟的脉搏数,可以有两种方式,一种为显示计数过程,最后锁定;还有一种是不显示计数过程,直接显示结果。

(4)所有部分电路均要有仿真结果,仿真中用5p-p的正弦波来模拟人的脉搏信号,实际接线时直接用信号发生器发出的5V的方波脉冲作为测试信号,故放大滤波整形电路部分只作仿真即可。

(5)对于放大部分电路,要求放大倍数至少70dB倍,输入电阻要求大于107欧,通频带为0.5Hz~50Hz,测试时还要测出输入输出电压的波形(即整形前后的电压波形)。

二、Multisim仿真设计1. 总体方案原理框图总体方案框图采用实验指导书上“数字脉搏计”中的参考方案,如下图:2. 信号放大电路这部分电路的功能是将传感器输出的电压信号(仿真用5mV的正弦波输入信号代替)放大,使其可以驱动后续的CMOS数字电路。

此部分电路具体要求为:①放大倍数为70dB;②输入阻抗大于107Ω。

考虑到简单的原则,此处利用理想放大器组成我们熟悉的反相比例放大电路。

其原理如下:电路图如图所示,在理想条件下有V o=-Vi×R2/R1 。

运放的闭环电压增益为Avf=-R2/R1,输入电阻为Rif=R1。

如果对输入电阻有要求可以先确定R1,再根据放大倍数确定R2。

为了减小输入偏置电流引起的运算误差,在同相输入端应接平衡电阻R3,且R3=R1∥R2。

放大倍数70dB即大约为3000倍,直接利用一级反相比例放大电路在仿真时是可行的。

然而实际运用中,若R1取10kΩ,则R2应取到30MΩ,两者相差过大,考虑真实电阻的误差,可能使放大倍数不准确。

脉搏计设计

一、设计题目

脉搏计的设计

二、设计任务

实现在15秒内测量1分钟的脉搏数,并且显示其数字。

测量范围符合事实情况正常人脉搏数为60~80次/分钟,婴儿为90~100次/分钟,老人为100~150次/分钟。

三、设计计划

电子技术课程设计共1周。

第1天:选题,查资料;

第2天:方案分析比较,确定设计方案;

第3天:电路原理设计;第4 Nhomakorabea:修改设计;

第5天:编写整理设计说明书。

四、设计要求

1.画出整体电路图。

2.分析实验结果,写出设计说明书。

指导教师:

教研室主任:

时间:年月日

课程设计名称:电子技术课程设计

题目:脉搏计的设计

专业:

班级:

姓名:

学号:

课程设计--数字电子脉搏计

数字电子脉搏计一.设计任务要求设计一个电子脉搏计,要求:实现在15s 内测量1min 的脉搏数,并且显示其数字。

正常人脉搏数60~80次/min ,婴儿为90~100次/min,老人为100~150次/min 。

1.实现在15秒内测量1 min 的脉搏数;2.用数码管将测得的脉搏数用数字的形式显示;3.测量误差小于4次/min 。

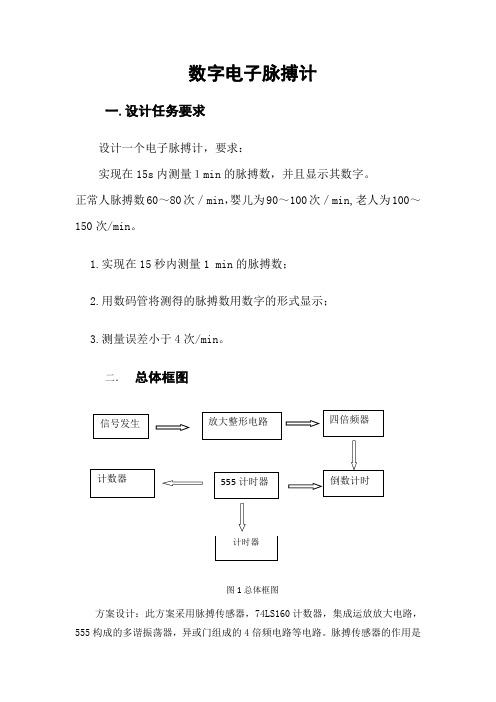

二.总体框图图1总体框图方案设计:此方案采用脉搏传感器,74LS160计数器,集成运放放大电路,555构成的多谐振荡器,异或门组成的4倍频电路等电路。

脉搏传感器的作用是计时器信号发生放大整形电路四倍频器倒数计时555计时器计数器将脉搏信号转换为响应的电脉冲信号。

由一个运放器和三个电阻就组成了符合要求的放大电路。

倍频电路要对脉搏进行调频,如将15s内传感器所获得的信号频率4倍频,即可得到对应一分钟的脉冲数,从而缩短测量时间。

555定时器是为了试验在规定时间内完成任务。

本设计中采用简单的74LS160作为计数器,因为它是十进制计数器无需改装,直接使用。

因为脉搏测试器中需要上百位的数字。

因此,将三片74LS160直接按并行进位方式连接即的千进制计数器。

三、元器件清单本实验采用数电中常见的器件,这样我们就可以熟练地使用而且可以降低该电路的故障率。

以下为本实验所使用的器件。

表一元器件清单1、异或门:当两个输入一致时,输出为0,输入相异时,输出为1。

异或门的原序号名称型号数量备注1 555定时器CB555 12 七段译码器DCD_HEX 63 十进制上升沿计数器74LS160D 64 与门74LS08 3 两输入5 与非门74LS08 2 两输入6 非门7400N 1 两输入7 同或门CD4077 1 两输入8 电阻ROHM 4 10KΩ9 电阻ROHM 1 9.1KΩ10 电阻ROHM 1 100KΩ11 电阻ROHM 1 5.1KΩ12 电容16CE470AX 1 0.01μF13 电容16CE470AX 1 0.1μF14 电容16CE470AX 1 3.8μF15 电容16CE470AX 1 33μF16 异或门4070BD 4 两输入17 单刀双掷开关 118 交流信号发生器 1 5000Hz,5V理图与真值表如图2-1所示图2-1异或门的逻辑符号与真值表2. 2输入与门如图2-2所示,A、B为与门的输入端,Y为与门的输出端。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《数字电子技术》课程设计报告班级电气1077 学号 1071206138 学生姓名缪亮亮专业电气工程及其自动化系别电子与电气工程学院指导教师电子技术课程设计指导小组淮阴工学院电子信息工程系2009年12月1、设计目的:a) 培养理论联系实际的正确设计思想,训练综合运用已经学过的理论和生产实际知识去分析和解决工程实际问题的能力。

b) 学习较复杂的电子系统设计的一般方法,了解和掌握模拟、数字电路等知识解决电子信息方面常见实际问题的能力,由学生自行设计、自行制作和自行调试。

c) 进行基本技术技能训练,如基本仪器仪表的使用,常用元器件的识别、测量、熟练运用的能力,掌握设计资料、手册、标准和规范以及使用仿真软件、实验设备进行调试和数据处理等。

d) 培养学生的创新能力。

2、设计要求:要求:实现在15S内测量1min的脉搏数,并且显示其数字。

正常人脉搏数为60~80次/min,婴儿为90~100次/min,老人为100~150次/min。

1、主要单元电路和元器件参数计算、选择;2、画出总体电路图;3、安装自己设计的电路,按照自己设计的电路,在通用板上焊接。

焊接完毕后,应对照电路图仔细检查,看是否有错接、漏接、虚焊的现象。

4、调试电路5、电路性能指标测试3、总体设计:3·1数字脉搏测试仪原理方框图上图即为数字式脉搏计的总体设计框图。

该数字式脉搏计由以下几部分组成:1)脉冲产生电路 2)放大整形电路 3)计数电路4)定时电路 5)译码显示电路3·2电路组成及工作原理数字式脉搏计设计的思路是:先由压电陶瓷片YD将拾取的脉搏跳动信号转换成电信号,经LM324放大整形后,送到由CD4553和CD4511组成的计数显示电路。

CD4553内部输入端设置了脉冲整形电路,所以对脉冲无甚特殊要求。

它只有一组BCD 码输出,但通过内部分时控制可形成三位十进制数字显示。

CD4511是译码器,其输出驱动三位LED共阴数码管。

BG1、BG2、BG3分别由CD4553的15、1、2脚控制实现三位数码管的分时显示。

CD4060组成计数闸门设定电路,R5、R6、C6与其内部电路组成振荡器,振荡器信号经内部213次分频后,由2脚输出延时 60 秒的正脉冲加到CD4553的11脚关闭闸门。

使用时,用手表带或松紧带将压电陶瓷片压在手腕的挠动脉处,注意一定要压紧。

在合上开关 K1 后即按一下复位开关 K2,使CD4060和CD4553清零,这时计数闸门打开,脉搏信号由CD4553进行计数。

1分钟后,CD4060输出一高电平,使计数闸门关闭。

这时数码管显示的数字即为每分钟的脉搏数。

3·3各框图的功能和可选电路及特点1)脉冲产生电路:2)放大整形电路:可选LM3243)计数电路:可选CD4553 4)定时电路:可选CD40605)译码显示电路:可选CD4511驱动共阴极数码管。

3·4电路制作所需的工具3·5元器件列表四、单元电路设计:4.1采样输入单元电路设计输入单元借助压电陶瓷将脉搏信号转换为电信号,通过电容C1耦合输入到集成运放LM324组成的同相放大器进行放大,23(1)o i V R v v R =+,放大倍数约为10倍。

放大后的信号输入到后面的积分电路进行整形。

当有信号输入时,电容器以近似恒流方式进行充电,输出电压o v 与时间t 成近似线性关系,io v v t RC≈。

当t >RC 时,o v 增大,直到o om v V =,即运放进入饱和状态,o v 保持不变,而停止积分。

此时的o v 可以近似看成是一个方波,能够符合计数器的触发要求。

单元电路如下图所示。

图1 输入采样单元电路4.1.1 LM324集成运算放大器特性LM324是四运放集成电路,它采用14脚双列直插塑料封装。

它的内部包含四组形式完全相同的运算放大器,除电源共用外,四组运放相互独立。

每一组运算放大器可用图4所示的符号来表示,它有5个引出脚,其中“+”、“-”为两个信号输入端,“V+”、“V-”为正、负电源端,“Vo”为输出端。

两个信号输入端中,Vi-(-)为反相输入端,表示运放输出端Vo的信号与该输入端的位相反;Vi+(+)为同相输入端,表示运放输出端Vo的信号与该输入端的相位相同。

其特点如下:1)具有宽的单电源或双电源工作电压范围;单电源3V~30V,双电源±1.5V~±15V ;2)内含相位校正回路, 外围元件少;3)消耗电流小:Icc=0.6mA (典型值, RL=∞) ;4)输入失调电压低:±2mV (典型值) ;5)电压输出范围宽:0V ~ Vcc—1.5V ;6)共模输入电压范围宽:0V ~ Vcc—1.5V。

图2 运算放大器4.1.2 LM324集成运算放大器引脚说明1脚 OUTPUT1 6脚 INPUT2- 11脚 GND2脚 INPUT1- 7脚 OUTPUT2 12脚 INPUT4+3脚 INPUT1+ 8脚 OUTPUT3 13脚 INPUT4-4脚 V+ 9脚 INPUT3- 14脚 OUTPUT4 OUTPUT5脚 INPUT2+ 10脚 INPUT3+14脚是运算放大器的输出端,也是这个芯片的输出;INPUT-是运算放大器的反向输入端,输出端输出的信号总与这个引脚的输入信号极性相反。

INPUT+是运算放大器的正向输入端,信号的输入与输出同向。

(LM324的引脚排列见图2)4.2计数器单元电路设计本电路计数器部分采用一片CD4553作为计数核心。

CD4553是具有选通脉冲输出控制的3位十进制计数器。

脉冲信号由CK 端输入,当计数锁定端LE 和显示允许段DIS 为低电平时,对脉冲信号进行计数。

计数结果为三位BCD 码,由Q0--Q3输出。

而三个输出选择端1DS 、2DS 、3DS 为低电平有效,通过3扫描输出的方法分别控制三个数码管。

当时基控制电路到达计时时间后,向DIS 端输出高电平,使计数器停止计数,并锁存,显示当前计数值。

MR 端用于清零,按下复位按钮后计数器清零,准备工作。

单元电路如下所示。

脉冲信号接数码管图3 计数器单元电路4.2.1 三位BCD 计数器CD4553特性CD4553由三个BCD 计数器级联而成,因而可以用个位、十位、百位进行计数,计数值从0—999。

由于它的计数输出端只有一个,而要完成三个计数器的输出,故采用3扫描输出的方法,逐个输出3个计数器的计数值,扫描频率由3、4脚的分时扫描振荡器外接电容的容量确定。

由于扫描频率较高故不影响计数输出的准确性。

与3个计数器输出相对应,还有3个相应的计数器输出选择端1DS 、2DS 、3DS ,低电平有效。

如当第一个计数器输出时,1DS 为低电平,2DS 、3DS 均为高电平;当第二个计数器输出时,2DS 为低电平,其余为高电平;第三个计数器输出时,3DS 为低电平。

这样可以通过1DS 、2DS 、3DS 与数码管配合,实现分时显示。

4.2.1 三位BCD 计数器CD4553真值表CD4553真值表由真值表可以看出,当复位端MR 为高电平时,计数器清零。

当LE 为高电平时,计数值被锁定,无法继续计数。

当显示允许端DIS 为低电平时,时钟脉冲CLK 下降沿计数;当时钟端CLK为高电平时,显示允许端输入上升沿脉冲计数;其余情况计数值不变。

当3个BCD 计数器计数值均为9时,进位端OVF 送出高电平脉冲。

4.2.1 三位BCD 计数器CD4553引脚说明 如右图所示,芯片 CD4553 的功能:1脚:数据选择输出端; 9脚:BCD 码输出端; 2脚:数据选择输出端; 10脚:锁存控制器; 3脚:外接电容管脚1; 11脚:时钟输入控制端; 4脚:外接电容管脚2; 12脚:时钟输入端; 5脚:BCD 码输出端; 13脚:复位端; 6脚:BCD 码输出端; 14脚:数据溢出端; 7脚:BCD 码输出端; 15脚:数据选择输出端; 8脚:接地; 16脚:电源。

图4 CD4553引脚排列4.3基准时间产生单元电路设计时基电路用来产生一个方波定时脉冲,用来控制计数器CD4553的计数允许端INH,以便使计数器在定时脉冲宽度固定的时间内对脉搏电脉冲计数,固定时间为1min 或30s 。

为得到精确的定时信号,采用振荡,分频的方法,在设计中选用CD4060 14级二进制串行计数/分频器来完成这种功能。

COUT 和COUT 端外接定时R 、C 元件构成振荡器。

调节RV1、RV2能使其震荡频率为273Hz ,那么其周期为1s 273。

如果从Q14输出,那么从定时开始到Q14输出高电平所需⨯时间为141s 260s 273⨯=。

如果从Q13输出,那么从定时开始到Q13输出高电平所需时间为131s 230s 273⨯=。

一旦Q14或Q13为高电平,那么CD4553的INH 也为高电平,计数器停止计数。

计数值不变送译码器后由数码管显示出这个稳定的计数值,即为1分钟的脉搏次数。

这个值能稳定一段时间后继续计数,但这段时间足够记录数值了。

若要重新计数,则按下复位按钮,CD4060和CD4553同时清零。

单元电路如下图所示。

图5 基准时间产生单元电路4.3.1 14级二进制串行计数/分频器CD4060特性CD4060由一个振荡器和14个T 触发器组成。

在时钟输入端设有施密特触发器,能自动对输入信号进行整形,允许对上升或下降缓慢的信号计数或分频,计数输出端仅有Q4—Q10、Q12—Q14等10个引出端。

当复位端R 为高电平时,计数器复位,Q4—Q10、Q12—Q14输出低电平。

计数脉冲由COUT 和CIN 输入,当COUT 和CIN 为脉冲下降沿时,计数器进1。

CIN 、COUT 和COUT 外接定时R 、C 元件或石英晶体构成振荡器。

当V 为10V 时,震荡频率允许为12MHz ,可由Q4—Q10、Q12—Q14得到所需的分频输出,常用于分频定时器和时间延迟电路。

4.3.2 14级二进制串行计数/分频器CD4060引脚说明Qn :二进制计数输出端 R :计数器复位端1φ 、0φ 、0φ:外接R 、C 元件或晶体构成振荡器作为时钟信号输入引脚排列如下图。

图6 CD4060引脚排列4.4译码显示单元电路设计CD4511 BCD锁存,7段译码、驱动器作为译码显示电路的核心部分,与三位一体共阴极数码管配合,作为显示输出。

CD4553输出的BCD码由Q0—Q3端输出到七段译码驱动器CD4511的A、B、C、D端,由它译码后经限流电阻R9—R15驱动共阴极数码管显示计数值。

本电路中不需要CD4511的灯测试及消隐功能,也不用其锁定功能,故将LT和BI端接Vdd,LE端接地。

单元电路图如下所示。

图7 译码显示单元电路4.4.1 BCD锁存,7段译码,驱动器CD4511特性CD4511是BCD七段锁存器式译码器,译码、驱动器由译码器和输出缓冲器构成,输出电流最大值可达25mA。