91R1DR28B10R51中文资料

国产ds1991L-F5 参数说明书

SELOCKEY.SOA§ 1,152-bit secure read/write, nonvolatilememory§ Secure memory cannot be decipheredwithout matching 64-bit password§ Memory is partitioned into 3 blocks of 384bits each§ 64-bit password and ID fields for eachmemory block§ 512-bit scratchpad ensures data transferintegrity§ Operating temperature range: -40°C to+70°C§ Over 10 years of data retentionCOMMON Button FEATURES§ Unique, factory-lasered and tested 64-bitregistration number (8-bit family code + 48-bit serial number + 8-bit CRC tester) assures absolute traceability because no two parts are alike§ Multidrop controller for MicroBUS§ Digital identification and information bymomentary contact§ Chip-based data carrier compactly storesinformation§ Data can be accessed while affixed to object § Economically communicates to bus masterwith a single digital signal at 16.3k bits per second§ Standard 16 mm diameter and 1-Busprotocol ensure compatibility with Button family§ Button shape is self-aligning with cup-shaped probes§ Durable stainless steel case engraved withregistration number withstands harsh environments§ Easily affixed with self-stick adhesivebacking, latched by its flange, or locked with a ring pressed onto its rim§ Presence detector acknowledges when readerfirst applies voltageF5 MICROCAN TMAll dimensions shown in millimetersORDERING INFORMATIONTM1991L-F5F5 MicroCanTM1991MultiKey Button TMTM1991 Button DESCRIPTIONThe TM1991 MultiKey Button is a rugged read/write data carrier that acts as three separate electronic keys, offering 1,152 bits of secure, nonvolatile memory. Each key is 384 bits long with distinct 64-bit password and public ID fields (Figure 1). The password field must be matched in order to access the secure memory. Data is transferred serially via the 1-Bus protocol, which requires only a single data lead and a ground return. The 512-bit scratchpad serves to ensure integrity of data transfers to secure memory. Data should first be written to the scratchpad where it can be read back. After the data has been verified, a copy scratchpad command will transfer the data to the secure memory. This process ensures data integrity when modifying the memory. A 48-bit serial number is factory lasered into each TM1991 to provide a guaranteed unique identity which allows for absolute traceability. The family code for the TM1991 is 02h. The durable MicroCan package is highly resistant to environmental hazards such as dirt, moisture and shock. Its compact button-shaped profile is self-aligning with mating receptacles, allowing the TM1991 to be easily used by human operators. Accessories permit the TM1991 to be mounted on plastic key fobs, photo-ID badges, printed-circuit boards or any smooth surface of an object. Applications include secure access control, debit tokens, work-in-progress tracking, electronic travelers and proprietary data.OPERATIONThe TM1991 is accessed via a single data line using the 1-Bus protocol. The bus master must first provide one of the four ROM Function Commands, 1) Read ROM, 2) Match ROM, 3) Search ROM, 4) Skip ROM. These commands operate on the 64-bit lasered ROM portion of each device and can singulate a specific device if many are present on the 1-Bus line as well as indicate to the bus master how many and what types of devices are present. The protocol required for these ROM Function Commands is described in Figure 9. After a ROM Function Command is successfully executed, the memory functions that operate on the secure memory and the scratchpad become accessible and the bus master may issue any one of the six Memory Function Commands specific to the TM1991. The protocol for these Memory Function Commands is described in Figure 5. All data is read and written least significant bit first.64-BIT LASERED ROMEach TM1991 contains a unique ROM code that is 64 bits long. The first eight bits are a 1-Bus family code. The next 48 bits are a unique serial number. The last eight bits are a CRC of the first 56 bits. (Figure 2.) The 1-Bus CRC is generated using a polynomial generator consisting of a shift register and XOR gates as shown in Figure 3. The polynomial is X8 + X5 + X4 + 1. Additional information about the Dallas 1-Bus Cyclic Redundancy Check is available in the Book of TM19xx Button Standards. The shift register bits are initialized to zero. Then starting with the least significant bit of the family code, one bit at a time is shifted in. After the 8th bit of the family code has been entered, then the serial number is entered. After the 48th bit of the serial number has been entered, the shift register contains the CRC value. Shifting in the eight bits of CRC should return the shift register to all zeros.MEMORY FUNCTION COMMANDSThe TM1991 has six device-specific commands. Three scratchpad commands: Write Scratchpad, Read Scratchpad and Copy Scratchpad and three subkey commands: Write Password, Write Subkey and Read Subkey. After the device is selected, the memory function command is written to the TM1991. The command is comprised of three fields, each one byte long. The first byte is the function code field. This field defines the six commands that can be executed. The second byte is the address field. The first six bits of this field define the starting address of the command. The last two bits of this field are the subkey address code. The third byte of the command is a complement of the second byte (Figure 4).TM1991 For the first use, since the passwords actually stored in the device are unknown, the TM1991 needs to be initialized. This is done by directly writing (i. e., not through the scratchpad) the new identifier and password for the selected subkey using the Write Password command. As soon as the new identifier and password are stored in the device, further updates should be done through the scratchpad.MEMORY MAP Figure 1* Each subkey or the scratchpad has its own unique address.64-BIT LASERED ROM Figure 28-Bit CRC Code48-Bit Serial Number8-Bit Family Code (02H) MSB LSB MSB LSB MSB LSB1-BUS CRC GENERATOR Figure 3TM1991 COMMAND STRUCTURE Figure 42nd byte3rd byte Command1st byteB7 B6B5 B4 B3 B2 B1 B0writescratchpad96H readscratchpad69H 1 1any value00H to 3FHcopyscratchpad3CH0 0 0 0 0 0readSubKey66H writeSubKey99Hany value 10H to 3FHwritepassword5AH Sub-KeyNr.:00or01or100 0 0 0 0 0ones complementof 2nd byteSCRATCHPAD COMMANDSThe 64-byte read/write scratchpad of the TM1991 is not password-protected. Its normal use is to build up a data structure to be verified and then copied to a secure subkey.Write Scratchpad [96H]The Write Scratchpad command is used to enter data into the scratchpad. The starting address for the write sequence is specified in the command. Data can be continuously written until the end of the scratchpad is reached or until the TM1991 is reset. The command sequence is shown in Figure 5, first page, left column.Read Scratchpad [69H]The Read Scratchpad command is used to retrieve data from the scratchpad. The starting address is specified in the command word. Data can be continuously read until the end of the scratchpad is reached or until the TM1991 is reset. The command sequence is shown in Figure 5, first page, center column.Copy Scratchpad [3CH]The Copy Scratchpad command is used to transfer specified data blocks from the scratchpad to a selected subkey. This command should be used when data verification is required before storage in a secure subkey. Data can be transferred in single 8-byte blocks or in one large 64-byte block. There are nine valid block selector codes that are used to specify which block is to be transferred (Figure 6). As a further precaution against accidental erasure of secure data, the 8-byte password of the destination subkey must be entered. If the password does not match, the operation is terminated. After the block of data is transferred to the secure subkey, the original data in the corresponding block of the scratchpad is erased. The command sequence is shown in Figure 5, first page, right column.SUBKEY COMMANDSEach of the subkeys within the TM1991 is accessed individually. Transactions to read and write data to a secured subkey start at the address defined in the command and proceed until the device is reset or the end of the subkey is reached.Write Password [5AH]The Write Password command is used to enter the ID and password of the selected subkey. This command will erase all of the data stored in the secure area as well as overwriting the ID and password fields with the new data. The TM1991 has a built-in check to ensure that the proper subkey was selected. The sequence begins by reading the ID field of the selected subkey; the ID of the subkey to be changed is then written into the part. If the IDs do not match, the sequence is terminated. Otherwise, the subkey contents are erased and 64 bits of new ID data are written followed by a new 64-bit password. The command sequence is shown in Figure 5, 2nd page, right column.MEMORY FUNCTIONS FLOW CHART Figure 5TMTMTMTMMEMORY FUNCTIONS FLOW CHART (cont’d) Figure 5 TMTMTM TMBLOCK SELECTOR CODES OF THE TM1991 Figure 6Block Nr.Address Range LS Byte Codes MS Byte0 to 700 to 3FH56567F51575D5A7F0identifier9A9A B39D646E694C1password9A9A4C629B91694C210H to 17H9A65B3629B6E964C318H to 1FH6A6A436D6B616643420H to 27H9595BC92949E99BC528H to 2FH659A4C9D649169B3630H to 37H6565B39D646E96B3738H to 3FH65654C629B9196B3Write SubKey [99H]The Write Subkey command is used to enter data into the selected subkey. Since the subkeys are secure, the correct password is required to access them. The sequence begins by reading the ID field; the password is then written back. If the password is incorrect, the transaction is terminated. Otherwise, the data following is written into the secure area. The starting address for the write sequence is specified in the command word. Data can be continuously written until the end of the secure subkey is reached or until the TM1991 is reset. The command sequence is shown in Figure 5, 2nd page, center column. Read SubKey [66H]The Read Subkey command is used to retrieve data from the selected subkey. Since the subkeys are secure, the correct password is required to access them. The sequence begins by reading the ID field; the password is then written back. If the password is incorrect, the TM1991 will transmit random data. Otherwise the data can be read from the subkey. The starting address is specified in the command. Data can be continuously read until the end of the subkey is reached or until the TM1991 is reset. The command sequence is shown in Figure 5, 2nd page, left column.1-Bus BUS SYSTEMThe 1-Bus bus is a system which has a single bus master and one or more slaves. In all instances, the TM1991 is a slave device. The bus master is typically a micro-controller. The discussion of this bus system is broken down into three topics: hardware configuration, transaction sequence, and 1-Bus signaling (signal types and timing). A 1-Bus protocol defines bus transactions in terms of the bus state during specified time slots that are initiated on the falling edge of sync pulses from the bus master. For a more detailed protocol description, refer to Chapter 4 of the Book of TM19xx Button Standards.HARDWARE CONFIGURATIONThe 1- bus has only a single line by definition; it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Bus bus must have an open drain connections or 3-state outputs. The TM1991 is an open drain part with an internal circuit equivalent to that shown in Figure 7. The bus master can be the same equivalent circuit. If a bidirectional pin is not available, separate output and input pins can be tied together.The bus master requires a pullup resistor at the master end of the bus, with the bus master circuit equivalent to the one shown in Figures 8a and 8b. The value of the pullup resistor should be approximately 5 k W for short line lengths.A multidrop bus consists of a 1-Bus bus with multiple slaves attached. The 1-Bus bus has a maximum data rate of 16.3k bits per second. The idle state for the 1-Bus bus is high. If, for any reason a transactionTM1991needs to be suspended, the bus MUST be left in the idle state if the transaction is to resume. If this does not occur, and the bus is left low for more than 120 m s, one or more of the devices on the bus may be reset.EQUIVALENT CIRCUIT Figure 7BUS MASTER CIRCUIT Figure 8TMTMTMTRANSACTION SEQUENCEThe protocol for accessing the TM1991 via the 1-Bus port is as follows:§Initialization§ROM Function Command§Memory Function Command§Transaction/DataINITIALIZATIONAll transactions on the 1-Bus bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the bus master followed by presence pulse(s) transmitted by the slave(s). The presence pulse lets the bus master know that the TM1991 is on the bus and is ready to operate. For more details, see the “1-Bus Signaling” sectionROM FUNCTION COMMANDSOnce the bus master has detected a presence pulse, it can issue one of the four ROM function commands. All ROM function commands are eight bits long. A list of these commands follows (refer to flowchart in Figure 9).Read ROM [33H]This command allows the bus master to read the TM1991’s 8-bit family code, unique 48-bit serial number and 8-bit CRC. This command can be used only if there is a single TM1991 on the bus. If more than one slave is present on the bus, a data collision will occur when all slaves try to transmit at the same time (open drain will produce a wired-AND result).Match ROM [55H]The match ROM command, followed by a 64-bit ROM sequence, allows the bus master to address a specific TM1991 on a multidrop bus. Only the TM1991 that exactly matches the 64-bit ROM sequence will respond to the subsequent memory function command. All slaves that do not match the 64-bit ROM sequence will wait for a reset pulse. This command can be used with a single or multiple devices on the bus.Skip ROM [CCH]This command can save time in a single drop bus system by allowing the bus master to access the memory functions without providing the 64-bit ROM code. If more than one slave is present on the bus and a read command is issued following the Skip ROM command, data collision will occur on the bus as multiple slaves transmit simultaneously (open drain will produce a wired-AND result).Search ROM [F0H]When a system is initially brought up, the bus master might not know the number of devices on the 1-Wire bus or their 64-bit ROM codes. The Search ROM command allows the bus master to use a process of elimination to identify the 64-bit ROM codes of all slave devices on the bus. The ROM search process is the repetition of a simple 3-step routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master performs this simple 3-step routine on each bit of the ROM. After one complete pass, the bus master knows the contents of the ROM in one device. The remaining number of devices and their ROM codes may be identified by additional passes. See Chapter 5 of the Book of TM19xx Button Standards for a comprehensive discussion of a search ROM, including an actual example.1-BUS SIGNALINGThe TM1991 requires strict protocols to ensure data integrity. The protocol consists of four types of signaling on one line: Reset Sequence with Reset Pulse and Presence Pulse, Write 0, Write 1 and Read Data. All these signals except presence pulse are initiated by the bus master. The initialization sequence required to begin any communication with the TM1991 is shown in Figure 10. A reset pulse followed by a presence pulse indicates the TM1991 is ready to send or receive data given the correct ROM command and memory function command. The bus master transmits (TX) a reset pulse (t RSTL , minimum 480 m s).The bus master then releases the line and goes into receive mode (RX). The 1-Bus bus is pulled to a high state via the pullup resistor. After detecting the rising edge on the data pin, the TM1991 waits (t PDH , 15-60m s) and then transmits the presence pulse (t PDL , 60-240 m s).ROM FUNCTIONS FLOW CHART Figure 9TMTMTMTM TMTM TMTMTMTMINITIALIZATION PROCEDURE “RESET AND PRESENCE PULSES” Figure 10480 m s £ t RSTL < ¥ *480 m s £ t RSTH < ¥(includes recovery time)15 m s £ t PDH < 60 m s 60 m s £ t PDL < 240 m s* In order not to mask interrupt signaling by other devices on the 1-Bus bus, tRSTL + t R should alwaysbe less than 960 m s.READ/WRITE TIME SLOTSThe definitions of write and read time slots are illustrated in Figure 11. All time slots are initiated by the master driving the data line low. The falling edge of the data line synchronizes the TM1991 to the master by triggering a delay circuit in the TM1991. During write time slots, the delay circuit determines when the TM1991 will sample the data line. For a read data time slot, if a “0” is to be transmitted, the delay circuit determines how long the TM1991 will hold the data line low overriding the 1 generated by the master. If the data bit is a “1”, the Button will leave the read data time slot unchanged.READ/WRITE TIMING DIAGRAM Figure 11Write-One Time Slot60 m s £ t SLOT < 120 m s1 m s £ t LOW1< 15 m s 1 m s £ t REC < ¥TMREAD/WRITE TIMING DIAGRAM (cont’d) Figure 11Write-Zero Time Slot60 m s < t LOW0 < t SLOT < 120 m s 1 m s < t REC < ¥Read-Data Time Slot60 m s £ t SLOT < 120 m s 1 m s £ t LOWR < 15 m s 0 £ t RELEASE < 45 m s 1 m s £ t REC < ¥t RDV = 15 m s t SU < 1 m sTMPHYSICAL SPECIFICATIONSSize See mechanical drawingWeight 3.3 gramsHumidity 90% RH at 50°CAltitude 10,000 feetExpected Service Life 10 years at 25°C (150 million transactions, see note 4) Safety Meets UL#913 (4th Edit.); Intrinsically Safe Apparatus,Approved under Entity Concept for use in Class I, Division1, Group A, B, C and D LocationsABSOLUTE MAXIMUM RATINGS*Voltage on any Pin Relative to Ground -0.5V to +7.0VOperating Temperature -40°C to +70°CStorage Temperature -40°C to +70°C*This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.DC ELECTRICAL CHARACTERISTICS (V PUP *=2.8V to 6.0V; -40°C to +70°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Input Logic Low V IL-0.30.8V1 Input Logic High V IH 2.2 6.0VOutput Logic Low @ 4 mA V OL0.4VOutput Logic High V OH V PUP 6.0V1,2 Input Resistance V IL500k W3* V PUP = external pullup voltageAC ELECTRICAL CHARACTERISTICS (-40°C to 70°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Time Slot Period t SLOT60120m sWrite 1 Low Time t LOW1115m sWrite 0 Low Time t LOW060120m sRead Data Valid t RDV exactly 15m sRelease Time t RELEASE01545m sRead Data Setup t SU1m s5 Recovery Time t REC1m sReset Low Time t RSTL480m sReset High Time t RSTH480m s4 Presence Detect High t PDH1560m sPresence Detect Low t PDL60240m sNOTES:1.All voltages are referenced to ground.2.V PUP= external pullup voltage to system supply.3.Input pulldown resistance to ground.4.An additional reset or communication sequence cannot begin until the reset high time has expired.5.Read data setup time refers to the time the host must pull the 1-Bus bus low to read a bit. Data isguaranteed to be valid within 1 m s of this falling edge and will remain valid for 14 m s minimum.。

ZSPM9000Al1R中文资料(ZMDI)中文数据手册「EasyDatasheet - 矽搜」

芯片9121参数

芯片9121参数全文共四篇示例,供读者参考第一篇示例:芯片9121参数是指搭载在一款芯片产品上的具体参数和性能指标。

芯片9121是一款常见的芯片型号,其参数包括芯片尺寸、工作电压、功耗、工作频率、接口类型等。

以下是对芯片9121参数的详细介绍。

芯片9121的尺寸是指芯片的物理尺寸大小。

一般来说,芯片尺寸越小,集成度越高,功耗越低。

芯片9121的尺寸为10mm*10mm*1mm,这个尺寸适合用于移动设备或物联网设备等小型产品的设计。

芯片9121的工作电压是指芯片在工作状态下所需的电压值。

芯片9121的工作电压范围为1.8V-3.3V,在这个范围内,芯片能够正常稳定地工作,保证数据传输的准确性和稳定性。

芯片9121的功耗是指芯片在正常工作状态下消耗的电能大小。

芯片9121的功耗为100mW,这个功耗水平相对较低,适合用于对功耗要求较高的产品设计。

芯片9121的接口类型是指芯片与外部设备或系统之间通信的接口类型。

芯片9121支持USB接口和SPI接口,这些接口能够满足不同产品设计的需求。

芯片9121的参数包括尺寸、工作电压、功耗、工作频率、接口类型等,这些参数能够全面展现芯片的性能和特性,为产品设计提供了重要的参考依据。

在选择芯片9121时,需要根据产品的具体需求来确定最适合的芯片参数配置,以确保产品的性能和稳定性。

【文章结束】第二篇示例:芯片9121是一种高性能的集成电路芯片,广泛应用于各种电子设备中。

它具有多种功能和特性,包括高频率、低功耗、高可靠性等优点,适用于各种场合和应用领域。

本文将详细介绍芯片9121的主要参数和特性,帮助读者了解这款芯片的性能和用途。

芯片9121的主要参数包括工作频率、功耗、传输速率、工作温度等。

该芯片的工作频率通常在几百兆赫至数千兆赫之间,可以实现高速数据处理和传输。

功耗方面,芯片9121具有低功耗特性,能够有效节省能源,延长电池续航时间。

传输速率是衡量芯片性能的重要指标之一,在芯片9121中,传输速率通常在几十兆比特每秒至几百兆比特每秒之间,可以实现快速数据传输和处理。

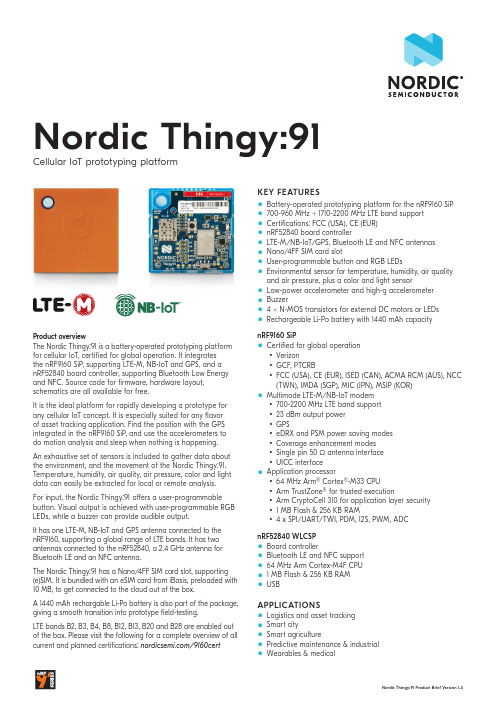

Nordic Thingy 91产品简要说明版本1.4说明书

RGB LEDs

Temperature, humidity, air quality

and air pressure Light/color sensor

Buzzer

2.4 GHz antenna

Low-power accelerometer PMIC Battery connector Power switch

Nordic Thingy:91 Product Brief Verent Program/debug device

selection switch nRF9160 SiP

nRF52840 WLCSP

High-g accelerometer

Nano/4FF SIM card slot

An exhaustive set of sensors is included to gather data about the environment, and the movement of the Nordic Thingy:91. Temperature, humidity, air quality, air pressure, color and light data can easily be extracted for local or remote analysis.

and air pressure, plus a color and light sensor Low-power accelerometer and high-g accelerometer Buzzer 4 x N-MOS transistors for external DC motors or LEDs Rechargeable Li-Po battery with 1440 mAh capacity

AT91SAM7X256中文版

– 64K 字节 (AT91SAM7X256) – 32K 字节 (AT91SAM7X128)

• 内存控制器 (MC)

– 嵌入式 Flash 控制器, 中止状态和未对齐检测

• 复位控制器 (RSTC)

– 基于上电复位单元和经过工厂标定的低功耗掉电检测 – 提供外部信号整形和复位源状态

2. AT91SAM7X256 和 AT91SAM7X128 的配置比较

AT91SAM7X256 和 AT91SAM7X128 仅在存储器大小上有所差别。Table 2-1 是这两个设备的主 要配置差别。

Table 2-1. 配置差别

设备 AT91SAM7X256 AT91SAM7X128

Flash 256K 字节 128K 字节

欢迎访问本公司网站 /

免责声明

本资料英文版本来源于互联网,将其译成中文版本以便于中国广大ARM爱好者交 流、学习,请勿用于任何商业目的。

本文件为英文原本之非正式翻译,不保证翻译的真实性和准确性,同时声明文件以英 文版本为准。

由于嵌入式领域我国并无统一名称规范,大部分术语均直译,另有部分术语参考了 ATMEL 公司的 AT91SAM7S64 中文资料,由于译者对嵌入式领域理解的深度有限,难 免有疏漏和错误之处,也希望大家指出。

– 8 个完全可编程消息对象邮箱, 16 位时间标志计数器

• 一个同步串行控制器 (SSC)

– 每个接受器和发送器都有独立的时钟和帧同步信号 – 支持I²S 模拟接口, 支持分时复用 – 支持 32 位数据传输的高速连续数据流功能

• 两个通用同步/异步收发器 (USART)

– 独立的波特率发生器, 可以 IrDA 红外调制/解调 – 支持 ISO7816 T0/T1 智能卡, 硬件握手信号以及 RS485 – USART1 口支持全 Modem 线

R51技术说明书(SNK)V1.2(4903101246 )

注意

1、 严禁带电插拔。 2、 请先切断电源,并等待5秒后再进行电气设备连接。

注意静电

本控制器为静电敏感设备,在使用和维护中请注意采取防静电措施。

本手册版权归宁波柯力传感科技股份有限公司所有,未经书面许可任何人不得进行完善和升级,宁波柯力传感科技股份有限公司保留修改本手册的权利。 修改手册恕不另行通知。

4.2.1 电源............................................................................................................................................................................. 5 4.2.2 传感器接口 ................................................................................................................................................................ 5 4.2.3 串行口......................................................................................................................................................................... 5 4.2.4 输入口......................................................................................................................................................................... 5 4.2.5 输出口......................................................................................................................................................................... 7 4.2.6 主板开关定义............................................................................................................................................................ 9

91 91 无线测温主机 使用说明书

91*91无线测温主机使用说明书目录一、产品概述 (3)二、无线测温系统结构 (3)2.1无线测温系统结构图 (3)2.2无线温度传感器原理结构图 (4)三、主要技术参数 (4)3.1主要功能: (4)3.2技术指标 (6)四、显示与参数设置 (7)4.1显示面板 (7)4.2参数设置 (7)4.2.1报警开关设置 (7)4.2.2参数查看 (9)4.2.3参数设置 (10)4.2.4极限温度记录 (11)4.2.5温度报警记录 (12)4.2.6温度失衡记录 (13)4.2.7恢复出厂设置 (13)4.2.8清除所有用户数据 (14)五、接线方式 (16)六、外形尺寸及安装方式 (16)七、无线测温系统典型组网方式 (17)八、维修及维护 (18)8.1有限保用条款 (18)8.2有限保用范围 (18)8.3法律责任范围 (18)附录一:典型接线图 (19)一、产品概述高压电气设备温度监测点都处于高电压、大电流、强磁场的环境中,甚至有的监测点还处在密闭的空间中,由于强电磁噪声和高压绝缘、空间的限制等问题,通常的温度测量方法无法解决这些问题导致无法使用。

我公司自主开发设计的无线温度监测系统采用无线电波进行信号传输。

传感器安装在高压设备上,与接收设备之间无电气连接,因此该系统从根本上解决了高压设备接点运行温度不易实时在线监测的难题。

无线温度监测系统具有极高的可靠性和安全性,可直接安装到每台高压开关、母线接头、户外刀闸、变压器等容易产生高温的电气接点处。

系统配备标准通讯接口,可联网运行。

通过上位机软件,可记录高压设备实时运行温度的数据。

为高压设备的维修提供历史数据,实现了高压设备热故障预知维护。

二、无线测温系统结构2.1无线测温系统结构图2.2无线温度传感器原理结构图无线温度传感器用于测量高压带电物体表面或接点处的温度,如高压开关柜内的裸露触点、母线连接处、户外刀闸及变压器等的运行温度。

无线温度传感器是由温度传感器、信号调制放大、逻辑控制电路、无线调制接口等组成(如下图所示)。

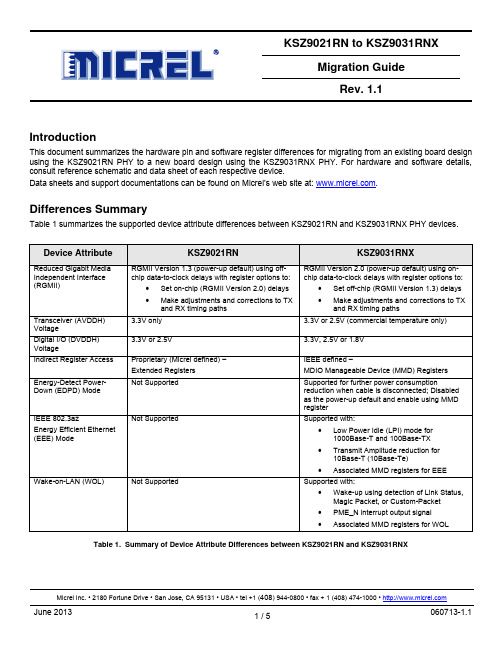

KSZ9021RN to KSZ9031RNX Migration Guide

KSZ9021RN to KSZ9031RNXMigration GuideRev. 1.1IntroductionThis document summarizes the hardware pin and software register differences for migrating from an existing board design using the KSZ9021RN PHY to a new board design using the KSZ9031RNX PHY. For hardware and software details, consult reference schematic and data sheet of each respective device.Data sheets and support documentations can be found on Micrel’s web site at: .Differences SummaryTable 1 summarizes the supported device attribute differences between KSZ9021RN and KSZ9031RNX PHY devices.Device Attribute KSZ9021RN KSZ9031RNXReduced Gigabit Media Independent Interface (RGMII) RGMII Version 1.3 (power-up default) using off-chip data-to-clock delays with register options to:•Set on-chip (RGMII Version 2.0) delays•Make adjustments and corrections to TXand RX timing pathsRGMII Version 2.0 (power-up default) using on-chip data-to-clock delays with register options to:•Set off-chip (RGMII Version 1.3) delays•Make adjustments and corrections to TXand RX timing pathsTransceiver (AVDDH)Voltage3.3V only 3.3V or 2.5V (commercial temperature only)Digital I/O (DVDDH)Voltage3.3V or 2.5V 3.3V, 2.5V or 1.8VIndirect Register Access Proprietary (Micrel defined) –Extended Registers IEEE defined –MDIO Manageable Device (MMD) RegistersEnergy-Detect Power-Down (EDPD) Mode Not Supported Supported for further power consumptionreduction when cable is disconnected; Disabledas the power-up default and enable using MMDregisterIEEE 802.3azEnergy Efficient Ethernet (EEE) Mode Not Supported Supported with:•Low Power Idle (LPI) mode for1000Base-T and 100Base-TX•Transmit Amplitude reduction for10Base-T (10Base-Te)•Associated MMD registers for EEEWake-on-LAN (WOL) Not Supported Supported with:•Wake-up using detection of Link Status,Magic Packet, or Custom-Packet•PME_N interrupt output signal•Associated MMD registers for WOL Table 1. Summary of Device Attribute Differences between KSZ9021RN and KSZ9031RNXPin DifferencesTable 2 summarizes the pin differences between KSZ9021RN and KSZ9031RNX PHY devices. Pin #KSZ9021RNKSZ9031RNXPin NameType Pin FunctionPin NameTypePin Function1 AVDDH P 3.3V analog V DD AVDDH P 3.3V/2.5V (commercial temp only) analog V DD 12 AVDDH P 3.3V analog V DD AVDDH P 3.3V/2.5V (commercial temp only) analog V DD 13VSS_PSGndDigital groundNC–No connectThis pin is not bonded and can be connected to digital ground for footprint compatibility with the Micrel KSZ9021RN Gigabit PHY.16 DVDDH P3.3V / 2.5V digital V DD DVDDH P 3.3V, 2.5V, or 1.8V digital V DD_I/O 17 LED1 /PHYAD0I/OLED Output:Programmable LED1 OutputConfig Mode:The pull-up/pull-down value is latched as PHYAD[0] during power-up / reset.LED1 /PHYAD0 /PME_N1I/O LED1 output:Programmable LED1 outputConfig mode:The voltage on this pin issampled and latched during the power-up/reset process to determine the value of PHYAD[0].PME_N output:Programmable PME_N output (pin option 1). This pin function requires an external pull-up resistor to DVDDH (digital V DD_I/O ) in a range from 1.0k Ω to 4.7k Ω. When asserted low, this pin signals that a WOL event has occurred.When WOL is not enabled, this pin function behaves as per the KSZ9021RN pin definition.This pin is not an open-drain for all operating modes.34 DVDDH P3.3V / 2.5V digital V DD DVDDH P 3.3V, 2.5V, or 1.8V digital V DD_I/O38 INT_N O Interrupt OutputThis pin provides aprogrammable interrupt output and requires an external pull-up resistor to DVDDH in the range of 1K to 4.7K ohms for active low assertion.INT_N/O Interrupt OutputThis pin provides aprogrammable interrupt output and requires an external pull-up resistor to DVDDH in the range of 1K to 4.7K ohms for active low assertion.This pin is an open-drain.PME_N2 PME_N output: Programmable PME_N output (pin option 2). When asserted low, this pin signals that a WOL event has occurred.When WOL is not enabled, this pin function behaves as per the KSZ9021RN pin definition. This pin is not an open-drain for all operating modes.40 DVDDH P 3.3V / 2.5V digital V DD DVDDHP3.3V, 2.5V, or 1.8V digitalV DD_I/O47 AVDDH P 3.3V analog V DD NC–NoconnectThis pin is not bonded and canbe connected to AVDDH powerfor footprint compatibility withthe Micrel KSZ9021RN GigabitPHY.48 ISET I/O Set transmit output levelConnect a 4.99KΩ 1%resistor to ground on thispin. ISET I/O Set the transmit output levelConnect a 12.1kΩ 1% resistorto ground on this pin.Table 2. Pin Differences between KSZ9021RN and KSZ9031RNXStrapping Option DifferencesThere is no strapping pin difference between KSZ9021RN and KSZ9031RNX.Register Map DifferencesThe register space within the KSZ9021RN and KSZ9031RNX consists of direct-access registers and indirect-access registers.Direct-access RegistersThe direct-access registers comprise of IEEE-Defined Registers (0h – Fh) and Vendor-Specific Registers (10h – 1Fh). Between the KSZ9021RN and KSZ9031RNX, the direct-access registers and their bits have the same definitions, except for the following registers in Table 3.Direct-access RegisterKSZ9021RN KSZ9031RNXName Description Name Description3h PHYIdentifier2 Bits [15:10] (part of OUI) – same asKSZ9031RNXBits [9:4] (model number) – unique forKSZ9021RNBits [3:0] (revision number) – uniquedepending on chip revision PHY Identifier 2 Bits [15:10] (part of OUI) – same asKSZ9021RNBits [9:4] (model number) – unique forKSZ9031RNXBits [3:0] (revision number) – uniquedepending on chip revisionBh ExtendedRegister –Control Indirect Register AccessSelect read/write control andpage/address of Extended RegisterReserved ReservedDo not change the default value ofthis registerCh ExtendedRegister –Data Write Indirect Register AccessValue to write to Extended RegisterAddressReserved ReservedDo not change the default value ofthis registerDh ExtendedRegister –Data Read Indirect Register AccessValue read from Extended RegisterAddressMMD Access –ControlIndirect Register AccessSelect read/write control and MMDdevice addressEh Reserved ReservedDo not change the default value ofthis register MMD Access –Register/DataIndirect Register AccessValue of register address/data for theselected MMD device address1Fh, bit [1] Software Reset 1 = Reset chip, except all registers0 = Disable resetReserved ReservedTable 3. Direct-access Register Differences between KSZ9021RN and KSZ9031RNXIndirect-access RegistersThe indirect register mapping and read/write access are completely different for the KSZ9021RN (uses Extended Registers) and KSZ9031RNX (uses MMD Registers). Refer to respective devices’ data sheets for details.Indirect registers provide access to the following commonly used functions:•1000Base-T link-up time control (KSZ9031RNX only)• Pin strapping status• Pin strapping override•Skew adjustments for RGMII clocks, control signals, and datao Resolution of skew steps are different between KSZ9021RN and KSZ9031RNX•Energy-Detect Power-Down Mode enable/disable (KSZ9031RNX only)•Energy Efficient Ethernet function (KSZ9031RNX only)•Wake-on-LAN function (KSZ9031RNX only)Revision HistoryRevision Date Summary of ChangesMigration Guide created1.0 12/7/121.1 6/7/13 Indicate PME_N1 (pin 17) for KSZ9031RNX is not an open-drain.Indicate INT_N (pin 38) is an open-drain for KSZ9021RN, but is not an open-drain for KSZ9031RNX.Indicate direct-access register 1Fh, bit [1] difference.。