计算机组成原理运算器实验—算术逻辑运算实验

计算机组成原理实验报告

计算机组成原理实验报告实验报告运算器实验⼀、实验⽬的掌握⼋位运算器的数据传输格式,验证运算功能发⽣器及进位控制的组合功能。

⼆、实验要求完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运⽤。

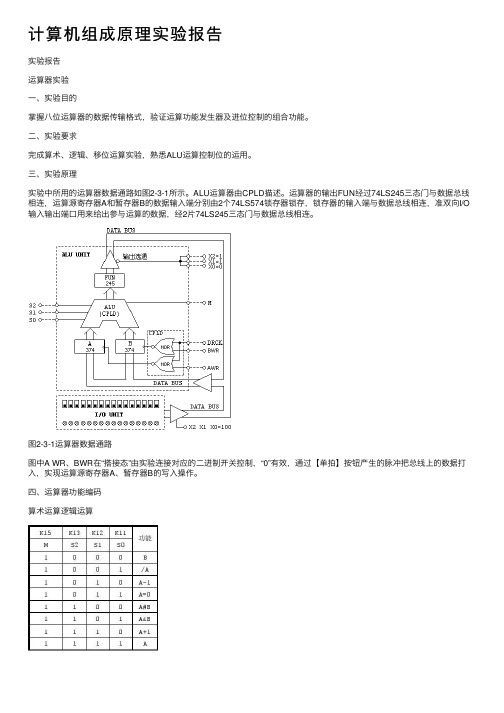

三、实验原理实验中所⽤的运算器数据通路如图2-3-1所⽰。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输⼊端分别由2个74LS574锁存器锁存,锁存器的输⼊端与数据总线相连,准双向I/O 输⼊输出端⼝⽤来给出参与运算的数据,经2⽚74LS245三态门与数据总线相连。

图2-3-1运算器数据通路图中A WR、BWR在“搭接态”由实验连接对应的⼆进制开关控制,“0”有效,通过【单拍】按钮产⽣的脉冲把总线上的数据打⼊,实现运算源寄存器A、暂存器B的写⼊操作。

四、运算器功能编码算术运算逻辑运算K23~K0置“1”,灭M23~M0控位显⽰灯。

然后按下表要求“搭接”部件控制路。

表2.3.2 运算实验电路搭接表算术运算1.运算源寄存器写流程通过I/O单元“S7~S0”开关向累加器A和暂存器B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K18=K17=“1”,按下流程分别读A、B。

3.加法与减法运算令M S2 S1 S0(K15 K13~K11=0100),为算术加,FUN及总线单元显⽰A+B的结果令M S2 S1 S0(K15 K13~K11=0101),为算术减,FUN及总线单元显⽰A-B的结果。

逻辑运算1.运算源寄存器写流程通过“I/O输⼊输出单元”开关向寄存器A和B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K17= K18=1,按下流程分别读A、B。

①若运算控制位设为(M S2 S1 S0=1111)则F=A,即A内容送到数据总线。

②若运算控制位设为(M S2 S1 S0=1000)则F=B,即B内容送到数据总线。

(计算机组成原理)实验一运算器实验

D5

D4

D3

D2

CLK D1 D0

Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

D7

D DA2(74LS273)6

D5

D4

D3

D2

CLK D1 D0

返回

D7-D0

BUS TO ALU

Cn181

B-DA2 B-DA1

DA1,DA2:两片74LS273

❖ 74LS273:带清零端的8D寄存器 ❖ MR:异步清零信号(--接+5V) 返回 ❖ CP:时钟脉冲(--B-DA1、 B-DA2)

74LS245

B0 B1 B2 B3 B4 B5 B6 B7

18 17 16 15 14 13 12 11

D0 D1

D2 D3 D4 D5 D6 D7

19 1

E D IR

地址

Ai

+5

❖ 只有当I/O-R#和Ai同时=0时E#打开,开关 值BUS(D7~D0)

2、Input Device

❖ 输入设备(开关)的工作过程:

0FFH+01H (算术加) 5BH+0A0H+FC(算术加) 5BH∧0A0H(逻辑与) 79H+32H+FC(算术加)

返回

(一)实验原理逻辑框图

T4

74299

299-B M

S0 S1 S2 S3

ALU UNIT

ALU (74LS181) T4

进位 判零 电路

ALU-B

CyCn CyNCn M Ci

B-DA1

DA1 (74LS273)

DA2 (74LS273)

B-DA2

I/O-R INPUT

Ai=“0”

计算机组成原理运算器组成实验指导书

实验一运算器组成实验(一)算术逻辑运算实验一、实验目的1. 掌握简单运算器的数据传送通路。

2. 验证运算功能发生器(74LS181)的组合功能。

二、实验设备TDN-CM+计算机组成原理教学实验系统一台,排线若干。

三、实验内容1.实验原理实验中所用的运算器通路如图1-1所示。

其中运算器由两片74LS181以并/串形式构成8位字长的ALU。

运算器的输出经过一个三态门(74LS245)和数据总线相连,运算器的两个数据输入端分别由两个锁存器(74LS373)锁存,锁存器的输入连至数据总线,数据开关(“INPUT DEVICE”)用来给出参与运算的数据,并经过一三态门(74LS245)和数据总线相连,数据显示灯(“BUS UNIT”)已和数据总线相连,用来显示数据总线内容。

图1-1 运算器数据通路图2.图中已将用户需要连接的控制信号用圆圈标明(其他实验相同,不再说明),其中除T4为脉冲信号,其他均为电平信号。

由于实验电路中的时序信号均已连至“W/R UNIT”的相应时序信号引出端,因此,在进行实验时,只需将“W/R UNIT”的T4接至“STATE UNIT”的微动开关KK2的输出端,按动微动开关,即可获得实验所需的单脉冲,而S3、S2、S1、S0、Cn、M、LDDR1、LDDR2、ALU-B、SW-B各电平控制信号用“SWITCH UNIT”中的二进制数据开关来模拟,其中Cn、ALU-B、SW-B为低电平有效,LDDR1、LDDR2为高电平有效。

3.实验步骤1.按图1-2连接实验电路并检查无误。

图中将用户需要连接的信号线(其它实验相同,不再说明)。

2.开电源开关。

3.用输入开关向暂存器 DR1 置数。

①拨动输入开关形成二进制数 01100101(或其它数值)。

(数据显示灯亮为 0,灭为1)。

②使 SWITCH UNIT 单元中的开关 SW-B=0(打开数据输入三态门)、ALU-B=1(关闭ALU输出三态门)、LDDR1=1、LDDR2=0。

计算机组成实验——验证74LS181运算和逻辑功能

计算机组成原理实验报告实验(验证74LS181运算和逻辑功能)一、实验目的:(1)掌握算数逻辑单元的工作原理;(2)熟悉简单运算器的数据传送通路;(3)画出逻辑电路图及布出美观整齐的接线图;(4)验证4位运算功能发生器组合功能。

二、实验仪器:NI_Circuit_Design_Suite_14_0_1_Education软件。

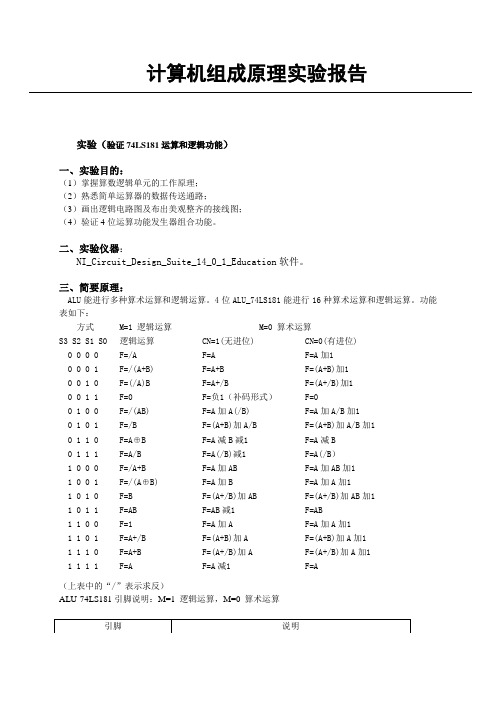

三、简要原理:ALU能进行多种算术运算和逻辑运算。

4位ALU_74LS181能进行16种算术运算和逻辑运算。

功能表如下:方式M=1 逻辑运算 M=0 算术运算S3 S2 S1 S0 逻辑运算CN=1(无进位) CN=0(有进位)0 0 0 0 F=/A F=A F=A加10 0 0 1 F=/(A+B) F=A+B F=(A+B)加10 0 1 0 F=(/A)B F=A+/B F=(A+/B)加10 0 1 1 F=0 F=负1(补码形式)F=00 1 0 0 F=/(AB) F=A加A(/B) F=A加A/B加10 1 0 1 F=/B F=(A+B)加A/B F=(A+B)加A/B加10 1 1 0 F=A⊕B F=A减B减1 F=A减B0 1 1 1 F=A/B F=A(/B)减1 F=A(/B)1 0 0 0 F=/A+B F=A加AB F=A加AB加11 0 0 1 F=/(A⊕B)F=A加B F=A加A加11 0 1 0 F=B F=(A+/B)加AB F=(A+/B)加AB加11 0 1 1 F=AB F=AB减1 F=AB1 1 0 0 F=1 F=A加A F=A加A加11 1 0 1 F=A+/B F=(A+B)加A F=(A+B)加A加11 1 1 0 F=A+B F=(A+/B)加A F=(A+/B)加A加11 1 1 1 F=A F=A减1 F=A(上表中的“/”表示求反)ALU-74LS181引脚说明:M=1 逻辑运算,M=0 算术运算四、实验数据及计量结果综上验证74LS181型4位ALU 的逻辑算术功能,列出结果如下表: S3 S2 S1 S0 数据1 数据2 算术运算(M=0)逻辑运算(M=1) Cn=1(无进位) Cn=0(有进位) 0 0 0 0 AH 5H A B 5 0 0 0 1 AH 5H F 0 0 0 0 1 0 AH 5H A B 5 0 0 1 1 AH 5H F 0 0 0 1 0 0 FH 1H D E E 0 1 0 1 FH 1H D E E 0 1 1 0 FH 1H D E E 0 1 1 1 FH 1H D E E 1 0 0 0 FHFHEFFM 状态控制M=1 逻辑运算,M=0算术运算 S3 S2 S1 S0运算选择控制 S3 S2 S1 S0决定电路执行哪一运算 A3 A2 A1 A0 运算数1,引脚3为最高位 B3 B2 B1 B0 运算数2,引脚3为最高位 Cn 最低位进位输入 Cn=0有进位;Cn=1 无进位 Cn+4本片产生的进位信号 Cn+4=0有进位;Cn+4=1无进位 F3 F2 F1 F0F3 F2 F1 F0运算结果,F3为最高位。

计算机组成原理运算器

计算机组成原理运算器算术逻辑运算器⼀、实验⽬的与要求⽬的:1.掌握算术逻辑运算器单元ALU(74LS181)的⼯作原理2.掌握简单运算器的数据传送通道3.验算由74LS181等组合逻辑电路的运算功能发⽣器运算功能4.按给定数据,完成实验指定的算术/逻辑运算要求:实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU的特性,并熟悉本实验中所⽤的模拟开关的作⽤和使⽤⽅法。

实验过程中,要认真进⾏实验操作,仔细思考实验有关的内容,把⾃⼰想得不太明⽩的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学⽬的。

实验完成后,要求每个学⽣写出实验报告。⼆、实验⽅案1.两⽚74LS181(每⽚4位)以并/串联形式构成字长为8为的运算器。2. 8为运算器的输出经过⼀个输⼊双向三态门(74LS245)与数据总线相连,运算器的两个数据输⼊端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是⽤于保存参加运算的数据和运算的结果。寄存器的输⼊端于数据总线相连。

3. 8位数据D7~D0(在“INPUT DEVICE”中)⽤来产⽣参与运算的数据,并经过⼀个输出三态门(74LS245)与数据总线相连。数据显⽰灯(BUS UNIT)已与数据总线相连,⽤来显⽰数据总线上所内容。

4. S3、S2、S1、S0是运算选择控制端,由它们决定运算器执⾏哪⼀种运算(16种算术运算或16种逻辑运算)。5. M是算术/逻辑运算选择,M=0时,执⾏算术运算,M=1时,执⾏逻辑运算。6. Cn是算术运算的进位控制端,Cn=0(低电平),表⽰有进位,运算时相当于在最低位上加进位1,Cn=1(⾼电平),表⽰⽆进位。逻辑运算与进位⽆关。

7. ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS 上。低电平有效。8. SW-B是输⼊三态门的控制端,控制“INPUT DEVICE”中的8位数据开关D7~D0数据是否送到数据总线BUS上。低电平有效。

计算机组成原理实验报告算术逻辑单元ALU实验(源代码全)

计算机组成原理实验报告算术逻辑单元ALU实验(源代码全)算术逻辑单元ALU实验⼀. 实验⽬的1、理解算术逻辑单元ALU的⼯作原理。

2、掌握算术逻辑单元ALU的设计⽅法。

3、验证32位算术逻辑单元ALU的加、减、与、移位等基本功能。

4、选定⼏组数据,完成⼏种算术/逻辑运算。

⼆. 实验设备1、 装有Xilinx Vivado的计算机⼀台。

2、LS-CPU-EXB-002教学系统实验箱⼀套。

三. 实验任务1、学习MIPS指令集,熟知指令类型,了解指令功能和编码,归纳基础的ALU运算指令。

2、归纳确定⾃⼰本次实验中准备实现的ALU运算,要求要求⾄少实现5种ALU运算,包含加减运算,其中减法在内部要转换为加法,见表1-1。

表1-1 ALU的控制信号选择端aluc ALU功能3 2 1 00 0 00 0 10 1 00 1 11 0 01 0 11 1 00 1 1 11 1 1 13、根据如图1-1所⽰的结构框图,设计实验⽅案,并⽤Verilog编写相应代码。

4、 对编写的代码进⾏仿真,得到正确的波形图。

5、将以上设计作为⼀个单独的模块,设计⼀个外围模块去调⽤该模块,如图1-2。

外围模块中需调⽤封装好的LCD触摸屏模块,显⽰ALU 的两个源操作数、操作码和运算结果,并且需要利⽤触摸功能输⼊源操作数。

操作码可以考虑⽤LCD触摸屏输⼊,也可⽤拨码开关输⼊。

6、将编写的代码进⾏综合布局布线,并下载到试验箱中的FPGA板⼦上进⾏演⽰。

四. 实验步骤这⾥给出实验代码,具体的实验步骤请看书alu.vmodule alu(a,b,aluc,r,z);input [31:0] a,b;input [3:0] aluc;output [31:0] r;output z;assign r = cal (a,b,aluc);assign z =~|r;function [31:0] cal;input [31:0] a,b;input [3:0] aluc;casex(aluc)4'b0000: cal = a + b;//加4'b0001: cal = a&b;4'b0010: cal = a^b;4'b0011: cal = b<<a[4:0];4'b0100: cal = a-b;4'b0101: cal = a|b;4'b0110: cal ={b[15:0],16'h0};4'b0111: cal = b>>a[4:0];4'b1111: cal = $signed(b)>>> a[4:0];//算术右移endcaseendfunctionendmodulealu-display.v//************************************************************************* // > ⽂件名: alu_display.v// > 描述:ALU显⽰模块,调⽤FPGA板上的IO接⼝和触摸屏// > 作者 : LOONGSON// > ⽇期 : 2016-04-14//************************************************************************* module alu_display(//时钟与复位信号input clk,input resetn,//后缀"n"代表低电平有效//拨码开关,⽤于选择输⼊数input [1:0] input_sel,//00:输⼊为控制信号(alu_control)//10:输⼊为源操作数1(alu_src1)//11:输⼊为源操作数2(alu_src2)//触摸屏相关接⼝,不需要更改output lcd_rst,output lcd_cs,output lcd_rs,output lcd_wr,output lcd_rd,inout[15:0] lcd_data_io,output lcd_bl_ctr,inout ct_int,inout ct_sda,output ct_scl,output ct_rstn);//-----{调⽤ALU模块}beginreg [3:0] alu_control;// ALU控制信号reg [31:0] alu_src1;// ALU操作数1reg [31:0] alu_src2;// ALU操作数2wire [31:0] alu_result;// ALU结果wire alu_z;alu alu_module(alu alu_module(.aluc(alu_control),.a(alu_src1 ),.b(alu_src2 ),.r(alu_result ),.z(alu_z));//-----{调⽤ALU模块}end//---------------------{调⽤触摸屏模块}begin--------------------// //-----{实例化触摸屏}begin//此⼩节不需要更改reg display_valid;reg [39:0] display_name;reg [31:0] display_value;wire [5:0] display_number;wire input_valid;wire [31:0] input_value;lcd_module lcd_module(.clk(clk ),//10Mhz.resetn(resetn ),//调⽤触摸屏的接⼝.display_valid(display_valid ),.display_name(display_name ),.display_value(display_value ),.display_number(display_number),.input_valid(input_valid ),.input_value(input_value ),//lcd触摸屏相关接⼝,不需要更改.lcd_rst(lcd_rst ),.lcd_cs(lcd_cs ),.lcd_rs(lcd_rs ),.lcd_wr(lcd_wr ),.lcd_rd(lcd_rd ),.lcd_data_io(lcd_data_io ),.lcd_bl_ctr(lcd_bl_ctr ),.ct_int(ct_int ),.ct_sda(ct_sda ),.ct_scl(ct_scl ),.ct_rstn(ct_rstn ));//-----{实例化触摸屏}end//-----{从触摸屏获取输⼊}begin//根据实际需要输⼊的数修改此⼩节,//建议对每⼀个数的输⼊,编写单独⼀个always块//当input_sel为00时,表⽰输⼊数控制信号,即alu_control always @(posedge clk)beginif(!resetn)beginalu_control <=12'd0;endelse if(input_valid && input_sel==2'b00)beginalu_control <= input_value[11:0];endend//当input_sel为10时,表⽰输⼊数为源操作数1,即alu_src1 always @(posedge clk)beginif(!resetn)if(!resetn)beginalu_src1 <=32'd0;endelse if(input_valid && input_sel==2'b10)beginalu_src1 <= input_value;endend//当input_sel为11时,表⽰输⼊数为源操作数2,即alu_src2 always @(posedge clk)beginif(!resetn)beginalu_src2 <=32'd0;endelse if(input_valid && input_sel==2'b11)beginalu_src2 <= input_value;endend//-----{从触摸屏获取输⼊}end//-----{输出到触摸屏显⽰}begin//根据需要显⽰的数修改此⼩节,//触摸屏上共有44块显⽰区域,可显⽰44组32位数据//44块显⽰区域从1开始编号,编号为1~44,always @(posedge clk)begincase(display_number)6'd1 :begindisplay_valid <=1'b1;display_name <="SRC_1";display_value <= alu_src1;end6'd2 :begindisplay_valid <=1'b1;display_name <="SRC_2";display_value <= alu_src2;end6'd3 :begindisplay_valid <=1'b1;display_name <="CONTR";display_value <={20'd0, alu_control};end6'd4 :begindisplay_valid <=1'b1;display_name <="RESUL";display_value <= alu_result;end6'd5 :begindisplay_valid <=1'b1;display_name <="ZF";display_value <= alu_z;enddefault:begindisplay_valid <=1'b0;display_name <=40'd0;display_value <=32'd0;endendcaseend//-----{输出到触摸屏显⽰}end//----------------------{调⽤触摸屏模块}end---------------------//endmodulealu_tb.v代码如下:module testbench;// Inputsreg [31:0] a;reg [31:0] b;reg [3:0] aluc;//outputwire [31:0] r;wire z;//Instantiate the Unit Under Test(UUT)alu uut(.a(a),.b(b),.r(r),.aluc(aluc),.z(z));initial begin// Initialize Inputsa=0;b=0;aluc=0;//Wait 100ns for global reset to finish#100;//Add stimulus hereendalways #10 a=$random;//$random为系统任务,产⽣⼀个随机的32位数always #10 b=$random;//#10表⽰等待10个单位时间(10ns),即每过10ns,赋值⼀个随机的32位数 always #10 aluc={$random}%2;//加了拼接符,{$random}产⽣⼀个⾮负数,除2取余得到0或1 endmodulealu.xdc⽂件如下:set_property PACKAGE_PIN AC19 [get_ports clk]set_property PACKAGE_PIN Y3 [get_ports resetn]set_property PACKAGE_PIN AC22 [get_ports input_sel[0]]set_property PACKAGE_PIN AD24 [get_ports input_sel[1]]set_property IOSTANDARD LVCMOS33 [get_ports clk]set_property IOSTANDARD LVCMOS33 [get_ports resetn]set_property IOSTANDARD LVCMOS33 [get_ports input_sel[1]]set_property IOSTANDARD LVCMOS33 [get_ports input_sel[0]]set_property PACKAGE_PIN J25 [get_ports lcd_rst]set_property PACKAGE_PIN H18 [get_ports lcd_cs]set_property PACKAGE_PIN K16 [get_ports lcd_rs]set_property PACKAGE_PIN L8 [get_ports lcd_wr]set_property PACKAGE_PIN K8 [get_ports lcd_rd]set_property PACKAGE_PIN J15 [get_ports lcd_bl_ctr]set_property PACKAGE_PIN H9 [get_ports {lcd_data_io[0]}]set_property PACKAGE_PIN K17 [get_ports {lcd_data_io[1]}]set_property PACKAGE_PIN J20 [get_ports {lcd_data_io[2]}]set_property PACKAGE_PIN M17 [get_ports {lcd_data_io[3]}]set_property PACKAGE_PIN L17 [get_ports {lcd_data_io[4]}]set_property PACKAGE_PIN L17 [get_ports {lcd_data_io[4]}]set_property PACKAGE_PIN L18 [get_ports {lcd_data_io[5]}]set_property PACKAGE_PIN L15 [get_ports {lcd_data_io[6]}]set_property PACKAGE_PIN M15 [get_ports {lcd_data_io[7]}]set_property PACKAGE_PIN M16 [get_ports {lcd_data_io[8]}]set_property PACKAGE_PIN L14 [get_ports {lcd_data_io[9]}]set_property PACKAGE_PIN M14 [get_ports {lcd_data_io[10]}]set_property PACKAGE_PIN F22 [get_ports {lcd_data_io[11]}]set_property PACKAGE_PIN G22 [get_ports {lcd_data_io[12]}]set_property PACKAGE_PIN G21 [get_ports {lcd_data_io[13]}]set_property PACKAGE_PIN H24 [get_ports {lcd_data_io[14]}]set_property PACKAGE_PIN J16 [get_ports {lcd_data_io[15]}]set_property PACKAGE_PIN L19 [get_ports ct_int]set_property PACKAGE_PIN J24 [get_ports ct_sda]set_property PACKAGE_PIN H21 [get_ports ct_scl]set_property PACKAGE_PIN G24 [get_ports ct_rstn]set_property IOSTANDARD LVCMOS33 [get_ports lcd_rst]set_property IOSTANDARD LVCMOS33 [get_ports lcd_cs]set_property IOSTANDARD LVCMOS33 [get_ports lcd_rs]set_property IOSTANDARD LVCMOS33 [get_ports lcd_wr]set_property IOSTANDARD LVCMOS33 [get_ports lcd_rd]set_property IOSTANDARD LVCMOS33 [get_ports lcd_bl_ctr]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[4]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[5]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[6]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[7]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[8]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[9]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[10]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[11]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[12]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[13]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[14]}]set_property IOSTANDARD LVCMOS33 [get_ports {lcd_data_io[15]}]set_property IOSTANDARD LVCMOS33 [get_ports ct_int]set_property IOSTANDARD LVCMOS33 [get_ports ct_sda]set_property IOSTANDARD LVCMOS33 [get_ports ct_scl]set_property IOSTANDARD LVCMOS33 [get_ports ct_rstn]拨码开关的连接,通过AC22、AD24拨码开关来控制输⼊SRC_1,SRC_2,CONTR的值五.结果记录及分析(1) 仿真波形。

计组实验报告(共10篇)

计组实验报告(共10篇)计组实验报告计算机组成原理实验报告一一、算术逻辑运算器1. 实验目的与要求:目的:①掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

②掌握简单运算器的数据传输通道。

③验算由74LS181等组合逻辑电路组成的运输功能发生器运输功能。

④能够按给定数据,完成实验指定的算术/逻辑运算。

要求:完成实验接线和所有练习题操作。

实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU 的特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

实验过程中,要认真进行实验操作,仔细思考实验有关的内容,把自己想得不太明白的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学目的。

实验完成后,要求每个学生写出实验报告。

2. 实验方案:1.两片74LS181(每片4位)以并/串联形式构成字长为8为的运算器。

2.8为运算器的输出经过一个输入双向三态门(74LS245)与数据总线相连,运算器的两个数据输入端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是用于保存参加运算的数据和运算的结果。

寄存器的输入端于数据总线相连。

3.8位数据D7~D0(在“INPUT DEVICE”中)用来产生参与运算的数据,并经过一个输出三态门(74LS245)与数据总线相连。

数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线上所内容。

4.S3、S2、S1、S0是运算选择控制端,由它们决定运算器执行哪一种运算(16种算术运算或16种逻辑运算)。

5.M是算术/逻辑运算选择,M=0时,执行算术运算,M=1时,执行逻辑运算。

6.Cn是算术运算的进位控制端,Cn=0(低电平),表示有进位,运算时相当于在最低位上加进位1,Cn=1(高电平),表示无进位。

逻辑运算与进位无关。

7.ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS上。

低电平有效。

算术逻辑运算实(仅供参考)

算术逻辑运算实(仅供参考)————————————————————————————————作者:————————————————————————————————日期:1、目的与要求1)掌握简单运算器的组成以及数据传送通路。

2)验证运算功能发生器(74LS181)的组合功能。

2、实验设备ZYE1601B计算机组成原理教学实验箱一台,排线若干。

3、实验步骤与源程序l) 按图1连接实验线路,仔细检查无误后,接通电源。

(图中DB表示数据总线,接线时应注意高低位一一对应)。

图1 算术逻辑运算实验接线图2) 用二进制数码开关向DR1和DR2寄存器置数。

具体操作步骤图示如下:检验DR1和DR2中存的数是否正确,具体操作为:关闭数据输入三态门(SW_G=1),打开ALU输出三态门(ALU_G=0)。

当设置S3、S2、S1、S0、M的状态为11111时,总线指示灯显示DR1中的数,而设置成10101时总线指示灯显示DR2中的数。

3) 验证74LS181的算术运算和逻辑运算功能(采用正逻辑)在给定DR1=C1、DR2=43的情况下,改变运算器的控制电平组合,观察运算器的输出,填入下表1中,并和理论值进行比较、验证74LS181的功能。

4、测试数据与实验结果表l运算器功能实验表DR1 DR2 S3 S2 S1 S0M=0(算术运算)M=1(逻辑运算)CN=1无进位CN=0有进位C1 43 0 0 0 0 F=11000001 F=11000010 F=00111110 C1 43 0 0 0 1 F=11000011 F=11000100 F=00111100 C1 43 0 0 1 0 F=11111101 F=11111110 F=00000010 C1 43 0 0 1 1 F=11111111 F=00000000 F=00000000 C1 43 0 1 0 0 F=01000001 F=01000010 F=10111110 C1 43 0 1 0 1 F=01000011 F=01000100 F=10111100 C1 43 0 1 1 0 F=01111101 F=01111110 F=10000010 C1 43 0 1 1 1 F=01111111 F=10000000 F=10000000 C1 43 1 0 0 0 F=00000010 F=00000011 F=01111111 C1 43 1 0 0 1 F=00000100 F=00000101 F=01111101 C1 43 1 0 1 0 F=00111110 F=00111111 F=01000011 C1 43 1 0 1 1 F=01000000 F=01000001 F=01000001 C1 43 1 1 0 0 F=10000010 F=10000011 F=11111111 C1 43 1 1 0 1 F=10000100 F=10000101 F=11111101 C1 43 1 1 1 0 F=10111110 F=10111111 F=11000011 C1 43 1 1 1 1 F=11000000 F=11000001 F=110000015、结果分析与实验体会1、比较理论值和实际测量值发现74181ALU有两种工作方式,对正逻辑操作来说,算术运算称正逻辑操作,对于负逻辑操作数来说,正好相反。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验报告 、实验名称 运算器实验—算术逻辑运算实验

、实验目的 1、了解运算器的组成原理。 2、掌握运算器的工作原理。 3、掌握简单运算器的数据传送通路。 4、验证运算功能发生器( 74LS181)的组合功能

三、实验设备 TDN-CM++ 计算机组成原理教学实验系统一套,导线若干 四、实验原理

实验中所用的运算器数据通路如图 1-1 所示。其中两片 74LSl81以串行方式 构成 8 位字长的 ALU, ALU 的输出经过一个三态门 (74LS245)和数据总线相连。 三态门由 ALU-R 控制,控制运算器运算的结果能否送往总线,低电平有效。 为实现双操作数的运算, ALU 的两个数据输入端分别由二个锁存器 DR1、 DR2 (由 74LS273实现)锁存数据。要将数据总线上的数据锁存到 DRl、DR2 中,锁 存器的控制端 LDDR1 和 DDR2必须为高电平,同时由 T4 脉冲到来。 数据开关“( INPUT DEVICE")用来给出参与运算的数据, 经过三态(74LS245) 后送入数据总线,三态门由 SW—B控制,低电平有效。数据显示灯 “( BUS UNIT") 已和数据总线相连,用来显示数据总线上的内容。 图中已将用户需要连接的控制信号用圆圈标明 (其他实验相同,不再说明 ), 其中除 T4 为脉冲信号外,其它均为电平信号。由于实验电路中的时序信号均已 连至“W/R UNIT ”的相应时序信号引出端, 因此,在进行实验时, 只需将“W /R UNIT"的 T4接至“ STATE UNIT ”的微动开关 KK2 的输入端,按动微动开 关,即可获得实验所需的单脉冲。 ALU 运算所需的电平控制信号 S3、S2、S1、S0 、Cn、M、LDDRl、LDDR2 、 ALU-B 、SW-B均由“ SWITCH UNIT ”中的二进制数据开关来模拟,其中 Cn、ALU —B、SW 一 B 为低电平有效 LDDR1 、LDDR2 为高电平有效。 对单总线数据通路,需要分时共享总线,每一时刻只能由一组数据送往总线。 五、实验内容 1.输入数据通过三态门 74LS245 后送往数据总线,在数据显示灯和数码显 示管 LED 上显示。 2.向 DRl(或 DR2)中置数,经 ALU 直传后,经过三态 245 送入数据总线, 在数据显示灯和数码显示管 LED 上显示 3.将输入 DRl 和 DR2 中的两个数进行算术逻辑运算,验证 AlU 的功能, 结果在数据显示灯和数码显示管 LED 上显示。

六、实验步骤 1、输入数据通过三态门 74LS245 后经过数据总线在数据显示灯和数码显示 管 LED 上直接显示

(1)按下图连接实验线路,仔细查线无误后,接通电源。 (2)用二进制数码开关输入数据 65H,观察总线数据显示灯和 LED 灯的变 化。设置:○1 SW-B=1;○2 从输入开关输入: 01100101;○3 打开三态门 SW-

B=0; ○4 数据在数码管上显示: LED-B=0 ,发 W/R 脉冲。 (3)观察实验结果。

2. 向 DRl(或 DR2)中置数,经ALU 直传后,经过三态 245送入数据总线, 在 数据显示灯和数码显示管 LED 上显示。 (1)重新连接电路,仔细检查无误之后,接通电源。 2)向DR1和DR2寄存器中置入数据 65H和 A7H。流程为: ○1 使 SWITCH UNIT 单元中的开关 SW-B=1; ○2 从输入开关输入: 01100101(数据显示:灯亮为 0,灯不亮为 1。下同); ○3 使开关 SW-B=0; ○4 设置 LDDR1=1 、LDDR2=0

○5 将数据打入 DR1[按 KK2 发 F4 脉冲],将总线上得数据在数码管上显示: LED-B=0 。 2)、用输入开关向寄存器 DR2 置数 .。 ○1 使 SWITCH UNIT 单元中的开关 SW-B=1; ○2 从输入开关输入: 10100111; ○3 使开关 SW-B=0; ○4 设置 LDDR1=0 、LDDR2=1 。 ○5 将数据打入 DR2[按 KK2 发 F4 脉冲],将总线上得数据在数码管上显示: LED-B=0 。 (3)、检验输入 DR1 和 DR2 寄存器中的数据是否正确。

1、关闭三态SW-B=1,关闭暂存器的输入: LDDR1=0 、 LDDR2=0 。 2、打开 ALU 输出三态门: ALU-B=0 ,设置运算器直传形式 S3S2S1S0M为 11111。 3、将总线上的数据在数码管上显示: LED-B=0 ,发 W/R 脉冲。 4、观察结果(即 DR1 中的数据)。

数据开关 寄存器 DR1 打开 数据开关

(01100101) (01100101) 三态门 (10100111)

1)、用

输

打开 寄存器 DR2

三态门 (10100111)

入开关向寄存器 DR1 置数 5、再次关闭三态门: SW-B=1。打开 ALU 输出三态门: ALU-B=0 。 6、设置运算器直传形式 S3S2S1S0M为 10101。 7、将总线上的数据在数码管上显示: LED-B=0 ,发 W/R 脉冲。 8、观察结果(即 DR2 中的数据)。

3、将输入 DR1 和 DR2 中的两个数进行算术逻辑运算,验证 ALU 的功能, 结果在数据显示灯和数码显示管 LED 上显示。

(1)、保持中数据不变,若不知道中是否有数据,可按实验步骤 2 中得( 3)去 检查。 (2)通过“ SWITCH UNIT ”改变开关 S3,S2,S1,S0,Cn,M 的值,可将两 数进行不同的运算。例如:设置 S3S2S1S0CnM=10010,运算器进行加法运算, 设置 S3S2S1S0CnM=01100,运算器进行减法运算。 最后根据运算结果填写下表: DR1 DR2 S3 S2 S1

S0

M=0( 算术运算 )

M=1 (逻辑运 算) Cn=1 无进位 Cn=0 有进

位

65 A7 0 0 0 0 F=(6 5) F=( 6 6 ) F=(9 A ) 65 A7 0 0 0 1 F=(E 7) F=( E8 ) F=( 1 8 ) 65 A7 0 0 1 0 F=(7 D) F=( 7 E ) F=( 82 ) 0 0 1 1 F=( ) F=( ) F=( )

0 1 0 0 F=( ) F=( ) F=( )

0 1 0 1 F=( ) F=( ) F=( )

01 1 0 F=( ) F=( ) F=( )

0 1 1 1 F=( ) F=( ) F=( )

1 0 0 0 F=( ) F=( ) F=( )

1 0 0 1 F=( ) F=( ) F=( )

1 0 1 0 F=( ) F=( ) F=( )

1 0 1 1 F=( ) F=( ) F=( )

1 1 0 0 F=( ) F=( ) F=( )

1 1 0 1 F=( ) F=( ) F=( )

1 1 1 0 F=( ) F=( ) F=( )

1 1 1 1 F=( ) F=( ) F=( )

七、实验结果 1、在实验步骤 1 第( 3)步观察到的结果是亮、暗、暗、亮、亮、暗、亮、暗, 即运算器最后存储的数据是 01100101,即 LED 显示为 65; 2、在实验步骤 2 第( 3)步观察到的结果是亮、暗、暗、亮、亮、暗、亮、暗, 即运算器最后存储的数据是 01100101,即 LED 显示为 65; 3、在实验步骤 2 第( 3)步观察到的结果是暗、亮、暗、亮、亮、暗、暗、暗, 即运算器最后存储的数据是 10100111,即 LED 显示为 A7; 4、步骤 3 中的运算结果如下:

DR1 DR2 S3 S2 S1

S0

M=0( 算术运算 )

M=1 (逻辑运 算) Cn=1 Cn=0 无进位 有进位

65 A7 0 0 0 0 F=(65) F=( 66 ) F=(9A ) 65 A7 0 0 0 1 F=(E7) F=( E8 ) F=( 18 ) 65 A7 0 0 1 0 F=(7D) F=( 7E ) F=( 82 ) 0 0 1 1 F=(FF) F=(00) F=(00 ) 0 1 0 0 F=(A5) F=(A6) F=(dA) 0 1 0 1 F=(27) F=(28) F=(58) 01 1 0 F=(BD) F=(BE) F=(C2) 0 1 1 1 F=(3F) F=(40) F=(4D) 1 0 0 0 F=(8A) F=(8B) F=(BF) 1 0 0 1 F=(0C) F=(0D) F=(3D) 1 0 1 0 F=( 4C) F=(AD) F=(7D) 1 0 1 1 F=( 24) F=(25) F=(25) 1 1 0 0 F=(CA) F=( CB) F=(FF) 1 1 0 1 F=(4C) F=(4D) F=(7D) 1 1 1 0 F=(E2) F=(E3) F=( E7) 1 1 1 1 F=( 64) F=(65) F=(65)

八、小结 通过这次实验, 我明白了要很好的完成实验首先一定要注意线路的连接, 需 要对应的要一一对应。 我掌握了算术逻辑运算器单元 ALU(74LS181)的工作原 理,并熟悉了怎样输入输出数据和验算由 74LS181 等组合逻辑思电路的运算功 能发生器运算功能等实验步骤和要求。