16位算数逻辑运算实验

基本算数运算(DSP实验报告)

基本算数运算一、实验目的和要求加、减、乘、除是数字信号处理中最基本的算术运算。

DSP 中提供了大量的指令来实现这些功能。

本实验学习使用定点DSP 实现16 位定点加、减、乘、除运算的基本方法和编程技巧。

本实验的演示文件为exer1.out。

二、实验原理1) 定点DSP 中的数据表示方法2) 实现16 位定点加法ld temp1,a ;将变量temp1 装入寄存器Aadd temp2,a ;将变量temp2 与寄存器A相加,结果放入A中stl a,add_result ;将结果(低16 位)存入变量add_result 中3)实现16 位定点减法stm #temp1,ar3 ;将变量temp1 的地址装入ar3 寄存器stm #temp3,ar2 ;将变量temp3 的地址装入ar2 寄存器sub *ar2+, *ar3,b ;将变量temp3 左移16 位同时变量temp1 也左移16 位,然后相减,结果放入寄存器B(高16位)中,同时ar2 加1。

sth b,sub_result ;将相减的结果(高16位)存入变量sub_result 4)实现16 位定点整数乘法rsbx FRCT ;清FRCT标志,准备整数乘ld temp1,T ;将变量temp1 装入T 寄存器mpy temp2,a ;完成temp2*temp1,结果放入A寄存器(32 位)5)实现16 位定点小数乘法我们使用下列ssbx FRCT ;FRCT=1,准备小数乘法ld temp1,16,a ;将变量temp1 装入寄存器A的高16位mpya temp2 ;完成temp2 乘寄存器A的高16 位,结果在B中,同时将temp2 装入T 寄存器sth b,mpy_f ;将乘积结果的高16 位存入变量mpy_f6)实现16 位定点整数除法代码如下:ld temp1,T ;将被除数装入T 寄存器mpy temp2,A ;除数与被除数相乘,结果放入A寄存器ld temp2,B ;将除数temp2 装入B 寄存器的低16位abs B ;求绝对值stl B,temp2 ;将B 寄存器的低16 位存回temp2ld temp1,B ;将被除数temp1 装入B寄存器的低16 位abs B ;求绝对值rpt #15 ;重复SUBC 指令16 次subc temp2,b ;使用SUBC 指令完成除法运算bcd div_end,agt ;延时跳转,先执行下面两条指令,然后判断A,若A>0,则跳转到标号div_end,结束除法运算stl B,quot_i ;将商(B寄存器的低16 位)存入变量quot_i sth B,remain_i ;将余数(B 寄存器的高16 位)存入变量remain_ixor B ;若两数相乘的结果为负,则商也应为负。

《计算机组成原理》学生实验报告

《计算机组成原理》学生实验报告(2011~2012学年第二学期)专业:信息管理与信息系统班级: A0922学号:10914030230姓名:李斌目录实验准备------------------------------------------------------------------------3 实验一运算器实验-----------------------------------------------------------7 实验二数据通路实验-------------------------------------------------------13 实验三微控制器实验--------------------------------------------------------18 实验四基本模型机的设计与实现------------------------------------------22实验准备一、DVCC实验机系统硬件设备1、运算器模块运算器由两片74LS181构成8位字长的ALU。

它是运算器的核心。

可以实现两个8位的二进制数进行多种算术或逻辑运算,具体由74181的功能控制条件M、CN、S3、S2、S1、S0来决定,见下表。

两个参与运算的数分别来自于暂存器U29和U30(采用8位锁存器),运算结果直接输出到输出缓冲器U33(采用74LS245,由ALUB信号控制,ALUB=0,表示U33开通,ALUB=1,表示U33不通,其输出呈高阻),由输出缓冲器发送到系统的数据总线上,以便进行移位操作或参加下一次运算。

进位输入信号来自于两个方面:其一对运算器74LS181的进位输出/CN+4进位倒相所得CN4;其二由移位寄存器74LS299的选择参数S0、S1、AQ0、AQ7决定所得。

触发器的输出QCY就是ALU结果的进位标志位。

QCY为“0”,表示ALU结果没有进位,相应的指示灯CY灭;QCY为“1”,表示ALU结果有进位,相应的指示灯CY点亮。

用单片机语言设计16位加法计算器实验报告

湖北第二师范学院计算机学院09计应单片机课程设计实验报告课程设计名称:电子计算器课程设计单位:10计应(1)班课设小组成员:徐凡(1060310039)凡平(1060310058)彭浩(1060310045)桂银(1060310010)潘光卉(1060300033)完成时间:2012年04月02日至2012年04月 24 日单片机课程设计实验报告课程设计题目:简易计算器作品功能描述:当通过输入键盘数字时,能够在显示器上显示输出的数值,并且通过想实现的简单运算功能,实现计算器的加、减、乘、除和清零,并将结果显示出来。

小组成员工作分工:徐凡:程序主框架的构造和主要功能函数的设计。

凡平:原理图的设计和硬件的焊接。

彭浩:基本功能函数的设计(“+,-,*,/”)。

桂银:程序流程图的设计和键盘扫描程序的实现。

潘光卉:编写文档和功能测试。

硬件电路设计:本设计中我们用的是AT89C52芯片,LCD1602 (PROTEUS中为LM016L)就是那个液晶屏,因为可以显示2行16个字符,故叫做LCD1602.11.0592M或12M晶振(CRYSTAL),两者均可,但要涉及到串口需选用12MKEYPAD-SMALLCALC就是那个4X4键盘电容20~30PF(CAP),接最小电路电容10PF主要接复位电路RESPACK-8排阻,为20K的,一个引脚接正极,另8个引脚接I/O口接RES电阻10K,接复位电路实物照片:硬件原理图原理说明:1,上电后,屏幕初始化;2,计算。

按下数字键,屏幕显示要运行的第一个数字,再按下符号键,然后再按下数字键,屏幕显示要运算的第二个数字,最后按下“=”号键,屏幕上显示出计算结果。

3,如果要再次计算,可以按下“ON/C”键清零,或者继续按下数字键,即可重新计算。

键盘使用说明如下:按键功能说明:Array“+”实现两个数的相加“-”实现两个数的相减“×”实现两个数的乘积“÷”实现两个数商的运算“ON/C”计算器显示的清零和接通电源程序控制流程图:软件设计:在程序设计方法上,模块化程序设计是单片机应用中最常用的程序设计方法。

16位超前进位加法器实验报告

实验名称:十六位超前进位加法器一、实验目的设计、验证并优化16位超前进位加法器的逻辑功能。

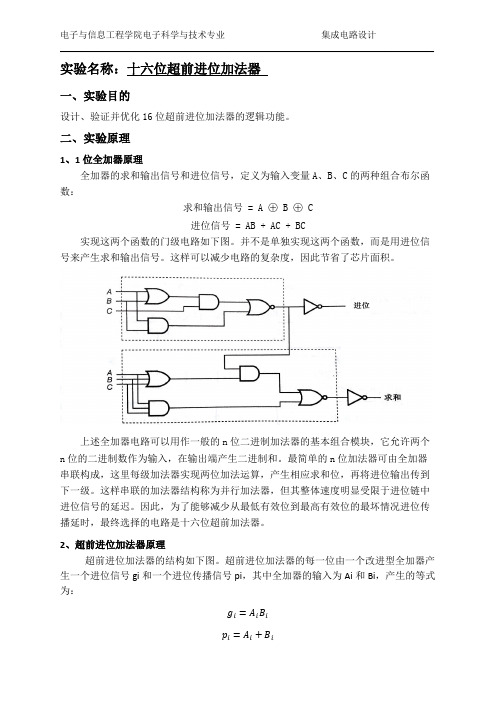

二、实验原理1、1位全加器原理全加器的求和输出信号和进位信号,定义为输入变量A、B、C的两种组合布尔函数:求和输出信号 = A ⊕ B ⊕ C进位信号 = AB + AC + BC实现这两个函数的门级电路如下图。

并不是单独实现这两个函数,而是用进位信号来产生求和输出信号。

这样可以减少电路的复杂度,因此节省了芯片面积。

上述全加器电路可以用作一般的n位二进制加法器的基本组合模块,它允许两个n 位的二进制数作为输入,在输出端产生二进制和。

最简单的n位加法器可由全加器串联构成,这里每级加法器实现两位加法运算,产生相应求和位,再将进位输出传到下一级。

这样串联的加法器结构称为并行加法器,但其整体速度明显受限于进位链中进位信号的延迟。

因此,为了能够减少从最低有效位到最高有效位的最坏情况进位传播延时,最终选择的电路是十六位超前加法器。

2、超前进位加法器原理超前进位加法器的结构如下图。

超前进位加法器的每一位由一个改进型全加器产生一个进位信号gi和一个进位传播信号pi,其中全加器的输入为Ai和Bi,产生的等式为:改进的全加器的进位输出可由一个进位信号和一个进位传输信号计算得出,因此进位信号可改写为:式中可以看出,当gi = 1(Ai = Bi = 1)时,产生进位;当pi = 1(Ai =1或Bi = 1)时,传输进位输入,这两种情况都使得进位输出是1。

近似可以得到i+2和i+3级的进位输出如下:下图为一个四位超前进位加法器的结构图。

信号经过pi和gi产生一级时延,经过计算C产生一级时延,则A,B输入一旦产生,首先经过两级时延算出第1轮进位值C’不过这个值是不正确的。

C’再次送入加法器,进行第2轮2级时延的计算,算出第2轮进位值C,这一次是正确的进位值。

这里的4个4位超前进位加法器仍是串行的,所以一次计算经过4级加法器,一级加法器有2级时延,因此1次计算一共经过8级时延,相比串行加法器里的16级时延,速度提高很多。

(完整word版)16位算术逻辑运算实验_共5页

16 位算术逻辑运算实验一、实验内容1、实验原理实验中所用16位运算器数据通路如图3-3所示。

其中运算器由四片74LS181以并/串形成16位字长的ALU构成。

低8位运算器的输出经过一个三态门74LS245(U33)到ALUO1插座,实验时用8芯排线和内部数据总线BUSD0~D7插座BUS1~6中的任一个相连,低8位数据总线通过LZD0~LZD7显示灯显示;高8位运算器的输出经过一个三态门74LS245(U33`)到ALUO1`插座,实验时用8芯排线和高8位数据总线BUSD8~D15插座KBUS1或KBUS2相连,高8位数据总线通过LZD8~LZD15显示灯显示;参与运算的四个数据输入端分别由四个锁存器74LS273(U29、U30、U29`、U30、)锁存,实验时四个锁存器的输入并联后用8芯排线连至外部数据总线EXD0~D7插座EXJ1~EXJ3中的任一个;参与运算的数据源来自于8位数据开并KD0~KD7,并经过一三态门74LS245(U51)直接连至外部数据总线EXD0~EXD7,输入的数据通过LD0~LD7显示。

2、实验接线本实验用到6个主要模块:⑴低8位运算器模块,⑵数据输入并显示模块,⑶数据总线显示模块,⑷功能开关模块(借用微地址输入模块),⑸高8位运算器模块,⑹高8位(扩展)数据总线显示模块。

根据实验原理详细接线如下(接线⑴~⑸同实验一):⑴ALUBUS连EXJ3;⑵ALUO1连BUS1;⑶SJ2连UJ2;⑷跳线器J23上T4连SD;⑸LDDR1、LDDR2、ALUB、SWB四个跳线器拨在左边(手动方式);⑹AR跳线器拨在左边,同时开关AR拨在"1"电平;⑺ALUBUS`连EXJ2;⑻ALUO1`连KBUS1;⑼跳线器J19、J25拨左边(16位ALU状态);⑽高8位运算器区跳线器ZI2、CN0、CN4连上短路套;二、实验目的1、掌握16位算术逻辑运算数据传送通路组成原理2、进一步验证算术逻辑运算能力发生器74LS181的组合功能三、实验步骤⑴连接线路,仔细查线无误后,接通电源。

算术逻辑运算实验报告

数学学院实验报告课程名称:计算机组成原理实验项目名称:算术逻辑运算实验一、实验目的1.了解运算器的组成结构。

2.掌握运算器的工作原理。

二、实验设备与器件PC机一台,TD-CMA实验系统一套。

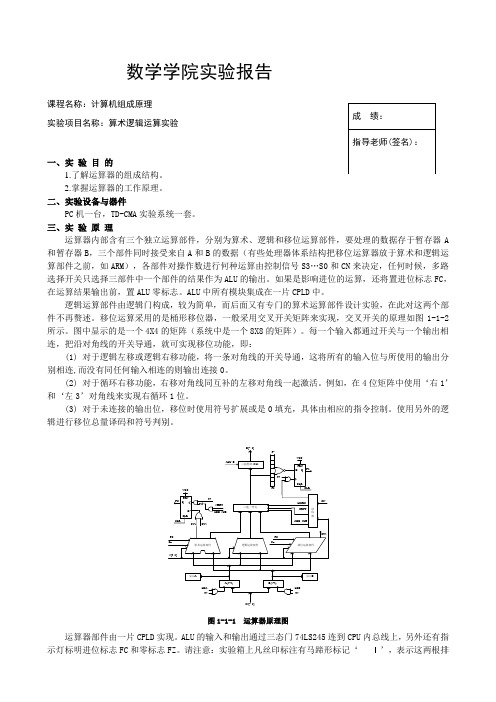

三、实验原理运算器内部含有三个独立运算部件,分别为算术、逻辑和移位运算部件,要处理的数据存于暂存器A 和暂存器B,三个部件同时接受来自A和B的数据(有些处理器体系结构把移位运算器放于算术和逻辑运算部件之前,如ARM),各部件对操作数进行何种运算由控制信号S3…S0和CN来决定,任何时候,多路选择开关只选择三部件中一个部件的结果作为ALU的输出。

如果是影响进位的运算,还将置进位标志FC,在运算结果输出前,置ALU零标志。

ALU中所有模块集成在一片CPLD中。

逻辑运算部件由逻辑门构成,较为简单,而后面又有专门的算术运算部件设计实验,在此对这两个部件不再赘述。

移位运算采用的是桶形移位器,一般采用交叉开关矩阵来实现,交叉开关的原理如图1-1-2所示。

图中显示的是一个4X4的矩阵(系统中是一个8X8的矩阵)。

每一个输入都通过开关与一个输出相连,把沿对角线的开关导通,就可实现移位功能,即:(1) 对于逻辑左移或逻辑右移功能,将一条对角线的开关导通,这将所有的输入位与所使用的输出分别相连,而没有同任何输入相连的则输出连接0。

(2) 对于循环右移功能,右移对角线同互补的左移对角线一起激活。

例如,在4位矩阵中使用‘右1’和‘左3’对角线来实现右循环1位。

(3) 对于未连接的输出位,移位时使用符号扩展或是0填充,具体由相应的指令控制。

使用另外的逻辑进行移位总量译码和符号判别。

图1-1-1 运算器原理图运算器部件由一片CPLD实现。

ALU的输入和输出通过三态门74LS245连到CPU内总线上,另外还有指示灯标明进位标志FC和零标志FZ。

请注意:实验箱上凡丝印标注有马蹄形标记‘’,表示这两根排针之间是连通的。

图中除T4和CLR ,其余信号均来自于ALU 单元的排线座,实验箱中所有单元的T1、T2、T3、T4都连接至控制总线单元的T1、T2、T3、T4,CLR 都连接至CON 单元的CLR 按钮。

16位乘法器

乘法器是众多数字系统中的基本模块。

从原理上说它属于组合逻辑范畴;但从工程实际设计上来说,它往往会利用时序逻辑设计的方法来实现,属于时序逻辑范畴。

通过这个实验使大家能够掌握利用FPGA/CPLD设计乘法器的思想,并且能够将我们设计的乘法器应用到实际工程中。

下面我们分别列举了十进制乘法运算和二进制乘法运算的例子。

下面这种计算乘法的方式是大家非常熟悉的:乘积项与乘数相应位对齐(即将乘积项左移),加法运算的数据宽度与被乘数的数据位宽相同。

下面例子中的被乘数和乘数都是无符号的整数,对于有符号数的乘法,可以将符号与数据绝对值分开处理,即绝对值相乘,符号异或。

乘法器的设计方法有两种:组合逻辑设计方法和时序逻辑设计方法。

采用组合逻辑设计方法,电路事先将所有的乘积项全部计算出来,最后加法运算。

采用时序逻辑设计方法,电路将部分已经得到的乘积结果右移,然后与乘积项相加并保存和值,反复迭代上述步骤直到计算出最终乘积。

在本次实验中我们就利用时序逻辑设计方法来设计一个16位乘法器,既然是利用时序逻辑设计方法那么我们就得利用时钟信号控制乘法器运算,那么这样用时序逻辑设计方法与用组合逻辑设计方法比较,它有什么好处呢?利用时序逻辑设计方法可以使整体设计具备流水线结构的特征,能适用在实际工程设计中。

IO口定义:clk:芯片的时钟信号。

rst_n:低电平复位、清零信号。

定义为0表示芯片复位;定义为1表示复位信号无效。

start: 芯片使能信号。

定义为0表示信号无效;定义为1表示芯片读入输入管脚得乘数和被乘数,并将乘积复位清零。

ain:输入a(被乘数),其数据位宽为16bit.bin:输入b(乘数),其数据位宽为16bit.yout:乘积输出,其数据位宽为32bit.done:芯片输出标志信号。

定义为1表示乘法运算完成,yout端口的数据稳定,得到最终的乘积;定义为0表示乘法运算未完成,yout端口的数据不稳定。

数据吞吐量的计算:数据吞吐量使指芯片在一定时钟频率条件下所能处理的有效数据量。

16位超前进位加法器实验报告

实验名称:十六位超前进位加法器一、实验目的设计、验证并优化16位超前进位加法器的逻辑功能。

二、实验原理1、1位全加器原理全加器的求和输出信号和进位信号,定义为输入变量A、B、C的两种组合布尔函数:求和输出信号= A ⊕B ⊕C进位信号= AB + AC + BC实现这两个函数的门级电路如下图。

并不是单独实现这两个函数,而是用进位信号来产生求和输出信号。

这样可以减少电路的复杂度,因此节省了芯片面积。

上述全加器电路可以用作一般的n位二进制加法器的基本组合模块,它允许两个n 位的二进制数作为输入,在输出端产生二进制和。

最简单的n位加法器可由全加器串联构成,这里每级加法器实现两位加法运算,产生相应求和位,再将进位输出传到下一级。

这样串联的加法器结构称为并行加法器,但其整体速度明显受限于进位链中进位信号的延迟。

因此,为了能够减少从最低有效位到最高有效位的最坏情况进位传播延时,最终选择的电路是十六位超前加法器。

2、超前进位加法器原理超前进位加法器的结构如下图。

超前进位加法器的每一位由一个改进型全加器产生一个进位信号gi和一个进位传播信号pi,其中全加器的输入为Ai和Bi,产生的等式为:改进的全加器的进位输出可由一个进位信号和一个进位传输信号计算得出,因此进位信号可改写为:式中可以看出,当gi = 1(Ai = Bi = 1)时,产生进位;当pi = 1(Ai =1或Bi = 1)时,传输进位输入,这两种情况都使得进位输出是1。

近似可以得到i+2和i+3级的进位输出如下:下图为一个四位超前进位加法器的结构图。

信号经过pi和gi产生一级时延,经过计算C产生一级时延,则A,B输入一旦产生,首先经过两级时延算出第1轮进位值C’不过这个值是不正确的。

C’再次送入加法器,进行第2轮2级时延的计算,算出第2轮进位值C,这一次是正确的进位值。

这里的4个4位超前进位加法器仍是串行的,所以一次计算经过4级加法器,一级加法器有2级时延,因此1次计算一共经过8级时延,相比串行加法器里的16级时延,速度提高很多。

实验一运算器部件实验1

实验一运算器部件实验一.实验类型设计型实验二.实验目的1.掌握4 位算术逻辑单元74181,先行进位发生器74182的工作原理和使用方法。

2.掌握16 位串/并运算器的工作原理及设计方法。

三、实验要求1.用四片4 位并行算术逻辑运算单元74181、一片先行进位发生电路74182,组装一个组间进位并行/串行可变的16 位运算器(每组四位)。

2.验证集成电路74181、74182 的功能。

3.分别测试16 位运算器组间串行进位和并行进位情况下的最大进位延迟时间。

四、实验芯片介绍1.74181芯片2.74182芯片四、实验原理1.实现CLA电路的芯片设计CLA电路的主要功能是接收BCLA加法器的Gi和Pi以及初始进位信号Cin,从而同时产生各BCLA加法器的低位进位信号(C4、C8、C12)。

假设4片BCLA加法器的先行进为输出依次是P1G1、P2G2、P3G3、P4G4,那么:Cn+x=G1+P1Cin,Cn+y=G2+P2Cn+x=G2+G1P2+P1P2Cin,Cn+z=G3+P3Cn+y=G3+G2P3+G1P2P3+P1P2P3Cin,Cn+4=G4+P4Cn+z=G4+G3P4+G2P3P4+G1P2P3P4+P1P2P3P4Cin.现令P*=P1P2P3P4,G*=G4+G3P4+G2P3P4+G1P2P3P4,则Cn+4=G*+P*Cin.根据上述一系列进位产生公式,可以在Multisim 2001利用TTL工具箱中74系列提供的工具创建CLA电路,实现图如图2所示。

图2 先行进位逻辑电路仿真图其中,具有两个输入端的与门、或非门都是TTL工具箱中74系列提供的工具, 而具有3个输入端和4个输入端的与门、或非门的实现方法有多种,可由学生发挥自身创造力,自己提出解决方案。

此处是使用Multisim 2001中对已有元器件的编辑功能实现的,从双输入的与门和或非门编辑改造而来。

要对上述CLA电路进行封装,以便其可以作为一个芯片模块使用。

实验三16位算术逻辑运算实验

实验三16位算术逻辑运算实验实验三16位算术逻辑运算实验⼀、实验⽬的1、掌握16位算术逻辑运算数据传送通路组成原理。

2、进⼀步验证算术逻辑运算功能发⽣器74L S181的组合功能。

⼆、实验内容1、实验原理实验中所⽤16位运算器数据通路如图3-3所⽰。

其中运算器由四⽚74L S181以并/串形成16位字长的A L U构成。

低8位运算器的输出经过⼀个三态门74L S245(U33)到内部总线,低8位数据总线通过L Z D0~L Z D7显⽰灯显⽰;⾼8位运算器的输出经过⼀个三态门74L S245(U33`)到A L U O1`插座,实验时⽤8芯排线和⾼8位数据总线B U S D8~D15插座K B U S1或K B U S2相连,⾼8位数据总线通过L Z D8~L Z D15显⽰灯显⽰;参与运算的四个数据输⼊端分别由四个锁存器74L S273(U29、U30、U29`、U30、)锁存,实验时四个锁存器的输⼊并联连⾄内部数据总线再⽤8芯线连接到外部数据总线E X D0~D7插座E X J1~E X J3中的任⼀个;参与运算的数据源来⾃于8位数据开并K D0~K D7,并经过⼀三态门74L S245(U51)直接连⾄外部数据总线E X D0~E X D7,输⼊的数据通过L D0~L D7显⽰。

2、实验接线本实验⽤到6个主要模块:⑴低8位运算器模块,⑵数据输⼊并显⽰模块,⑶数据总线显⽰模块,⑷功能开关模块(借⽤微地址输⼊模块),⑸⾼8位运算器模块,⑹⾼8位(扩展)数据总线显⽰模块。

根据实验原理详细接线如下:1、J20,J21,J22,接上短路⽚,图3-1.J20,J21,J22接上短路⽚2、J24,J25,J26接左边;图3-2.J24,J25,J26接左边3、J27,J28 左边图3-3.J27,J28接左边4、J23 置右边T4选“SD”图3-4.J23接右边5、JA5 置“接通”;图3-5.JA5置上⽅“接通”6、JA6 置“⼿动”;图3-6.JA6置下边“⼿动”7、JA3 置“接通”;图3-7.JA3置右边“接通”8、JA1,JA2,JA4置“⾼阻”;图3-8.JA1、JA2接下边“⾼阻”图3-9.JA4置左边“⾼阻”9、JA8 置上⾯“微地址”图3-10.JA8置上⾯“微地址”10、EXJ1接BUS3图3-11.EXJ1接BUS3 11、ALO1'接KBUS1图3-12.ALO1接KBUS1 12、开关CE 、AR 置1图3-13.CE与AR各⾃置113、ZI2,CN4,CN0接上短路⽚图3-14.Z12,CN4和CN0都接上短路⽚3、实验步骤⑴连接线路,仔细查线⽆误后,接通电源。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

五.实验总结

六、教师提问及回答

四、实验步骤

⑴连接线路,仔细查线无误后,接通电源。

⑵用二进制数码开关KD0~KD7向DR1、DR2、DR3、DR4寄存器置数。方法:关闭ALU输出三态门应使ALUB`=1(即开关ALUB=1),开启输入三态门应使SWB`=0(即开关SWB=0),选通哪一个寄存器用对应开关LDDR1~LDDR4(高电平有效),其中LDDR3、LDDR4开关在高8位运算器上部,输入脉冲T4按手动脉冲发生按钮。设置数据开关具体操作步骤图示如下:

·开关ALUB=0,关闭输入三态门;

·开关SWB=1,打开输出三态门;

·LDDR1~LDDR4四个开关全拨在"0"电平。

·根据下表3-2,置功能开关S3、S2、S1、S0、M、CN,以验证74LS181的算术运算和逻辑运算功能。

说明:如果要实现16位带进位控制算术逻辑运算,只需在实验三的基础上将开关AR=1变成AR=0即可。

说明:LDDR1、LDDR2、ALUB`、SWB`、LDDR3、LDDR4六个信号电平由对应的开关LDDR1、LDDR2、ALUB、SWB、LDDR3、LDDR4给出,拨在上面为"1",拨在下面为"0",电平值由对应显示灯显示;T4由手动脉冲开关给出。

⑶进一步验证74LS181的算术运算和逻辑运算功能(采用正逻辑)。

三.实验连线

本实验用到6个主要模块:⑴低8位运算器模块,⑵数据输入并显示模块,⑶数据总线显示模块,⑷功能开关模块(借用微地址输入模块),⑸高8位运算器模块,⑹高8位(扩展)数据总线显示模块。根据实验原理详细接线如下(接线⑴~⑸同实验一):

⑴ALUBUS连EXJ3;

⑵ALUO1连BUS1;

⑶SJ2连UJ2;

计算机组成原理实验报告

系别

班级

学号

姓名

地点

计算机科学系

计算机组成原理实验室

课程名称

计算机组成原理

实验名称

16位算数逻辑运算实验

实验过程

一.实验目的

1、掌握16位算术逻辑运算数据传通路组成原理

2、进一步验证算术逻辑运算能力发生器74LS181的组合功能

二.实验原理

实验中所用16位运算器数据通路如图3-3所示。其中运算器由四片74LS181以并/串形成16位字长的ALU构成。低8位运算器的输出经过一个三态门74LS245(U33)到ALUO1插座,实验时用8芯排线和内部数据总线BUSD0~D7插座BUS1~6中的任一个相连,低8位数据总线通过LZD0~LZD7显示灯显示;高8位运算器的输出经过一个三态门74LS245(U33`)到ALUO1`插座,实验时用8芯排线和高8位数据总线BUSD8~D15插座KBUS1或KBUS2相连,高8位数据总线通过LZD8~LZD15显示灯显示;参与运算的四个数据输入端分别由四个锁存器74LS273(U29、U30、U29`、U30、)锁存,实验时四个锁存器的输入并联后用8芯排线连至外部数据总线EXD0~D7插座EXJ1~EXJ3中的任一个;参与运算的数据源来自于8位数据开并KD0~KD7,并经过一三态门74LS245(U51)直接连至外部数据总线EXD0~EXD7,输入的数据通过LD0~LD7显示。

⑷跳线器J23上T4连SD;

⑸LDDR1、LDDR2、ALUB、SWB四个跳线器拨在左边(手动方式);

⑹AR跳线器拨在左边,同时开关AR拨在"1"电平;

⑺ALUBUS`连EXJ2;

⑻ALUO1`连KBUS1;

⑼跳线器J19、J25拨左边(16位ALU状态);

⑽高8位运算器区跳线器ZI2、CN0、CN4连上短路套;