计算机组成原理实验报告 算术逻辑运算单元实验

计算机组成原理实验报告

3)在增大合法码的码距时,所有码的码距应尽量均匀增大,以保证对所有码的检错能力平衡提高。

下面具体看一下对一个字节进行海明编码的实现过程。

只实现一位纠错两位检错,由前面的表可以看出,8位数据位需要5位校验位,可表示为H13H12…H2H1。

0

0

1

1

0

0

1

1

0

S1

0

0

1

0

1

0

1

0

1

0

1

0

1

由此可得校验后的数据位表达式为:

D1=D1 (S1•S2• • •S5)

D2=D2 (S1• •S3• •S5)

D3=D3 ( •S2•S3• •S5)

D4=D4 (S1•S2•S3• •S5)

D5=D5 (S1• • •S4•S5)

D6=D6 ( •S2• •S4•S5)

答:我们认为16位数据位的编码原理与8位数据位的hamming编码原理基本相同。即:,在k个数据位之外加上r个校验位,从而形成一个k+r位的新的码字,使新的码字的码距比较均匀地拉大。把数据的每一个二进制位分配在几个不同的偶校验位的组合中,当某一位出错后,就会引起相关的几个校验位的值发生变化,这不但可以发现出错,还能指出是哪一位出错,为进一步自动纠错提供了依据。

《计算机组成原理》

实验报告

实验室名称:S402

任课教师:邹洋

小组成员:王娜任芬

学号:2010212121 2010212119

实验一_Hamming码2

实验二_乘法器7

计算机组成原理--实验二算术逻辑运算实验

计算机组成原理--实验⼆算术逻辑运算实验实验⼆算术逻辑运算实验⼀、实验⽬的(1)了解运算器芯⽚(74LS181)的逻辑功能。

(2)掌握运算器数据的载⼊、读取⽅法,掌握运算器⼯作模式的设置。

(3)观察在不同⼯作模式下数据运算的规则。

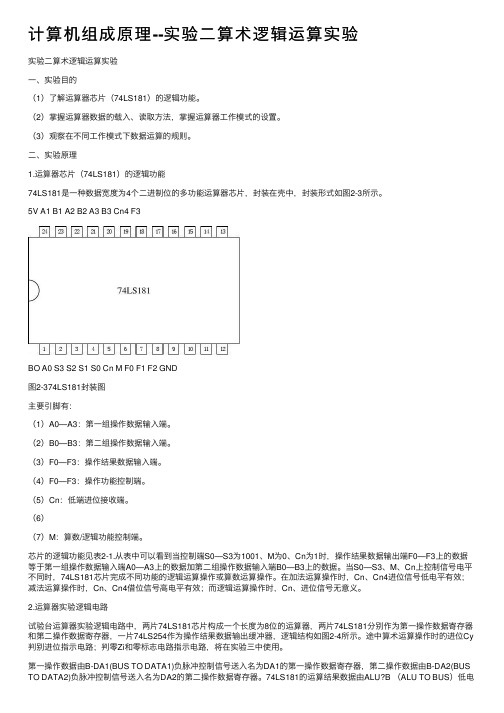

⼆、实验原理1.运算器芯⽚(74LS181)的逻辑功能74LS181是⼀种数据宽度为4个⼆进制位的多功能运算器芯⽚,封装在壳中,封装形式如图2-3所⽰。

5V A1 B1 A2 B2 A3 B3 Cn4 F3BO A0 S3 S2 S1 S0 Cn M F0 F1 F2 GND图2-374LS181封装图主要引脚有:(1)A0—A3:第⼀组操作数据输⼊端。

(2)B0—B3:第⼆组操作数据输⼊端。

(3)F0—F3:操作结果数据输⼊端。

(4)F0—F3:操作功能控制端。

(5)Cn:低端进位接收端。

(6)(7)M:算数/逻辑功能控制端。

芯⽚的逻辑功能见表2-1.从表中可以看到当控制端S0—S3为1001、M为0、Cn为1时,操作结果数据输出端F0—F3上的数据等于第⼀组操作数据输⼊端A0—A3上的数据加第⼆组操作数据输⼊端B0—B3上的数据。

当S0—S3、M、Cn上控制信号电平不同时,74LS181芯⽚完成不同功能的逻辑运算操作或算数运算操作。

在加法运算操作时,Cn、Cn4进位信号低电平有效;减法运算操作时,Cn、Cn4借位信号⾼电平有效;⽽逻辑运算操作时,Cn、进位信号⽆意义。

2.运算器实验逻辑电路试验台运算器实验逻辑电路中,两⽚74LS181芯⽚构成⼀个长度为8位的运算器,两⽚74LS181分别作为第⼀操作数据寄存器和第⼆操作数据寄存器,⼀⽚74LS254作为操作结果数据输出缓冲器,逻辑结构如图2-4所⽰。

途中算术运算操作时的进位Cy 判别进位指⽰电路;判零Zi和零标志电路指⽰电路,将在实验三中使⽤。

第⼀操作数据由B-DA1(BUS TO DATA1)负脉冲控制信号送⼊名为DA1的第⼀操作数据寄存器,第⼆操作数据由B-DA2(BUS TO DATA2)负脉冲控制信号送⼊名为DA2的第⼆操作数据寄存器。

计算机组成原理算术逻辑运算实验

实验2 算术逻辑运算实验一、实验目的1.掌握简单运算器的组成以及数据传送通路2.验证运算功能发生器(74LS181)的组合功能二、实验设备74LS181(两片),74LS273(两片), 74LS245(一片),开关若干,灯泡若干,单脉冲一片三、实验原理实验中的运算器由两片74LS181以并/串形式构成8位字长的ALU。

运算器的输出经过一个三态门(74LS245)和数据总线相连,运算器的两个数据输入端分别由两个锁存器(74LS373)锁存,锁存器的输入连至数据总线,数据开关用来给出参与运算的数据(A和B),并经过一个三态门(74LS245)和数据显示灯相连,显示结果。

74LS181:完成加法运算74LS273:输入端接数据开关,输出端181。

在收到上升沿的时钟信号前181和其输出数据线之间是隔断的。

在收到上升沿信号后,其将输出端的数据将传到181,同时,作为触发器,其也将输入的数据进行保存。

因此,通过增加该芯片,可以通过顺序输入时钟信号,将不同寄存器中的数据通过同一组输出数据线传输到181芯片的不同引脚之中74LS245:相当于181的输出和数据显示灯泡组件之间的一个开关,在开始实验后将其打开,可以使181的运算结果输出并显示到灯泡上四、实验步骤1. 选择实验设备:根据实验原理图,将所需要的组件从组件列表中拖到实验设计流程栏中。

2. 搭建实验流程:将已选择的组件进行连线(鼠标从一个引脚的端点拖动到另一组件的引脚端,即完成连线)。

搭建好的实验流程图如图2所示。

具体操作如下:①将74LS273芯片的0-7号引脚(数据端从低到高)及9号引脚(复位端)接到开关上,8号引脚接至单脉冲组件,左右两个74LS273芯片分别保存参与运算的数据A和B。

接着把两个74LS273组件的11-14号引脚(数据的低四位)分别接到74LS181组件(左)的0-7号引脚上,其中0-3号引脚为A的低四位,4-7号引脚为B的低四位。

计算机组成原理实验报告_32位ALU设计实验

实验三32位ALU设计实验一、实验目的学生理解算术逻辑运算单元(ALU)的基本构成,掌握Logisim 中各种运算组件的使用方法,熟悉多路选择器的使用,能利用前述实验完成的32位加法器、Logisim 中的运算组件构造指定规格的ALU 单元。

二、实验原理、内容与步骤实验原理、实验内容参考:1、32位加法功能的原理与设计1)设计原理1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。

这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。

而最后的第32位必须在前31位全部计算出结果后,才能开始计算。

这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

2)电路设计32位加法功能2、32位减法功能的原理与实现1)变减法为加法的原理1.在Y引脚处使用求补器(32位),即可变减法为加法2.用构造好的32位加法器。

Y各位取反,C0取1,即可达到减法变加法。

无符号数的减法溢出,带加减功能的ALU的进位取反后表示,有符号数的减法溢出,仍然用最高位和符号位是否相等来判断2)电路设计32位减法功能3、加减溢出检测的设计(不考虑乘除法)1)有符号数溢出的设计有符号数溢出的设计2)无符号数溢出的设计无符号数溢出的设计4、移位的原理与设计1)逻辑移位逻辑移位2)算术移位算术移位5、逻辑运算功能的原理与设计2)与、或、异或、或非逻辑6、大于、等于、小于功能设计大于、等于、小于功能设计7、AluOP的控制原理与设计1)原理:AluOP的控制原理与设计8、总电路设计图算术逻辑运算单元ALU三、实验结论及分析(实验完成功能情况、存在问题分析或改进思路、自己的心得体会等。

实验报告算术逻辑单元

一、实验目的1. 理解算术逻辑单元(ALU)的基本原理和功能。

2. 掌握ALU的设计方法和实现过程。

3. 通过实验加深对计算机组成原理的理解。

二、实验原理算术逻辑单元(ALU)是计算机中执行算术运算和逻辑运算的核心部件。

它主要完成加、减、乘、除等算术运算以及与、或、非、异或等逻辑运算。

ALU的设计和实现是计算机组成原理中的基础内容。

三、实验内容1. 设计一个8位ALU,能够完成加、减、乘、除、与、或、非、异或等运算。

2. 使用Verilog HDL语言实现该ALU。

3. 在FPGA平台上进行测试,验证ALU的功能。

四、实验步骤1. 分析ALU的功能需求,确定输入和输出信号。

2. 设计ALU的内部结构,包括运算单元、控制单元和寄存器。

3. 使用Verilog HDL语言编写ALU的代码。

4. 在FPGA平台上进行测试,验证ALU的功能。

五、实验结果与分析1. 实验结果根据实验要求,我们设计了一个8位ALU,能够完成加、减、乘、除、与、或、非、异或等运算。

以下是部分实验结果:(1)加法运算输入:A = 10101010,B = 11001100输出:10111010(2)减法运算输入:A = 11001100,B = 10101010输出:01010100(3)乘法运算输入:A = 10101010,B = 11001100输出:1111100000(4)除法运算输入:A = 11111111,B = 10000000输出:11111111(5)与运算输入:A = 10101010,B = 11001100输出:10001000(6)或运算输入:A = 10101010,B = 11001100输出:11101110(7)非运算输入:A = 10101010输出:01010101(8)异或运算输入:A = 10101010,B = 11001100输出:011001102. 实验分析通过实验,我们成功设计并实现了8位ALU。

《计算机组成原理》实验报告---8位算术逻辑运算实验

.'.计算机专业类课程实验报告课程名称:计算机组成原理学 院:信息与软件工程学院专 业:软件工程学生姓名:学 号:指导教师:日 期: 2012 年 12 月 15 日电子科技大学实验报告一、实验名称:8位算术逻辑运算实验二、实验学时:2三、实验内容、目的和实验原理:实验目的:1.掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

2.掌握模型机运算器的数据传送通路组成原理。

3.验证74LS181的组合功能。

4.按给定数据,完成实验指导书中的算术/逻辑运算。

实验内容:使用模型机运算器,置入两个数据DR1=35,DR2=48,改变运算器的功能设定,观察运算器的输出,记录到实验表格中,将实验结果对比分析,得出结论。

实验原理:1.运算器由两片74LS181以并/串形式构成8位字长的ALU。

.'. 2.运算器的输出经过一个三态门(74LS245)和数据总线相连。

3.运算器的两个数据输入端分别由两个锁存器(74LS273)锁存。

4.锁存器的输入连至数据总线,数据开关(INPUT DEVICE)用来给出参与运算的数据,并经过一三态门(74LS245)和数据总线相连。

5.数据显示灯(BUS UNIT)已和数据总线相连,用来显示数据总线内容。

实验器材(设备、元器件):模型机运算器四、实验步骤:1. 仔细查看试验箱,按以下步骤连线1)ALUBUS连EXJ32) ALU01连BUS13) SJ2连UJ24) 跳线器J23上T4连SD5) LDDR1,LDDR2,ALUB,SWB四个跳线器拨在左边6) AR跳线器拨在左边,同时开关AR拨在“1”电平2. 核对线路,核对正确后接通电源3. 用二进制数据开关KD0-KD7向DR1和DR2寄存器置入8位运算数据。

①调拨8位数据开关KD0-KD7为01100101(35H),准备向DR1送二进制数据。

②数据输出三态缓冲器门控信号ALUB=1(关闭)。

③数据输入三态缓冲器门控信号SWB=0(打开)。

计组实验报告(共10篇)

计组实验报告(共10篇)计组实验报告计算机组成原理实验报告一一、算术逻辑运算器1. 实验目的与要求:目的:①掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

②掌握简单运算器的数据传输通道。

③验算由74LS181等组合逻辑电路组成的运输功能发生器运输功能。

④能够按给定数据,完成实验指定的算术/逻辑运算。

要求:完成实验接线和所有练习题操作。

实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU 的特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

实验过程中,要认真进行实验操作,仔细思考实验有关的内容,把自己想得不太明白的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学目的。

实验完成后,要求每个学生写出实验报告。

2. 实验方案:1.两片74LS181(每片4位)以并/串联形式构成字长为8为的运算器。

2.8为运算器的输出经过一个输入双向三态门(74LS245)与数据总线相连,运算器的两个数据输入端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是用于保存参加运算的数据和运算的结果。

寄存器的输入端于数据总线相连。

3.8位数据D7~D0(在“INPUT DEVICE”中)用来产生参与运算的数据,并经过一个输出三态门(74LS245)与数据总线相连。

数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线上所内容。

4.S3、S2、S1、S0是运算选择控制端,由它们决定运算器执行哪一种运算(16种算术运算或16种逻辑运算)。

5.M是算术/逻辑运算选择,M=0时,执行算术运算,M=1时,执行逻辑运算。

6.Cn是算术运算的进位控制端,Cn=0(低电平),表示有进位,运算时相当于在最低位上加进位1,Cn=1(高电平),表示无进位。

逻辑运算与进位无关。

7.ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS上。

低电平有效。

计算机组成原理 运算器实验—算术逻辑运算实验

实验报告一、实验名称运算器实验—算术逻辑运算实验二、实验目得1、了解运算器得组成原理。

2、掌握运算器得工作原理.3、掌握简单运算器得数据传送通路。

4、验证运算功能发生器(74LS181)得组合功能.三、实验设备TDN-CM++计算机组成原理教学实验系统一套,导线若干。

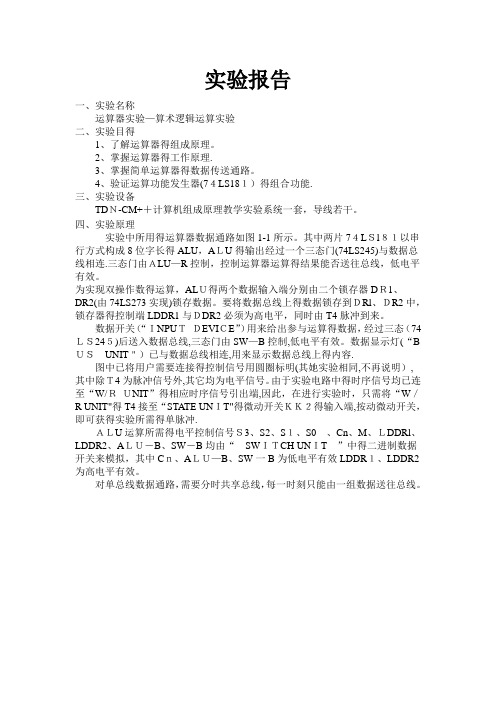

四、实验原理实验中所用得运算器数据通路如图1-1所示。

其中两片74LSl81以串行方式构成8位字长得ALU,ALU得输出经过一个三态门(74LS245)与数据总线相连.三态门由ALU—R控制,控制运算器运算得结果能否送往总线,低电平有效。

为实现双操作数得运算,ALU得两个数据输入端分别由二个锁存器DR1、DR2(由74LS273实现)锁存数据。

要将数据总线上得数据锁存到DRl、DR2中,锁存器得控制端LDDR1与DDR2必须为高电平,同时由T4脉冲到来。

数据开关(“INPUTDEVICE”)用来给出参与运算得数据,经过三态(74LS245)后送入数据总线,三态门由SW—B控制,低电平有效。

数据显示灯(“B USUNIT")已与数据总线相连,用来显示数据总线上得内容.图中已将用户需要连接得控制信号用圆圈标明(其她实验相同,不再说明),其中除T4为脉冲信号外,其它均为电平信号。

由于实验电路中得时序信号均已连至“W/RUNIT”得相应时序信号引出端,因此,在进行实验时,只需将“W/R UNIT"得T4接至“STATE UNIT"得微动开关KK2得输入端,按动微动开关,即可获得实验所需得单脉冲.ALU运算所需得电平控制信号S3、S2、S1、S0、Cn、M、LDDRl、LDDR2、ALU-B、SW-B均由“SWITCH UNIT ”中得二进制数据开关来模拟,其中Cn、ALU—B、SW一B为低电平有效LDDR1、LDDR2为高电平有效。

对单总线数据通路,需要分时共享总线,每一时刻只能由一组数据送往总线。

五、实验内容1.输入数据通过三态门74LS245后送往数据总线,在数据显示灯与数码显示管LED上显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西华大学数学与计算机学院实验报告

课程名称:计算机组成原理年级:2011级实验成绩:

指导教师:祝昌宇姓名:蒋俊

实验名称:算术逻辑运算单元实验学号:312011*********实验日期:2013-12-15

一、目的

1. 掌握简单运算器的数据传输方式

2. 掌握74LS181的功能和应用

二、实验原理

(1)ALU单元实验构成

1、结构试验箱上的算术逻辑运算单元上的运算器是由运算器由2片74LS181构成8字长的ALU 单元。

2、2片74LS373作为2个数据锁存器(DR1、DR2),8芯插座ALU-OUT作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。

3、运算器的数据输出由一片74LS244(输出缓冲器)来控制,8芯插座ALU-OUT作为数据输出端,可通过短8芯扁平电缆把数据输出端连接到数据总线上。

(2)ALU单元的工作原理

数据输入锁存器DR1的EDR1为低电平,并且D1CK有上升沿时,把来自数据总线上的数据打入锁存器DR1。

同样,使EDR2为低电平,并且D2CK有上升沿时,把来自数据总线上的数据打入锁存器DR2。

算术逻辑运算单元的核心是由2片74LS181构成,它可以进行2个8位二进制数的算术逻辑运算,74LS181的各种工作方式可通过设置其控制信号来实现(S0、S1、S2、S3、M、CN)。

当实验者正确设置了74LS181的各个控制信号,74LS181会运算数据锁存器DR1、DR2内的数据。

由于DR1、DR2已经把数据锁存,只要74LS181的控制信号不变,那么74LS181的输出数据也不会发生改变。

输出缓冲器采用74LS244,当控制信号ALU-O为低电平时,74LS244导通,把74LS181的运算结果输出到数据总线;ALU-O为高电平时,74LS244的输出为高阻。

图1 算术逻辑单元原理图三、使用环境

计算机组成原理实验箱

四、实验步骤

(一).逻辑或运算实验

1.把ALU-IN(8芯的盒型插座)与CPT-B板上的二进制开关单元中J1插座相连(对应二进制开关H16~H23), 把ALU-OUT(8芯的盒型插座)与数据总线上的DJ2相连。

2.把D1CK和D2CK用连线连到脉冲单元的PLS1上,把EDR1、EDR2、ALU-O、S0、S1、S2、S3、CN、M

3

4

5数据锁存器,通过逻辑笔来测量确定DR1寄存器(74LS373)的输出端,检验数据是否进入DR1中。

6

7数据锁存器。

$ 经过74LS181的计算,把运算结果输出到数据总线上,数据总线上的LED显示灯IDB0~IDB7显示为77H。

(二)不带进位位加法运算实验

1

2数据锁存器,通过逻辑笔来测量确定DR1寄存器(74LS373)的输出端,检验数据是否进入DR1中。

3

4数据锁存器。

$ 经过74LS181的计算,把运算结果输出到数据总线上,数据总线上的LED显示灯IDB0~IDB7显示为88H。

(三)实验数据记录

验证74LS181的算术运算和逻辑运算,在保持DR1=65H、DR2=A7H时,改变运算器的功能设置,观察运算器的输出,填入表1中,并和理论分析进行比较、验证。

五、总结

通过本次实验我掌握了算术逻辑运算器单元ALU(74LS181)的工作原理和简单运算器的数据传送通道,了解了由74LS181等组合逻辑电路的运算功能,能够按给定数据按实验要求完成实验指定的算术逻辑运算。

自己能够更清楚了算术逻辑运算器的功能,同时更明白逻辑加与算术的区别,提高了动手能力。