数字系统时钟抖动

时钟抖动度量指标和测试方法概述

PAGE 068定位导航与授时Positioning,Navigation and Timing时钟抖动度量指标和测试方法概述■ 龙丹(海军工程大学 430033)数字通信系统中,时钟抖动是影响通信质量的因素之一,在系统设计、设备研制、工程验收等各环节抖动指标是必须考虑的。

本文介绍了通信中常用的抖动概念、分类、度量指标和测试方法,并对时钟设备抖动指标测试进行了描述。

最后对抖动测试的发展方向进行了展望。

In digital communication systems, clock jitter is one of the factors that affect communication quality, and jitter indicators must be considered in various links such as system design, equipment development, and engineering acceptance. This article introduces the jitter concepts, classifications, metrics and test methods commonly used in communications, and describes the jitter index test of clock equipment. Finally, the development direction of jitter test is prospected.时钟抖动 高速时钟同步Clock jitter; high-speed clock synchronizationDoi:10.3969/j.issn.1673-5137.2021.02.010摘 要Abstract关键词Key Words1. 背景ITU-T G.810标准中抖动的定义是“数字信号的各个有效瞬时相对其当时的理想位置(相位)的短期性偏离”,相位偏离的频率称为抖动频率,“短期”指变化的频率大于或等于10Hz(这里是通信领域传统的定义,其他领域对抖动可能有不同的定义)[1]。

pll jitter 指标

pll jitter 指标

PLL(Phase-Locked Loop)是一种控制系统,用于在输入信号和参考信号之间保持恒定的相位差。

Jitter是指时钟信号或数据信号在时间域上的抖动,即信号的周期性或稳定性受到干扰而产生的波动。

因此,PLL Jitter指标是用来衡量PLL系统中时钟信号或数据信号的抖动程度的指标。

从多个角度来看,PLL Jitter指标的重要性体现在以下几个方面:

1. 系统稳定性,PLL Jitter指标直接影响系统的稳定性和性能。

高抖动会导致时钟信号不稳定,可能导致数据传输错误或时序不准确,影响系统整体性能。

2. 信号完整性,在数字通信系统中,时钟信号的抖动会影响到数据的采样和恢复,因此PLL Jitter指标对于保证信号的完整性和准确性至关重要。

3. 设计优化,了解PLL Jitter指标可以帮助工程师优化PLL 系统的设计,选择合适的参数和器件,以最大程度地减小抖动,提

高系统性能。

4. 标准遵从,在一些行业标准中,对于PLL Jitter指标有明确的要求,特别是在高速通信和数据存储领域,因此了解和符合这些指标是非常重要的。

在实际应用中,评估PLL Jitter指标通常需要通过仪器进行测量和分析,例如频谱分析仪、时钟数据恢复器等。

工程师们会根据具体的系统要求和标准,对PLL Jitter指标进行测试和验证,以确保系统的稳定性和性能。

总之,PLL Jitter指标是衡量PLL系统性能的重要参数,对于数字通信和控制系统的设计和优化具有重要意义。

通过对PLL Jitter指标的全面了解和有效管理,可以提高系统的稳定性和可靠性,满足特定应用的要求。

输出波形上下抖动的原因

输出波形上下抖动的原因波形上下抖动(Jitter)是指信号传输过程中时间间隔的不稳定性,波形在时间轴上出现微小的漂移的现象。

它可能会导致数据传输错误、性能下降和系统故障等问题。

波形上下抖动的原因非常复杂,包括时钟不稳定性、电磁干扰、信号传输路径的不对称性,以及噪声等。

一、时钟不稳定性:时钟是所有数字系统中最重要的组件之一,它确定了数据传输的时间间隔。

时钟源的不稳定性可能是波形上下抖动的主要原因之一、时钟源可能受到温度变化、电源噪声、振荡器偏移、时钟分配器的不均匀负载等因素的影响,从而导致时钟信号的不稳定,进而引起波形上下抖动。

二、电磁干扰:电磁干扰是指周围电子设备和电磁场对信号的影响。

在现代电子设备中,特别是在高速通信和数据中心应用中,电磁辐射和电磁干扰可能会通过电源线、地线、信号线等途径影响信号的传输质量。

电磁干扰可能产生许多随机噪声,导致信号的上下抖动。

三、信号传输路径的不对称性:信号传输路径不对称可能由不同的原因引起,例如PCB布线不均匀、信号线长度不一致、不同信号层之间的耦合等。

当信号在不对称的路径上传输时,由于信号传播速度的变化,可能会出现波形上下抖动的情况。

四、噪声:五、时钟与数据的不匹配:当数据的边沿与时钟信号的边沿不完全匹配时,可能引起波形上下抖动。

这种不匹配可能由于采样时钟的相位偏移、时钟频率的差异、时钟抖动等因素引起。

不完全匹配的时钟和数据可能会导致传输错误和性能下降。

六、传输介质的特性:传输介质的特性也对波形上下抖动起着重要的影响。

例如,在高速通信中,传输介质的衰减、色散、损耗等因素都会导致波形上下抖动。

此外,传输介质的温度变化、机械振动等因素也会对信号的传输质量产生负面影响。

七、设备老化和磨损:设备的老化和磨损也可能导致波形上下抖动。

例如,电容的老化、电阻的变化、传输线的损耗等因素在长时间使用后可能会导致信号的上下抖动。

总结起来,波形上下抖动是由多个因素共同作用造成的。

这些因素包括时钟不稳定性、电磁干扰、信号传输路径的不对称性、噪声、时钟与数据的不匹配、传输介质的特性以及设备老化和磨损等。

时间抖动(jitter)的概念及其分析方法

时间抖动(jitter)的概念及其分析方法随着通信系统中的时钟速率迈入GH z级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3GH z以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

本文介绍了时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

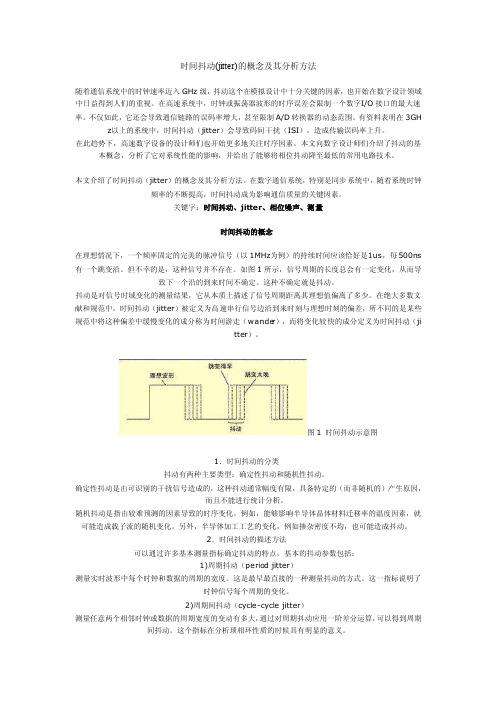

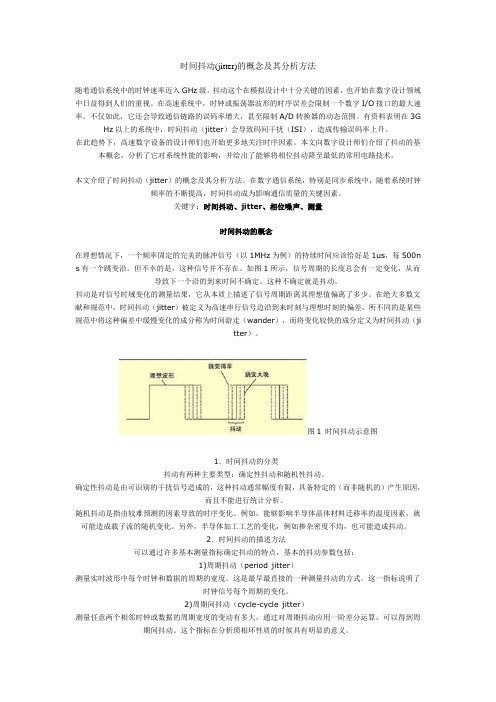

关键字:时间抖动、jitter、相位噪声、测量时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns 有一个跳变沿。

但不幸的是,这种信号并不存在。

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

时钟抖动的定义与测量方式

译自: SiT-AN10007 Rev 1.2 January 2014Clock Jitter Definitions and Measurement Methods时钟抖动的定义与测量方式[译]懒兔子1 简介抖动是实际信号的一组边沿与理想信号之间的偏差(兔子:说白了,抖动就是实际情况和理想情况不一样,差别越大抖动越大)。

时钟信号的抖动通常由系统中的噪声或其他干扰因素引起。

影响因素包括热噪声、电源变化(波动)、负载的状况(负载也可以反过来影响时钟信号)、设备噪声和临近电路耦合进来的干扰。

2 抖动的分类抖动可以通过许多方式测量(不同方式测量到的抖动被分别加以定义),以下是主要的抖动分类:1. 周期抖动(Period Jitter)2. 相邻周期间的抖动(Cycle to Cycle Period Jitter)3. 长时间抖动(Long Term Jitter)4. 相位抖动(Phase Jitter)5. 单位时间间隔抖动(TIE,Time Interval Error)2.1 周期抖动周期抖动是时钟信号的实际周期长度与理想周期长度之间的偏差,测量样本为数目不定(随机)的一组周期。

如果给定一定数目的单个时钟周期,我们就可以通过测量每个周期的长度并计算平均的周期长度,以及这些时钟周期的标准差和峰峰值(peak-to-peak value)。

这里所说的标准差和峰峰值也分别被称为RMS抖动和Pk-Pk周期抖动。

许多文献将周期抖动直接定义为被测时钟周期与理想周期之间的误差。

但是真实情况下很难对理想周期进行量化。

如果我们用示波器观察一个标称100MHz的晶振,测得的平均时钟周期却可能是9.998ns,而不是理想的10ns。

所以退而求其次,通常将平均周期作为理想周期看待(兔子:因为实际周期都是在理想值周围按照一定规律分布的,如果测量时间足够长,得到的平均值就可以非常接近理想值)。

2.1.1 周期抖动的应用周期抖动对于计算数字系统的时序裕量十分有用。

dpll时钟去抖原理

dpll时钟去抖原理

DPLL(Digital Phase-Locked Loop)是一种数字锁相环技术,用于抑制时钟抖动(jitter)的影响。

时钟抖动是由外界环境和电路噪音引起的时钟信号的不稳定性和波动性。

DPLL时钟抖动抑制原理如下:

1. 参考时钟源:DPLL系统中使用一个准确且稳定的参考时钟源作为参考信号。

这个参考时钟源通常是一个高精度的晶振或外部时钟源。

2. 相频检测器(Phase Detector):DPLL系统中的相频检测器用于比较参考时钟和反馈时钟信号之间的相位差。

相频检测器的输出是一个对相位差大小和方向的度量。

3. 数字滤波器(Digital Filter):相频检测器输出的相位差信号会通过数字滤波器进行滤波和处理。

数字滤波器用于平滑相频检测器输出的相位差信号,去除高频的噪声和波动。

4. 锁定环路:系统根据经过滤波的相位差信号来调整反馈时钟信号,使其与参考时钟保持同步。

调整可以通过延迟或提前反馈时钟信号来实现。

5. VCO(Voltage-Controlled Oscillator):DPLL系统中的VCO用于产生反馈时钟信号。

调整后的相频检测器输出通过控制VCO的电压输入,以调整VCO的频率,从而使反馈时钟信号趋于与参考时钟信号同频。

6. 反馈环路:经VCO发生器产生的时钟信号经过延迟电路后反馈至相频检测器,形成闭环控制。

通过以上的反馈机制,DPLL系统可以实时对时钟抖动进行监测和调整,使得反馈时钟能够与参考时钟同频且稳定。

这样可以有效抑制时钟抖动对系统性能的影响,提高信号的稳定性和准确性。

时间抖动(jitter)的概念及其分析方法

时间抖动(jitter)的概念及其分析方法随着通信系统中的时钟速率迈入GHz级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。

在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。

不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。

有资料表明在3G Hz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。

在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。

本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。

本文介绍了时间抖动(jitter)的概念及其分析方法。

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。

关键字:时间抖动、jitter、相位噪声、测量时间抖动的概念在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500n s有一个跳变沿。

但不幸的是,这种信号并不存在。

如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。

这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。

在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter)。

图1 时间抖动示意图1.时间抖动的分类抖动有两种主要类型:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。

随机抖动是指由较难预测的因素导致的时序变化。

例如,能够影响半导体晶体材料迁移率的温度因素,就可能造成载子流的随机变化。

时钟抖动(CLK)和相位噪声之间的转换

应用笔记3359时钟抖动(CLK)和相位噪声之间的转换摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。

本文还描述了周期抖动和相位噪声谱之间的关系,并介绍如何将相位噪声谱转换成周期抖动。

几乎所有集成电路和电气系统都需要时钟(CLK)。

在当今世界中,人们以更快的速度处理和传送数字信息,而模拟信号和数字信号之间的转换速率也越来越快,分辨率越来越高。

这些都要求工程师更多地关注时钟信号的质量。

时钟信号的质量通常用抖动和相位噪声来描述。

抖动包括周期抖动,逐周期抖动和累计抖动,最常用的是周期抖动。

时钟的相位噪声用来说明时钟信号的频谱特性。

本文首先简单介绍用来测量时钟抖动和相位噪声的装置。

然后介绍周期抖动和相位噪声之间的关系,最后介绍将相位噪声谱转换成周期抖动的简单公式。

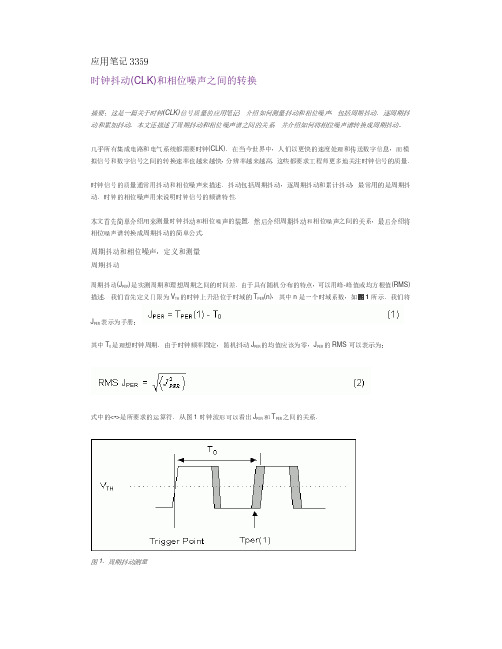

周期抖动和相位噪声:定义和测量周期抖动周期抖动(J PER)是实测周期和理想周期之间的时间差。

由于具有随机分布的特点,可以用峰-峰值或均方根值(RMS)描述。

我们首先定义门限为V TH的时钟上升沿位于时域的T PER(n),其中n是一个时域系数,如图1所示。

我们将JPER表示为手册:其中T0是理想时钟周期。

由于时钟频率固定,随机抖动J PER的均值应该为零,J PER的RMS可以表示为:式中的<•>是所要求的运算符。

从图1时钟波形可以看出J PER和T PER之间的关系。

图1. 周期抖动测量相位噪声测量为了理解相位噪声谱L(f)的定义,我们首先定义时钟信号的功率谱密度S C(f)。

将时钟信号接频谱分析仪,即可测得S C(f)。

相位噪声谱L(f)定义为频率f处的S C(f)值与时钟频率f C处的S C(f)值之差,以dB表示。

图2说明了L(f)的定义。

图2. 相位噪声谱的定义相位噪声谱L(f)的数学定义为:注意L(f)代表的是f C和f处谱值的比,L(f)将在下文介绍。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字系统时钟抖动

数字系统时钟抖动是指当数字系统的时钟信号存在不稳定性或噪声时,导致时钟信号产生微小的偏移或抖动现象。

时钟信号在数字系统

中起着至关重要的作用,它用于同步各个模块的操作,确保数据的准

确传输和处理。

然而,时钟抖动会对系统的性能和可靠性产生负面影响。

本文将探讨数字系统时钟抖动的原因、后果以及应对措施。

一、时钟抖动的原因

1. 元器件误差:元器件的制造和使用过程中会存在一定的误差,例

如晶体振荡器的频率精度、时钟发生器的稳定性等。

这些误差在时钟

信号传输过程中会放大,导致时钟抖动。

2. 环境干扰:数字系统所处的环境中存在各种干扰源,如电磁波干扰、温度变化、电源波动等。

这些干扰会对时钟信号的传输和接收产

生影响,进而引起时钟抖动。

3. 信号串扰:在复杂的数字系统中,各个信号线之间会存在串扰现象,即一个信号线上的电磁场对其他信号线产生影响。

当时钟信号受

到其他信号线的串扰时,也会导致时钟抖动。

二、时钟抖动的后果

1. 时序错误:时钟抖动可能导致时钟信号的上升沿或下降沿不准确,进而造成时序错误。

这会导致数据传输出错、计时错误等问题,严重

时可能导致整个系统的崩溃。

2. 数据稳定性下降:时钟抖动会导致数据的采样和恢复不准确,使得数据的稳定性下降。

在高速数据传输中,时钟抖动可能导致数据丢失或数据错误,影响系统的可靠性和性能。

3. 时钟频率偏移:时钟抖动可能导致时钟信号的频率产生微小的偏移,进而影响系统的时钟同步和数据处理速度。

这会给系统的运行带来一定的难度和不确定性。

三、应对时钟抖动的措施

1. 选择高质量的元器件:在设计和选择数字系统的元器件时,应注重其频率精度、稳定性和抗干扰能力。

采用高质量的晶体振荡器、时钟发生器等元器件,能够减小时钟抖动的概率。

2. 优化时钟布线:合理设计时钟信号的布线路径,避免与其他信号线的干扰。

尽可能使用短而直接的时钟线路,减少串扰的可能性。

3. 电磁屏蔽和滤波:对数字系统中的时钟信号进行电磁屏蔽和滤波处理,减少来自外界的干扰。

这可以采用屏蔽罩、屏蔽线材、滤波器等措施来实现。

4. 时钟同步技术:采用适当的时钟同步技术,例如时钟提取、时钟分配和时钟重构等方法,可以有效降低时钟抖动的影响。

通过对时钟信号的控制和校正,使得时钟信号更稳定可靠。

结语

数字系统时钟抖动是一个复杂而常见的问题,需要我们在设计和应用过程中给予足够的重视。

只有采取有效的措施来减小时钟抖动,才

能确保数字系统的正常运行和可靠性。

通过合理的元器件选择、布线优化和时钟同步技术应对时钟抖动,我们能够提高系统的性能、减少数据错误,并为数字系统的发展提供更稳定可靠的时钟信号。