多模块程序设计忽略P-182

矿用隔爆兼本安型可编程控制箱的PLC模块设计

科学技术创新2021.03矿用隔爆兼本安型可编程控制箱的P LC 模块设计叶源涛李鹏王子懿(安徽理工大学机械工程学院,安徽淮南232001)随着煤矿自动化与信息化水平的提高,建设集约、安全、高效、绿色型矿井,实现减员提效、保障生产安全成了煤炭行业追求的目标[1]。

为了实现矿井排水设备的无人值守和智能联动控制,能够在节能减排基础上有效延长机组使用寿命,在减员增效基础上进一步减轻工作人员劳动强度,在安全生产的基础上提高矿井的自动化水平和运营管理水平,基于PLC 的矿用隔爆兼本安型隔爆箱就是为了提高这方面的能力而应用的,它是矿井排水系统的核心控制部分。

本控制箱可用于煤矿井下或其他周围空气中含有爆炸性气体的工矿企业中[2]。

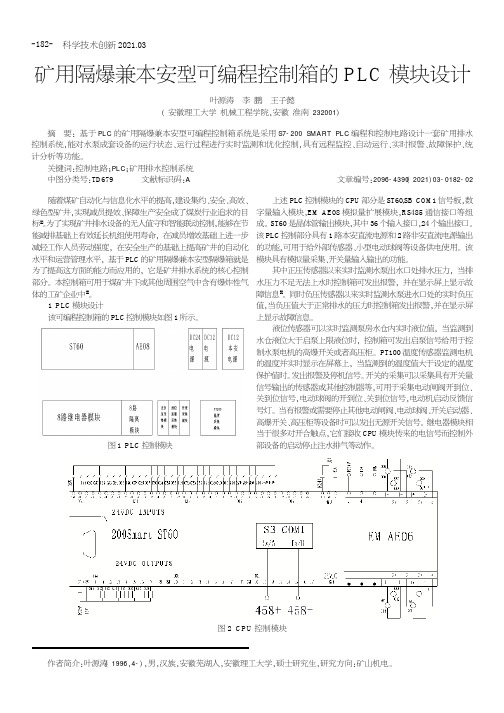

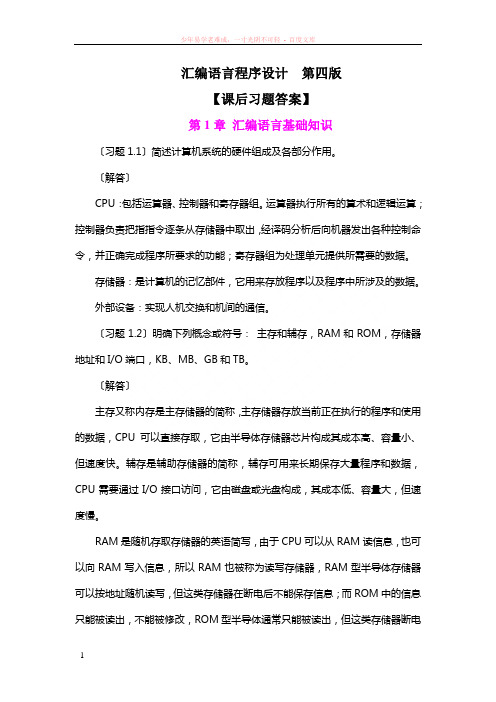

1P LC 模块设计该可编程控制箱的PLC 控制模块如图1所示。

图1P LC 控制模块上述PLC 控制模块的CPU 部分是ST60,SB CO M 1信号板,数字量输入模块,EM A E08模拟量扩展模块,R S485通信接口等组成。

ST60是晶体管输出模块,其中36个输入接口,24个输出接口。

该PLC 控制部分具有1路本安直流电源和2路非安直流电源输出的功能,可用于给外部传感器、小型电动球阀等设备供电使用。

该模块具有模拟量采集、开关量输入输出的功能。

其中正压传感器以来实时监测水泵出水口处排水压力,当排水压力不足无法上水时控制箱可发出报警,并在显示屏上显示故障信息[3]。

同时负压传感器以来实时监测水泵进水口处的实时负压值,当负压值大于正常排水的压力时控制箱发出报警,并在显示屏上显示故障信息。

液位传感器可以实时监测泵房水仓内实时液位值,当监测到水仓液位大于启泵上限液位时,控制箱可发出启泵信号给用于控制水泵电机的高爆开关或者高压柜。

PT100温度传感器监测电机的温度并实时显示在屏幕上,当监测到的温度值大于设定的温度保护值时。

发出报警及停机信号。

开关的采集可以采集具有开关量信号输出的传感器或其他控制器等,可用于采集电动闸阀开到位、关到位信号,电动球阀的开到位、关到位信号,电动机启动反馈信号灯。

汇编语言程序设计(第四版)【课后答案】

汇编语言程序设计第四版【课后习题答案】第1章汇编语言基础知识〔习题1.1〕简述计算机系统的硬件组成及各部分作用。

〔解答〕CPU:包括运算器、控制器和寄存器组。

运算器执行所有的算术和逻辑运算;控制器负责把指指令逐条从存储器中取出,经译码分析后向机器发出各种控制命令,并正确完成程序所要求的功能;寄存器组为处理单元提供所需要的数据。

存储器:是计算机的记忆部件,它用来存放程序以及程序中所涉及的数据。

外部设备:实现人机交换和机间的通信。

〔习题1.2〕明确下列概念或符号:主存和辅存,RAM和ROM,存储器地址和I/O端口,KB、MB、GB和TB。

〔解答〕主存又称内存是主存储器的简称,主存储器存放当前正在执行的程序和使用的数据,CPU可以直接存取,它由半导体存储器芯片构成其成本高、容量小、但速度快。

辅存是辅助存储器的简称,辅存可用来长期保存大量程序和数据,CPU需要通过I/O接口访问,它由磁盘或光盘构成,其成本低、容量大,但速度慢。

RAM是随机存取存储器的英语简写,由于CPU可以从RAM读信息,也可以向RAM写入信息,所以RAM也被称为读写存储器,RAM型半导体存储器可以按地址随机读写,但这类存储器在断电后不能保存信息;而ROM中的信息只能被读出,不能被修改,ROM型半导体通常只能被读出,但这类存储器断电后能保存信息。

存储器由大量存储单元组成。

为了区别每个单元,我们将它们编号,于是,每个存储单元就有了一个存储地址,I/O接口是由一组寄存器组成,为了区别它们,各个寄存器进行了编号,形成I/O地址,通常称做I/O端口。

KB是千字节、MB是兆字节、GB是吉字节和TB是太字节,它们都是表示存储器存储单元的单位。

〔习题1.3〕什么是汇编语言源程序、汇编程序、目标程序?〔解答〕用汇编语言书写的程序就称为汇编语言源程序;完成汇编工作的程序就是汇编程序;由汇编程序编译通过的程序就是目标程序。

〔习题1.4〕汇编语言与高级语言相比有什么优缺点?〔解答〕汇编语言与高级语言相比的优点:由于汇编语言本质就是机器语言,它可以直接地、有效地控制计算机硬件,因而容易产生运行速度快,指令序列短小的高效目标程序,可以直接控制计算机硬件部件,可以编写在“时间”和“空间”两方面最有效的程序。

模块化程序设计中隐藏同名变量的应用

e do n fr

? srk 1+ ! S t (, ) =,

re turn S

edu c n fn

运 行 结 果 , 明 显 错 误 。 分 析 上 述 程 序 , 可 以 发 现 , 自 定 义 函 数

运行 结果 :

3用P I T 命 令 隐藏 主程序 中 可能存 在 的变量 RVA E 为 解 决 上述 问题 ,可 以在 子 程 序 中用 P IA E 令隐 藏 主程 序 中可 能 R VT 命 存 在 的变量 ,使 这些 变量 在子 程序 中暂 时无 效 。有两 种命令 格 式: 【 格式 1 RV T< 】P IAE 内存 变量 表 > 【 格式 2 RV TA LL K X E T通 配符 > 】P IAE L [IE C P < I E ]

范 围 ,在它 的 定义 域 内有效 。v 中变量 的 作用 范 围有 三种 :全 局变 量 在整 F 个 程序 中 ,包括 上 下级 过程 中都有 效 用 ,用p b i声 名 ;局部 变量 只 在 定 u lc 义 它的模 块 内有效 ,用 lc l 名 ;私有 变量 在定 义它 的模块 和 它的下 级子 o a声

V A

【术用 技应 】

VF 块 化 程 序 设 计 中 隐 藏 同 名 变 量 的 应 用 模

刘艾侠

( 宝鸡职业技术学院 陕西 宝鸡 711) 203

摘

要: 结构化程序 设计尽管 简化程序设 计过程 ,然 而也给变 量 的使用 带来一 些问题 。其 中尤为突 出的是 同名变量 的重叠 ,相互 影响 。通 过隐藏变置 ,消除

中定 义 的同名 变 量 ,我原 来只 是 简单 根据 变 量名 称进 行 区分 ,由于 作用 范 围不 同 ,因 为虽 然 同名但 互不 影 响 ;但这 样 的方 法 用在 相互 调用 的模 块中

EDA实验1lxm二选一数据选择器

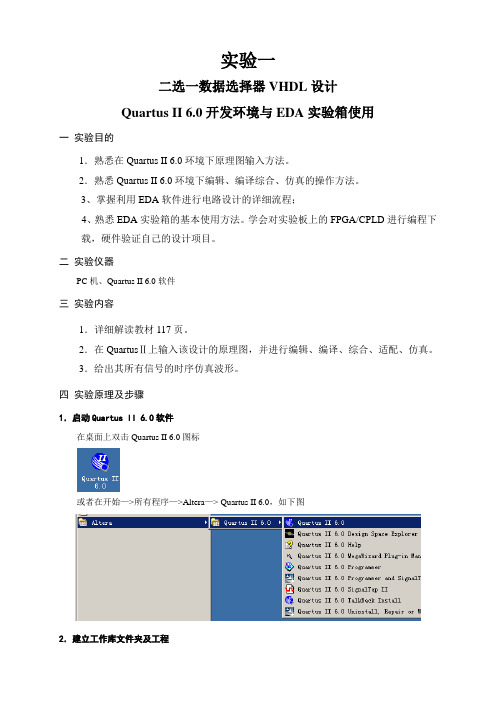

实验一二选一数据选择器VHDL设计Quartus II 6.0开发环境与EDA实验箱使用一实验目的1.熟悉在Quartus II 6.0环境下原理图输入方法。

2.熟悉Quartus II 6.0环境下编辑、编译综合、仿真的操作方法。

3、掌握利用EDA软件进行电路设计的详细流程;4、熟悉EDA实验箱的基本使用方法。

学会对实验板上的FPGA/CPLD进行编程下载,硬件验证自己的设计项目。

二实验仪器PC机、Quartus II 6.0软件三实验内容1.详细解读教材117页。

2.在QuartusⅡ上输入该设计的原理图,并进行编辑、编译、综合、适配、仿真。

3.给出其所有信号的时序仿真波形。

四实验原理及步骤1.启动Quartus II 6.0软件在桌面上双击Quartus II 6.0图标或者在开始—>所有程序—>Altera—> Quartus II 6.0,如下图2.建立工作库文件夹及工程任何一次设计都是一项工程(Project),所有此工程相关的所有设计文件都需要放在同一个文件夹里。

不同的设计放在不同的文件夹中。

在E盘下建立一个存放本次设计的工程文件夹,比如“shiyan1”。

注意不要使用中文文件夹,文件夹的存放路径也不要包含中文。

注意本实验室计算机C盘和D盘是重启后复原,不要将任何文件和文件夹放置在桌面或者C、D盘下。

初次打开Quartus II 6.0,会有如图提示:选择是的情况下,首先是新工程向导:介绍下一步下一步下一步,选择目标芯片,首先在Family栏选择ACEX1K系列,然后选择此系列的具体芯片:EP1K30TC144-3。

注意不要选成了EP1K30TC144-3。

下一步就点完成。

3.建立文本程序文件选择File菜单下的New或者直接点击工具栏中的新建图标,选择新建文件类型为VHDL File。

接下来另存文件:保存时需更改文件名与项目名称一样,注意保存在同一个工程文件夹下面。

2021年广西科技大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)

2021年广西科技大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、某存储器容量为64KB,按字节编址,地址4000H~5FFFH为ROM区,其余为RAM 区。

若采用8K×4位的SRAM芯片进行设计,则需要该芯片的数量是()。

A.7B.8C.14D.162、某一计算机采用主存Cache存储层次结构,主存容量有8个块,Cache容量有4个块,采取直接映射方式。

若主存块地址流为0,1,2,5,4,6,4,7,1,2,4,1,3,7,2,一开始Cache为空,此期间Cache的命中率为()。

A.13.3%B.20%C.26.7%D.33.3%3、在补码一位乘中,若判断位Y n Y n+1=01,则应执行的操作为()。

A.原部分积加[-x]补,然后右移一位B.原部分积加[x]补,然后右移一位C.原部分积加[-x] 补,然后左移一位D.原部分积加[x]补,然后左移一位4、在浮点机中,()是隐藏的。

A.阶码B.数符C.尾数D.基数5、设x为整数,[x]补=1.x1x2x3x4x5,若要x<-16,x1~ x5应满足的条件是()。

A. x1~ x5至少有一个为1B.x1必须为1,x2~x5至少有一个为1C.x1必须为0,x2~x5至少有一个为1D.x1必须为0,x2~x5任意6、在下面描述的PCI总线的基本概念中,不正确的表述是()。

A.PCI总线支持即插即用B.PCI总线可对传输信息进行奇偶校验C.系统中允许有多条PCI总线D.PCI设备一定是主设备7、下列关于总线设计的叙述中,错误的是()。

A.并行总线传输比串行总线传输速度快B.采用信号线复用技术可减少信号线数量C.采用突发传输方式可提高总线数据传输率D.采用分离事务通信方式可提高总线利用率8、假定机器M的时钟频率为200MHz,程序P在机器M上的执行时间为12s。

对P优化时,将其所有乘4指令都换成了一条左移两位的指令,得到优化后的程序P。

可编程设备服务器PDS系列使用手册说明书

支援模块包含PDS-5000系列: PDS-5105D-MTCPDS-700/PDS-700 系列:DS-712, DS-715, PDS-720(D), PDS-721(D), PDS-732(D), PDS-734(D), PDS-742(D), PDS-743(D), PDS-752(D), PDS-755(D), PDS-762(D), PDS-782(D), PDS-782(D)-25.PDSM-700系列:PDSM-721(D), PDSM-732(D), PDSM-734(D), PDSM-742(D), PDSM-743(D), PDSM-752(D), PDSM-755(D), PDSM-762(D), PDSM-782(D).PPDS-700-MTCP 系列:PPDS-720(D)-MTCP, PPDS-721(D)-MTCP, PPDS-732(D)-MTCP, PPDS-734(D)-MTCP, PPDS-742(D)-MTCP, PPDS-743(D)-MTCP, PPDS-752(D)-MTCP, PPDS-755(D)-MTCP, PPDS-762(D)-MTCP, PPDS-782(D)-MTCP.PPDSM-700-MTCP 系列:PPDSM-720(D)-MTCP, PPDSM-721(D)-MTCP, PPDSM-732(D)-MTCP, PPDSM-734(D)-MTCP, PPDSM-742(D)-MTCP, PPDSM-743(D)-MTCP, PPDSM-752(D)-MTCP, PPDSM-755(D)-MTCP, PPDSM-762(D)-MTCP, PPDSM-782(D)-MTCP.PPDS-700-IP67系列:承诺 郑重承诺: 凡泓格科技股份有限公司产品从购买后,开始享有一年保固,除人为使用不当的因素除外。

责任声明凡使用本系列产品除产品质量所造成的损害,泓格科技股份有限公司不承担任何的法律责任。

keil3错误提示

keil3错误提示编译产生的警告信息:1 .警告提示类型 173警告提示信息: WarningC173:missing return-expression(缺少返回表达式) 解决方法:在函数的结尾处加入和函数声明的返回值类型相同的返回值。

2. 警告提示类型 182警告提示信息: WarningC182:pointer to different objects(指针指向不同的目标)解决方法:将指针和指针指向的对象的数据类型改成一致。

3. 警告提示类型 206警告提示信息:WarningC206:missing function prototype(缺少函数原型) 解决方法:被引用函数未被声明或不存在,检查是否声明或编写。

4. 警告提示类型 209警告提示信息:WarningC209:too few actual parameters(太少的实参)解决方法:查看被调用的函数原型,检查入口参数是否与原型一致。

5. 警告提示类型 275警告提示信息:WarningC275:expression with possibly no effect(表达式可能无效)解决方法:删除或修改无用表达式。

6. 警告提示类型 276警告提示信息 WarningC276:constant in condition expression(条件表达式为常数)解决方法:检查判断条件,在判断表达式中将常值条件改正。

7. 警告提示类型 280警告提示信息:WarningC280:'??'unreferenced local variable(局部变量在函数中未作任何的存取操作)解决方法:删除函数中变量的声明。

8. 警告提示类型 317警告提示信息:WarningC317:attempt to redefine macro'??'(宏名称重新定义无效)解决方法:将重复定义的宏名重新起名即可。

编译产生的错误信息1. 错误提示信息:error C100:unpritable character 0x?? skipped(跳过不可打印的字符0x,,)解决方法:在对应的语句里存在非法字符,找到非法字符,如中文字符,删掉即可。

汽车设计专业术语

1) PP Produc tionProveo ut 生产验证2) TTO Tool Try-Out 工装设备试运行3) (J1) Job 1 整车投产4) DFMEADesign Failur e Mode Effect s Analys is 故障模式影响分析设计5) DVP Design Verifi catio n Plan 设计验证计划6) DVP&R Design Verifi catio n Plan & Report设计验证计划和结果7) FMEA Failur e Mode Effect s Analys is 故障模式影响分析8) FPDS Ford Produc t Develo pment System福特产品开发系统9) GYR Green-Yellow-Red 绿-黄-红10) MRD Materi al Requir ed Date 物料要求到厂日11) OTT OK-TO-TOOL 可以开模12) TKO Toolin g-Kick-Off 工装启动13) OEM origin al Equipm ent Manufa cture r 设备最初制造厂14) FtF/F2F Face To Face 面对面会议15) PV Produc tionValida tion产品验证16) OTS Off-Toolin g-Sample完全工装样件17) QOS Qualit y Operat ing System质量运作体系18) TS-16949Techni cal Specif icati on – 16949技术规范-1694919) APQP Advanc ed Produc t Qualit y Planni ng 先期产品质量计划20) IPD In PlantDate 进厂日21) PPM Partsper Millio n (applie d to defect ive Suppli er parts)零件的百万分比率(适用于供应商不合格零件)22) PPAP Produc tionPart Approv al Proces s 生产件批准程序23) Pre-PV Pre -Produc tionValida tion产品预先验证24) 1PP- FirstPhaseof Produc tionProve-Out 第一次试生产25) 3C Custom er(顾客导向)、Compet ition(竞争导向)、Compet ence(专长导向)26) 4S Sale, Sparep art零配件, Servic e, Survey信息反馈27) 5S 整理,整顿,清理,清洁,素养28) 8D- 8 Discip line29) ABS Anti-lock Brakin g System30) AIAG 美国汽车联合会31) ANPQPAllian ce New Produc t Qualit y Proced ure32) Apport ionme nt 分配33) APQP Advanc ed Produc t Qualit y Plan34) Backli te Windsh ield后窗玻璃35) Benchm ark Data 样件资料36) bloods hot adj.充血的, 有血丝的37) BMW Bavari an MotorWorks38) C.P.M Certif ied Purcha singmanger认证采购经理人制度39) CB- Confir matio n Build确认样车制造40) CC- Change CutOff设计变更冻结41) CC\SC- critic al/signif icant charac teris tic42) CCR Concer n & Counte rmeas ure Reques t43) CCT CrossCompan y Team44) Charac teris ticsMatrix特性矩阵图45) COD Cash on Delive ry 货到付现预付货款(T/T in advanc e)46) CP1- Confir matio n Protot ype 1st 第一次确认样车47) CP2- Confir matio n Protot ype 2nd 第二次确认样车48) Cpk 过程能力指数Cpk=Zmin/349) CPO Comple menta ry Partsorder50) Crafts mansh ip 精致工艺51) Cross-functi onalteams跨功能小组52) CUV Car-BasedUltili ty Vehicl e53) D1:信息收集;8D54) D2:建立8D小组;55) D3:制定临时的围堵行动措施,避免不良品流出;56) D4:定义和证实根本原因,避免再发;57) D5:根据基本原因制定永久措施;58) D6:执行和确认永久措施;59) D7:预防再发,实施永久措施;60) D8:认可团队和个人的贡献。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五章 多模块程序设计(忽略) P - 182 第六章 微处理器8086的总线结构和时序 P – 216 6.1 8086系统总线结构 P217 微处理器8086引脚如图6.1 P2178086具有两种各种模式:最大工作模式和最小工作模式,由引脚MX MN /选择。

6.1.1 两种工作方式公用引脚定义 1. 地址∕数据总线AD 15—AD 0 :输入∕输出,三态;时分复用,在总线周期的1T 状态作为地址 线15A —0A 输出,在其他状态作数据线15D —0D (双向)。

619S A ,518S A ,417S A ,316S A :输出,三态;时分复用,在总线周期的1T 状表6.1 S 4 S 3的功能(P218) 态作为地址线19A —16A 输出,其他状态为状态 线,06=S ,IF S =5当前值;4S ,3S 用来指示当前使用的段寄存器。

GND AD 14AD 13AD 12AD 11AD 10AD 09AD 08AD 07AD 06AD 05AD 04AD 03AD 02AD 01AD 00MNI INTR CLKGND VCCAD 15AD 16/S 3AD 17/S 4AD 18/S 5AD 19/S 6BHE /S 7MN / MXRD HOLD HLDA WR M / OI D T/R DEN ALE INTA TEST READY RESET RQ /GT 0RQ /GT 1LOCK S 2S 1S 0QS 0QS 1(((((((())))))))图 6.1 8086引脚图 P217最大工作模式最小工作模式2. 控制总线1)MX MN /:工作模式选择,输入。

1 — CPU 处于最小工作模式;0 — CPU处于最小工作模式。

2)RD :输出,三态。

读信号,低有效,有效时表示CPU 正在执行从存储器或 I/O 口输入数据。

3)NMI :非屏蔽中断请求输入,上升沿有效。

当该引脚输入一个有效沿时,CPU在执行完现行指令后,立即进行非屏蔽中断请求处理(不受IF 影响)。

4)INTR :可屏蔽中断请求输入,高电平有效。

有效时表示外部有INTR 请求。

CPU在每条指令的最后状态对INTR 进行测试,如有效且IF=1,则在现行指令完成后响应INTR 请求。

5)RESET :CPU 复位(启动)信号输入,高电平有效,至少保持四个时钟周期。

有效时,IP ,DS ,ES ,SS ,标志寄存器和指令队列寄存器被清0,置CS 为FFFFH ,启动后(RESET 变低),CPU 从FFFFH:0000H 执行程序。

6)READY :准备就绪信号输入,来自存储器或I/O 接口的应答信号,高有效。

CPU在总线周期的T 3状态的开始测试READY ,当READY 有效时,表示存储器或I/O 接口准备就绪,将在下一个状态完成数据交换;否则CPU 自动插入一个(或几个,硬件电路决定)等待状态(T W ),并在等待状态T W 开始测试READY ,直到READY 有效为止。

7)TEST :测试信号输入,低有效。

在CPU 执行WAIT 指令时,每隔5个时钟周期对TEST 进行一次测试,如有效则脱离WAIT 状态,执行下一条指令。

8)7/S BHE :输出,三态。

在总线周期的T 1状态输出BHE ,低有效,表示使用高八位数据线;在总线周期的其他状态输出S 7,暂无定义。

表6.2 BHE 和0A 的不同组合状态 P2196.1.2 最小方式下引脚定义和系统总线构成 P219 1/ MX MN (接到+5V ),CPU 工作于最小工作方式。

为单处理器系统,但也允许其他的主控设备(DMA 控制器)占用总线。

1)INTA :中断响应信号(对INTR ),输出。

是CPU 响应INTR 请求时发向中断控制器的响应信号:在相邻的二个总线周期输出两个负脉冲(第一个为响应;第二个驱动中断控制器释放中断类型号n )。

2)ALE :地址锁存允许信号,输出,高有效,用于地址锁存。

3)DEN :数据允许信号,输出,低有效,表示CPU 准备好接收或发送数据,一般接到数据总线双向驱动器的允许端。

4)R DT /:数据收发信号,输出。

1 — CPU 处于发送数据状态;0 — CPU 处于接收数据状态。

一般接到数据总线双向驱动器的传送方向控制端。

5)IO M /:输出,三态。

1 — CPU 访问的是存储器;0 — CPU 访问的I/O 口。

6)WR :输出,三态。

写信号,低有效,有效时表示CPU 正在执行写存储器或 I/O 口操作(输出数据)。

7)HOLD :总线请求输入,高有效。

系统中其他总线控制设备向CPU 申请总线使用权。

8)HLDA :总线请求响应信号,输出,高有效。

是对HOLD 的响应信号,此时CPU已放弃总线的管理权。

表6.3 IO M /、RD 和WR 组合决定的传送类型0系统总线结构1) 地址锁存器8282 (74LS373、74LS573)7DI —0DI :数据输入端;7DO —0DO :数据输出端; STB :选通输入,高有效;OE :输出允许端。

注意:STB 为电位型,透明的具有三态输出的锁存器。

相类似器件74LS373、74LS573,引脚位置有差异。

DI 0DI 1DI 2DI 3DI 4DI 5DI 6DI 7OE 01234567图6.3(a )8282 P2212)双向数据收法器8286 P2217A —0A :数据输入输出;7B —0B :数据输入输出 OE :输出允许端。

T = 0 A ← B T :传输方向控制; T = 0 A → B3)时钟控制电路 8284 P223① C F /:0选择内部震荡电路;1选择外部时钟输入; 输出CLK 为3分频。

② 复位电路:完成整形、反相, 及与CLK 同步。

③ READY 信号与CLK 同步。

4) 8086最小方式系统的系统总线构成A 0A 1A 2A 3A 4A 5A 6A 7OE TB 0B 1B 2B 3B 4B 5B 7图6.4(b )8282 P221B 6系统总线图 6.2 8086最小方式的系统总线结构 P220图6.5 典型的 8284时钟电路 P2216.1.3 最大方式下引脚定义和系统总线构成 P223 1/ MX MN (接到0V ),CPU 工作于最大工作方式。

为多处理器系统,除DMA 控制器外,还了配协处理器占用总线(8087可 执行指令。

1)1QS 、0QS :指令队列状态输出。

表6.5 指令队列状态位的输出 P2242)2S 、1S 、0S :(输出,三态)状态输出,由8288产生所需的控制信号。

● CEN :片允许信号,高有效(系统有二片)。

● AEN :支持多总线结构,输入,低有效, (与仲裁器8289相连)。

● IOB :BOI=1时仅产生端口控制信号及INTA 。

● PDEN MCE /:产生中断响应信号相应的 同步信号(IOB=0时)。

注意:/MRDC :存储器读 /MWTC :存储器写 /IORC :端口读 /IOWC :端口写/AMWC :先行存储器写 /AIOWC :先行端口写其他:DEN :数据允许信号,与最小模式极性相反;R DT /、ALE 、INTA 与最小模式相同。

图6.7 8288逻辑符号 P226/MRDC /MWTC /IORC /IOWC /AMWC /AIOWC /INTA D T/ R DEN ALE/S 2/S 1/S 0/AEN CEN IOB MCE/ PDENGNDVCC3)LOCK :总线锁定信号,低有效。

该信号由指令前缀LOCK 使其有效,不允许其他设备使用总线,直到下一条指令执行完成为止;在INTR 的响应周期也有效。

4)1/GT RQ 和0/GT RQ :双向(输入/输出),用于输入总线请求和输出总线授 权信号。

8086最大方式下系统总线构成如图6.6 P225 注意:● 在最大工作方式下:/MRDC :存储器读/MWTC :存储器写 /IORC :端口读 /IOWC :端口写● 在最小工作方式下:WR 、RD 和IO M /;可逻辑合成以上信号。

●重点掌握最下方式总线结构。

6.2 8086系统总线时序 P227注意:研究总线信号之间的时间关系,是计算机接口技术的基础。

● 8086的时钟频率为5M ,时钟周期为200微秒;● CPU 每执行一条指令至少要通过总线访问存储器一次(取指); ● 一个总线周期至少由四个时钟周期构成(无等待); ● 每个时钟周期称为一个状态。

● 典型的总线周期时序如下:T 1T 2T 3T W T 4T 1T 2T 3T 4T 1T 1T 1T 2T 3T W T W T 4总线周期等待状态图 6.9 典型的总线周期时序 P2286.2.1 最小方式系统总线周期时序 P2281. 读总线周期和写总线周期 ① 读总线周期② 写总线周期注意:① T 1开始输出地址019A A 和BHE ,T 2开始用作状态线和数据线;② T 1开始使IO M /、R DT /、ALE 有效;③ 在ALE 的下降沿锁存地址和/BHE (T 1上升沿锁存);④ T 3的上升沿测试READY ,如有效,则T 4结束;否则插入T W 再测试。

状态输出地址 /BHE 输出A 19/S 6—A 16/S 3/BHECLK AD 16 —AD 0地址输出数据输入(来自M 或IO )ALE M/ IORD D T/ R DEN 图 6.10 (a) 总线读周期 P229状态输出地址 /BHE 输出A 19/S 6—A 16/S 3/BHECLKAD 16 —AD 0地址输出CPU 数据输出ALE M/ IO 低为IO 读 高为存储器读WR D T/ R DEN图 6.10 (b) 总线写周期 P229( RD )( RD=1 )2. 中断响应周期注意:CPU 在执行正常程序时,INTR 有效,且IF=1,则在现行指令执行完成后进入中断响应周期,在中断响应周期的第一个总线周期发出第一个INTA 信号,告诉中断管理器CPU 已响应中断;在中断响应周期的第二个总线周 期发出第二个INTA 信号,中断管理器释放中断类型号(n ),CPU 则读取 中断类型号(n )。

3. 总线请求和总线授予时序注意:如CPU 在4T 之前或1T 期间收到一个HOLD 请求,则在1T 的下降沿放弃总线的管理且使HLDA 有效(为高),将总线的控制权授予提出总线请求的主 控设备,知道该设备撤消总线请求为止;此后,CPU 在每个状态的上升沿 测试HOLD 信号,如无效,则使HLDA 信号无效(延迟1~2状态使HLDA 信 号为低),CPU 接管总线,继续执行程序。