白金PC电源技术分析

CM6901 LLC 金牌PC电源

GENERAL DESCRIPTION FEATURESCM6502THH is designed to meet 90+ spec. (total efficiency). It has the following key features.1.) 420V bulk capacitor value can be reduced, and alsoPFC Boost Capacitor ripple current can be reduced2.) Turbo Speed PFC may reduce 420 Bulk Capacitorsize further3.) A PGB function is designed for interfacing to nextstage controller or the House Keeping IC atsecondary side. It has a customer programmablelow threshold PGTHL4.) “Remember it was Light Load” function and“Remember it was Full Load” function may reducePFC 420V Bulk Capacitor size further. It boosts thetotal efficiency as well.5.) No Load Consumption can be reduced to 290mW at270VAC6.) Better Power Factor and Better THD7.) Clean Digital PFC Brown Out8.) The stress over the entire external power device isreduced and EMI noise reduced9.) Superior Surge Noise ImmunityCM6502THH is designed to meet the EPA/90+ regulation. With the proper design, its efficiency of power supply can easily approach 90+. Patents Pending23V Bi-CMOS process.Designed for EPA/90+efficiencySelectable Boost output from 380V to 355V during light loadCustomer Programmable the Low Threshold of PGB comparator at PGTHL pin“Remember It was Light Load” function to improve the efficiency“Remember It was Light Load” function to have extra hold-up time @ light loadClean Digital PFC Brown OutAll high voltage resistors can be greater than 5 Mega ohm (5 Mega to 8 Mega ohm) to improve the no load consumption.Rail to rail CMOS Drivers with on, 60 ohm and off, 30 ohm with 17V zeners.Fast Start-UP Circuit without extra bleed resistor to aid VCC reaches 13V sooner.Low start-up current (50uA typ.)Low operating current (2.1mA typ.)Adjustable Long Delay Time for Line Sagging(Up to 2 Second)16.5V VCC shunt regulatorDynamic Soft PFC to ease the stress of the Power Device and Ease the EMI-filter design.Better Power Factor and Better THDAverage current, continuous or discontinuous boost leading edge PFC.Current fed Gain Modulator for improved noise immunity. Gain Modulator is a constant maximum power limiter.Precision Current Limit, over-voltage protection, UVLO, and soft start, and Reference OK.APPLICATIONS PIN CONFIGURATIONEPA/90+ related Power Supply Desktop PC Power Supply Internet Server Power Supply LCD Power Supply PDP Power Supply AC Adaptor IPC Power Supply UPSBattery Charger DC Motor Power Supply Monitor Power SupplyTelecom System Power Supply Distributed PowerDIP-14 (P14) / SOP-14 (S14)TOP View9PGTHL 13IEAO ISS VREF VFB VEAO 12810PFCOUT11VCC RTCTISENSE 21674VRMS 3PGB GND5IAC 14PIN DESCRIPTIONOperating Voltage Pin No.SymbolDescriptionMin. Typ. Max.Unit 1 I EAOPFC transconductance current error amplifier output (Gmi).0 VREFV2 I AC IAC has 2 functions:1. PFC gain modulator reference input.2. At start up, IAC is connected to VCC and it helps to reduce the startup time and it helps to reduce the no load consumption. Typical RAC resistor is about 6 Mega ohm to 8 Mega ohm to sense the line.0 100 uA3 I SENSE PFC Current Sense: for both Gain Modulator and PFC ILIMIT comparator.-1.3 0.7 V 4V RMSLine Input Sense pin for multiplier and also it is the PFC Brown out sense pin.0 6 V5 ISSPFC Soft Start pin: It supplies ~ 10uA to SS pin. It provides a close-loop soft start function during power supply start up. When VFB is lower than PGTHL, PGBcomparator, SS pin is discharged through an internal ~ 145.3K Ohm resistor.PFC Soft Start function can just need a simple capacitor0 VCC V6 PGTHL PGTHL is an input I/O. The user can program the LowThreshold of the Power Good which can determine thecomparator output of PGB (open drain) to be pulled high.0 2.25 V7 RTCT Oscillator timing node; timing set by RT and CT 0.8 4 V 8 GND Ground9 PGB PGB is the PG comparator output. The input of PG comparator is using Vfb (pin 13) to compare with the high threshold, 2.25V (preset internally) and the low threshold, PGTHL (pin 6, Set by user).When 380V is ready, pin 9 is open-drain and it will be pulled low.0 6 V10 PFC OUT PFC driver output 0 VCC V 11 V CCPositive supply for CM6502THH10 15 18 V12 VREFMaximum 3.5mA buffered output for the internal 7.5V reference when VCC=14V7.5 V13 V FBPFC transconductance voltage error amplifier input0 2.5 3 V14 VEAO PFC transconductance voltage error amplifier output(GmV)0 6 VSimplified Block Diagram (CM6502THH)ORDERING INFORMATIONPart Number Temperature Range PackageCM6502THHXIS* -40℃ to 125℃14-Pin Narrow SOP (S14)CM6502THHXISTR* -40℃ to 125℃14-Pin Narrow SOP (S14)CM6502THHXIP* -40℃ to 125℃14-Pin Narrow DIP (P14)*Note: X : Suffix for Halogen Free and PB Free ProductTR : Package is Typing ReelABSOLUTE MAXIMUM RATINGSAbsolute Maximum ratings are those values beyond which the device could be permanently damaged.Parameter Min.Max.UnitsV CC18V IEAO 0VREF+0.3V I SENSE Voltage -5 0.7 VPFC OUT GND – 0.3 VCC + 0.3 VI REF 3.5mAI AC Input Current 1 mAPeak PFC OUT Current, Source or Sink 0.5 APFC OUT, Energy Per Cycle 1.5 μJJunction Temperature 150 ℃Storage Temperature Range -65 150 ℃Operating Temperature Range -40 125 ℃Lead Temperature (Soldering, 10 sec) 260 ℃Thermal Resistance (θJA)Plastic DIP Plastic SOIC 80105℃/W℃/WELECTRICAL CHARACTERISTICS:Unless otherwise stated, these specifications apply Vcc=+14V, PGTHL=+2.0V, R T = 5.88K k Ω, C T = 1000pF, T A =Operating Temperature Range (Note 1)CM6502THHSymbol ParameterTest ConditionsMin. Typ. Max.UnitClean Digital PFC Brown Out VRMS Threshold High Room Temperature=25℃ 1.70 1.78 1.88 VVRMS Threshold LowRoom Temperature=25℃ 0.98 1.03 1.1VHystersis 710 760 810 mVAC High/Low line ThresholdSweep Vrms pin3.3253.53.675VVoltage Error Amplifier (g mv )Input Voltage Range0 3 VTransconductance V NONINV = V INV , VEAO = 2.25V @ T=25℃35 50 65μmhoFeedback Reference Voltage (High)SS > VREF and Veao > 2.25V and Vrms<2V2.45 2.52 2.58 VFeedback Reference Voltage (Low)SS > VREF and Veao < 1.75V and Vrms<2V 2.17 2.26 2.35 V Input Bias Current Note 2 -0.1 -0.05 μAOutput High Voltage 5.8 6.0 VOutput Low Voltage0.10.4VSource Current Overdrive Voltage = 100mV @ T=25℃ 1 7μA Sink Current Overdrive Voltage = 100mV @ T=25℃ -55 -28μA Open Loop GainDC gain30 40 dBPower Supply Rejection Ratio11V < V CC < 16.5V6075dBCurrent Error Amplifier (g mi )Input Voltage Range (Isense pin)-1.2 0.7 VTransconductance V NONINV = V INV , IEAO = 1.5V @ T=25℃ 50 67 85μmho Input Offset Voltage VEAO=0V, IAC is open -1010mVOutput High Voltage 6.8 7.3 7.8 VOutput Low Voltage0.1 0.4 VELECTRICAL CHARACTERISTICS :(Unless otherwise stated, these specifications apply Vcc=+14V, PGTHL=+2.0V, R T = 5.88K kΩ, C T = 1000pF,T A=Operating Temperature Range (Note 1)CM6502THHSymbol Parameter TestConditionsMin. Typ. Max.Unit SinkCurrent I SENSE = -0.5V, IEAO = 1.5V -40 -34 -28μA SourceCurrent I SENSE = +0.5V, IEAO = 4.0V 25 33 40μA Open Loop Gain DC Gain 30 40 dBPower Supply Rejection Ratio 11V < V CC < 16.5V 60 75 dBPFC OVP ComparatorThresholdVoltage 2.7 2.85 3 V Hysteresis 200 320 mV PFC Green Power Detect ComparatorVeao Threshold Voltage 0.14 0.28 0.4 VTri-Fault DetectFault Detect HIGH 2.7 2.85 3 VTime to Fault Detect HIGH V FB=V FAULT DETECT LOW toV FB=OPEN, 470pF from V FB to GND2 4 msFault Detect LOW 0.1 0.28 0.4 VPFC I LIMIT ComparatorThresholdVoltage -1.38 -1.28 -1.18 V(PFCI LIMIT– Gain Modulator Output) 300450mVDelay to Output (Note 4) Overdrive Voltage = -100mV 700 nsPGTHLPGB_CMP_HIGH PGTHL=2V 2.14 2.25 2.36 V PGB_CMP_LOW PGTHL=2V 1.88 2.07 V Hystersis 100 350 mV Offset -3535mV Remember Full-Load Threshold 1.94 2.02 VRemember Light-Load Threshold 1.82 1.9 VELECTRICAL CHARACTERISTICS:Unless otherwise stated, these specifications apply Vcc=+14V, PGTHL=+2.0V, R T = 5.88K kΩ, C T = 1000pF, T A=Operating Temperature Range (Note 1)CM6502THHSymbol Parameter TestConditionsMin. Typ. Max.Unit GAIN ModulatorGain1 (Note 3) I AC = 20μA, V RMS =1.125, V FB = 2.375V @T=25℃ SS<VREF4.45.56.6Gain2 (Note 3 ) I AC = 20μA, V RMS = 1.45588V, V FB=2.375V @ T=25℃ SS<VREF4 5 6Gain3 (Note 3) I AC = 20μA, V RMS =2.91V, V FB = 2.375V @T=25℃ SS<VREF0.88 1.1 1.32Gain4 (Note 3) I AC = 20μA, V RMS = 3.44V, V FB = 2.375V@ T=25℃ SS<VREF0.72 0.9 1.08Bandwidth (Note 4) I AC = 40μA 1 MHzOutput Voltage = Rmul * (I SENSE-I OFFSET) I AC = 50μA, V RMS = 1.125V, V FB = 2.375VSS<VREF0.75 0.8 0.85 VOscillator (Measuring fpfc)Initial fpfc Accuracy 1 R T = 5.88 kΩ, C T = 1000pF, T A = 25℃IAC=0uA64 68 72 kHzVoltage Stability 11V < V CC < 16.5V 2 %TemperatureStability 2 % Ramp Valley to Peak Voltage VEAO=6V and IAC=20uA 2.5 VPFC Dead Time (Note 4) 550 950 nsCT Discharge Current V RAMP2 = 0V, V RAMP1 = 2.5V 10 11 12 mALight Load Veao ThresholdLight Load Threshold (High) Room Temperature=25℃ 2.38 2.5 2.62 VLight Load Threshold (Low) Room Temperature=25℃ 1.9 2 2.1 VHysteresis 400 500 600 mVELECTRICAL CHARACTERISTICSUnless otherwise stated, these specifications apply Vcc=+14V, PGTHL=+2.0V, R T = 5.88K kΩ, C T = 1000pF,T A=Operating Temperature Range (Note 1)CM6502THHUnitSymbol Parameter Test ConditionsMin. Typ. Max.ReferenceVoltage T A = 25℃, I(VREF) = 0mA 7.3 7.5 7.7 V OutputRegulation 11V < V CC < 16.5V@ T=25℃ 3 5 mV LineVCC=10.5V,0mA < I(VREF) < 2.0mA;25 50 mV@ T=25℃Load RegulationVCC=14V,0mA < I(VREF) < 3.5mA;25 50 mVT A = -40℃~85℃Stability 0.4 % TemperatureTotal Variation Line, Load, Temp 7.3 7.7 VmV Long Term Stability T J = 125℃, 1000HRs 5 25PFCMinimum Duty Cycle IEAO > 4.5V 0 %Maximum Duty Cycle V IEAO < 1.2V 93 95 %I OUT = -20mA @ T=25℃ 11.8 18 ohmI OUT = -100mA @ T=25℃18Output Low RdsonohmI OUT = 10mA, V CC = 9V @ T=25℃ 0.5 1 VI OUT = 20mA @ T=25℃ 24 40 ohmOutput High RdsonI OUT = 100mA @ T=25℃40ohm Rise/Fall Time (Note 4) C L = 100pF @ T=25℃ 50 ns Soft StartμA Soft Start Current Room Temperature=25℃7 10 12μA Soft Start Discharge Current Vrms=0.926V, Soft Start=8V 1 3.5SupplyμA Start-UpCurrent V CC = 12V, C L = 0 @ T=25℃ 50 65 Operating Current 14V, C L = 0 2.35 3.5 mATurn-On Undervoltage Lockout Threshold CM6502THH 12.35 12.85 13.65 VTurn-Off Undervoltage Lockout Hysteresis CM6502THH 2.8 2.95 3.1 V Shunt Regulator (VCC zener)Zener Threshold Voltage Apply VCC with Iop=20mA 16.15 17 17.85 VNote 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.Note 2: Includes all bias currents to other circuits connected to the V FB pin.Note 3: Gain ~ K x 5.3V; K = (I SENSE – I OFFSET) x [I AC (VEAO – 0.7)]-1; VEAO MAX = 6VNote 4: Guaranteed by design, not 100% production test.Getting Start:To start evaluating CM6502THH from the exiting CM6800 or ML4800 board, 6 things need to be taken care before doing the fine tune:1.) Change RAC resistor (on pin 2, IAC) from the old valueto a higher resistor value between 6 Mega ohms to 8 Mega ohms. Start with 6 Mega ohm first.2.) Change RTCT pin (pin 7) from the existing value toRT=5.88K ohm and CT=1000pF to have fpfc=68Khz, fRTCT=272Khz for CM6502THH.3.) Adjust all high voltage resistor around 5 mega ohm orhigher.4.) VRMS pin (pin 4) needs to be 1.1V at VIN=80Vac rightbefore PFC brown out and to be 1.70V at VIN=85VAC right before PFC brown in for universal input application for line input from 85VAC to 270VAC.5.)At full load, the average Veao needs to be around 4.5Vand the ripple on the Veao needs to be less than 250mV when the light load comparator are triggered.6.) Soft Start pin (pin 5), the soft start current has beenreduced from CM6800’s 20uA to CM6502THH’s 10uA.Soft Start capacitor can be reduced to 1/2 from your original CM6800 capacitor.Functional DescriptionCM6502THH is designed for high efficient power supply for both full load and light load. It is a ZVS-Like PFC supply controller.The CM6502THH is an average current controlled, continuous/discontinuous boost Power Factor Correction (PFC) which uses leading edge modulation.In addition to power factor correction, a number of protection features have been built into the CM6502THH. These include soft-start, PFC over-voltage protection, peak current limiting, brownout protection, duty cycle limiting, and under-voltage lockout. Power Factor CorrectionPower factor correction makes a nonlinear load look like a resistive load to the AC line. For a resistor, the current drawn from the line is in phase with and proportional to the line voltage, so the power factor is unity (one). A common class of nonlinear load is the input of most power supplies, which use a bridge rectifier and capacitive input filter fed from the line. The peak-charging effect, which occurs on the input filter capacitor in these supplies, causes brief high-amplitude pulses of current to flow from the power line, rather than a sinusoidal current in phase with the line voltage. Such supplies present a power factor to the line of less than one (i.e. they cause significant current harmonics of the power line frequency to appear at their input). If the input current drawn by such a supply (or any other nonlinear load) can be made to follow the input voltage in instantaneous amplitude, it will appear resistive to the AC line and a unity power factor will be achieved.To hold the input current draw of a device drawing power from the AC line in phase with and proportional to the input voltage, a way must be found to prevent that device from loading the line except in proportion to the instantaneous line voltage. The PFC section of the CM6502THH uses a boost-mode DC-DC converter to accomplish this. The input to the converter is the full wave rectified AC line voltage. No bulk filtering is applied following the bridge rectifier, so the input voltage to the boost converter ranges (at twice line frequency) from zero volts to the peak value of the AC input and back to zero. By forcing the boost converter to meet two simultaneous conditions, it is possible to ensure that the current drawn from the power line is proportional to the input line voltage. One of these conditions is that the output voltage of the boost converter must be set higher than the peak value of the line voltage. A commonly used value is 385VDC, to allow for a high line of 270VAC rms. The other condition is that the current drawn from the line at any given instant must be proportional to the line voltage. Establishing a suitable voltage control loop for the converter, which in turn drives a current error amplifier and switching output driver satisfies the first of these requirements. The second requirement is met by using the rectified AC line voltage to modulate the output of the voltage control loop. Such modulation causes the current error amplifier to command a power stage current that varies directly with the input voltage. In order to prevent ripple, which will necessarily appear at the output of boost circuit (typically about 10VAC on a 385V DC level); from introducing distortion back through the voltage error amplifier, the bandwidth of the voltage loop is deliberately kept low. A final refinement is to adjust the overall gain of the PFC such to be proportional to 1/(Vin x Vin), which linearizes the transfer function of the system as the AC input to voltage varies.Since the boost converter topology in the CM6502THH PFC isof the current-averaging type, no slope compensation is required. More exactly, the output current of the gain modulator is given by:Gain=Imul/IacK=Gain/(VEAO-0.7V)I mul = K x (VEAO – 0.7V) x I ACDynamic Soft PFC (patent pending)Dynamic Soft PFC is one of the main feature of CM6502THH. Dynamic Soft PFC is to improve the efficiency, to reduce power device stress, to ease EMI, and to ease the monotonic output design while it has the more protection such as the short circuit with power-foldback protection. Its unique sequential control maximizes the performance and the protections among steady state, transient and the power on/off conditions.PFC Section: Gain ModulatorFigure 1 shows a block diagram of the PFC section of the CM6502THH. The gain modulator is the heart of the PFC, as it is this circuit block which controls the response of the current loop to line voltage waveform and frequency, rms line voltage, and PFC output voltages. There are three inputs to the gain modulator. These are:1. A current representing the instantaneous input voltage (amplitude and wave-shape) to the PFC. The rectified AC input sine wave is converted to a proportional current via a resistor and is then fed into the gain modulator at I AC . Sampling current in this way minimizes ground noise, as is required in high power switching power conversion environments. The gain modulator responds linearly to this current.2. A voltage proportional to the long-term RMS AC line voltage, derived from the rectified line voltage after scaling and filtering. This signal is presented to the gain modulator at VRMS. The gain modulator’s output isinversely proportional to V RMS 2. The relationship between V RMS and gain is illustrated in the Typical Performance Characteristics of this page.3. The output of the voltage error amplifier, VEAO. The gainmodulator responds linearly to variations in this voltage.The output of the gain modulator is a current signal, in theform of a full wave rectified sinusoid at twice the line frequency. This current is applied to the virtual-ground (negative) input of the current error amplifier. In this way the gain modulator forms the reference for the current error loop, and ultimately controls the instantaneous current draw of the PFC from the power line. The general formula of the output of the gain modulator is:I mul =2RMSAC V 0.7V)-VEAO I (×x constant(1)Where K is in units of [V -1]Note that the output current of the gain modulator is limited around 140μA and the maximum output voltage of the gain modulator is limited to 140uA x 5.7K=0.8V. This 0.8V also will determine the maximum input power.However, I GAINMOD cannot be measured directly from I SENSE . I SENSE = I GAINMOD -I OFFSET and I OFFSET can only be measured when VEAO is less than 0.5V and I GAINMOD is 0A. Typical I OFFSET is around 25uA.IAC=20uA, Veao=6V Gain vs. VRMS (pin4) When VRMS below 1V, the PFC is shut off. Designer needs to design 80VAC with VRMS average voltage= 1.14V.AC MUL AC OFFSET SENSE I I I I I =−=GainSelecting R AC for IAC pin IAC pin is the input of the gain modulator. IAC also is a current mirror input and it requires current input. By selecting a proper resistor R AC , it will provide a good sine wave current derived from the line voltage and it also helps program the maximum input power and minimum input line voltage.R AC =Vin min peak x 50K. For example, if the minimum line voltage is 85VAC, the R AC =85 x 1.414 x 50K = 6.0 Mega ohm.Vrms Description:VRMS pin is designed for the following functions:1. VRMS is used to detect the AC Brown Out (Also, wecan call it Clean Digital PFC brown out.). When VRMS is less than 1.03 V +/-5%, PFCOUT will be turned off and VEAO will be softly discharged. When VRMS is greater than 1.78V +/-5%, PFCOUT is enabled and VEAO is released.Current Error Amplifier, IEAO The current error amplifier’s output controls the PFC duty cycle to keep the average current through the boost inductora linear function of the line voltage. At the inverting input tothe current error amplifier, the output current of the gain modulator is summed with a current which results from anegative voltage being impressed upon the I SENSE pin. The negative voltage on I SENSE represents the sum of all currents flowing in the PFC circuit, and is typically derived from a current sense resistor in series with the negative terminal of the input bridge rectifier.In higher power applications, two current transformers aresometimes used, one to monitor the IF of the boost diode. As stated above, the inverting input of the current error amplifier is a virtual ground. Given this fact, and the arrangement of the duty cycle modulator polarities internal to the PFC, an increase in positive current from the gain modulator will cause the output stage to increase its dutycycle until the voltage on I SENSE is adequately negative to cancel this increased current. Similarly, if the gainmodulator’s output decreases, the output duty cycle willdecrease, to achieve a less negative voltage on the I SENSEpin.Error Amplifier CompensationThe PWM loading of the PFC can be modeled as anegative resistor; an increase in input voltage to the PWMcauses a decrease in the input current. This response dictates the proper compensation of the two transconductance error amplifiers. Figure 2 shows the types of compensation networks most commonly used for the voltage and current error amplifiers, along with their respective return points. The current loop compensation is returned to V REF to produce a soft-start characteristic on the PFC: as the reference voltage comes up from zero volts, it creates a differentiated voltage on I EAO which prevents the PFC from immediately demanding a full duty cycle on its boost converter.Clean Digital PFC Brown OutClean Digital PFC Brown Out provides a clean cut off when AC input is much lower than regular AC input voltage such as 67Vac. Inside of Clean Digital PFC Brown Out, there is a comparator monitors the Vrms (pin 4) voltage. Clean Digital PFC Brown Out inhibits the PFC and Veao (PFC error amplifier output) is pulled down when the Vrms is lower than off threshold, 1.04V (The off Vin voltage usually corresponds to 70Vac). When the Vrms voltage reaches 1.75V (The On Vin voltage usually corresponds to 86.62V and when Vin = 80Vac, Vrms = 1.14V), PFC is on. Before PFC is turned on, Vrms (pin 4) represents the peak voltage of the AC input. Before PFC is turned off, Vrms (pin 4)represents the Vrms voltage of the AC input.Cycle-By-Cycle Current Limiter andSelecting R SENSE The I SENSE pin, as well as being a part of the current feedbackloop, is a direct input to the cycle-by-cycle current limiter for the PFC section. Should the input voltage at this pin ever be more negative than –1.25V, the output of the PFC will be disabled until the protection flip-flop is reset by the clock pulse at the start of thenext PFC power cycle.R S is the sensing resistor of the PFC boost converter. During the steady state, line input current x R SENSE = I mul x 5.7K. Sincethe maximum output voltage of the gain modulator is I mul max x5.7K= 0.8V during the steady state, RSENSE x line input current willbe limited below 0.8V as well. When VEAO reaches maximum VEAO which is 6V, Isense can reach 0.8V. At 100% load, VEAO should be around 4.5V and ISENSE average peak is 0.6V. It will provide the optimal dynamic response + tolerance of thecomponents.Therefore, to choose R SENSE , we use the following equation: R SENSE + R Parasitic =0.6V x Vinpeak / (2 x Line Input power)For example, if the minimum input voltage is 80VAC, and the maximum input rms power is 200Watt, R SENSE + R Parasitic = (0.6V x 80V x 1.414) / (2 x 200) = 0.169 ohm. The designer needs to consider the parasitic resistance and the margin of the powersupply and dynamic response. Assume R Parasitic = 30 mOhm,R SENSE = 139 mOhm.PFC OVP In the CM6502THH, PFC OVP comparator serves to protect the power circuit from being subjected to excessive voltages if the load should suddenly change. A resistor divider from the high voltage DC output of the PFC is fed to VFB. When the voltage on VFB exceeds 2.79V, the PFC output driver is shut down. The PWM section will continue to operate. The OVP comparator has 250mV of hysteresis, and the PFC will not restart until the voltage at VFB drops below 2.54V. The VFB power components and the CM6502THH are within their safe operating voltages, but not so low as to interfere with the boost voltage regulation loop.PFC Voltage LoopThere are two major concerns when compensating the voltage loop error amplifier, V EAO ; stability and transientresponse. Optimizing interaction between transient response and stability requires that the error amplifier’s open-loop crossover frequency should be 1/2 that of the line frequency, or 23Hz for a 47Hz line (lowest anticipated international power frequency).deviate from its 2.5V (nominal) value. If this happens, the transconductance of the voltage error amplifier, GMv will increase significantly, as shown in the Typical Performance Characteristics. This raises the gain-bandwidth product of the voltage loop, resulting in a much more rapid voltage loop response to such perturbations than would occur with a conventional linear gain characteristics. The Voltage Loop Gain (S)CVV DC EAO 2OUTDC IN FBEAOOUT FB EAO OUT Z *GM *C *S *ΔV *V 2.5V*P ΔV ΔV *ΔV ΔV *ΔV ΔV ≈=Z CV : Compensation Net Work for the Voltage Loop GM v : Transconductance of VEAO P IN : Average PFC Input PowerV OUTDC : PFC Boost Output Voltage; typical designed value is 380V.C DC : PFC Boost Output CapacitorPFC Current LoopThe current transcondutance amplifier, GMi, I EAO compensation is similar to that of the voltage error amplifier, V EAO with exception of the choice of crossover frequency. The crossover frequency of thecurrent amplifier should be at least 10 times that ofthe voltage amplifier, to prevent interaction with the voltage loop. It should also be limited to less than 1/6th that of the switching frequency, e.g. 8.33kHz for a 50kHz switching frequency.The Current Loop Gain (S)CI I S OUTDC SENSE EAOEAO OFF OFFISENSE Z *GM *2.5V*L *S R *V ΔI ΔI *ΔI ΔD *ΔD ΔV ≈=Z CI : Compensation Net Work for the Current Loop GM I : Transconductance of IEAOV OUTDC :PFC Boost Output Voltage; typical designed value is 380V and we use the worst condition to calculate the Z CI R SENSE : The Sensing Resistor of the Boost Converter2.5V:The Amplitude of the PFC Leading Edge Modulation Ramp(typical)L: The Boost InductorThe gain vs. input voltage of the CM6502THH’s voltage error amplifier, V EAO has a specially shaped non-linearity such that under steady-state operating conditions the transconductance of the error amplifier, GMv is at a local minimum. Rapid perturbation in line or load conditions will cause the input to the voltage error amplifier (V FB ) toI SENSE Filter, the RC filter between R SENSE and I SENSE : There are 2 purposes to add a filter at I SENSE pin:1.) Protection: During start up or inrush current conditions, it will have a large voltage cross Rs which is the sensing resistor of the PFC boost converter. It requires the I SENSE Filter to attenuate the energy.2.) To reduce L, the Boost Inductor: The I SENSE Filter To reduceL, the Boost Inductor: The I SENSE Filter also can reduce the Boost Inductor value since the I SENSE Filter behaves like an integrator before going I SENSE which is the input of the current error amplifier, IEAO.The I SENSE Filter is a RC filter. The resistor value of the I SENSE Filter is 100 ohm because I OFFSET x the resistor can generate an offset voltage of IEAO. By selecting R FILTER equal to 100ohm will keep the offset of the IEAO less than 10mV. Usually, we design the pole of I SENSE Filter at fpfc/6=8.33Khz, one sixth of the PFC switching frequency. Therefore, the boost inductor can be reduced 6 times without disturbing the stability. Therefore, the capacitor of the I SENSE Filter, C FILTER , will be around 190.5nF.。

ApexgamingAG-750M电源详细测评!

Apexgaming AG-750M电源详细测评!说到Apexgaming这个品牌大家可能会比较陌生,实际上它是美商艾湃与台湾首利实业共同合作的品牌,公司总部位于美国加州,在2017年以Apexgaming名义正式登陆市场,主打的是电竞周边产品。

不过要说到最近Apexgaming最引人注目的事件,那毫无疑问就是其在PC电源领域中投下的一枚重磅炸弹,售价仅为人民币399元、可享受10年质保的80Plus金牌认证电源Apexgaming AG-750M,这款电源在玩家群中引起了广泛的讨论。

Apexgaming AG-750M电源简介Apexgaming AG-750M电源由台湾首利电子进行代工,基于主动式PFC+半桥LLC谐振+同步整流+DC to DC架构打造,采用全模组接口设计,额定功率为750W,通过了80Plus金牌认证。

这个规格在目前的PC电源领域中已经很常见了,但这款电源的市场售价只需要399元,而且还可以享受10年质保服务,这让其一下子成为了玩家群中的焦点。

Apexgaming AG-750M电源Apexgaming AG-750M电源长度为16cm,比起标准14cm长度的ATX电源要略长一点,不过这点长度对于机箱安装兼容性的影响很小,几乎可以忽略不计。

Apexgaming AG-750M电源采用单路+12V输出设计,最高电流为62A,相当于最高744W输出功率;+5V与+3.3V则通过DC to DC电路从+12V转换输出,最高电流均为25A,两路联合输出的额定功率为150W。

电源采用的是14cm直径的7扇叶散热风扇,常规温控方案,没有做低负载低温风扇停转的功能电源交流输出接口配置有独立开关Apexgaming AG-750M电源采用全模组线材设计,其中10pin+14pin的接口为24pin主供电接口模组线,3个8pin对应的是PCI-E显卡供电与CPU供电接口模组线,4个6pin接口则对应SATA供电与D型4pin接口的模组线。

白金机汇总

白金机汇总《白金机参数》设计小型变压器的计算公式:1、Ps=V2I2+V3I3......(瓦)式中Ps:输出总视在功率(V A)V2V3:二次侧各绕组电压有效值(V)I2I3:二次侧各绕组电流有效值(A)2、Ps1=Ps/η(瓦)式中Ps1:输入总视在功率(VA)η:变压器的效率,η总是小于1,对于功率为1KW以下的变压器η=0.8~0.9I1=Ps1/V1×(1.11.~2)(A)式中I1:输入电流(A)V1:一次输入电压有效值(V)(1.1~1.2):空载励磁电流大小的经验系数3、S=KO×根号Ps(CM²)式中S:铁芯截面积(CM²)Ps:输出功率(W)KO:经验系数、参看下表:Ps(W)0~10 10~50 50~500 500~1000 1000以上KO 2 2~1.75 1.5~1.4 1.4~1.2 1S=a×b(CM²)b′=b÷0.94、计算每个绕组的匝数:绕组感应电动势有效值E=4.44fwBmS×10ˉ4次方(V)设WO表示变压器每感应1伏电动势所需绕的匝数,即WO=W/E=10(4次方)/4.44FBmS(匝/V)不同硅钢片所允许的Bm值也不同,冷扎硅钢片D310取1.2~1.4特,热扎的硅钢片D41、D42取1~1.2特D43取1.1~1.2特。

一般电机用热轧硅钢片D21、D22取0.5~0.7特。

如硅钢片薄而脆Bm可取大些,厚而软的Bm可取小些。

一般Bm可取在1.7~1特之间。

由于一般工频f=50Hz,于是上式可以改为WO=45/BmS(匝/V)根据计算所得WO值×每绕组的电压,就可以算得每个绕组的匝数(W)W1=V1WO、W2=V2WO.......以此类推,其中二次侧的绕组应增加5%的匝数,以便补偿负载时的电压降。

5、计算绕组的导线直径D,先选取电流密度J,求出各绕组导线的截面积St=I/j(mm²)式中St:导线截面积(mm²)I:变压器各绕组电流的有效值(A)J:电流密度(A/mm²)上式中电流密度以便选用J=2~3安/mm²,变压器短时工作时可以取J=4~5A/mm²。

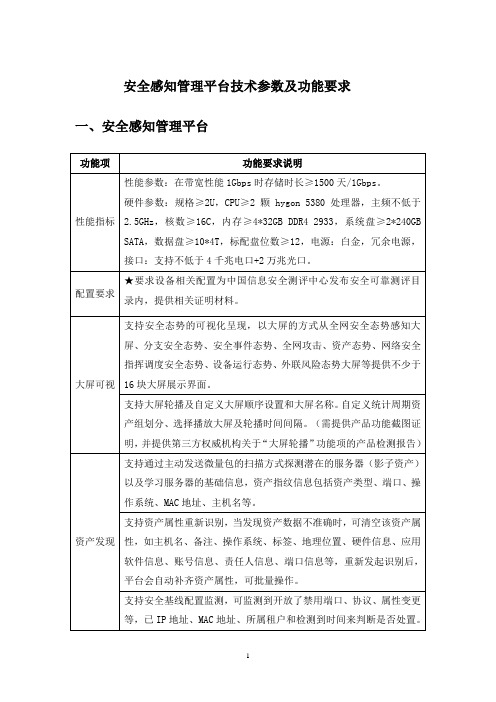

安全感知管理平台技术参数及功能要求

联动行为管理

支持联动原有行为管理设备,支持上网行为管理做资产用户名对接,精准识别终端资产责任人。(需提供截图打印加盖原厂公章证明)

★支持联动原有行为管理设备,支持与行为管理设备的联动,包含上网提醒、冻结账号等(需提供截图打印加盖原厂公章证明)

事后异常行为检测

具备元数据行为分析引擎:httpflow、dnsflow、adflow、icmpflow、maillflow等, 通过异常行为分析,结合各类机器学习算法完成未知威胁检测。包括:内网穿透、代理、远控、隧道、反弹shell等事后检测场景。

先进性

证明

为保障安全服务效果,满足数据和网络安全要求,所投态势感知平台产品厂商需通过可信云评估,提供相应的可信云认证报告

提供三年原厂质保及原厂免费现场服务,产品的安装、培训由原厂工程师完成实施。

二、

功能项

功能要求说明

性能规格

性能参数:网络层吞吐量≥1Gbps,应用层吞吐量≥500Mbps。

硬件参数:规格≥1U,内存大小≥8G,硬盘容量≥128G SSD,电源:单电源,接口:支持不低于6千兆电口+4千兆光口SFP。

配置要求

挖矿专项检测

支持挖矿专项检测页面,具备挖矿攻击事前、事中和事后全链路的检测分析能力,综合运用威胁情报、IPS特征规则和行为关联分析技术,如检测发现文件传输(上传下载)阶段的异常,对挖矿早期的准备动作即告警。

平台内置挖矿安全知识库,对常见的挖矿如:Bluehero挖矿蠕虫变种、虚拟货币挖矿、EnMiner挖矿病毒、PowerGhost挖矿病毒、DDG挖矿病毒、Docker挖矿、DDG挖矿变种、GroksterMiner挖矿病毒、Linux 挖矿木马、ZombieBoy挖矿木马等提供详细的背景介绍、感染现象、详细分析、相关IOC(MD5、C2、URL)、解决方案。

电源你不知道的事日系电容大起底

电源你不知道的事(1)日系电容大起底1日系电容:红宝石;NCC回顶部【PConline 杂谈】电源在DIY硬件中往往最容易被DIY玩家所忽视,其关注程度始终不及CPU或显卡如此耀眼。

对于CPU或显卡,DIY 玩家会关注其芯片组,频率或工艺多方面影响其性能的参数。

而对于电源,很多人只关注其额定功率与品牌这些表面很肤浅的东西,极少人会了解电源真正的“内心”。

电源你不知道的事是机电频道新出的系列文章,目的就是让网友对电源有更多的了解。

而今期作为第一期,我们首先来聊一下市面上究竟流行哪些主电容?各自有何优缺点?要想聊一下市面上的主电容究竟有哪些?就要先了解什么是主电容。

如上图,这个圆柱体就是电源的主电容。

其主要作用在于滤波作用,用来滤除高频和脉冲干扰,而主电容的容量直接影响电源的保持时间。

下面我们就看一下,现时市面上究竟有哪些主流的主电容。

日系电容——Rubycon(红宝石)日系电容Rubycon(红宝石)是日本最高电容质专业铝质电解电容电容器制造厂之一,拥有50年专业制造经验。

它与日本的同类名牌产品相比,具有高阻抗、低纹波、长寿命等特点,特别适用于可靠性、稳定性方面都要求较高的电子线路中。

所以如今很多中高端的电源产品都会见到此品牌电容的踪影,但由于其价格成本较台系或国产电容要高,所以一般在中低端电源不易看到。

在如今市面上多款电源中有哪些电源在用红宝石的电容呢?长城最新推出的极致火力全模组电源系列,游戏悍将的霸道5/6系列电源等这些都是采用日系电容Rubycon(红宝石)作为其强大的部件。

日系电容——NCC(Nippon Chemi-Con)NIPPONCHEMI-CON是日本三大电解电容器品牌之一。

日本贵弥功株式会社(以下简称为“日本贵弥功”,也被称为'嘉美工')自1931年创业以来,以开发铝电解电容器为出发点,并在这此基础上展开了各种电子元器件的开发工作。

目前在全球的市场占有率第一。

电脑电源80plus标准

电脑电源80plus标准随着科技的不断发展,电脑已经成为我们生活中不可或缺的一部分。

而电脑电源作为电脑的重要部件之一,对于电脑的稳定性和能效性有着至关重要的影响。

在选择电脑电源时,80PLUS认证标准成为了消费者们关注的焦点之一。

那么,什么是80PLUS标准?它又有着怎样的重要意义呢?80PLUS标准是由美国电力研究所(EPRI)和美国环保署(EPA)联合提出的一项电源能效认证标准。

该标准旨在鼓励电源供应商生产和销售更加高效的电源产品,以降低能源消耗和减少对环境的影响。

80PLUS标准通过对电源转换效率的测试和认证,将电源分为不同等级,包括白金、钛金、金和银四个等级。

这些等级分别对应着不同的能效要求,白金级别的电源能效最高,而银级别的电源能效较低。

80PLUS标准的实施,对于消费者、生产商和环境都有着积极的意义。

首先,对于消费者来说,选择80PLUS认证的电源产品可以有效降低电脑的能耗,减少用电成本。

其次,高效的电源可以减少电脑发热,延长硬件的使用寿命,提高电脑的稳定性。

对于生产商来说,遵循80PLUS标准可以促使其提高电源产品的能效,提升产品竞争力,同时也符合环保要求,有利于企业可持续发展。

对于环境来说,减少电源的能耗可以降低对环境的影响,减少温室气体的排放,有利于环境保护。

在实际购买电脑电源时,消费者应该如何根据80PLUS标准进行选择呢?首先,消费者可以根据自己的电脑配置和使用需求,选择对应的80PLUS等级。

一般来说,对于一般家用电脑,选择金级或银级的电源已经可以满足日常需求。

其次,消费者可以通过查看电源产品的能效认证标识,来判断产品是否符合80PLUS标准。

最后,消费者还可以通过查看产品的能效报告,了解产品在不同负载下的能效表现,选择更加符合自己需求的产品。

总的来说,80PLUS标准作为电源产品的能效认证标准,对于提高电源产品的能效、降低能耗、保护环境都有着积极的意义。

消费者在购买电脑电源时,应该根据自己的需求和80PLUS标准进行选择,以获得更好的使用体验和节能效果。

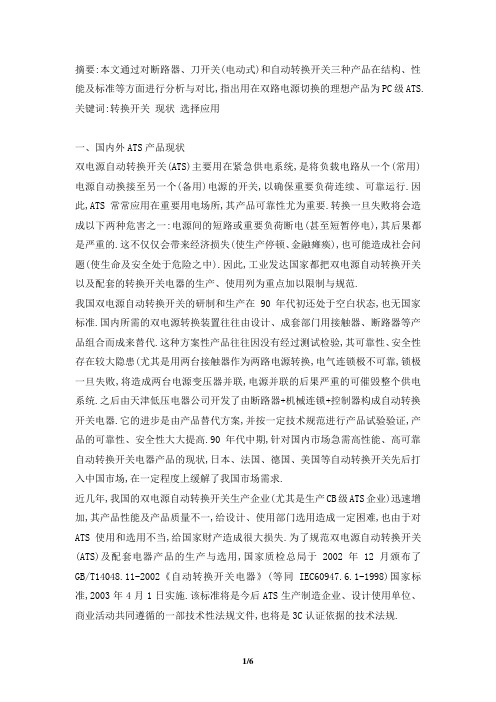

PC级ATS与CB级的区别及特点

摘要:本文通过对断路器、刀开关(电动式)和自动转换开关三种产品在结构、性能及标准等方面进行分析与对比,指出用在双路电源切换的理想产品为PC级ATS. 关键词:转换开关现状选择应用一、国内外ATS产品现状双电源自动转换开关(ATS)主要用在紧急供电系统,是将负载电路从一个(常用)电源自动换接至另一个(备用)电源的开关,以确保重要负荷连续、可靠运行.因此,ATS常常应用在重要用电场所,其产品可靠性尤为重要.转换一旦失败将会造成以下两种危害之一:电源间的短路或重要负荷断电(甚至短暂停电),其后果都是严重的.这不仅仅会带来经济损失(使生产停顿、金融瘫痪),也可能造成社会问题(使生命及安全处于危险之中).因此,工业发达国家都把双电源自动转换开关以及配套的转换开关电器的生产、使用列为重点加以限制与规范.我国双电源自动转换开关的研制和生产在90年代初还处于空白状态,也无国家标准.国内所需的双电源转换装置往往由设计、成套部门用接触器、断路器等产品组合而成来替代.这种方案性产品往往因没有经过测试检验,其可靠性、安全性存在较大隐患(尤其是用两台接触器作为两路电源转换,电气连锁极不可靠,锁极一旦失败,将造成两台电源变压器并联,电源并联的后果严重的可催毁整个供电系统.之后由天津低压电器公司开发了由断路器+机械连锁+控制器构成自动转换开关电器.它的进步是由产品替代方案,并按一定技术规范进行产品试验验证,产品的可靠性、安全性大大提高.90年代中期,针对国内市场急需高性能、高可靠自动转换开关电器产品的现状,日本、法国、德国、美国等自动转换开关先后打入中国市场,在一定程度上缓解了我国市场需求.近几年,我国的双电源自动转换开关生产企业(尤其是生产CB级ATS企业)迅速增加,其产品性能及产品质量不一,给设计、使用部门选用造成一定困难,也由于对ATS使用和选用不当,给国家财产造成很大损失.为了规范双电源自动转换开关(ATS)及配套电器产品的生产与选用,国家质检总局于2002年12月颁布了GB/T14048.11-2002《自动转换开关电器》(等同IEC60947.6.1-1998)国家标准,2003年4月1日实施.该标准将是今后ATS生产制造企业、设计使用单位、商业活动共同遵循的一部技术性法规文件,也将是3C认证依据的技术法规.双电源自动转换开关(ATS)分PC有与CB级两种.代表PC级的具有世界先进水平的产品有美国的ASCO及日本共立.代表CB级的有法国的施耐德等.目前,国内生产CB级ATS产品的企业约几十家,如天津低压电器公司、天津万高、等公司.生产PC级ATS产品的企业有无锡韩光、北京第一低压电器、上海超韩等.生产电动式刀开关(用于双电源切换)产品的企业也有5-6家,如法国朔高美等.自动转换开关电器(ATSE)一般由两部分组成:①自动转换开关本体;②控制器.1.1自动转换开关本体又分两类:第一类为CB级,它是由两台断路器加机械连锁组成,具有短路保护功能;第二类为PC级,一体式结构(三点式).它是双电源切换的专用开关,具有结构简单、体积小、自身连锁、转换速度快(0.2s内)、安全、可靠等优点,但需要配备短路保护电器.1.2控制器控制器也有两种形式:一种由传统的电磁式继电器构成;另一种是数字电子型智能化产品.它具有性能好,参数可调及精度高,可靠性高,使用方便等优点.国内外常见的几种ATS产品及电动式刀开关产品的对比见表1.常见ATS产品与电动式刀开关产品的对比表1生产厂家电器级别连锁操作方式触头系统转换时间控制器控制发电机组加载负荷符合IEC60947-6-1标准美国ASCO PC级无需单线圈单刀双投式 170ms 智能型有无符合日本共立 PC级机械连锁单线圈单刀双掷式 30~80ms 智能型有无符合韩国DACO PC级机械连锁单线圈单刀双掷式 120ms 智能型有无符合香港斯沃 PC级机械连锁单线圈单刀双掷式 150ms 智能型有无符合法国施耐德电动开关机械连锁两台电操断路器 1.5s 智能型有有仅符合GB14048.2天津低压 CB级机械连锁单台电操断路器 2.5s 外接有有符合法国朔高美刀开关机械连锁直流电机双刀双掷式 1s ――――――仅符合GB14048.3二、产品结构分析对比及ATS的选择目前,国内市场上用于两路电源切换的大致有三种开关:①CB级ATS;②PC级 ATS;③刀开关(电动).下面从产品结构、性能及所遵循的标准三个方面,分别将CB级与PC级ATS;PC 级ATS与刀开关(电动)进行对比和分析.从中不难发现,PC级ATS是理想的双电源切换开关.2.1 CB级与PC级ATS两者有以下区别2.1.1两者机械设计理念不同CB级是由断路器组成,而断路器是以分断电弧为已任,要求它的机械应快速脱扣.因而断路器的机构存在滑扣、再扣问题;而PC级产品不存在该方面问题.PC级产品的可靠性远高于CB级产品.2.1.2断路器不承载短路耐受电流,触头压力小供电电路发生短路时,当触头被斥开产生限流作用,从而分断短路电流;而PC级ATS应承受20Ie及以上过载电流.触头压力大不易被斥开,因而触头不易被熔焊.这一特性对消防供电系统尤为重要.2.1.3双电源在转换过程中存在电源叠加问题PC级ATS充分考虑了这一因素.PC级ATS的电气间隙、爬电距离的180%、150%(标准要求).因而PC级ATS安全性更好.2.1.4触头材料的选择角度不同断路器常常选择银钨、银碳化钨材料配对,这有利于分断电弧.但该类触头材料易氧化,备用触头长期暴露在外,在其表现易形成阻碍导电、难驱除的氧化物,当备用触头一但投入使用,触头温升增高易造成开关烧毁甚至爆炸;而PC级ATS充分考虑了触头材料氧化带来的后果,尤其是日本共立的ATS其接点有硅合金制成,高度抗燃烧,而且当开关运行时,每一次接触自滑触点可以清理灰尘和氧化,这大大提高了ATS的使用寿命,降低了风险.2.2 PC级ATS与刀开关(电动)区别2.2.1两者遵循的标准不同PC级ATS符合GB/T14048.11《自动转换开关电器》.刀开关(电动)符合GB14048.3《开关、隔离器、隔离开关以及熔断器组合电器》.2.2.2灭弧系统不同PC级ATS充分考虑了在电源转换过程中可能出现的二次电弧击穿问题,所以对触头开距有一定要求,而且要求电弧的游离气体应迅速排放.否则,易造成电源相间短路.2.2.3两者电气性能要求不同PC级ATS是在6In电流,1.05Ue电压下,接通/分断循环次数为12次;而刀开关是在3Ie/1Ue下,接通/分断5次.两者的电气寿命、机械寿命也不同.PC级ATS的电气寿命是在2In/1.05Ue条件下至少操作循环1000次,机械寿命5000次;而刀开关的电气寿命仅在1In/1Ue条件下操作200次,机械寿命800次.两者电气可靠性不同.2.2.4切换速度不同PC级ATS切换速度一般小于0.3s;而刀开关用于双电源转换时切换速度不少于1s.2.2.5试验方法不同在进行接通与分断试验时,PC级ATS是在不同的电源相序下进行(灭弧能力考核较严);而刀开关对相序无要求.通过上述对比可知PC级ATS是理想的双电源转换开关.三、ATS产品的应用随着经济发展,现代生活和现代工业对断电的容忍能力越来越差.国外工业发达国家(尤其是美国和日本)把ATS及配套产品视为电源的一部分,对ATS产品选择与使用都很慎重.在双电源紧急供电系统首选PC级产品,且开关在转换过程中不允许中间停留(即不带零位).其目的是增加电源的可靠性.由于备用电源种类不同,ATS选择也应有所不同.目前,国内备用电源有三种形式:(1)电网;(2)发电机组;(3)EPS(蓄电池组逆变).当备用电源为(2)或(3)时,其容量一般仅是常用电源容量的20%~30%.ATS一般是不允许带大电动机或高感抗负载转换.如大电动机负载在运行中切换,电源相位差距较大时它将受到巨大的机械应力.同时由电动机产生的反电势引起的过电流可能造成熔断器熔断或断路器脱扣.解决方法常采用电阻吸收或减负荷方式.在ATS的应用电路中一般采用熔断器隔离器,它们在电路中起两个作用,一是短路保护;二是维修隔离.四、公司PC级ATS产品简介为了向广大用户提供理想的ATS产品,上海超玛进出口有限公司与日韩两国此类产品的生产厂商长期合作,目前是日本共立和韩国DACO ATS的国内总代理.该产品完全符合国家标准及相应的国际标准的PC级ATS.日本共立SSK-MZ系列产品有30A、60A、100A、150A、300A、400A、500A、600A、800A、1000A、1200A、1400A、1800A、2000A、3000A;韩国DACO ATS M型产品有:400A、600A、800A、1000A、1200A、1400A、2000A、2500A、3200A、4000A;DACO ATS T型产品有:100A、200A、400A.SSK-MZ型产品特点1)足够的接触开放时间,以避免在转换过程中可能出现的电弧放电.2)板簧保证接触压力不变,因此在电压变换的情况下接触导电率不变.3)因为机械闭锁装置的存在,在转换之后,无需操作电流.4)接点有硅合金制成,高度抗燃烧.5)当开关运行时,每一次接触自滑触点可以清理灰尘和氧化.6)共立SSK系列双电源转换开关的时间转换等级:MZ为30ms~80ms、ES为3~8ms;可满足要求比较高的计算机控制系统、通信系统以及医疗设备等两路电源的切换.。

个人电脑电源解析

个人计算机电源原理解析站长研究个人PC 电源,必须从开关电源芯片开始。

这里是一个PTP-2038电源的实际应用的例子,其分析思路对电源的维修具有普遍意义。

第一部分:TL494芯片这是一个应用极为广泛的控制器件,在个人PC 电源中,基本使用的都是这个芯片。

它是由TI 公司生产的。

一.芯片管脚定义TL494是16脚芯片。

图1:TL494管脚排列1脚/同相输入:误差放大器1同相输入端。

2脚/反相输入:误差放大器1反相输入端。

3脚/补偿/PWM 比较输入:接RC 网络,以提高稳定性。

4脚/死区时间控制:输入0-4VDC 电压,控制占空比在0-45%之间变化。

同时该因脚也可以作为软启动端,使脉宽在启动时逐步上升到预定值。

5脚/C T :振荡器外接定时电阻。

6脚/R T :振荡器外接定时电容。

振荡频率:f=1/R T C T 。

7脚/GND :电源地。

8脚/C1:输出1集电极。

9脚/E1:输出1发射极。

10脚/E2:输出2发射极。

11脚/C2:输出2集电极。

12脚/Vcc :芯片电源正。

7-40VDC 。

同相输反向输补偿/PWM 死区时间控制C T R T C1 同相输反向输V REFE1 输出控Vcc C213脚/输出控制:输出方式控制,该脚接地时,两个输出同步,用于驱动单端电路。

接高电平时,两个输出管交替导通,可以用于驱动桥式、推挽式电路的两个开关管。

14脚/VREF:5VDC电压基准输出。

15脚/反相输入:误差放大器2反相输入端。

16脚/同相输入:误差放大器2同相输入端。

二.基本特性1.具有两个完整的脉宽调制控制电路,是PWM芯片。

2.两个误差放大器。

一个用于反馈控制,一个可以定义为过流保护等保护控制。

3.带5VDC基准电源。

4.死区时间可以调节。

5.输出级电流500mA。

6.输出控制可以用于推挽、半桥或单端控制。

7.具备欠压封锁功能。

三.结构原理图2给出了TL494的内部原理框图。

图2:TL494内部原理框图芯片内部电路包括振荡器、两个误差比较器、5VDC 基准电源、死区时间比较器、欠压封锁电路、PWM 比较器、输出电路等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一部分:交流输入输入保险、开关、低匝数的共模电感(电感高频性能好),Y电容接PE地,用接地的导体将其屏蔽。

应该注意到热敏电阻和压敏Y电容都有套管覆盖,安规比较注意。

输入差模电感采用了铁硅铝磁环,并使用了直径1.25mm的线,铁硅铝磁环的耗损比传统使黄白铁粉芯少了很多。

PCB走线上,都经过了两个X电容,其中一个大电容和一个小电容共0.9uF,能较好的提高了差模LC滤波器的截止频率,提升了滤波效果。

共模电感使用了体积非常大的高磁导率铁氧体磁环其直径为T29*19*14//AL8700,采用直径1.25mm的线绕,电感量为10mH,并且要注意到,只在磁环表面只有绕了一层,第二层绕的很分散,这样主要是为了降低绕组之间的寄生电容,提高电感的截止频率。

另外在共模电感前面,马上接Y电容,形成LC滤波器,提升共模抑制效果。

整流桥用了2个并联,并且是共用一个散热片,这样使两个二极管的热耦合,均流效果好一点。

第二部分:PFC(计算表)PFC部分的电感,电感量为360uH采用两股0.85mm线并饶,采用铁硅铝磁环,其体积为:40mm*20mm。

PFC部分使用两个MOSFET并联(型号:6R125P),使用一个二极管输出(型号:ROHE SCS108AG),电容为430V/390uF 两个。

PFC高压母线通过Y电容连接到次级输出地。

PFC的控制芯片是NCP1654//65KHZ,是8脚平均电流控制器。

其驱动输出电流达到1.5A,能很好的驱动较大功率的MOSFET。

下面是NCP1654的典型应用。

这个IC的功能有:输出过压保护、反馈开环保护(通过关闭驱动实现)、输入欠压好过压保护(BO 引脚还集成AC波形检测)、内置软启动、过流保护、过功率限制。

1 脚GND2脚AC波形和误差放大器的信号的乘法器输出,为电流信号。

通过VM引脚的电容和电阻转为电压形式,用于产生跟随AC波形的PWM信号。

3脚电流检测,IC内部有电流源,通过CS外接的电阻检测,整流桥端的电压,来实现电流控制,该引脚有电流限制和过功率保护功能。

4 脚BO AC波形输入和欠压过压保护功能。

5 脚反馈的误差放大器补偿部分6脚输出电压检测7 脚VCC 工作电压9-20V。

8 脚DRV 峰值1.5A电流输出,驱动能力较为强大。

该PFC控制IC的特点:内置有欠压过压保护、FB引脚集成输出过压保护、CS引脚集成电流限制和过功率保护、平均电流模式控制。

PFC部分效率测试和分析:在不通电(未加直流偏置)测试PFC电感(铁硅铝材质),电感量为360uH。

经计算在满载860瓦和低压90V输入时,在电流的直流偏置作用下,电感量会下降55-60%。

因此可以得出该PFC电感的满载电感量为210uH,经计算取电感纹波电流为44% * 电感电流三角波的平均值。

在这个比例下,可以在90V输入下得到210uH的电感量。

由于他们采用的是外径40mm、厚度20mm的磁环,我找了美磁铁硅铝的产品手册,最为接近的是77083,外径40mm厚度15mm,磁导率为60,电感系数AL为81。

计算满载所需要的电感量和考虑直流偏置下的电感量下降,可以得到75匝(使用77083-A7磁环)能符合210uH的要求。

由于铁硅铝的磁环在高频和高磁通摆幅下磁芯耗损较大,考虑是否需要通过加大匝数降低磁芯的dB变化,来降低磁芯损耗。

我没有数他们的磁环上的匝数,但是可以看到匝数并不少。

他们的磁环采用铜线是外径0.9,实际铜线可能在0.85mm。

我用电流密度5A/mm^2,计算满足低压满载的电流至少需要2股1mm的铜线,但考虑PC电源的大风扇,所以他们的电流密度选的大一些,这样降低了一些铜线消耗,加大了铜线DC损耗。

经计算在满载和低压下铜线DC耗损为0.8W,磁环耗损为3W,磁芯耗损计算公式来于美磁的产品手册。

所以用75匝,磁芯耗损还是较大,如果有条件应该进一步的加大铜线匝数,降低磁芯的dB值,这样才能降低在低压满载时的磁芯损耗,提升效率。

如果PFC电感的交流损耗比较小的话,可以忽略绕组的交流损耗。

但是实际上还是需要注意的,由于是采用低磁导率的磁环,所以电感内部没有直接开气隙,在气隙周围带来的损耗也可以避免,这也是为什么要选择磁环的原因。

考虑在230V输入下的PFC损耗:首先PFC电感的占空比和电流大大降低,MOSFET流过的电流也会降低。

相比低压,高压情况下MOSFET的导通耗损下降非常多,输出电容上的耗损接近一致。

该样机采用了2个COOLMOS并联,在这样的配置下,导通耗损被降低到了非常低的地步。

PFC输出二极管,在高压下二极管导通时间加大。

加大了二极管的导通耗损。

但是在二极管上的恢复电荷的耗损是不可避免的,在选择整流二极管时,应该考虑恢复电流小和恢复时间短的二极管。

但是该样机上采用了SIC二极管,降低了高温和高电流时的正向压降,减少了传统快恢复二极管上的恢复电流引起的耗损。

也正是因为采用了SIC二极管的原因,在PFC上没有使用RC吸收元件。

桥式整流上的耗损:在低压满载时,流过整流桥的电流非常大,整流桥的耗损达到了夸张的19W,在该样机上采用了2个整流桥并联,来应对低压满载的情况。

在高压230V输入时,整流桥的耗损也有8W。

不可小视,因此在该电源样机上,采用了两个整流桥和一个较大的散热器来对付整流桥上的耗损和温升。

如何提高PFC段的效率?1、对高压输入来讲,希望PFC电感的铜线匝数少一些,能明显的提升效率。

在高压输入时PFC磁芯耗损非常小。

因此可以选择较粗的铜线,满足较低的电流密度,降低铜线的DC损耗。

2、使用低导通内阻和低COSS电容的MOSFET,减弱硬开关存在的COSS电容开关耗损。

加大驱动电流,降低电压和电流交叉时间,降低交叉耗损。

3、使用在高温时低压降二极管,低恢复电荷二极管。

减弱导通耗损和开关耗损。

4、选用低电阻的电流感测电阻,降低电流采样的损耗。

5、选择低耗损的磁芯,同时也要有低磁导率应对CCM模式的高直流偏置,同时使用交错的铜线绕制,尽量降低磁芯耗损和铜线耗损。

6、第三部分:LLC谐振电路部分分析LLC控制IC为CM6901TX,其典型应用如下图:这个IC是台湾冠鸿电子的产品,其功能有:LLC/SRC+SR控制,能适应LLC 区域和SRC区域工作,并在轻载时有PWMING功能解决空载频率太高的问题。

IC内部集成有反馈to频率的误差放大器和轻载PWMING控制器。

软启动电容具有使能和关闭功能,LLC谐振回来电流超过限制后,通过对软启动电容的充放电实现自动重启保护。

其内部框图如下:各引脚的功能:1、RSET 外部连接的电阻,将PEAO运放输出电压转为电流,实现频率调整。

SR 在PWMING控制模式,该引脚电压会低于1.5V。

2、VFB 输出电压反馈引脚,连接内部误差放大器。

3、FEAO 误差放大器的输出,用于连接补偿元件4、D_IN- 轻载运算放大器的反相输入端5、D_IN+ 轻载PWMING模式的运算放大器的同相输入端。

6、DEAO PWMING模式运算放大器的输出端,外接补偿元件7、CSS PWM/PFM工作模式的软启动,当低于1V时关闭驱动输出。

当电流超过限制时,通过对这个引脚放电和充电实现自动重启功能。

8、ILIM 电流检测输入,1V为限制值。

9、RT/CT 振荡器,能设定最低开关频率10、GND11、SDRVB SR管驱动12、SDRV13、PRIDRVB14、PRIDRV15、VCC 工作电压10-23V16、REF 内部7.5V的基准电压输出同步整流的死区时间控制:当电源工作在SRC模式,次级电流连续。

SR控制器应该和初级开关信号同步,当初级开关信号开启后,相对应的SR信号应该要开启,同时初级信号关闭后,SR信号也要关闭,否则就是炸鸡。

同时由于电流连续,为了效率考虑次级SR应该在整个周期内都应该开启状态。

但是实际上应该加入死区时间,次级SR两路信号应该插入死区时间,避免在初级开通时,发生炸鸡。

下面是CM6901的SR控制逻辑:1、初级两路信号之间延迟为TDEAD1,这个延迟用于实现ZVS和提高桥式电路的可靠性,可以根据要求来设定。

典型值:610ns2、初级信号开启后,距离次级SR信号开启这段时间被成为“上升沿死区时间TDelay2”,这个时间是SR管的电流从S>>D的过程,适当的延迟可以使SR管实现ZVS,提高驱动效率。

但是这个段时间不能太长,否则流过体二极管的电流很大之后,在打开SR管,那样耗损还是很大,SR失去意义。

典型值:660ns3、SR管先关闭距离初级关闭之间的时间距离,被成为下降沿死区时间Tdelay1。

这个死区时间的插入主要是为了提高SR的可靠性。

这样操作使得SR管关闭后,靠体二极管流过正弦波的较低电流。

同时避免了因为SR的关闭延迟和初级死区时间,遇到一起。

当SR还未完全关闭,初级另外一路已经打开,发生炸鸡。

典型值100ns这种情况在英飞凌的LLC+SR控制器也有相应的措施,就是提前关闭SR,因为SR关闭并非驱动一去掉就完全阻断,是需要一定时间的。

如果能在初级关闭前,提前关闭SR管,则大大的提高了可靠性。

调节频率和死区时间的办法如下:频率调节和死区时间的设定:次级SR管比初级主管先关闭的实现:通过设置Vrest引脚的电压(通过两个电阻对REF分压),该电压加1.5V后送到SR_PWM比较器的反相输入端,当RTCT引脚上的三角板电压高于1.5V+Vrest后,比较器状态改变,关闭SR管。

因此可以通过改变Vrest引脚的电压来实现次级SR管的比主开关管提前关闭的时间(或比例)。

当Vrest引脚电压越高,SR开通的时间越短,Vrest电压越低SR开通的时间越长,当然在高于谐振频率运行时需要,让SR提前一段时间关闭有利于提高可靠性。

初级两路开关之间的死区时间:初级开关的开通时间长度是由RTCT引脚内部对电容CT充电,CT上的三角板到从谷值1.25V达峰值3V的时间决定,两个开关管之间的死区时间是由对CT放电的时间决定。

因此较大的电容CT,可以加大死区时间,改变对CT的充电电流,来改变频率。

软启动策略:CSS引脚内部有1V的比较器,当该引脚电压低于1V时,关闭驱动输出。

在LLC的软启动阶段希望要有足够高的频率,使得谐振回路的的阻抗从很大,慢慢较小,使得流过谐振回路的电流慢慢加大,这就是软启动的目的。

在IC内部有电流源典型值为7.5uA为外接的电容充电,当VCSS电压低于1V时,VFAEO 电压为5.25V,当CSS电压高于1V后,FAEO的电压开始下降,同时开关频率从大到小变化,FAEO = (VFB-(VSS-1))*GMV。

保护和自动重启:1、VFB电压高于2.93V2、VFB电压低于0.5V或FB短路到地。

3、指示电流的电压高于1V。