中值滤波器FPGA实现

FPGA比较矩阵排序法及在中值滤波器中的应用

E AC 1 7 E C:2 0

d i1 . 9 9 j i n 1 0 — 4 0 2 1 . 1 0 9 o :0 3 6 / . s . 0 5 9 9 . 0 2 0 .0 s

FG P A比较 矩 阵排 序 法 及在 中值 滤 波器 中的应 用 米

吕伟新 , 李清清 娄俊 岭。 ,

集成电路构 造一 种硬件矩 阵比较器 , 将输人数据按行列排列后 进行 比较 , 使第 j 的比较输 出结果相 加 , 行 即可求取第 j 个输人

数据在输入 数据 集合 中的序列值 。采用 F G P A芯片构造多种排序器 , 最大延 时均在几 十 n 量级 , s 将排序 器应用于 构造一维 和

二维中值滤波器延时小于 5 n 。硬件矩 阵比较器实现排序 和滤波 , 0s 原理简单 , 实时性好 。

关键 词 : 排序 : 比较矩阵排序 ; 中值滤波 ;P A FG

中图分 类号 : P 9 . 1 T 3 14

文献标 识码 : A

文 章编 号 :0 5 9 9 ( 0 2 0 — 0 4 0 10 — 40 2 1 )1 03 — 5

cntui a xcm a t , esces ev u fnu a oj naclci esm o m ai nv u s f ostt gm t o pr o t cs v a eo ipt t N . i o etni t u c pr o a e i n i r a rh u i l da l o sh fo s l o

L ii ,IQn qn L U J nig VWe n L i ig ,O u l x g n

( . ooi stt, ab tueo eh o g , ab 5 0 1C ia 1R btsI tueH ri I i t fTcnl y H ri 10 0 , hn ; c ni nn t s o n 2 R bts ntueH ri tue Tcnl y H ri 50 1 C i . oo s it, abnI i to ehoo , abn10 0 , hn c iI t s n t f g a; 3 R btsIs ueH ri ntueo Tcnlg H ri 50 1 C i ) . ooi nt t,ab s i f e o oy,ab c t i nI t t h n1 00 , n ha

基于FPGA的改进型中值滤波研究

巴

2o' . 2 11

0 引言

视 频 图像 处 理 技 术应 用 日益 广 泛 ,实 时性 要 求越 来越 高。若单纯 采用软 件的 方法进行 一些前 期 的预处理 ,

e vrn n f ats , n co dn c mua o s es i yh s entsf d n i me t r l a da c rigt s hs l ini a bl a b e t e . o o Qu u I o u i t tf i i t ei i

c me e in meh d b s d o se l n . mp r d wi r dt n ei s s c ei n h s r a y a c lr td o sa d s t o ae n asmb y l e Co a e t t i o a d s , u h d s a e t c ee ae g i h a i l n g g g l

t e u r me t Atls, u h d s n h sh d a i lt n t h oe s s m’ i lm e tt n meh d wi h i me r q i e n . at s c ei a a n s g mu ai o t e wh l y t S mp e n ai t o t t e o e o h

但 是随 着 电子技术 的发 展 ,特别 是 F GA技 术 的迅猛发 P 之 时 ,该方 法减少 的计算 量是很 可观 的,因此快速 中值 展, 使用 F G P A来对视频信号进行 中值滤波这类运算简单 , 滤波可 以大大加快处理速度。 但数据量大的处理, 使得系统实时性成为一种现实。

基于FPGA的中值滤波算法研究与硬件设计

编程器件的基础上进一步发展的产物。它是作为专 用集 成 电路 ( I ) ASC 领域 中的一种半 定制 电路 而出现

的 。既解 决 了定制 电路 的不 足 ,又克服 了原有 可编 程器件 门电路 数有 限的 缺点 。根据 面阵 C D 器 件 C 驱 动 要 求 ,采 用 此 项 技 术 进 行 了 图 像 处 理 专 用 F G 芯片设 计 ,对完 成 以 F G 图像处 理芯 片为 PA PA 核心 的实时 图像处 理系 统 的设计 有重 要意 义 。

中值滤波是一种非线性的图像平滑方法 ,与均

值滤 波器 以及 其它线 性 滤波器 相 比 ,它能够很 好地 滤 除脉 冲噪声 ,同时又 能够保 护 目标 图像边缘 。它

是一种邻域运算 , 类似于卷积 ,但计算的不是加权 求和 ,而是把邻域中的像素按灰度级进行排序 ,然

V0. 1 No 1 1 3 . Ma . o 8 r20

基于FPGA的快速中值滤波算法实现

• 98•武汉迈迪克光电股份有限公司陈军旗 南开大学滨海学院 赵凤怡• 99•就能够构建出快速中值滤波的硬件模块,满足图像实时处理的要求。

2 设计实现2.1 滑动窗口模块基于邻域操作的图像处理算法广泛采用滑动窗口技术,用于获取待处理图像相关位置的原始数据(汤露,程姝,基于FPGA的实时中值滤波算法硬件设计,工业控制计算机,2018年第2期20-22页)。

本设计中采用3*3的窗口模板,模块的结构如图2所示。

4个LineBuffer和9个单寄存器组成模块的缓存单元,每个LineBuffer由双口RAM构成,其位宽和存储深度由视频图像的数据规模决定,至少要满足一行数据的存储要求;列缓存对每一行的输出进行移位操作,实现3个元素的顺序输出;多路选择器负责对输入输出的数据进行路由选择,保证输出数据的结构特征,满足算法设计的技术要求。

组成行缓存的4个LineBuffer在视频行同步信号的边沿切换工作状态,形成 “乒乓操作”结构。

任意时刻,保持一个LineBuffer处于写状态,其它三个LineBuffer处于读状态。

在同步信号的控制下依序切换,4个周期形成一个循环,周而复始。

由于4个LineBuffer的输出状态不断切换,为保证输出数据在空间上的顺序关系,需要对输出的3行数据进行重定位。

考虑到算法第一步要求对每一列的数据进行排序,本质上就已经打乱了原始数据的顺序关系。

因此可以直接对LineBuffer的输出数据进行排序输出,这样进入列缓存的数据已经完成算法要求的第一步处理,直接生成了中间序列。

2.2 快速排序算法的原理与与处理流程已经在论文2.2节有详细介绍,其中第一步已经在生成滑动窗口的过程完成,接下来需要对滑动窗口内每一行的三个元素分别进行排序,实现的代码如下所示。

其中X1为第一行的最大值,X2为第二行的中间值,X3为第三行的最小值,它们三个构成第三步对角线上的三个元素。

按照相同的方法,对X(n)重新排序,其中值即为最终的输出结果。

基于 FPGA 的数字滤波器设计与实现

基于 FPGA 的数字滤波器设计与实现引言:数字滤波器是现代信号处理的重要组成部分。

在实际应用中,为了满足不同信号处理的需求,数字滤波器的设计与实现显得尤为重要。

本文将围绕基于 FPGA的数字滤波器的设计与实现展开讨论,介绍其工作原理、设计方法以及优势。

同时,还将介绍一些实际应用场景和案例,以展示基于 FPGA 的数字滤波器在实际应用中的性能和效果。

一、数字滤波器的基本原理数字滤波器是一种将输入信号进行滤波处理,改变其频谱特性的系统。

可以对频率、幅度和相位进行处理,实现信号的滤波、去噪、增强等功能。

数字滤波器可以分为无限脉冲响应滤波器(IIR)和有限脉冲响应滤波器(FIR)两种类型。

IIR滤波器是通过递归方式实现的滤波器,其输出信号与过去的输入信号和输出信号相关。

FIR滤波器则是通过纯前馈结构实现的,其输出信号仅与过去的输入信号相关。

两种类型的滤波器在性能、复杂度和实现方式上存在一定差异,根据具体的应用需求选择适合的滤波器类型。

二、基于 FPGA 的数字滤波器的设计与实现FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,通过可编程逻辑单元(PLU)、可编程连线(Interconnect)和可编程I/O(Input/Output)实现。

其可编程性使得 FPGA 成为数字滤波器设计与实现的理想平台。

1. FPGA的优势FPGA具有以下几个优势,使得其成为数字滤波器设计与实现的首选平台:灵活性:FPGA可以根据设计需求进行自定义配置,可以通过修改硬件逻辑来满足不同应用场景的需求。

可重构性:FPGA可以重复使用,方便进行修改和优化,减少芯片设计过程中的成本和风险。

高性能:FPGA具有并行处理的能力,可以实现多通道、高速率的实时数据处理,满足对于实时性要求较高的应用场景。

低功耗:FPGA可以进行功耗优化,通过减少冗余逻辑和智能布局布线来降低功耗。

2. 数字滤波器的实现方法基于 FPGA 的数字滤波器的实现方法主要有两种:直接法和间接法。

中值滤波器算法

中值滤波器算法中值滤波器算法是一种常用的图像处理算法,用于去除图像中的噪声。

噪声是图像中不希望存在的干扰信号,可能由于图像采集过程中的电磁干扰、传感器的噪声或信号传输过程中的干扰等原因引起。

噪声会使得图像失真,降低图像的质量和清晰度,因此需要进行去噪处理。

中值滤波器算法的基本思想是将图像中的每个像素点的灰度值替换为该像素点周围邻域中灰度值的中值。

这样可以有效地去除噪声,并保持图像的边缘和细节信息。

中值滤波器算法的具体步骤如下:1. 对图像进行扫描,遍历图像中的每个像素点。

2. 对于每个像素点,选择一个固定大小的邻域窗口,该窗口覆盖了该像素点及其周围的像素。

3. 将窗口中的所有像素的灰度值按照大小进行排序,找到排序后的中间值。

4. 将该中间值作为该像素点的新灰度值。

5. 重复步骤2到步骤4,直到遍历完所有像素点。

中值滤波器算法的核心在于选择合适的窗口大小。

窗口大小的选择会影响去噪的效果和图像的细节保留程度。

如果窗口过小,可能无法去除大尺度的噪声;如果窗口过大,可能会导致图像细节的模糊。

因此,在实际应用中需要根据具体情况进行选择。

中值滤波器算法具有以下优点:1. 对于椒盐噪声等随机噪声有较好的去噪效果,能够有效地去除噪声点。

2. 不会引入新的噪声,保持图像的边缘和细节信息。

3. 算法简单,计算速度快,适用于实时处理和嵌入式系统。

然而,中值滤波器算法也存在一些局限性:1. 对于高斯噪声等连续分布的噪声效果较差,无法完全去除噪声。

2. 窗口大小的选择需要根据具体情况进行调整,调整不当可能会导致图像细节的丢失或模糊。

3. 算法无法区分图像中的目标和噪声,可能会将目标的细节也平滑掉。

为了提高中值滤波器算法的去噪效果,可以结合其他滤波方法进行优化。

例如,可以先使用高斯滤波器对图像进行平滑处理,然后再应用中值滤波器进行去噪。

这样可以兼顾去噪效果和图像细节的保留。

中值滤波器算法是一种简单且有效的图像去噪方法。

通过选择合适的窗口大小,可以去除图像中的噪声,提高图像的质量和清晰度。

基于FPGA的中值滤波算法的实现

基于FPGA的中值滤波算法的实现1.背景知识中值滤波法是⼀种⾮线性平滑技术,它将每⼀像素点的灰度值设置为该点某邻域窗⼝内的所有像素点灰度值的中值.中值滤波是基于排序统计理论的⼀种能有效抑制噪声的⾮线性信号处理技术,中值滤波的基本原理是把数字图像或数字序列中⼀点的值⽤该点的⼀个邻域中各点值的中值代替,让周围的像素值接近的真实值,从⽽消除孤⽴的噪声点。

⽅法是⽤某种结构的⼆维滑动模板,将板内像素按照像素值的⼤⼩进⾏排序,⽣成单调上升(或下降)的为⼆维数据序列。

⼆维中值滤波输出为g(x,y)=med{f(x-k,y-l),(k,l∈W)} ,其中,f(x,y),g(x,y)分别为原始图像和处理后图像。

W为⼆维模板,通常为3*3,5*5区域,也可以是不同的的形状,如线状,圆形,⼗字形,圆环形等。

中值滤波法对消除椒盐噪声⾮常有效,在光学测量条纹图象的相位分析处理⽅法中有特殊作⽤,但在条纹中⼼分析⽅法中作⽤不⼤.中值滤波在图像处理中,常⽤于保护边缘信息,是经典的平滑噪声的⽅法。

2.中值滤波理论中值滤波是⼀种⾮线性滤波,在数字图像处理中,对于 N X N (N 为奇数) 中值滤波器,可以滤除⼩于或等于邻域中(N 2- 1)/2 个像素的噪声并且较好地保持图像的边缘[3]。

对图像进⾏中值滤波处理⾸先要确定⼀个模板 N ×N ,⼀般选取 3X 3 或 5 ×5。

中问位置的图像数据的表达式为f (x ,y ) = med{f (x ± k,Y ± Z) , (K≤ (N -1) /2,Z≤ (N-1) /2) }要得到模板中数据的中间值,⾸先要将数据按⼤⼩排序,然后根据有序的数字序列来找中问值。

中值滤波排序的过程有很多成熟的算法,如冒泡排序、⼆分排序等,⼤多是基于微机平台的软件算法,⽽适合硬件平台的排序算法则⽐较少。

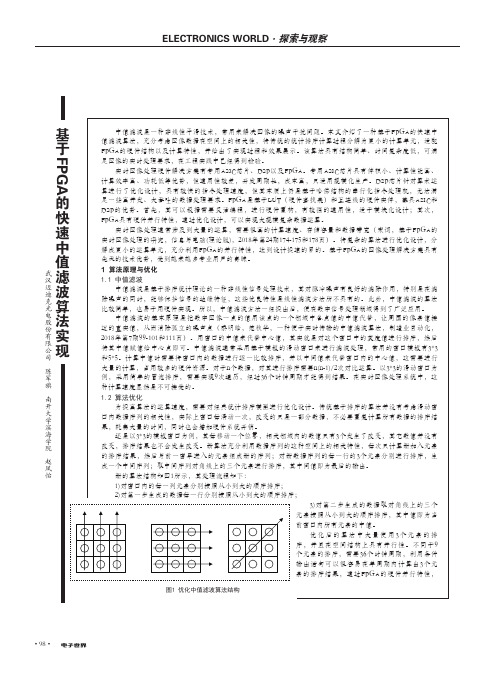

3.FPGA硬件实现⽅法L(1,1) L(1,2) L(1,3)L(2,1) L(2,2) L(2,3)L(3,1) L(3,2) L(3,3)如上所⽰,为⼀个3x3的图像模板,第⼀步:分别对三⾏像素进⾏排序(例:由L11,L12,L13得到L1max,L1mid,L1min);第⼆步:分别对三⾏像素中的最⼤,中间和最⼩分别进⾏排序(例:由L1max,L2max,L3max得到Lmax_max,Lmax_mid,Lmax_min);第三步:对最⼤的最⼩,中间的中间以及最⼩的最⼤进⾏排序(例:由Lmax_min,Lmid_mid,Lmin_max得到midian);FPGA的算法实现步骤基本如此。

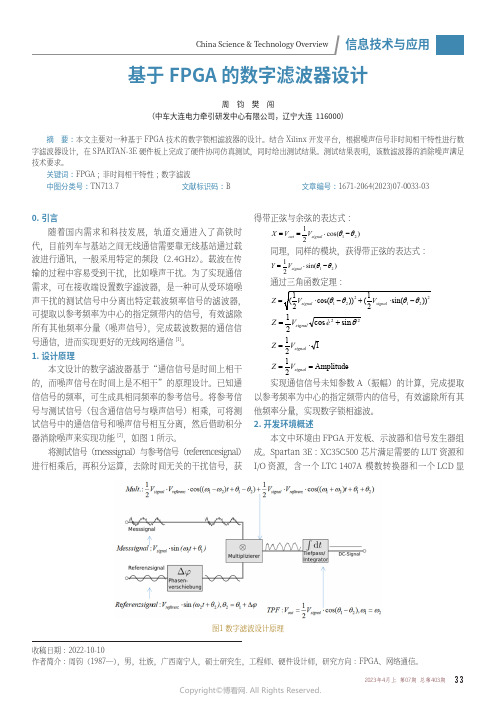

基于FPGA_的数字滤波器设计

332023年4月上 第07期 总第403期信息技术与应用China Science & Technology Overview进行相乘后,再积分运算,去除时间无关的干扰信号,获I/O 资源,含一个LTC 1407A 模数转换器和一个收稿日期:2022-10-10作者简介:周钧(1987—),男,壮族,广西南宁人,硕士研究生,工程师、硬件设计师,研究方向:FPGA、网络通信。

基于FPGA 的数字滤波器设计周 钧 樊 闯(中车大连电力牵引研发中心有限公司,辽宁大连 116000)摘 要:本文主要对一种基于FPGA 技术的数字锁相滤波器的设计。

结合Xilinx 开发平台,根据噪声信号非时间相干特性进行数字滤波器设计,在SPARTAN-3E 硬件板上完成了硬件协同仿真测试,同时给出测试结果。

测试结果表明,该数滤波器的消除噪声满足技术要求。

关键词:FPGA ;非时间相干特性;数字滤波图1 数字滤波设计原理342023年4月上 第07期 总第403期信息技术与应用China Science & Technology Overview示器。

示波器Tektronix TPS 2024:带宽为200MHz,最高取样速率:2.0GS/s,具有4个通道。

信号发生器HM-8030:频率50MHz 至10MHz,具备高纯度和幅度稳定性。

3.基于FPGA 的数字滤波器设计3.1 设计框架FPGA 设计框架如图2所示。

块,滤波模块和LCD 显示模块这些二级模块组成;(5)各二级模块根据功能划分,将各自功能用VHDL 进行编码设计。

二级模块经过仿真实现,在顶层模块进行结合,实现一整套系统功能。

3.3.1 模数转换设计ADC 芯片将采集的模拟信号离散化为单个离散采样值。

再将采样值转为数字值,根据板卡搭载的ADC 芯片[4]simulation 仿真产生的模拟信号可以非常接近,但是始图3 测试验证(a)测试1(b)测试2China Science & Technology Overview信息技术与应用0,4 V(max 0,223 V)(max 0,239 V)(max 0,233 V)(max 0,214 V)(max 0,234 V)352023年4月上 第07期 总第403期。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计报告书《数字信号处理及系统设计》中值滤波-FPGA设计设计人:袁兴班级:硕研10级3班学号:2010010339山东科技大学中值滤波器-FPGA 实现■ 前沿对于许多图像处理问题,传统的线性滤波方法存在着固有的缺陷。

为此,最近几十年来,发展起来了一类新的非线性滤波器结构—中值滤波器。

这类滤波器在图像信号处理中具有独特的优势,目前已成为非线性滤波领域的一个研究点。

针对传统中值滤波算法排序量多、速度慢的缺点,提出了一种基于FPGA 的中值滤波快速算法。

充分利用两个相邻滤波窗口中的相关排序信息,随着一列新像素的移入,同时更新已有的排序信息,从而完成中值滤波处理。

该算法将每个窗口查找中值的比较次数降到很低,达到了快速抑制噪声及保持图像细节的目的。

中值滤波器设计的原理中值滤波是一种非线性滤波方法,于1971年首次提出[1]。

它首先对邻域点的灰度值进行排序,然后选择中间值作为输出灰度值。

中值滤波的公式如下:g (x, y )=med (f (x -i ,y -j ))i ,j ∈S (1)其中,g (x, y)和f (x, y)为像素灰度值;S 为模板窗口。

中值滤波要实现的是用中值g (x, y)来代替中心点值f (x, y)。

对于椒盐噪声来说,由于模板的中值很大程度上不会是噪声,因此中值滤波能很好地消除它。

当中心点值为噪声时,其值和中值数值相差较大,应该用中值来代替中心点值。

但是,当中心点值不为噪声时,其值和中值数值相差不大,如果还用中值来代替中心点值,那么虽然对于单个像素点来说,不会产生较大的差异,但是如果对一整幅图像都进行这样的处理,这将在一定程度上使整幅图像变得模糊。

据此,可以对中值滤波算法做一些改进。

首先,排序窗口内的图像数据,找到中值。

然后将中值和中心点值做差,将差值与事先设定的阈值T 进行比较,如果两值之差的绝对值|g (x ,y -f (x, y)|大于等于阈值T ,则认为中心点图像数据是噪声,用中值代替原数据值;如果两值之差的绝对值|g (x ,y -f (x, y)|小于阈值T ,则认为中心点图像数据是有效数据,保持不变。

即'(,)(,)(,)(,)(,)(,)(,)g x y g x y f x y T g x y f x y g x y f x y T ⎧-≥⎪=⎨-⎪⎩ 2) 其中,g (x, y)如式(1)中定义。

阈值T 的选择应该针对不同的图像,根据经验或者实验进行选取。

如果阈值选择过大,将有可能滤除不掉噪声;如果阈值选择过小,将仍会使图像变得模糊。

由于噪声和周围像素相差较大,也和中值相差较大,因此阈值一般选择在几十左右。

这样,滤波处理之后的图像在除去噪声的同时会更加接近于原图像,能在更大程度上保留图像细节,使图像更清晰。

■中值滤波的快速算法我们都知道,冒泡排序算法,在中值滤波中,是最基本、最经典的传统通用算法。

很多经过改进后的优化版本的快速算法和经过推广衍生后的性能增强的中值滤波算法,都是基于这个冒泡排序算法的原理而产生的。

我们下面将会着重描述的中值滤波的快速算法,就是在这个冒泡算法上,经过修改优化得到的。

这个快速算法的理念就在于,我们没有必要对输入窗口中的所有灰度值都进行排序,也不需要得到它们的完整序列。

我们只需要找到那个排列在中间位置的值就可以了。

它包含了以下所罗列出来的三个步骤:第一步:对输入窗口中的每一列的灰度值,形成一个象素数组,并且对每一个象素数组进行单独的排序。

第二步:对输入窗口中的每一行的灰度值,也形成一个类似的象素数组,并且同样对每一个象素数组进行单独的排序。

第三步:经过排序之后,形成了新的输入窗口,这个窗口在行和列中都已经得到了排序,对现在排序之后的输入窗口中的对角线上的所有灰度值进行排序,并且选出这一个对角线上所有灰度值的中间值,然后这个中间值就是整个输入窗口的中值,也就是要作为最后输出的那个中值。

我们可以得到这样一个快速算法。

就是在特殊的3×3的象素大小的输入窗口的情况下,有九个数据需要被处理。

那么我们就顺便按照物理位置将这个九个象素点分成列的三组,然后分别进行排序,得到每一列数据的最大值、中间值和最小值。

然后对三个最大值、三个最小值和三个中间值进行排序,得到的结果,我们只取三个数,也就是三个最大值中的最小值,三个中间值中的中间值和三个最小值中的最大值。

这三个值对应上面的那个说法,就是经过两个步骤之后,行和列都已经排序完了之后的一个对角线上的三个值。

这三个值最后经过排序得到的中间值,就是整个输入窗口中九个象素点的灰度值中的中间值了。

中值滤波的快速算法的过程如下图1所示:图1 在输入窗口大小为3X3的情况下的中值滤波快速算法中值滤波算法核心是排序,排序算法的优劣直接决定了求取中间值的效率。

从而决定滤波器的整体性能。

基于硬件的排序算法设计可以充分的利用硬件平台的并行性特点,从而达到加快处理的速度目的。

下面分析3X3窗口图像数据的数学模型,说明中间值的求得过程。

设窗口的数据分别为:W11 W12 W13W21 W22 W23W31 W32 W33第一步:可以将9个数据按行数分成3组(L1、L2、L3),分别进行排序。

L1min=min(W1y) L1med =med(W1y) L1max=max(W1y)L2min=min(W2y) L2med =med(W2y) L2max=max(W2y)L3min=min(W3y) L3med =med(W3y) L3max=max(W3y)第二步:重新分组,将每组中的最大值,供3个值,选出组成大值组V1,类似的组成中值组V2和小值组V3,再次分别排序。

V1min=min(Lx max) V1med =med(Lx max) V1max=max(Lx max)V2min=min(Lx med) V2med =med(Lx med) V2max=max(Lx med)V3min=min(Lx min) V3med = med(Lx min) V3max =max(Lx min)经过分析可得到:V1max 是9个值中最大的,不可能是中间值;V1med 是由小到大排列的9个值中至少是处于第6的位置,不可能是中间值;V2min 是由小到大排列的9个值中最多是处于第4的位置,不可能是中间值;V2max 是由小到大排列的9个值中至少是处于第6的位置,不可能是中间值;V3min 是由小到大排列的9个值中处于最小的位置,不可能是中间值;V3med 是由小到大排列的9个值中至多是处于第4的位置,不可能是中间值;第三步:排除了以上六个值,还剩下大值组的V1min,中值组的V2med和小值组V3max的三个值可能是中间值。

将这三个值排序,可以证明这三个值的中间值med{V1min,V2med,V3max}就是这9个值中的中间值,用Smed 表示。

证明如下:这三个值由这9个数值组成的矩阵中的位置如下:V1min V1med V1maxV2min V2med V2maxV3min V3med V3max假设max(V1min,V2med,V3max)是这9个数值中的中间值Smed,那么Smed 是矩阵中包括主对角线在内的左下角6个值中最大的,在9点由小到大的排序中至少处于第六的位置,所以不可能是中间值;同理,假设min(V1min,V2med,V3max)是这9个数值中的中间值Smed,那么Smed在这9个值的由大到小的排序中至多是处于第四的位置,也不可能是中间值。

由于奇数点的中值一定存在,则唯一的可能就是事实,所以med{V1min,V2med,V3max}一定是这9个值的中间值Smed.图2 3X3窗口的中值滤波快速算法示意图整个算法可以分成以上三个步骤,而且每个步骤在硬件平台上完全可以并行执行,这样可以大大的提高排序的效率。

另外,算法不是对9点数据的完整排序,而是采用分组比较的办法找到中值。

简化了排序的过程,从而提高了效率。

■中值滤波的软件和硬件实现1、中值滤波的软件实现为证明该快速算法的正确性及可执行性,用C++对该算法进行建模仿真。

中值滤波的软件实现最重要的是排序。

排序主要是采用了冒泡排序法,从一帧图像中读取数据,进行滤波算法。

将排序后的数据写入到新的图形文件中,从而得到滤波后的图像。

冒泡排序较为简单,最重要的是如何将一帧图像中的数据进行整合后给冒泡算法。

从一幅图像中读取数据并进行数据排放的部分代码如下:unsigned char buffer[54+1024]; //定义原图像头缓冲区fread(buffer,1,54+1024,fp); //读取文件头54个字节unsigned long length=width*higth; //图像的总象素个数unsigned char readData[higth][width]; //用于存储原图数据的数组unsigned char writeData[higth][width]; //用于存储原图数据的数组fread(&readData[0][0], sizeof(unsigned char),length, fp);//从原图读入数据for(i=0;i<higth;i++)for(j=0;j<width;j++)writeData[i][j]=readData[i][j];unsigned char D[9]; //定义选取框for(i=1;i<higth-1;i++)for(j=1;j<width-1;j++){D[0]=readData[i-1][j+1];D[1]=readData[i][j+1];D[2]=readData[i+1][j+1];D[3]=readData[i-1][j];D[4]=readData[i][j];D[5]=readData[i+1][j];D[6]=readData[i-1][j-1];D[7]=readData[i][j-1];D[8]=readData[i+1][j-1];writeData[i][j]=lvbo(D); //调用冒泡排序算法}软件对图像进行中值滤波的效果如下:图3 滤波前的一幅静态图像图4 中值滤波后的静态图像结果:从两幅图像的比对中发现:中值滤波的图像相对于原图有点模糊,主要是将相邻的像素值进行了均值处理。

2、中值滤波的硬件实现1)标准中值滤波对邻域中的像素按灰度级进行排序,然后选择该组的中间值作为输出像素值。

对于3×3窗口的中值滤波,采用图下图所示的3级比较电路输出中值,。

第一级比较电路由3个三输入比较器C组成,每个比较器的输出数据依序排列(参见图示)。

将3组比较结果中最小的3个数放在一起、中间的3个数放在一起、最大的3个数放在一起,参加第二级比较。