基于FPGA的滤波器的设计

基于FPGA的FIR滤波器设计

~ ( 4 )

滤 波 器 的参 数 输 入 进 去 , 设 计 好 参 数 之 后 点 击D e s i g n F i l t e r ,则 可 以得 到 低 通 幅 频 响应 和相频的分析 。 同时 得 到 设计 的F I R 系数 h ( n ) 的值 如 下 :

1 . 引 言 2 1 世 纪 是 数 字 信 息 的时 代 , 数 字 化 、 智 能 化 和 网 络 化 已经 成 为 了一 种 趋 势 ,而 数 字

滤 波 器 的 单 位 脉 冲 响 应 ,即

t t ( e ) = ∑h ( k ) e

) = H( e j  ̄

化又是后 面两者 的基 础 。实 际的生活 中能接 触 到 的各 种 信 号 ,例 如 最 常 见 的广 播 信 号 , 通信信号 等等的大部 分都属于模 拟信号 ,有 小 部 分 是 数 字 信 号 。 模 拟 信 号 直 接 处 理 起 来 会 有 困 难 , 所 以 大 部 分 要 用 到 数 字 信 号 处 理 。 而 在 数 字 信 号处 理 方 法 中 , 数 字 滤 波 器 属 于是数字 信号处理 的一种常 用电子系统 。 数 字 滤 波 器 是 通 过 数 字 运 算 器 件 对 输 入 的 数 字 信 号 进 行 处 理 , 改 变 信 号 频 谱 , 以得 到 期 望的响应特 性的离散 时 间系 统。根据数 字滤 波 器 的 功 能 特 点 , 可 分 为 低 通 、 高 通 、 带 通 、 带 阻 和 全 通 类 型 , 根 据 冲 激 响 应 特 性 的 不 同 ,又 可 分 为 I I R  ̄ N F I R 数 字 滤 波 器 , 其 中 FI R 滤波 器 由于其 自身 的优点 ,成 为信号 处 理 中 滤 波 器 的 一 种 最 常 用 电路 。 2 F I R 滤波器基本原理与结构

基于FPGA的sinc3结构的数字抽取滤波器

基于FPGA的sinc3结构的数字抽取滤波器基于FPGA的sinc3结构的数字抽取滤波器,今年电子设计大赛D题必用的模块,实测效果非常好,做西格玛-德尔塔ADC必用的滤波器module sinc3(mdata1, mclk1, reset, DATA ,word_clk,mode);input mclk1; /*滤波器工作时钟*/input reset; /*滤波器复位*/input mdata1; /*接收到的待滤波的数据*/input [1:0]mode;output [15:0] DATA; /*滤波完成的数据*/output word_clk;integer location;integer info_file;reg [35:0] ip_data1;reg [35:0] acc1;reg [35:0] acc2;reg [35:0] acc3;reg [35:0] acc3_d1;reg [35:0] acc3_d2;reg [35:0] diff1;reg [35:0] diff2;reg [35:0] diff3;reg [35:0] diff1_d;reg [35:0] diff2_d;reg [15:0] DATA;reg [11:0] word_count;reg word_clk;reg init;/*Perform the Sinc ACTION*/always @ (mdata1)if(mdata1==0)ip_data1 <= 0; /* change from a 0 to a -1 for 2's comp */elseip_data1 <= 1;/*ACCUMULATOR (INTEGRATOR) Perform the accumulation (IIR) at thespeed of the modulator.Z = one sample delayMCLKOUT = modulators conversion bit rate*/always @ (posedge mclk1 or posedge reset)if (reset)begin/*initialize acc registers on reset*/acc1 <= 0;acc2 <= 0;acc3 <= 0;endelsebegin/*perform accumulation process*/acc1 <= acc1 + ip_data1;acc2 <= acc2 + acc1;acc3 <= acc3 + acc2;end/*DECIMATION STAGE (MCLKOUT/ WORD_CLK)*/ always @ (negedge mclk1 or posedge reset)if (reset)。

基于FPGA的IIR低通数字滤波器的设计

文件 时调 用 已建立好 的模 块 。测 试仿 真结 果表 明基于 F GA设计 的 IR数字滤 波器 达到 了设计 要求 。 P I

关键 词 :I I R数字 滤波 器 级 联型 中图分 类号 :T 1 N7 3 F GA P 文章 编号 :1 0 .8 22 1)20 2 .3 0 34 6 (0 20 .0 40

小截 断误 差的考 虑 , 据设计 指标 首先 利用 Mal 依 t b进行 参数 的计算 并进行 量化 ,同时获得 系统 的幅频 响应 、 a 单位 冲击 响应等 系统 基本信 息 。随后 在分 析 IR 数字 滤波器 内部 乘法器 、加 法器 的输入 输 出基础上 ,调 用 I Q ats I u r 软件 调试 程序 建立乘 法器 和加 法器模 块 ,依据 自顶 向下的设 计思想 搭建 整体 电路 ,并在 建立项 层 uI

据 幅度 特 性 指 标 要 求 设 计 了 一个 输 入 8位 、输 出

8位 的 IR低 通 数 字滤 波 器 。 I

频谱分析等领域 。数字滤波器按照响应方 式的不 同 ,可 分 为 FR ( 限长 脉 冲 响 应 )滤 波 器 和 IR I 有 I ( 限长 脉 冲 响应 ) 波 器 ] 比较 于 FR 数 无 滤 。相 I

Ab tat On ido IR d i l l rw ihhs8i usa d8o tusi ds ndbsdo PG I src: ekn I i t f t hc a n t n u t s ei e ae nF A.n f g ai e p p g tr so elain o sdrn erai h ut g err rt 'tep rmeesaecm ue n em frai t .cniei dces g tectn ro, sl h aa t r o p td ad z o g n i y r q a te yui t bb sdo eing ieie h se fr aino a ntd ep nead u ni db sn Mal ae nd s ud l .Tes tm i om t m g i erso s n z g a g n y n o f u ip l e o s r l curd L trbsdo ea a s p t n u u IRdgtl l rn e m us rs ne e s aq i . ae ae t n l io i u do t tf I ii f t n r e p a ao e , nh y sf n a p o ai e i mut l ainada dr c ie Quru it n erdt tpmut l aina da drm c ie l lpi t n d e hn , ats s r s re s lpi t n d e a hn d i c o ma H a f o eu i c o mo

基于FPGA的通用FIR滤波器设计

-

495 6

. . . . . . . . . . . . . . — —

实

验

技

术

与

管

理

第 2 7卷

第 1 0期

21 0 0年 1 O月

.

CN1 — 2 3 T 1 0 4/

Ex e i nt lTe hnM n g me t n

中 图分 类号 : N7 3 T 1 文献标志码 : A 文 章编 号 : 0 2 4 5 ( 0 0 1 — 0 9 0 1 0— 96 2 1 )0 0 6 — 4

Dein o nvra I ftrb sdo P sg fu iesl R i e ae n F GA F l

V0 . 7 NO 0 Oc .20 0 12 .1 t 1

基 于 F G 的通 用 FR滤 波器 设 计 PA I

聂 伟 ,杨 胜 姚 ,王 岩 嵩

( 京 化 工 大 学 计 算机 系统 与 通信 实验 中心 ,北 京 10 2 ) 北 0 0 9

摘

要 :提 出 了一 种 基 于 FP GA(il r g a f dp o rmma l aea ry 的 通 用 F R(iiei us e p n e 滤 波 器 设 e beg t ra ) I fnt mp lers o s )

b n —t p。a d i h st ea v n a e fhg r q e c e ou in a d ls e o ren e e .Th o g alb a d FP a d so n t a h d a t g so i h fe u n y rs l t n s r s u c e d d o e r u h M ta n — GA i lt n 。t er s l h w h tt i f t rme t h e in r q i me t . smu a i s h e ut s o t a h s i e e st ed sg e ur o s l e ns Ke r s n v r a R f t r i i l i e ;FP y wo d :u ie s lFI i e ;dg t l r l a ft GA;wi d w t o n o me h d

基于FPGA实现FIR数字滤波电路的设计及应用

编号:__________基于FPGA实现FIR数字滤波电路的设计及应用(最新版)编制人:__________________审核人:__________________审批人:__________________编制单位:__________________编制时间:____年____月____日车辆在动态称重时,作用在平台上的力除真实轴重外,还有许多因素产生的干扰力,如:车速、车辆自身谐振、路面激励、轮胎驱动力等,给动态称重实现高测量造成很大困难。

若在消除干扰的过程中采用模拟方法滤波,参数则不能过大,否则将产生过大的延迟导致不能实现实时处理,从而造成滤波后的信号仍然含有相当一部分的噪声。

所以必须采用数字滤波消除干扰。

FIR滤波的原理及实现本文采用FIR数字滤波,其原理如公式1所示。

Y(n)=(1)其中h(k)为系统滤波参数,x(n)为采集的信号,Y (n)为滤波后的输出信号。

FIR滤波器的h(n)0≤n≤N-1H(z)=(2)在本文中N=17。

由于h(n)具有对称性质,即:h(n)=h(N-1-n)(n=0,1,。

..,(N-1)/2)(3)这样就可以把FIR滤波器设计成具有线性相位。

利用这一情况,可以得到的乘法结构,需要(N+1)/2次乘法,仅是级联或并联结构所需次数的一半,因此,实际应用中多采用此方法。

我们选用17点的FIR滤波算法,这样实现 FIR卷积运算需要执行9次乘法和16次加法。

为了实现数据的实时处理,需要在20ms内完成这个卷积运算,如果选用单片机89C51(12M晶振)则无法实现。

所以我们选用了Altera公司的FLEX10K20。

FLEX10K系列是工业界个嵌入式的PLD,采用重复可构造的CMOSSRAM工艺,把连续的快速通道互连与独特的嵌入式阵列结构相结合,同时也结合了众多可编程器件的优点来完成普通门阵列的宏功能。

具有高密度、低成本、低功率等特点。

图1硬件结构框图硬件设计由于我们选用的AD1674芯片转换时间为10ms,而所设计的电路每隔20ms启动转换,所以有足够的时间完成模数转换。

基于FPGA与Matlab的最优FIR数字滤波器设计

图 1 直 接 l F R 滤 波 器 结 构 型 I

- 4

从 滤波器的系统函数可知它是恒稳定 的, 需要反馈 , 不 只要 加 权

.

∞

| 。

: : \

系 数 hi hN 1 i0 ≤N一 ) I (= (一 一) ≤i ) ( 1, R滤 波 器 就具 有 严格 的线 性 相 位 。一 F 般 而 言, 常用 的 FR滤 波 器 是线 性 相 位 的 , 滤 波 器 的 系 数 满 足某 种对 I 即

三 、 R 滤 波器 的 F FI PGA设 计 与 实 现

曲 ∑ ( ) : 一

其 中 xng 输 入 采 样 序 列 ,(是 滤 波 器 系 数 , () hi ) L是 滤 波 器 的 系 数 长度 ,() 示 滤 波器 的 输 出 序 列 。也 可 以用 卷 积 来 表示 输 出序 列 y ) y 表 n ( n 与 xn、( 的关 系 。 ( hn ) )

^p I 目 ,l i奢 l 31参数 提取 设 计 指 标 如下 : . 通 带 类 型: 陷波 通 带衰 减 :.1 B O0d 采 样频 率:.k z 75 h 通 带 边 频率 1 7 kz和 215 h . 5h 5 .7 k z

陷 波 频率 :.7 k z 1 5h 8 阶 数: 8 6

102 3 0 2)

要 】I 滤波器是一种被广泛应用的基本 的数字信号处理部件, FR 针对常用的软 、 硬件方法设计实现 FR 滤波器存在 的问题, 出采用 I 提

M a小 的 切 比 雪 夫等 波 纹 逼 近 方 法. 计 并 在 F GA 上 高速 并 行 实现, 格 线性 相 位 FR 滤 波 器 的 方案 。 d 设 P 严 I

滤 波 器设 计 工 具 箱 (l r eintobx 。faol 以设 计 几 乎所 有 的 ied g o ft s lo ) dt 可 基 本 的 常规 滤 波 器 , 括 缶 和 . 的 各 种 设计 方 法 。它 操 作 简 单 , 便 包 i r 方 灵活。

基于FPGA的卡尔曼滤波器的设计与实现

图12 卡尔曼滤波的时序仿真图

QuartusⅡ时序仿真(续)

用DSP Builder设计卡尔曼滤波模型是整个系统设计 中的一个子模块,把卡尔曼滤波模型转化后的VHDL文 件生成图元文件,如下图所示,以便在整个系统设计 中调用。

图13 生成的卡尔曼图元文件

基于FPGA的卡尔曼滤波器各功能模块设计

利用LA1032逻辑分析仪验证总体设计的正确性

DSP Builder是 Altera公司推出的 FPGA 的系统级 设计工具。它将 Matlab 和 Simulink系统级设计工 具的算法开发、仿真和验证功能与QuartusII的基 于 Verilog HDL 及 VHDL 语言的设计流程整合在一

起,实现了这些工具的集成,为用户提供了一个从 软件到硬件的完整的 DSP 开发平台。

基于FPGA的卡尔曼滤波器各功能模块设计

芯片模块结构

芯片模块的划分如下图所示,分频模块和AD控 制模块采用VHDL语言编程实现,卡尔曼滤波模块 用DSP Builder软件进行设计。

图1 芯片模块结构划分示意图

基于FPGA的卡尔曼滤波器各功能模块设计

单元功能模块设计 *分频模块 分频模块是将外部时钟进行分频设定,得到系统 内部AD控制模块和卡尔曼滤波模块所需要的时钟, 并为AD芯片提供时钟信号基准。此模块采用VHDL语 言编程实现。这里给出10分频时序仿真图,其中分 频模块的外部时钟输入频率为50MHz,产生的时钟 频率为5MHz。

使用 DSP Builder设计数字信号处理系统的流程为:

(1)在Matlab/Simulink中建立一个*.mdl模型文件,用图形方式调用 Altera DSP Builder和Simulink其他库中的图形模块进行数学模型 设计; (2)利用Simulink图形化仿真分析功能对此设计模型进行纯数学上的仿 真、验证及修改; (3)通过Altera DSP Builder中的SignalCompiler模块把 Matlab/Simulink的设计文件(· mdl)转成相应的硬件描述语言 VHDL设计文件(·vhd),以及用于控制综合与编译的RTL脚本; (4)在 SignalCompiler里用选定的工具自动进行综合和编译,或用 QuartusII 调用上述VHDL 文件,选择器件型号锁定引脚重新编译; (5)配置芯片(program device),即把SRAM对象文件(*.sof)下载到FPGA 芯片.

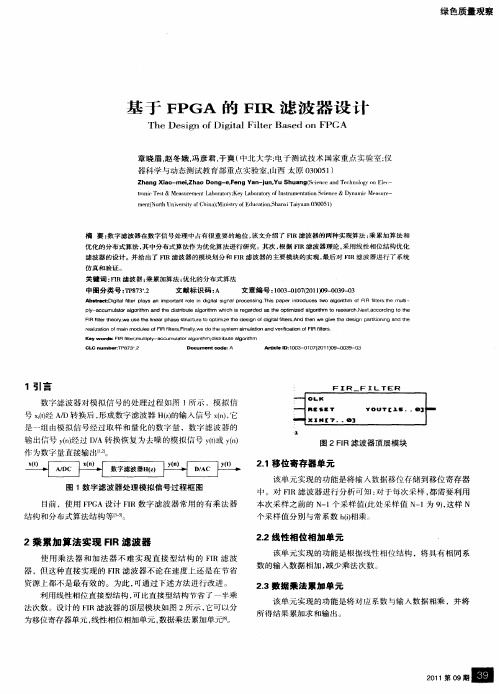

基于FPGA的FIR滤波器设计

该单元 实现 的功能是将输人数据 移位 存储到移位寄存器

中 。对 FR滤 波 器 进 行 分 析 可 知 : 于 每 次 采 样 , 需 要 利 用 I 对 都 本 次 采 样 之 前 的 N 1 采 样 值 ( 处 采样 值 N 1 9, 样 N 一个 此 一 为 )这

号 xt AD转换后 , 成数 字滤波 器 Hz的输入信 号 x )它 经 / ( ) 形 ( ) (, n

是 一 组 由模 拟 信 号 经过 取 样 和 量 化 的数 字 量 ,数 字 滤 波 器 的

1

输 出信号 y ) ( 经过 DA转换恢 复为去噪的模拟信号 y) yn n / (或 () t

r l a i f an m o ls o I I r ial , e ( h y tm i uat n a d v ii in o I ie s eai t z on o i due fF R t s Fn l w m e y 3 t e s se sm I i n er c o fF R ft r o o f at l a g i m ; srb t l r h l orh ditiu e ago i m t t

me t ot iesto hn) nsq o u ain h n i aya 30 1 n( rhUnvri f ia; i ,f ct , ax i n0 0 5 ) N y C Mi t Ed oS T u

摘 要: 数字 滤波 器在数 字信 号处理 中占有很 重要 的地位 , 该文介 绍 了 FR滤 波 器的两种 实 现算法 : I 乘累 加算 法和

Zh n a me,h o Do g- ,e g Ya j nYuSh ngs’ feadT cn lg nEe— a gXio- i a n eF n n-u , ua (( l n eh o y lc Z i c P o 0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

xxx大学本科毕业设计·论文 I 摘 要 自适应滤波器是统计信号处理的一个重要组成部分。在现代滤波处理技术中,自适应滤波器的处理效果尤为突出。在众多滤波器中,特别是在一些对信号处理的实时性要求比较高,体积功耗有严格限制的场合,使用FPGA硬件实现的数字滤波器更为广泛。 本论文从自适应滤波器研究的重要意义入手,介绍了线性自适应滤波器的算法,对几种基于最小均方误差准则或最小平方误差准则的自适应滤波器算法进行研究,就滤波器的基本原理及设计方法做了简单的介绍,最终设计基于FPGA的LMS算法设计复数自适应滤波器,对设计方法进行叙述,并以VHDL语言编写程序进行仿真测试。

关键词:自适应滤波器;FPGA;自适应算法LMS;有限冲激响应滤波器

xxx大学本科毕业设计·论文

II FPGA-based design of adaptive filter Student:TAN xx Teacher:CHEN xx

Abstract:Adaptive filter is a statistical signal processing as an important component.

Processing technology in the modern filter, the adaptive filter, particularly in the treatment effect. Among the filters, especially in some of the real-time signal processing requirements of higher power, there are strict restrictions on the size of the occasion, the use of FPGA hardware to achieve a wider range of digital filters. In this paper, adaptive filter from the importance of research to start to introduce the linear adaptive filter algorithm, based on several criteria MMSE or least square error criteria for the study of adaptive filter algorithm, it filters The basic principle and design method of a brief introduction, the final design of FPGA-based design of complex LMS adaptive filter algorithm, the design methods described, and VHDL languages in maxplus simulation test platform.

Keywords: adaptive filter;FPGA;LMS adaptive algorithm;finite impulse response filter xxx大学本科毕业设计·论文

III 目 录 摘 要 ................................................................................................................................... I 1 绪论 .................................................................................................................................. 1 1.1 引 言 ....................................................................................................................... 1 2 自适应算法研究及分析 ................................................................................................... 1 2.1 自适应滤波基本概念 ............................................................................................. 1 2.2 变步长自适应滤波算法 ......................................................................................... 2 2.3 仿射投影算法 ......................................................................................................... 3 2.4 RLS自适应滤波算法 .............................................................................................. 3 2.5 LMS算法及其推广 ................................................................................................. 3 2.6小结.......................................................................................................................... 6 3 滤波器原理介绍............................................................................................................... 7 3.1 自适应滤波器原理 ................................................................................................. 7 3.2 本文滤波器的工作原理 ......................................................................................... 8 4 基于FPGA的自适应滤波器的设计 ............................................................................ 11 4.1 基本设计方法 ....................................................................................................... 11 4.2 设计流程 ............................................................................................................... 12 4.2.1 设计准备 ....................................................................................................................... 13 4.2.2 设计输入 ....................................................................................................................... 13 4.2.3 功能仿真 ....................................................................................................................... 14 4.2.4 设计处理 ....................................................................................................................... 14 4.2.5 时序仿真 ....................................................................................................................... 14 4.2.6 器件编程测试 ............................................................................................................... 14 4.3 自适应滤波器设计 ............................................................................................... 15 4.3.1 自适应滤波器结构 ....................................................................................................... 16 4.3.2 复数滤波器设计与实现 ............................................................................................... 18 4.3.3 基本设计准备 ............................................................................................................... 19 4.3.4 复数自适应滤波器设计防真 ....................................................................................... 22 4.4小结........................................................................................................................ 24 5 结论 ................................................................................................................................ 25 致 谢 .............................................................................................................................. 26 参考文献 ............................................................................................................................ 27