迟滞比较器设计

cmos电压迟滞比较器电路

cmos电压迟滞比较器电路摘要:一、引言二、CMOS 电压迟滞比较器电路的工作原理1.电路结构2.工作原理三、CMOS 电压迟滞比较器的特性1.输入电压范围2.输出电压3.迟滞特性四、CMOS 电压迟滞比较器的应用1.波形发生器2.电压监控器3.逻辑电路五、CMOS 电压迟滞比较器的优缺点1.优点2.缺点六、结论正文:一、引言CMOS 电压迟滞比较器电路是一种广泛应用于电子领域的电压比较器,其具有较高的性能和稳定性,被广泛应用于各种电子设备中。

本文将详细介绍CMOS 电压迟滞比较器电路的工作原理、特性以及应用。

二、CMOS 电压迟滞比较器电路的工作原理1.电路结构:CMOS 电压迟滞比较器电路主要由NMOS 和PMOS 晶体管组成,具有输入端、输出端和电源端。

其核心部分是电压比较器,具有两个输入端和一个输出端。

2.工作原理:当输入电压达到一定值时,比较器将根据输入电压的差异产生不同的输出电压。

具体而言,当输入电压差大于预设阈值时,输出电压为高电平;当输入电压差小于预设阈值时,输出电压为低电平。

三、CMOS 电压迟滞比较器的特性1.输入电压范围:CMOS 电压迟滞比较器具有较宽的输入电压范围,可以满足不同应用场景的需求。

2.输出电压:CMOS 电压迟滞比较器的输出电压具有较大的驱动能力,可以驱动多种负载。

3.迟滞特性:CMOS 电压迟滞比较器具有较好的迟滞特性,能够在一定范围内保持稳定的输出电压。

四、CMOS 电压迟滞比较器的应用1.波形发生器:CMOS 电压迟滞比较器可以产生不同频率和幅度的波形信号,被广泛应用于通信领域。

2.电压监控器:CMOS 电压迟滞比较器可以用于监测电源电压、模拟信号等,具有较高的精度和稳定性。

3.逻辑电路:CMOS 电压迟滞比较器可以与其他逻辑电路器件组合,实现复杂的逻辑功能。

五、CMOS 电压迟滞比较器的优缺点1.优点:CMOS 电压迟滞比较器具有较高的性能、稳定性和可靠性,输入电压范围宽,输出电压驱动能力强,迟滞特性好。

LM339--迟滞比较器

LM339——迟滞比较器一、功能描述本电路是将LM339制作成一个反相迟滞比较器,通过在反相端输入信号,与同相端的基准电压比较,当U+> U-时,输出端相当于开路,输出高电平;当U+<U-时,输出管饱和,相当于输出端接低电平。

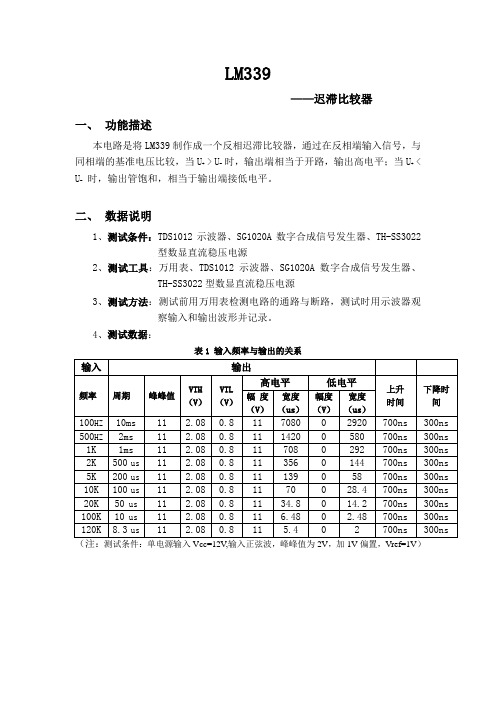

二、数据说明1、测试条件:TDS1012示波器、SG1020A数字合成信号发生器、TH-SS3022型数显直流稳压电源2、测试工具:万用表、TDS1012示波器、SG1020A数字合成信号发生器、TH-SS3022型数显直流稳压电源3、测试方法:测试前用万用表检测电路的通路与断路,测试时用示波器观察输入和输出波形并记录。

4、测试数据:表1 输入频率与输出的关系测试条件:单电源输入Vcc=12V,输入正弦波,峰峰值为2V,加1V偏置,Vref=1V)图1 输入频率与输出的关系表2 输入电压与输出的关系测试条件:单电源输入Vcc=12V,输入正弦波,频率为5K,Vref=1V)5、结果分析:迟滞比较器中加入正反馈可以克服输出端的抖动,所以在输入电压幅值增加时,输出端的幅值没有发生任何改变。

输出电压的幅值不会随频率的改变而改变,但是保持高低电平的时间高度随着频率的增大而减小,并且波形随频率的增大开始产生失真,在我们的测量中,最大可以达到210KHZ。

同时从上面的数据可以看出,上升时间总是大于下降时间。

三、芯片介绍1、芯片特点:内部装有四个独立的电压比较器,工作电源电压范围宽,单电源、双电源均可工作(单电源: 2~36V ,双电源:±1~±18V );消耗电流小,I CC =1.3mA;输入失调电压小,V IO =±2mV ; 共模输入电压范围宽, Vic=0~Vcc-1.5V;输出与TTL ,DTL ,MOS ,CMOS 等兼容; 输出可以用开路集电极连接“或”门.2、芯片用途:满足比较器的基本用途,可以用作单限比较器,迟滞比较器,窗口比较器等,用来比较电压,用得最多的是在电磁炉中,做过压过热保护。

同向迟滞比较器电路

同向迟滞比较器电路同向迟滞比较器电路(hysteresis comparator)是一种常见的电路设计,用于比较输入信号与参考电压并输出相应的逻辑电平。

它在电子设备和系统中广泛应用于电压比较、开关控制和信号处理等领域。

同向迟滞比较器电路能够解决传统比较器电路中的抖动和干扰问题,并提供更稳定可靠的输出。

它通过使用正反馈回路,增加了一个称为迟滞带(hysteresis band)的区域,在输入信号变化时产生一个阈值,这使得比较器只在输入信号超过或低于特定阈值时才能切换输出状态。

在同向迟滞比较器电路中,输入信号与参考电压被连接到一个差分放大器。

差分放大器通过放大输入信号,并将其转换成一个电流或电压信号,再经过一个反馈网络,形成一个正反馈回路。

这个正反馈回路通过改变阈值电压,实现输入信号的比较和输出电平的切换。

正反馈回路通常由一个滞回电阻和一个滞回电容组成,它们决定了比较器电路的迟滞特性。

滞回电阻控制着迟滞带的大小,滞回电容则决定着迟滞带的斜率。

通常情况下,选择合适的滞回电阻和滞回电容可以根据系统需求来调整迟滞带的宽度和响应速度。

同向迟滞比较器电路的优点在于能够抑制输入信号中的噪声和抖动,从而提高系统的稳定性和抗干扰能力。

它适用于需要在信号变化较小的情况下进行精确比较的应用,例如温度传感器、光电传感器和压力传感器等。

在设计同向迟滞比较器电路时,一些注意事项需要被考虑。

首先,选取合适的滞回电阻和滞回电容值,以确保迟滞带的宽度满足系统要求。

其次,特别关注电源电压和输入偏置电流对比较器性能的影响,避免过大的电源电压或输入偏置电流导致误差或不稳定的输出。

此外,考虑到比较器的功耗和速度要求,选择合适的操作放大器和电源电压,使得电路能够在所需的响应速度和功耗范围内工作。

总之,同向迟滞比较器电路是一种功能强大且实用的电路设计,通过增加正反馈回路和迟滞带,解决了传统比较器电路的抖动和干扰问题。

合理选取滞回电阻和滞回电容值,注意电源电压和输入偏置电流对比较器性能的影响,能够确保电路工作稳定可靠。

迟滞比较器原理及计算

迟滞比较器原理及计算迟滞比较器(Hysteresis Comparators)是一种电路器件,用于将一个电压信号进行比较,并在输入信号穿过设定阈值时提供一个输出。

其原理基于正反馈,可以提供一种滞后效应,使得输出在阈值之间有一个死区。

迟滞比较器的原理如下:当输入电压超过上限阈值时,输出切换到高电平,然后输入电压必须降低到下限阈值以下,输出才能切换回低电平。

这种死区效应有助于排除输入信号的噪声,并提高比较器的稳定性。

常见的迟滞比较器电路包括基于运算放大器(OP-AMP)和正反馈电阻网络构成的非反转比较器。

迟滞比较器的工作原理导出了其计算方式。

在理想情况下,假设电压源的输入为V_in,上限阈值为V_upper,下限阈值为V_lower,输出电压为V_out。

则当输入电压超过上限阈值时,输出电压切换为高电平,当输入电压低于下限阈值时,输出电压切换为低电平。

常见的计算方式是基于迟滞比较器的振幅范围(或称为迟滞窗口)来确定。

振幅范围是指上限阈值与下限阈值之间的差值,即V_upper - V_lower。

选择合适的振幅范围可以在输入信号的变化过程中提供适当的抗干扰能力。

为了更好地理解迟滞比较器的计算,可以考虑一个经典的非反转迟滞比较器电路,其中上限阈值为V_upper,下限阈值为V_lower,输入电压为V_in,输出电压由一个比较器和正反馈网络决定。

根据电路设计和正反馈网络的选择,我们可以计算出适当的上限阈值和下限阈值,以及输出状态的切换时刻。

总之,迟滞比较器通过正反馈的设计提供一个滞后效应,使得输出在输入信号穿过设定阈值时有一个死区。

其计算方式可以基于阈值的选择和正反馈网络的特性来确定。

迟滞比较器被广泛应用于各种电子设备和电路,如电压比较、斜率计算器、峰值检测等领域。

proteus滞回比较器电路设计

Proteus滞回比较器电路设计1.引言比较器是一种常见的电子元件,用于将输入信号与一个基准值进行比较,并输出对应的逻辑电平。

滞回比较器是一种特殊类型的比较器,其输出状态在输入信号经过基准值时会发生突变,从而产生滞回现象。

本文将介绍如何在P ro te us软件中设计一个滞回比较器电路。

2.硬件设计2.1元件选择在设计滞回比较器电路时,我们需要选择合适的元件。

以下是一些常用的元件:-运算放大器(O p-Am p):用于放大输入信号,并产生滞回效应;-电阻:用于设置滞回比较器的阈值;-二极管:用于限制电压范围;-耦合电容:用于隔离直流偏置。

2.2电路连接在P ro te us中,我们可以使用V i rt ua lI ns tr um ent(VI)&PC BD es ig n软件来进行电路设计和仿真。

1.打开Pr ot eu s软件,并创建一个新的工程文件。

2.在C om po ne nt s栏中选择合适的元件,并将其拖放到工作区。

3.连接元件的引脚以构建滞回比较器电路。

-运算放大器的非反馈输入端连接到输入信号源,反馈输入端与输出端连接。

-通过电阻将反馈输入端与滞回比较器的阈值连接。

-使用二极管和耦合电容对输入信号进行限制和隔离。

4.完成电路设计后,保存并命名文件。

3.电路仿真3.1设置仿真参数在P ro te us中进行电路仿真前,需设置仿真参数以确保正确的模拟结果。

1.在工具栏中选择"P r ot eu sV SM Si mu lat i on"。

2.在仿真设置对话框中,设置仿真时长、采样频率和仿真步长等参数。

3.2运行仿真1.在工具栏中选择"R u nS im ul at io n"按钮,开始执行电路仿真。

2.检查仿真结果,观察滞回比较器的输出变化。

4.仿真结果分析通过Pr ot eu s仿真得到的结果可以帮助我们对滞回比较器电路的性能进行评估和优化。

迟滞比较器电路课程设计

迟滞比较器电路课程设计一、课程目标知识目标:1. 让学生掌握迟滞比较器电路的基本原理,理解其工作状态及特点。

2. 使学生了解迟滞比较器在模拟电子技术中的应用,掌握相关电路分析方法。

3. 帮助学生掌握迟滞比较器电路参数对电路性能的影响,能够进行简单的参数计算。

技能目标:1. 培养学生能够运用所学知识设计简单的迟滞比较器电路,具备实际操作能力。

2. 培养学生通过仿真软件对迟滞比较器电路进行仿真分析,提高实践操作能力。

3. 提高学生运用所学知识解决实际问题的能力,培养创新思维和团队协作精神。

情感态度价值观目标:1. 培养学生对电子技术的兴趣,激发学生学习热情,形成主动学习的态度。

2. 培养学生严谨的科学态度,注重实验数据的真实性,遵循实验操作规范。

3. 增强学生的环保意识,培养学生节约资源、爱护公共财物的价值观。

课程性质分析:本课程为电子技术基础课程,通过学习迟滞比较器电路,使学生掌握模拟电子技术的基本知识,为后续相关课程学习打下基础。

学生特点分析:学生具备一定的电子技术基础知识,具有较强的学习能力和动手操作欲望,对实际应用有较高的兴趣。

教学要求:1. 理论联系实际,注重培养学生的实践操作能力。

2. 注重启发式教学,引导学生主动思考,培养解决问题的能力。

3. 强化团队合作,培养学生的沟通与协作能力。

二、教学内容1. 迟滞比较器电路原理:讲解迟滞比较器的定义、工作原理,分析其与普通比较器的区别和优势。

- 教材章节:第二章第四节“迟滞比较器”2. 迟滞比较器电路分析:介绍迟滞比较器的电路结构,分析电路中各个元件的作用,探讨不同参数对电路性能的影响。

- 教材章节:第二章第五节“迟滞比较器的性能分析”3. 迟滞比较器电路设计:讲解如何根据实际需求设计迟滞比较器电路,包括参数计算、元件选型等。

- 教材章节:第二章第六节“迟滞比较器的设计与应用”4. 迟滞比较器电路仿真:指导学生使用仿真软件(如Multisim、Proteus 等)对迟滞比较器电路进行仿真分析,验证理论知识的正确性。

迟滞比较器运算

迟滞比较器运算

滞回比较器又称迟滞比较器,是一个具有迟滞回环传输特性的比较器。

它的运算过程相对复杂,下面以一个实例进行说明:

假设要设计一个电池欠压保护电路,该电路使用双阈值迟滞比较器,以18.5V作为低阈值电压,高阈值电压在18.5V到24V之间,即选择21V作为高阈值电压。

首先,确定比较器的负输入端。

通过两个分压电阻进行分压,这两个分压电阻的取值既不能过大也不能过小。

电池的阈值设置为18.5V到21V,而电池标称电压值为24V,最大值为29V,综合考虑后选择在21V时保证流过分压电阻的电流为1mA左右。

因此,选择R1=20K,R6=1K。

其次,计算阈值电压变化时U1的值。

当BATT=18.5V时,U1=18.5乘以R6/R1+R6=0.88V;当BATT=21.0V时,U1=21.0乘以

R6/R1+R6=1V。

然后,计算比较器输出高电平和低电平时的等效电路。

当U1=0.88V 时,比较器输出低电平,忽略R3、R4支路,此时电源电压为5V,保持电路1mA电流,可确定R5+R2等于5K上下,选择R5=1K,

R2=4K。

最后,确定R3的阻值。

通过以上步骤,就可以完成双阈值迟滞比较器的运算。

需要注意的是,上述示例仅为基本原理,实际运算过程中还需要考虑许多因素,如输入信号的频率、噪声、比较器的响应时间等。

cmos电压迟滞比较器电路

cmos电压迟滞比较器电路摘要:一、引言二、CMOS 电压迟滞比较器电路的工作原理1.基本结构2.工作原理三、CMOS 电压迟滞比较器电路的特性1.输入电压范围2.输出电压3.灵敏度四、CMOS 电压迟滞比较器电路的应用1.电源监控电路2.窗口比较器五、CMOS 电压迟滞比较器电路的设计1.设计步骤2.设计实例六、总结正文:一、引言CMOS 电压迟滞比较器电路是一种广泛应用于电子设备中的电路,具有较高的性能和较低的功耗。

本篇文章将详细介绍CMOS 电压迟滞比较器电路的工作原理、特性、应用以及设计方法。

二、CMOS 电压迟滞比较器电路的工作原理1.基本结构CMOS 电压迟滞比较器电路主要由NMOS 和PMOS 晶体管组成。

其中,NMOS 晶体管作为负载,PMOS 晶体管作为传输门。

此外,还有一个参考电压源用于提供基准电压。

2.工作原理当输入电压高于基准电压时,PMOS 晶体管导通,使得NMOS 晶体管的导通电阻减小,从而使得输出电压上升;反之,当输入电压低于基准电压时,PMOS 晶体管截止,使得NMOS 晶体管的导通电阻增大,从而使得输出电压下降。

三、CMOS 电压迟滞比较器电路的特性1.输入电压范围CMOS 电压迟滞比较器电路的输入电压范围较宽,可以满足不同应用场景的需求。

2.输出电压CMOS 电压迟滞比较器电路的输出电压具有较高的分辨率,可以实现较高的比较精度。

3.灵敏度CMOS 电压迟滞比较器电路的灵敏度较高,可以实现对输入电压的快速响应。

四、CMOS 电压迟滞比较器电路的应用1.电源监控电路CMOS 电压迟滞比较器电路可以用于监控电源电压,当电源电压发生波动时,通过控制相应的电路开关实现对电源电压的稳定。

2.窗口比较器CMOS 电压迟滞比较器电路可以应用于窗口比较器,实现对输入信号的波形检波和幅度比较。

五、CMOS 电压迟滞比较器电路的设计1.设计步骤CMOS 电压迟滞比较器电路的设计主要包括确定电路结构、选择合适的元件参数以及进行仿真验证等步骤。

利用迟滞比较器实现蓄电池充放电电路设计

利用迟滞比较器实现蓄电池充放电电路设计蓄电池是一种能够储存电能的装置,广泛应用于车辆、太阳能系统和备用电源等领域。

为了有效地控制蓄电池的充放电过程,通常需要使用比较器来监测和调节电压。

而迟滞比较器是一种特殊的比较器,能够提供一定的带电压差的滞后效果,从而可以有效地控制电压的波动。

本文将使用迟滞比较器设计一个蓄电池充放电电路,并详细介绍其原理和实现过程。

首先,我们需要确定蓄电池的充电电压范围和充电电流。

假设我们使用的是一个12V的铅酸蓄电池,其最大充电电压为14.4V,最大充电电流为2A。

在设计充电电路时,我们希望能够实现以下功能:-当蓄电池电压低于13.6V时,启动充电过程;-当蓄电池电压达到14.4V时,停止充电过程;-充电电流控制在2A以内。

为了实现以上功能,我们可以设计如下的充电电路:首先,使用一个交流-直流电源将交流电转换为12V的直流电压,作为充电电源。

接下来,将电源的正极连接到一个迟滞比较器的正极引脚,同时将蓄电池的正极连接到比较器的负极引脚。

通过调节比较器的阈值电压和迟滞时间,可以实现对蓄电池的充电控制。

当蓄电池电压低于13.6V时,比较器输出低电平,启动充电过程;当蓄电池电压达到14.4V时,比较器输出高电平,停止充电过程。

同时,通过连接一个电流传感器到充电回路中,可以实时监测电流大小,从而控制充电电流在2A以内。

在设计放电电路时-当蓄电池电压低于11.0V时,停止放电过程;-放电电流控制在2A以内。

为了实现以上功能,我们可以设计如下的放电电路:首先,将蓄电池的正负极连接到一个迟滞比较器中,同时连接一个电流传感器到放电回路中。

通过调节比较器的阈值电压和迟滞时间,可以实现对蓄电池的放电控制。

当蓄电池电压低于11.0V时,比较器输出高电平,停止放电过程;当蓄电池电压达到11.5V时,比较器输出低电平,启动放电过程。

同时,通过电流传感器监测放电电流大小,控制放电电流在2A以内。

通过以上设计,我们可以实现对蓄电池充放电过程的有效控制,保证蓄电池的使用安全和稳定性。

LM339--迟滞比较器

LM339——迟滞比较器一、功能描述本电路是将LM339制作成一个反相迟滞比较器,通过在反相端输入信号,与同相端的基准电压比较,当U+> U-时,输出端相当于开路,输出高电平;当U+<U-时,输出管饱和,相当于输出端接低电平。

二、数据说明1、测试条件:TDS1012示波器、SG1020A数字合成信号发生器、TH-SS3022型数显直流稳压电源2、测试工具:万用表、TDS1012示波器、SG1020A数字合成信号发生器、TH-SS3022型数显直流稳压电源3、测试方法:测试前用万用表检测电路的通路与断路,测试时用示波器观察输入和输出波形并记录。

4、测试数据:表1 输入频率与输出的关系测试条件:单电源输入Vcc=12V,输入正弦波,峰峰值为2V,加1V偏置,Vref=1V)图1 输入频率与输出的关系表2 输入电压与输出的关系测试条件:单电源输入Vcc=12V,输入正弦波,频率为5K,Vref=1V)5、结果分析:迟滞比较器中加入正反馈可以克服输出端的抖动,所以在输入电压幅值增加时,输出端的幅值没有发生任何改变。

输出电压的幅值不会随频率的改变而改变,但是保持高低电平的时间高度随着频率的增大而减小,并且波形随频率的增大开始产生失真,在我们的测量中,最大可以达到210KHZ。

同时从上面的数据可以看出,上升时间总是大于下降时间。

三、芯片介绍1、芯片特点:内部装有四个独立的电压比较器,工作电源电压范围宽,单电源、双电源均可工作(单电源: 2~36V ,双电源:±1~±18V );消耗电流小,I CC =1.3mA;输入失调电压小,V IO =±2mV ; 共模输入电压范围宽, Vic=0~Vcc-1.5V;输出与TTL ,DTL ,MOS ,CMOS 等兼容; 输出可以用开路集电极连接“或”门.2、芯片用途:满足比较器的基本用途,可以用作单限比较器,迟滞比较器,窗口比较器等,用来比较电压,用得最多的是在电磁炉中,做过压过热保护。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

迟滞比较器设计

1.

设计需求分析:

电路工作描述:例如:当Vin<300mmHg 压力对应电压值(如:2.7V)时,Vout 为低电平,当Vin>2.7V 时,Vout 为高电平,使Q7导通,Valve 信号为低电平,气阀打开。

直到Vin<0.3V 时,Vout 才恢复为低电平。

血压模块过压保护电路模型如下:

说明:图中Vin 为压力传感器压力电压值

对应于迟滞比较器的电压传输特性图,VTL=0.3V ,VTH=2.7V ,VOL=0V ,VOH=VCC 。

2.电路模型计算:

从电压传输特性图可以看出,Vout=VOL 时,Vin=VTH 。

由运放的虚短和虚断特性可以

得出,其中

2

R VCC Vref +=()1

*IRin IRf

IRin 算式VOL Rin Vref Rf Rin VTH Rf

VOL

Vref Rin Vref VTH VOL Vref IRf Rin Vref

VTH −+=

−=

−−=

−=

=当Vout=VOH 时,Vin=VTL ,同理可得。

()2*IRin IRf

IRin 算式Rf VOH Rin Vref Rf Rin VTL Rf

VOH

Vref Rin Vref VTL Rf

VOH Vref IRf Rin Vref

VTL −+=

−=

−−=

−=

=

将VTH 与VTL 相减得:()3

........*算式Rf

Rin VOL VOH VTL VTH −=

−将需求分析中的VTL=0.3V ,VTH=2.7V ,VOL=0V ,VOH=VCC(实际为3.3V),代入上面的算式3中,可得4..........375.1算式Rin Rf =。

将算式4代入算式1中,可得到Vref=1.563V

3.

参数选择:

v

R1,R2电阻的选择:根据2

12

*

R R R VCC Vref +=R1=1.111*R2。

考虑到实际电

阻阻值和功耗方面要求,有以下电阻可选:

R 2(K Ω)

R 1(K Ω)22.2222.22.444233.3335.15.66612022.222224.4423033.335156.661300333.3510

566.61

为了达到精确的目的,可以用两个串联电阻代替R1。

v

Rin 和Rf 的选择:根据Rin Rf *375.1=,考虑到实际电阻阻值,功耗,系统电路影响等方面要求,有以下电阻可选:

R i n (K Ω)R f (K Ω)1.52.062522.752.23.0252.43.32230.2524

33

4.仿真验证:

仿真工具:MultiSIM 10.0,电路原理图及仿真结果如下图所示:

从仿真结果来看,R1=33K,R2=30K,Rin=24K和Rf=33K这个参数组合,可以满足电路功能。