3D封装与硅通孔TSV工艺技术

电子封装总结报告范文

一、报告背景随着电子技术的飞速发展,电子产品的性能和功能不断提升,对电子封装技术的要求也越来越高。

电子封装技术作为电子产品的重要组成部分,对于提高电子产品的可靠性、稳定性和性能具有重要意义。

本报告旨在总结近年来电子封装技术的发展现状,分析存在的问题,并提出未来发展趋势。

二、电子封装技术发展现状1. 3D封装技术近年来,3D封装技术成为电子封装领域的研究热点。

3D封装技术通过垂直堆叠多个芯片,提高了芯片的集成度和性能。

目前,3D封装技术主要分为硅通孔(TSV)、倒装芯片(FC)和异构集成(Heterogeneous Integration)等类型。

2. 基于纳米技术的封装技术纳米技术在电子封装领域的应用越来越广泛,如纳米压印、纳米自组装等。

这些技术可以提高封装的精度和性能,降低制造成本。

3. 新型封装材料新型封装材料的研究和应用为电子封装技术的发展提供了有力支持。

例如,聚酰亚胺(PI)、聚对苯二甲酸乙二醇酯(PET)等材料在高温、高压、高频等环境下具有优异的性能。

4. 封装测试与可靠性随着电子封装技术的不断发展,封装测试与可靠性研究成为重点关注领域。

通过测试和评估封装性能,确保电子产品的质量和可靠性。

三、存在的问题1. 封装成本较高随着封装技术的不断发展,封装成本逐渐提高。

如何降低封装成本,提高性价比成为电子封装领域的重要课题。

2. 封装可靠性问题电子封装技术在高温、高压等恶劣环境下容易产生可靠性问题。

如何提高封装的可靠性,延长产品使用寿命成为研究重点。

3. 封装工艺复杂电子封装工艺复杂,涉及多个环节。

如何优化封装工艺,提高生产效率成为电子封装领域的一大挑战。

四、未来发展趋势1. 高性能封装技术未来电子封装技术将朝着高性能、低功耗、小型化方向发展。

例如,硅通孔(TSV)技术将继续发展,以满足更高集成度的需求。

2. 绿色封装技术随着环保意识的不断提高,绿色封装技术将成为电子封装领域的重要发展方向。

例如,可回收、可降解的封装材料将得到广泛应用。

tsv的主要工艺步骤及方法

tsv的主要工艺步骤及方法一、制造硅通孔硅通孔(TSV)的制造是TSV技术的核心步骤之一。

在这一步,通过物理或化学方法在芯片上制造出穿透硅片的孔洞,这些孔洞将用于实现芯片间的垂直互连。

有多种方法可以用来制造硅通孔,包括但不限于深反应离子刻蚀(DRIE)、激光钻孔等。

二、填充硅通孔在硅通孔制造完成后,需要对其进行填充,以实现电信号的传输。

填充材料一般选用导电金属,如铜、钨等。

填充硅通孔的方法有化学气相沉积(CVD)、物理气相沉积(PVD)和电镀等。

选择合适的填充方法需要根据实际应用需求和工艺条件来决定。

三、连接硅通孔填充完硅通孔后,需要进行硅通孔间的连接,以实现芯片间的互连。

连接方法可以采用焊接、导电胶等。

在连接过程中,需要确保连接稳定可靠,以防止在后续使用中出现脱落或接触不良等问题。

四、测试与验证在完成硅通孔的制造、填充和连接后,需要进行测试与验证,以确保TSV 技术能够满足实际应用需求。

测试内容包括但不限于:导通性能测试、机械性能测试和可靠性测试等。

通过测试与验证,可以及时发现并解决潜在的问题,提高TSV技术的可靠性和稳定性。

五、封装与集成在TSV技术应用中,封装与集成是关键步骤之一。

通过封装与集成,可以将多个芯片垂直堆叠在一起,实现更小体积、更高性能的电子系统。

在封装与集成过程中,需要考虑到散热、信号传输、电源分配等问题,以确保整个系统的稳定运行。

六、可靠性评估TSV技术的可靠性是评估其性能的重要指标之一。

可靠性评估可以通过多种方法来实现,如加速老化试验、环境适应性试验等。

通过可靠性评估,可以了解TSV技术在不同环境和工作条件下的性能表现,为后续改进和优化提供依据。

七、失效分析失效分析是TSV技术中重要的一环,通过对失效样品的检测和分析,可以了解失效的原因和机制,从而提出相应的改进措施。

失效分析方法包括扫描电子显微镜(SEM)、能谱分析(EDS)等。

通过失效分析,可以提高TSV技术的可靠性和稳定性,为实际应用提供更加可靠的解决方案。

TSV工艺技术

TSV工艺技术TSV(Through Silicon Via)工艺技术是一种用于三维集成电路中的先进封装技术。

这种技术通过在硅片上钻孔,然后在孔中填充金属,实现了不同层次芯片之间的电连接,从而实现了高密度的芯片封装和高速数据传输。

TSV工艺技术具有许多优点。

首先,它可以提供更高的集成密度。

传统的芯片封装技术中,芯片仅能在一个平面上布置,而TSV技术使得芯片的多层堆叠成为可能。

通过将多个芯片垂直堆叠在一起,可以有效地提高芯片的整体集成度。

其次,TSV技术还可以提供更短的信号传输路径,减少信号传输延迟。

因为TSV是直接通过硅片内部传输信号,相比于传统的外部线路,信号的传输路径更短,从而能够提供更高的数据传输速率。

另外,TSV还可以减少芯片之间的串扰,提高电路的稳定性和可靠性。

TSV工艺技术的实现主要包括三个步骤:孔钻孔、金属填充和封装。

首先,通过激光钻孔或机械钻孔的方式,在硅片上形成所需的孔洞。

这一步骤需要高度精确的控制,以避免对芯片造成损伤。

接下来,将金属填充到孔洞中。

填充材料通常选择铜或钨,因为它们具有良好的导电性能。

填充金属可以使用物理气相沉积或浸涂的方法,以确保孔洞充满金属。

最后,将填充完毕的芯片进行封装,以保护芯片和TSV结构。

TSV工艺技术在电子行业中有广泛应用。

首先,它可以提高芯片的性能和功能。

通过TSV技术,不同功能的芯片可以堆叠在一起,并通过TSV连接进行互联,从而实现更复杂的电路功能。

其次,TSV技术可以减小芯片尺寸。

由于芯片堆叠在一起,芯片的整体尺寸可以减小,从而实现更小型化的设备。

此外,TSV技术还可以降低能耗。

由于TSV可以提供更短的信号传输路径,电路的响应速度更快,功耗更低。

最后,TSV 工艺技术为芯片的延伸和升级提供了可能。

当芯片发展到一定阶段,无法再单独升级时,可以通过TSV连接新的芯片层来实现升级,延长设备的使用寿命。

总之,TSV工艺技术是一种用于三维集成电路中的高级封装技术。

TSV技术

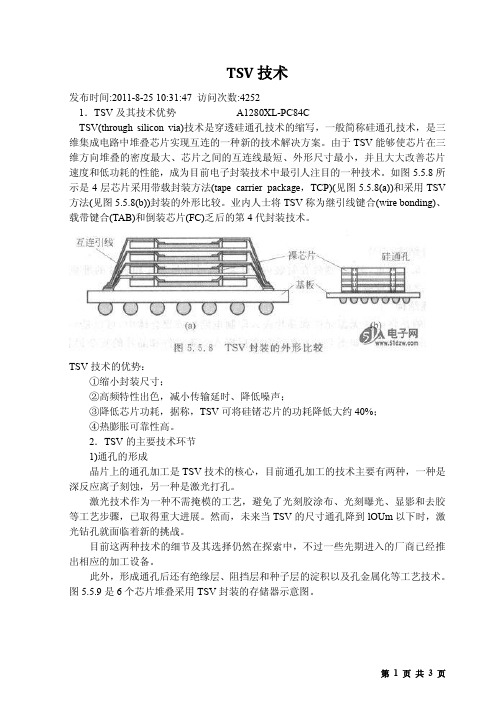

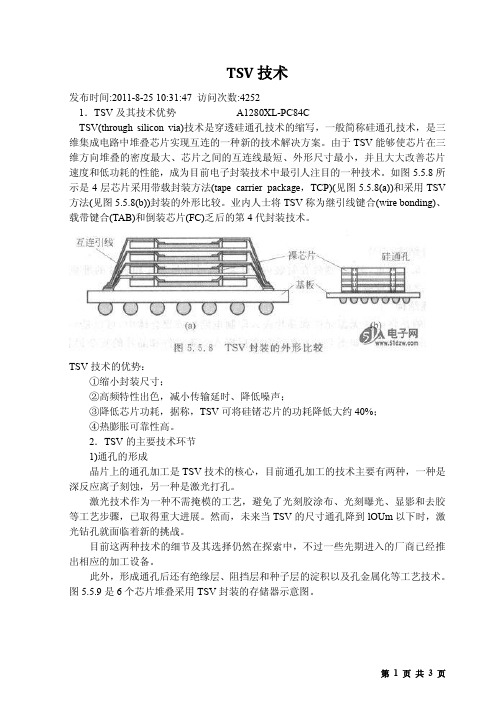

TSV技术发布时间:2011-8-25 10:31:47 访问次数:42521.TSV及其技术优势A1280XL-PC84CTSV(through silicon via)技术是穿透硅通孔技术的缩写,一般简称硅通孔技术,是三维集成电路中堆叠芯片实现互连的一种新的技术解决方案。

由于TSV能够使芯片在三维方向堆叠的密度最大、芯片之间的互连线最短、外形尺寸最小,并且大大改善芯片速度和低功耗的性能,成为目前电子封装技术中最引人注目的一种技术。

如图5.5.8所示是4层芯片采用带载封装方法(tape carrier package,TCP)(见图5.5.8(a))和采用TSV 方法(见图5.5.8(b))封装的外形比较。

业内人士将TSV称为继引线键合(wire bonding)、载带键合(TAB)和倒装芯片(FC)乏后的第4代封装技术。

TSV技术的优势:①缩小封装尺寸;②高频特性出色,减小传输延时、降低噪声;③降低芯片功耗,据称,TSV可将硅锗芯片的功耗降低大约40%;④热膨胀可靠性高。

2.TSV的主要技术环节1)通孔的形成晶片上的通孔加工是TSV技术的核心,目前通孔加工的技术主要有两种,一种是深反应离子刻蚀,另一种是激光打孔。

激光技术作为一种不需掩模的工艺,避免了光刻胶涂布、光刻曝光、显影和去胶等工艺步骤,已取得重大进展。

然而,未来当TSV的尺寸通孔降到lOUm以下时,激光钻孔就面临着新的挑战。

目前这两种技术的细节及其选择仍然在探索中,不过一些先期进入的厂商已经推出相应的加工设备。

此外,形成通孔后还有绝缘层、阻挡层和种子层的淀积以及孔金属化等工艺技术。

图5.5.9是6个芯片堆叠采用TSV封装的存储器示意图。

2)晶片减薄如果不用于3D封装,目前0.3~0.4mm的晶片厚度没有问题,但如果晶片用于3D封装则需要减薄,以保证形成通孔的孔径与厚度比例在合理范围,并且最终封装的厚度可以接受。

即使不考虑层堆叠的要求,单是芯片间的通乳互连技术就要求上层芯片的厚度在20~30μm,这是现有等离子开孔及金属沉积技术比较适用的厚度。

半导体tsv工艺

半导体tsv工艺

半导体TSV工艺是一种新型的三维封装技术,它是通过在晶圆上开孔,将芯片内部的电路通过垂直连接器连接到晶圆的另一侧,从而实现芯片内部电路的三维堆叠。

TSV是Through Silicon Via的缩写,意为通过硅通孔。

半导体TSV工艺是一种先进的封装技术,它可以将多个芯片进行堆叠,从而实现更高的性能和更小的封装尺寸。

相比传统的封装技术,半导体TSV工艺具有以下优点:

1.更高的性能:半导体TSV工艺可以将多个芯片堆叠在一起,从而实现更高的性能。

由于芯片之间的距离更近,信号传输速度更快,同时也减少了信号传输的损失。

2.更小的封装尺寸:半导体TSV工艺可以将多个芯片堆叠在一起,从而实现更小的封装尺寸。

这对于移动设备等小型电子产品来说非常有利,可以实现更小巧的设计。

3.更低的功耗:半导体TSV工艺可以实现更短的信号传输路径,从而减少功耗。

这对于需要长时间使用的电子产品来说非常有利。

半导体TSV工艺的制造过程包括以下步骤:

1.晶圆准备:首先需要准备好晶圆,并在晶圆上进行刻蚀和清洗等处理,以便后续的工艺步骤。

2.TSV开孔:在晶圆上开孔,通过硅通孔将芯片内部的电路连接到晶圆的另一侧。

3.金属填充:将金属填充到开孔中,以便后续的连接。

4.封装:将多个芯片堆叠在一起,并进行封装,以保护芯片并提高性能。

半导体TSV工艺是一种非常先进的封装技术,它可以实现更高的性能和更小的封装尺寸。

随着电子产品的不断发展,半导体TSV工艺将会越来越广泛地应用于各种领域。

硅通孔(TSV)电学传输特性分析与优化

硅通孔(TSV)电学传输特性分析与优化硅通孔(TSV)电学传输特性分析与优化摘要:硅通孔(TSV)是一种用于芯片内部互联的三维封装技术。

本文通过对TSV电学传输特性的分析与优化,探讨了TSV的制备工艺对其性能的影响,并提出了一些优化措施。

1. 引言随着芯片尺寸的不断减小和集成度的不断提高,二维封装方式逐渐不能满足芯片内部大规模互联的需求。

硅通孔(TSV)作为一种三维封装技术,能够实现芯片内部的垂直互联,为芯片的高集成度提供可能。

TSV的电学传输特性的分析与优化对于实现高性能的三维封装至关重要。

2. TSV的制备工艺TSV的制备通常包括刻蚀、填充和研磨等步骤。

刻蚀是将硅衬底上的孔洞形成的过程,可以采用干法或湿法刻蚀。

填充是将导电材料填充到TSV中,常用的填充材料有铜、银等。

研磨是将填充材料的余量删减至需要的高度,以便与芯片的上下层相连接。

制备工艺的参数设置和优化对于TSV的电学传输特性具有重要影响。

3. TSV的电学传输特性分析TSV的电学传输特性可以通过测试TSV的电阻和电容来进行分析。

电阻是TSV的主要电学性能指标之一,影响着信号传输的速度和功耗。

电阻的大小与TSV的尺寸、填充材料和制备工艺等因素有关。

电容是TSV的另一个重要性能指标,反映了TSV 的电荷传输能力。

电容的大小与TSV的尺寸、绝缘层的厚度等因素相关。

4. TSV的电学传输特性优化为了优化TSV的电学传输特性,可以采取以下措施:4.1 优化制备工艺参数制备工艺参数的优化对于TSV的电学性能具有重要影响。

如刻蚀参数的优化可以改善TSV的表面平整度,减小接触电阻。

填充材料的选择和填充参数的优化可以改善TSV的导电性能。

研磨参数的优化可以减小TSV的表面粗糙度,降低剩余电阻。

4.2 优化填充材料填充材料的选择对TSV的电阻有着重要影响。

铜是一种常用的填充材料,具有较低的电阻和较高的导电性能。

然而,铜容易产生应力,导致TSV的可靠性下降。

TSV技术

TSV技术发布时间:2011-8-25 10:31:47 访问次数:42521.TSV及其技术优势A1280XL-PC84CTSV(through silicon via)技术是穿透硅通孔技术的缩写,一般简称硅通孔技术,是三维集成电路中堆叠芯片实现互连的一种新的技术解决方案。

由于TSV能够使芯片在三维方向堆叠的密度最大、芯片之间的互连线最短、外形尺寸最小,并且大大改善芯片速度和低功耗的性能,成为目前电子封装技术中最引人注目的一种技术。

如图5.5.8所示是4层芯片采用带载封装方法(tape carrier package,TCP)(见图5.5.8(a))和采用TSV 方法(见图5.5.8(b))封装的外形比较。

业内人士将TSV称为继引线键合(wire bonding)、载带键合(TAB)和倒装芯片(FC)乏后的第4代封装技术。

TSV技术的优势:①缩小封装尺寸;②高频特性出色,减小传输延时、降低噪声;③降低芯片功耗,据称,TSV可将硅锗芯片的功耗降低大约40%;④热膨胀可靠性高。

2.TSV的主要技术环节1)通孔的形成晶片上的通孔加工是TSV技术的核心,目前通孔加工的技术主要有两种,一种是深反应离子刻蚀,另一种是激光打孔。

激光技术作为一种不需掩模的工艺,避免了光刻胶涂布、光刻曝光、显影和去胶等工艺步骤,已取得重大进展。

然而,未来当TSV的尺寸通孔降到lOUm以下时,激光钻孔就面临着新的挑战。

目前这两种技术的细节及其选择仍然在探索中,不过一些先期进入的厂商已经推出相应的加工设备。

此外,形成通孔后还有绝缘层、阻挡层和种子层的淀积以及孔金属化等工艺技术。

图5.5.9是6个芯片堆叠采用TSV封装的存储器示意图。

2)晶片减薄如果不用于3D封装,目前0.3~0.4mm的晶片厚度没有问题,但如果晶片用于3D封装则需要减薄,以保证形成通孔的孔径与厚度比例在合理范围,并且最终封装的厚度可以接受。

即使不考虑层堆叠的要求,单是芯片间的通乳互连技术就要求上层芯片的厚度在20~30μm,这是现有等离子开孔及金属沉积技术比较适用的厚度。

三维集成电路(3D IC)中硅通孔(TSV)链路的多场分析

三维集成电路(3D IC)中硅通孔(TSV)链路的多场分析三维集成电路(3D IC)中硅通孔(TSV)链路的多场分析引言:随着电子技术的不断发展,集成电路的功能越来越复杂,对于电路板的布局和连接的要求也越来越高。

传统的2D集成电路已经面临着功耗、散热和信号传输等问题,为了克服这些问题,人们提出了3D集成电路(3D IC)的概念。

3D IC通过垂直堆叠多层芯片来实现更高的集成度和性能。

而硅通孔(TSV)链路作为3D IC中芯片间的关键连接组件,受到了广泛关注。

本文将对TSV链路进行多场分析,探讨其在3D IC中的性能和优化方法。

1. TSV链路的结构与工作原理TSV链路是一种通过在不同芯片间钻孔并填充导电材料的技术,用于实现芯片间的电信号传输和能量供应。

典型的TSV链路结构包括导电填充物、绝缘层以及TSV孔的孔壁。

TSV链路的工作原理是通过导电填充物提供电信号和能量传输的路径,而绝缘层则用于隔离相邻的TSV链路。

2. TSV链路的挑战与问题尽管TSV链路在3D IC中起到了关键的作用,但是它也带来了一些挑战与问题。

首先,TSV孔的填充过程需要解决填充物与孔壁之间的黏附性和填充度的问题。

其次,在高频电信号传输方面,TSV链路可能会引起信号的损耗和噪声,从而影响系统性能。

另外,由于3D IC中芯片的堆叠密度较高,TSV链路的散热问题也不可忽视。

3. TSV链路的多场分析方法为了解决上述问题,人们利用电磁场理论、热传导理论和机械力学理论等多场分析方法对TSV链路进行研究。

在电磁场方面,可以通过研究TSV链路的等效电路模型和传输线理论来分析电信号的传输损失和噪声问题。

在热传导方面,可以通过模拟TSV链路的热传导路径和热源来分析散热性能。

在机械力学方面,可以分析TSV链路在机械应力下的稳定性和可靠性。

4. TSV链路的优化方法为了提高TSV链路的性能,人们提出了一系列的优化方法。

例如,在TSV孔填充过程中可以选择合适的填充材料和填充工艺,以提高填充度和黏附性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

强V键合采用工艺有金属—金属键合技术和高 分子粘结键合等。金属一金属键合技术有一种趋 势,因为这种技术可以同时实现机械和电学的接触 界面。如铜一铜键合在350℃一400℃温度下施加 压力超过30 rain,接着在350℃一400℃下的氮气 气氛退火30 min一60 min完成。这种技术使用金属 对TSV进行封帽,之后采用氧化物和金属同步CMP 进行平坦化,经过专利保护的表面处理技术,可使用 标准的键合/对准机在大气环境下1 min一2 min实 现芯片或者晶圆的键合。在350 oC温度下施加压 力,在低CoO键合操作下可以获得单一的金属界

大多数3D—IC工艺中,单个Ic的厚度要求都

远低于75 Ixm。减薄器件晶圆成为很重要的工艺之

一。减薄技术面临的首要挑战就是超薄化工艺所要

求的<50斗m的减薄能力。传统上,减薄工艺仅仅

需要将硅片从晶圆加工完成时的原始厚度减薄到

300斗m~400斗m。在这个厚度上,硅片仍然具有相

当的厚度来容忍减薄工程中的磨削对硅片的损伤及

所谓MCM一3D技术.就是在高密度多层互连 基板上,采用微焊接和封装工艺将构成电子电路的 各种微型元器件(Ic裸芯片及片式元器件)进行三 维立体组装,形成高密度、高性能和高可靠性的微电 子产品(包括组件、部件、子系统和系统)。按照 MCM基板材料技术可分为三类:MCM—L采用层压 有机基材,制造基于普通印制板技术,如图l(a)所

对于逻辑电路上存储器传统的二维处理器架 构,在同一芯片上包含∞和£1级缓存作为处理器 核,而将也级缓存放在另一个独立的芯片上。因此 处理器核与缓存间的互连可能会比较长,在一些情 况下,将导致在数据从一端传递到另一端之前经历 多个时钟周期。在多核处理器系统中,为避免这种 速度问题所需的巨大带宽,也会采用能够缩短互连 长度的TSV技术,使用该技术,不同尺寸的芯片叠 层在一起提高品质性能,成为芯片与圆片叠层逻辑 电路加存储器应用的最佳选择。还有的芯片制造商 如Intel同时关注逻辑电路加存储器的叠层和逻辑 电路加逻辑电路的叠层方式,前者包括将缓存和主 存叠层在高性能逻辑器件之上,而后者则是将一个 完整的逻辑电路拆分到两个或更多的器件层上,将 会需要使用比莳者更小的互连节距。

第30卷第6期 2009年11月

电子工艺技术

Electronics Pfoc妫s Technology

3D封装与硅通孔(TSV)工艺技术

郎鹏,高志方,牛艳红

(太原风华信息装备殷份有限公司,山西 太原030024)

摘要:在Ic制造技术受到物理极限挑战的今天,3D封装技术越来越成为了微电子行业关 注的热点。对3D封装技术结构特点、主流多层基板技术分类及其常见键舍技术的发展作了论述,

the strong demands around 2015.

Key words:3D package;Through·-silicon——via;IC manufacturing

Document Code:A

Article ID:1001—3474(2009)06—0323一04

由于MCM一3D封装技术在组装密度、信号传 输速度、电性能以及可靠性等方面独具优势,目前已 成为能最大限度地提高集成度和提高高速单片IC 性能,制作高速电子系统,实现整机小型化、多功能 化、高可靠性和高性能的最有效途径¨。J。

Technology of 3 D Packaging and TSV

LANG Peng,GAO Zhi—fang,Niu Yah—hong

(Taiyuan Fenguha Information—equipment Co.,LTD,Taiyuan 030024,China)

Abstract:IC manufacturing faced the challenges of physical limits,3D packaging technology has in—

ver the past few years,Especially,髑V key technologies,such嬲wafer thinning technology,through—hole

manufacturing technology and bonding technology.Give out the 7rSV technology development trend with

换‘6‘。

,

激光技术作为一种不需掩膜的工艺,避免了光

刻胶涂布、光刻曝光、显影和去胶等工艺步骤,已取

得重大进展。三星(韩国)已经在存储器叠层中采

用了这一技术。激光加工系统供应商Xsil公司(爱 尔兰)为偈V带来了最新解决方案,Xsil称激光钻

孔工艺将首先应用到低密度闪存及CMOS传感器

万方数据

2009年11月

随着3D技术的演化以及应用中通孔尺寸和节 距的缩小,叠层中每层的厚度也很有可能会减小。

将硅片厚度减到5岬以下,电路性能也不会恶化。

因此,很有可能的是可制造性而非电学性能将成为 未来的限制因素。诸如CMOS图像传感器、存储器 和逻辑电路上存储器之类3D应用,使3D技术不断 发展和成熟¨j。 2.1应用与需求牵引

郎鹏等:3D封装与硅通孔(TsV)工艺技术

中,随着工艺及生产能力的提高,将会应用到DRAM 中。然而,未来当TSV尺寸降到10斗m以下时,激 光钻孔是否可以进一步缩小,面临着挑战。

在髑V刻蚀设备领域,Lam Research(美国)推 出了第一台300 mm TSV刻蚀设备2300 Syndion,并 已投入使用。而Aviza(美国)针对鸭V先进封装也 推出了Omega i2L刻蚀系统,日月光(ASK/台湾)已 宣布将采用此系统用作先进制程技术的研发。 1.2.2通孔绝缘

万方数据

324

电子工艺技术

第30卷第6期

技术的不断进步发展而言。

图1三种不同基板MCM

图2键合工艺技术 3D封装的主要优势为:具有最小的尺寸和质 量,将不同种类的技术集成到单个封装中,用短的垂 直互连代替长的2D互连,降低寄生效应和功耗等。 码V的关键技术是z轴互连和电隔离技术。包括 通孔的形成;堆叠形式(晶圆到晶圆、芯片到晶圆或 芯片到芯片);键合方式(直接Cu—Cu键合、粘接、 直接熔合和焊接);绝缘层、阻挡层和种子层的淀 积;铜的填充(电镀)和去除;再分布引线(RDL)电 镀;晶圆减薄;测量和检测等。而这种集成技术会使 IC制造与封装发生工艺交叠HJ。 l偈V关键工艺技术 rI.SV集成被定义为一种系统级集成结构,在这 一结构中,多层平面器件被堆叠起来,并经由穿透硅 通孔(1'sV)在z方向连接起来,主要工艺技术为层 减薄技术、通孔工艺、对准和键合技术等。 1,1减薄工艺

的严重翘曲使表面损伤扩大,进而破裂的危险。

1.2通孔制造是TsV技术的核心,目前“钻

蚀”TSV的技术主要有两种,一种是干法刻蚀或称

博世刻蚀,另一种是激光烧蚀。博世工艺为MEMS

工业而开发,快速地在去除硅的SF6等离子刻蚀和

实现侧壁钝化的C4F8等离子沉积步骤之间循环切

和湿法刻蚀等,目前在实际批量生产中应用最多目

前业界的主流解决方案是采用东京精密公司所率先

倡导的一体机思路,将硅片的磨削、抛光、保护膜去

除和划片膜粘贴等工序集合在一台设备内,通过独

创的机械式搬送系统使硅片从磨片一直到粘贴划片

膜为止始终被吸在真空吸盘上,始终保持平整状态。

当硅片被粘贴到划片膜上后,比划片膜厚还薄的硅

内在应力,同时其刚性也足以使硅片保持原有的平

整状态㈣。

在传统减薄工艺的粗精磨之后残留在磨削表面

的损伤是造成破片的主要直接原因。之所以产生这

样的损伤是因为磨削工艺本身就是一种物理损伤性

工艺,其去除硅材质的过程本身就是一个物理施压、

损伤、破裂和移除的过程。为了消除这些表面损伤

及应力,人们考虑了各种方法:干抛、湿抛、干法刻蚀

示;MCM—C采用陶瓷烧制基材,基于LTCC (HTCC)技术,如图1(b)所示;MCM—D采用沉积 硅基片,制造过程基于集成电路技术的TSV硅通孔 技术,如图I(C)所示。

在MCM电子系统中高达50%的功耗用在芯片 的互连线上,即使对于65 llm工艺节点的铜互连线 来说,引线电阻和寄生电容也已经成为问题。

3D封装按照封装堆叠及Ic裸芯片焊接(键合) 技术近二十年来经历着三个重要阶段,如图2所示。 有人将鸭V技术称之为第四代封装技术。之所以 被称作第四代封装技术,正是基于微电子装联键合 技术从软铅焊、丝焊和芯片凸点倒装焊到通孔互连

作者简介:郎鹏(1958一),男,毕业于西安交通大学,研究员级高工,主要从事电子专用设备设计与研究工作。

由于鸭V还可以集成互不兼容的工艺,又被称 为“异质集成”。如手机中的功率放大器都是使用 GaAs工艺制造的。而在实际上,只有很少几种电路 需要使用GaAs工艺。而鸭V集成将允许这些小块 的GaAs电路键合在CMOS电路的上面,构成一个 完整的电路。这也会在本质上降低成本。这一技术 具有很强的军用背景,实际上在军事领域被称为

通常氧化物(SiO:)绝缘层可以使用硅烷 (Sill。)或TEOS通过CVD工艺沉积获得。如果 TSV在芯片制造之后进行绝缘和填充,则需要小心 选择沉积温度。为获得具有合适密度的功能性绝缘 层,典型的TEOS沉积温度在275℃一350℃。

诸如CMOS图像传感器和存储器等应用,则要 求更低的沉积温度。一些设备制造商开发了这类低 温氧化物沉积技术,可以在室温下进行沉积,可作为 鸭V的高效有机绝缘层。 1.2.3阻挡层、种子层和填镀

在未来10年~15年到达传统器件制造其自身 物理极限,而新型器件结构,比如碳纳米管(CNT)、 自旋电子器件以及分子开关等,还不能发展到可被 实际使用的水平情况下,TSV封装技术必将成为微 电子行业关注的热点。最先应用将会是CMOS图像