assura(formixedsignal)

SIGNALINTEGRITY(信号完整性)外文翻译

SIGNAL INTEGRITYRaymond Y. Chen, Sigrid, Inc., Santa Clara, CaliforniaIntroductionIn the realm of high-speed digital design, signal integrity has become a critical issue, and is posing increasing challenges to the design engineers. Many signal integr ity problems are electromagnetic phenomena in nature and hence related to the EMI/EMC discussions in the previous sections of this book. In this chapter, we will discuss what the typical signal integrity problems are, where they come from, why it is important to understand them and how we can analyze and solve these issues. Several software tools available at present for signal integrity analysis and current trends in this area will also be introduced.The term Signal Integrity (SI) addresses two concerns in the electrical design aspects – the timing and the quality of the signal. Does the signal reach its destination when it is supposed to? And also, when it gets there, is it in good condition? The goal of signal integrity analysis is to ensure reliable high-speed data transmission. In a digital system, a signal is transmitted from one component to another in the form of logic 1 or 0, which is actually at certain reference voltage levels. At the input gate of a receiver, voltage above the reference value Vih is considered as logic high, while voltage below the reference value Vil is considered as logic low. Figure 14-1 shows the ideal voltage waveform in the perfect logic world, whereas Figure 14-2 shows how signal will look like in a real system. More complex data, composed of a string of bit 1 and 0s, are actually continuous voltage waveforms. The receiving component needs to sample the waveform in order to obtain the binary encoded information. The data sampling process is usually triggered by the rising edge or the falling edge of a clock signal as shown in the Figure 14-3. It is clear from the diagram that the data must arrive at the receiving gate on time and settle down to a non-ambiguous logic state when the receiving component starts to latch in. Any delay of the data or distortion of the data waveform will result in a failure of the data transmission. Imagine if the signal waveform in Figure 14-2 exhibits excessive ringing into the logic gray zone while the sampling occurs, then the logic level cannot be reliably detected.SI ProblemsT ypical SI Problems“Timing” is everything in a high-speed system. Signal timing depends on the delay caused by the physical length that the signal must propagate. It also depends on the shape of the waveform w hen the threshold is reached. Signal waveform distortions can be caused by different mechanisms. But there are three mostly concerned noise problems:•Reflection Noise Due to impedance mismatch, stubs, visa and other interconnect discontinuities. •Crosstalk Noise Due to electromagnetic coupling between signal traces and visa.•Power/Ground Noise Due to parasitic of the power/ground delivery system during drivers’ simultaneous switching output (SSO). It is sometimes also called Ground Bounce, Delta-I Noise or Simultaneous Switching Noise (SSN).Besides these three kinds of SI problems, there is other Electromagnetic Compatibility or Electromagnetic Interference (EMC/EMI) problems that may contribute to the signal waveform distortions. When SI problems happen and the system noise margin requirements are not satisfied – the input to a switching receiver makes an inflection below Vih minimum or above Vil maximum; the input to a quiet receiver rises above V il maximum or falls below Vih minimum; power/ground voltage fluctuations disturb the data in the latch, then logic error, data drop, false switching, or even system failure may occur. These types of noise faults are extremely difficult to diagnose and solve after the system is built or prototyped. Understanding and solving these problems before they occur will eliminate having to deal with them further into the project cycle,and will in turn cut down the development cycle and reduce the cost[1]. In the later part of thischapter, we will have further investigations on the physical behavior of these noise phenomena, their causes, their electrical models for analysis and simulation, and the ways to avoid them.1. Where SI Problems HappenSince the signals travel through all kinds of interconnections inside a system, any electrical impact happening at the source end, along the path, or at the receiving end, will have great effects on the signal timing and quality. In a typical digital system environment, signals originating from the off-chip drivers on the die (the chip) go through c4 or wire-bond connections to the chip package. The chip package could be single chip carrier or multi-chip module (MCM). Through the solder bumps of the chip package, signals go to the Printed Circuit Board (PCB) level. At this level, typical packaging structures include daughter card, motherboard or backplane. Then signals continue to go to another system component, such as an ASIC (Application Specific Integrated Circuit) chip, a memory module or a termination block. The chip packages, printed circuit boards, as well as the cables and connecters, form the so-called different levels of electronic packaging systems, as illustrated in Figure 14-4. In each level of the packaging structure, there are typical interconnects, such as metal traces, visa, and power/ground planes, which form electrical paths to conduct the signals. It is the packaging interconnection that ultimately influences the signal integrity of a system.2. SI In Electronic PackagingTechnology trends toward higher speed and higher density devices have pushed the package performance to its limits. The clock rate of present personal computers is approaching gigahertz range. As signal rise-time becomes less than 200ps, the significant frequency content of digital signals extends up to at least 10 GHz. This necessitates the fabrication of interconnects and packages to be capable of supporting very fast varying and broadband signals without degrading signal integrity to unacceptable levels. While the chip design and fabrication technology have undergone a tremendous evolution: gate lengths, having scaled from 50 µm in the 1960s to 0.18 µm today, are projected to reach 0.1 µm in the next few years; on-chip clock frequency is doubling every 18 months; and the intrinsic delay of the gate is decreasing exponentially with time to a few tens of Pico-seconds. However, the package design has lagged considerably. With current technology, the package interconnection delay dominates the system timing budget and becomes the bottleneck of the high-speed system design. It is generally accepted today that package performance is one of the major limiting factors of the overall system performance.Advances in high performance sub-micron microprocessors, the arrival of gigabit networks, and the need for broadband Internet access, necessitate the development of high performance packaging structures for reliable high-speed data transmission inside every electronics system.Signal integrity is one of the most important factors to be considered when designing these packages (chip carriers and PCBs) and integrating these packages together.3、SI Analysis3.1. SI Analysis in the Design FlowSignal integrity is not a new phenomenon and it did not always matter in the early days of the digital era. But with the explosion of the information technology and the arrival of Internet age, people need to be connected all the time through various high-speed digital communication/computing systems. In this enormous market, signal integrity analysis will play a more and more critical role to guarantee the reliable system operation of these electronics products. Without pre-layout SI guidelines, prototypes may never leave the bench; without post-layout SI verifications, products may fail in the field. Figure 14-5 shows the role of SI analysis in the high-speed design process. From this chart, we will notice that SI analysis is applied throughout the design flow and tightly integrated into each design stage. It is also very common to categorize SI analysis into two main stages: reroute analysis and post route analysis.In the reroute stage, SI analysis can be used to select technology for I/Os, clock distributions, chip package types, component types, board stickups, pin assignments, net topologies, and termination strategies. With various design parameters considered, batch SI simulations on different corner cases will progressively formulate a set of optimized guidelines for physical designs of later stage. SI analysis at this stage is also called constraint driven SI design because the guidelines developed will be used as constraints for component placement and routing. The objective of constraint driven SI design at the reroute stage is to ensure that the signal integrity of the physical layout, which follows the placement/routing constraints for noise and timing budget, will not exceed the maximum allowable noise levels. Comprehensive and in-depth reroute SI analysis will cut down the redesign efforts and place/route iterations, and eventually reduce design cycle.With an initial physical layout, post route SI analysis verifies the correctness of the SI design guidelines and constraints. It checks SI violations in the current design, such as reflection noise, ringing, crosstalk and ground bounce. It may also uncover SI problems that are overlooked in the reroute stage, because post route analysis works with physical layout data rather than estimated data or models, therefore it should produce more accurate simulation results.When SI analysis is thoroughly implemented throughout the whole design process, a reliable high performance system can be achieved with fast turn-around.In the past, physical designs generated by layout engineers were merely mechanical drawings when very little or no signal integrity issues were concerned. While the trend of higher-speed electronics system design continues, system engineers, responsible for developing a hardware system, are getting involved in SI and most likely employ design guidelines and routing constraints from signal integrity perspectives. Often, they simply do not know the answers to some of the SI problems because most of their knowledge is from the engineers doing previous generations of products. To face this challenge, nowadays, a design team (see Figure 14-6) needs to have SI engineers who are specialized in working in this emerging technology field. When a new technology is under consideration, such as a new device family or a new fabrication process for chip packages or boards, SI engineers will carry out the electrical characterization of the technology from SI perspectives, and develop layout guideline by running SI modeling and simulation software [2]. These SI tools must be accurate enough to model individual interconnections such as visa, traces, and plane stickups. And they also must be very efficient so what-if analysis with alternative driver/load models and termination schemes can be easily performed. In the end, SI engineers will determine a set of design rules and pass them to the design engineers and layout engineers. Then, the design engineers, who are responsible for the overall system design, need to ensure the design rules are successfully employed. They may run some SI simulations on a few critical nets once the board is initially placed and routed. And they may run post-layout verifications as well. The SI analysis they carry out involves many nets. Therefore, the simulation must be fast, though it may not require the kind of accuracy that SI engineers are looking for. Once the layout engineers get the placement and routing rules specified in SI terms, they need to generate an optimized physical design based on these constraints. And they will provide the report on any SI violations in a routed system using SI tools. If any violations are spotted, layout engineers will work closely with design engineers and SI engineers to solve these possible SI problems.3.2.Principles of SI AnalysisA digital system can be examined at three levels of abstraction: log ic, circuit theory, and electromagnetic (EM) fields. The logic level, which is the highest level of those three, is where SI problems can be easily identified. EM fields, located at the lowest level of abstraction, comprise the foundation that the other levels are built upon [3]. Most of the SI problems are EM problems in nature, such as the cases of reflection, crosstalk and ground bounce. Therefore, understanding the physical behavior of SI problems from EM perspective will be very helpful. For instance, in the following multi-layer packaging structure shown in Figure 14-7, a switching current in via a will generate EM waves propagating away from that via in the radial direction between metal planes. The fields developed between metal planes will cause voltage variations between planes (voltage is the integration of the E-field). When the waves reach other visa, they will induce currents in those visa. And the induced currents in that visa will in turn generate EM waves propagating between the planes. When the waves reach the edges of the package, part of them will radiate into the air and part of them will get reflected back. When the waves bounce back and forth inside the packaging structure and superimpose to each other, resonance will occur. Wave propagation, reflection, coupling and resonance are the typical EM phenomena happening inside a packaging structure during signal transients. Even though EM full wave analysis is much more accurate than the circuit analysis in the modeling of packaging structures, currently, common approaches of interconnect modeling are based on circuit theory, and SI analysis is carried out with circuit simulators. This is because field analysis usually requires much more complicated algorithms and much larger computing resources than circuit analysis, and circuit analysis provides good SI solutions at low frequency as an electrostatic approximation.Typical circuit simulators, such as different flavors of SPICE, employ nodal analysis and solve voltages and currents in lumped circuit elements like resistors, capacitors and inductors. In SI analysis, an interconnect sometimes will be modeled as a lumped circuit element. For instance, a piece of trace on the printed circuit board can be simply modeled as a resistor for its finite conductivity. With this lumped circuit model, the voltages along both ends of the trace are assumed to change instantaneously and the travel time for the signal to propagate between the two ends is neglected. However, if the signal propagation time along the trace has to be considered, a distributed circuit model, such as a cascaded R-L-C network, will be adopted to model the trace. To determine whether the distributed circuit model is necessary, the rule of thumb is – if the signal rise time is comparable to the round-trip propagation time, you need to consider using the distributed circuit model.For example, a 3cm long stripling trace in a FR-4 material based printed circuit board will exhibits 200ps propagation delay. For a 33 MHz system, assuming the signal rise time to be 5ns, the trace delay may be safely ignored; however, with a system of 500 MHz and 300ps rise time, the 200ps propagation delay on the trace becomes important and a distributed circuit model has to be used to model the trace. Through this example, it is easy to see that in the high-speed design, with ever-decreasing signal rise time, distributed circuit model must be used in SI analysis.Here is another example. Considering a pair of solid power and ground planes in a printed circuit board with the dimension of 15cm by 15cm, it is very natural to think the planes acting as a large, perfect, lumped capacitor, from the circuit theory point of view. The capacitor model C= erA/d, an electro-static solution, assumes anywhere on the plane the voltages are the same and all the charges stored are available instantaneously anywhere along the plane. This is true at DC and low frequency. However, when the logics switch with a rise time of 300ps, drawing a large amount of transient currents from the power/ground planes, they perceive the power/ground structure as a two-dimensional distributed network with significant delays. Only some portion of the plane charges located within a small radius of the switching logics will be able to supply the demand. And voltages between the power/ground planes will have variations at different locations. In this case, an ideal lumped capacitor model is obviously not going to account for the propagation effects. Two-dimensional distributed R-L-C circuit networks must be used to model the power/ground pair.In summary, as the current high-speed design trend continues, fast rise time reveals the distributed nature of package interconnects. Distributed circuit models need to be adopted to simulate the propagation delay in SI analysis. However, at higher frequencies, even the distributed circuit modeling techniques are not good enough, full wave electromagnetic field analysis based on solving Maxwell’s equations must come to play. As presen ted in later discussions, a trace will not be modeled as a lumped resistor, or a R-L-C ladder; it will be analyzed based upon transmission line theory; and a power/ground plane pair will be treated as a parallel-plate wave guide using radial transmission line theory.Transmission line theory is one of the most useful concepts in today’s SI analysis. And it is a basic topic in many introductory EM textbooks. For more information on the selective reading materials, please refer to the Resource Center in Chapter 16.In the above discussion, it can be noticed that signal rise time is a very important quantity in SI issues. So a little more expanded discussion on rise time will be given in the next section.信号完整性介绍在高速数字设计领域,信号完整性已经成为一个严重的问题,是造成越来越多的挑战的设计工程师。

宿主及合成器常用术语中英文对照表

宿主及合成器效果器常用术语中英文对照表About 关于(软件信息)Accent 重音,强音Active 活跃,起作用Add 增加,加法(合成方式)Adjust 调整,调节Adjusts 调节ADSR 包络校准AfterTouch 触后(缩写AT)Air 空气,空间感All 全部,完整和弦Always 总是,始终AM(Amplitude Modulation)振幅调制,调幅(合成方式)Amount 数量,影响程度(缩写AMNT)Amplifiter 放大器Amplitude 振幅,音量,放大器(缩写AMP)Analog 色偏差,模拟(信号)Anchor 标记,定位Application 应用,程序Apply 应用Area 范围,区域Arpeggiator 琶音,琶音器(缩写ARP)Articulation 清晰度ASIO (Audio Stream Iput Output)Steinberg开发的计算机声卡低延迟专业驱动Assign 分配,指派(设备功能)Assingment 分配,设置(设备功能)Asymmetry 不对称性,偏移(缩写ASYM)Asynchronous 不同步,异步Attack 启动,触发(缩写A或ATT)Attributes 属性Audio 音频Author 创造者,作者Auto 自动Available 可用的平衡(信号)(缩写BAL ) 带通(滤波)模式带除,带阻(滤波)模式Band段带,区间(滤波器模式) Bank 库存(音色)Base 基础,基于Basic 基础(波形)Bass 低音,低频,低音乐器(贝司)Beat 拍子,节拍Bend 弯音,弯音轮,弯音范围Bipolar 双极(信号)Blend 混合比,透明度Box 封装BPM 节拍,速度Break 分割,分开Breakpoint 分界点,连接点Breath 呼吸,呼吸控制器Bright 明亮(音色)Brightness 明亮程度(音色)Browser 浏览器Bypass 旁通BalanceBand pass Band RejectCabinet机架,音箱头 Carrier搭载,载波器 Center中间,居中(缩写C ) Chain链(信号) Change改变(音色排序) Chunnel通道,声道(缩写C Clear清除 Click滴答声,颗粒,单机 Clip修剪,分离器 Clock时钟(同步) Close关闭,停止 Clouds云(粒子) Coarse粗略调节(音调) Code编码 Color色彩(声音) Comb 梳妆Combiner 混合器Comment 注释,备注Company 单位,团队Compare 对比,比较Chorus合唱,合唱效果器 Computer计算机,电脑 Container 容器Control 控制C或 CHN )Controller 控制器(缩写CTRY)Copy 复制,拷贝Create 创建,创造Curve 曲线图Cut 切除Cutoff 截止频率Damp 阻尼,抑制db 分贝,振幅单位DC Offset 直流偏移Decay 衰减,回落(缩写D或DEC)Default 默认,缺省(参数)Delay 延迟,延迟效果器Delete 删除Demo 试用(软件,演示)Dens 密度Depth 深度Destination 目标(调制)Detune 解谐,音调偏移Developer 开发者Diffusion 扩散,传播Digital 数字,数码(缩写DIGI)Displace 偏移,转移Distortion 失真,失真效果器Dotted 附点音Double 双重,双倍Down 向下,下行Download 下载Draft 实时Draw 描绘(波形)Drive 驱动,过载程度Driver 驱动器,光驱Dry 干声,原始声Dynamic 动态Easy 容易Echo 回声Edit 编辑Editor 编辑器Effect 效果器EG (Envelope Generator)包络发生器Electric 电子(设备,乐器)(缩写ELEC)Emphasis 强调(截止频率)Empty 空白的,待编辑的Enabled 打开,激活End 结束,结束处Ensemble 群体感,群奏,合奏(ENS)Envelope 包络(缩写ENV)Equalizer 均衡,均衡器(缩写EQ)Expand 扩展,扩展器ER (Early Reflection)早期反射Event 事件Example 举例Expert 专业,复杂,详细(操作)Explorer 浏览(硬盘)Export 导出Expression 表情External 外部的(信号)FFader 推子,衰减器Fat 肥厚,饱满Feedback 反馈程度,反复次数(缩写FBK)File 文件(菜单)Filter 滤波,滤波器Fine 精细调节(音调)Flanger 镶边,镶边效果器Flat 平坦(图形参数)FM(Frequency Modulation)频率调制,调频(合成方式)Formant 共振峰Fractal 不规则碎片(波形)Fractalize 分裂碎片(合成方式)Freeze 冻结Frequency 频率(缩写FREQ)FX 效果GGain 增益(音量)Gate 门,噪声门,时值Generator 发生器Genre 风格,流派Gibbs 吉布斯(现象)Glide 滑音,滑音模式Global 全局,整体Granular 颗粒,粒子(合成方式)Grid 网格Group 群组HHarmonic 谐波,泛音Harmonics 泛音High 高,高频(缩写HI)Highest 最高的(音)Hold 保持,持续HPF(High Pass Filter)高通滤波器Hz 赫兹(频率单位)II/O(Input/Output)输入/输出Icon 图标Image 图像Import 导入In 入口Index 指数,指标Information 信息,注释Inharmonic 不谐和的Input 输入,输入通道Insert 插入Instruments 乐器,工具Interpolate 加入变化Inverse Sawtooth 倒锯齿波Inverse 倒转,反转Invert 颠倒,反转Iterations 重复,反复KKey 琴键,键位,调式Keyboard 键盘,键盘乐器,键盘跟踪器,键盘跟踪功能(缩写KBD)Knob 旋钮LLag 懒散,缓缓,滞后Latch 持续演奏Latest 最后的(音)Layer 层面,层次Lead 领奏,主奏(音色类型)Learn 识别,捕获Left 左边,左声道Legato 连音,连奏Lenght 长度,时值Level 强度,程度多用于表示音量Limit 限制,限度Limiter 限制限制器(缩写LIM)Link 连接,关联List 列表Load 读取,调用Logic 逻辑Loop 循环素材Low 低,低频(缩写LIM)Low Frequency Oscillator 低频振荡器(缩写LFO)Lowest 最低的(音)Low Pass Filter低通滤波器(缩写LPF)Magnitude 数量Main 主要的Make 安排,制造Maker 制造者Manager 管理器Manual 手动,不自动Mapping 映射Master 主要的,总控,总线Matrix 矩阵Max 最大的Message 信息Middle 中频,中间(缩写MID)Musical Instrument Digital Interface数字化乐器接口(缩写MIDI)Min 最小的Mix 混音,混合,混合比例Mixer 混合器,调音台Mode 模式,方式Modeling 建模Modifiers 校正,调节器Modulate 调制,调制器Modulated 已调制,被调制Modulation 调制,调制轮,调制技术Module 模块Monitor 监听Mono 单声道,单音模式Morph 变化,复合(波形)Mouth 用嘴表达一样的(效果)ms 毫秒,时间单位Multi 多(功能)Multicomb 梳妆延迟(效果)Multiplivator 倍频Multitap 多输出延迟(效果)Mute 静音(音轨)(缩写M)NName 名字(音色)Navigator 导航器New 新的(音色)Next 下一步,下一个Noise 噪音Normal 正常,标准Notch 带除(缩写NOT)Notches 等级,程度Note 音符Number 数字,数量(缩写NUM)OOctave 八度,每八度(缩写OCT)OFF 关闭,停止Offset 偏移(频率)ON 打开,启动Open 打开,启动Operator 操作,控制,操作器,运算器(缩写OP)Option 选项Order 次序,工作状态(缩写ORD)Oscillator 振荡器缩写(OSC)Out 出口Output 输出,输出通道Overall 全局,总控Overdrive 过载,过载效果器Overload 信号过载PPad 铺底,铺垫(音色类型)Pan 声像Panel 面板Parallel 并联Parameter 参数,参量Pass 通过(滤波器模式)Paste 粘贴Pattern 图示,模式Pulse Code Modulation 脉冲编码调制(缩写PCM)Peak 顶点(图形参数)Perform 执行演奏Phase 相位Phaser 移相,移相效果器Physical 物理的Ping-Pong 乒乓(效果)Pink 粉红(噪音)Pipe 管道(效果)Pitch 音高偏移,定调Pitchbend 弯音轮,弯音控制器Play 演奏,播放Pluck 拨奏Plugin 插件Point 节点,端点Polyphonic 复音,复音数Polyphony 复音,复音数(缩写POLY)Portamento 滑音,延音(缩写PORTA)Position 位置Post 加速Power 功率。

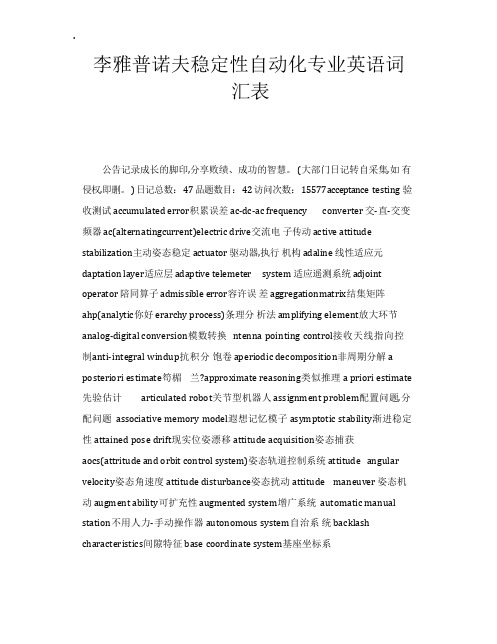

李雅普诺夫稳定性自动化专业英语词汇表

.李雅普诺夫稳定性自动化专业英语词汇表公告记录成长的脚印,分享败绩、成功的智慧。

(大部门日记转自采集,如有侵权,即删。

) 日记总数: 47 品题数目: 42 访问次数: 15577 acceptance testing 验收测试 accumulated error积累误差 ac-dc-ac frequency converter 交-直-交变频器 ac(alternatingcurrent)electric drive交流电子传动 active attitude stabilization主动姿态稳定 actuator 驱动器,执行机构 adaline 线性适应元daptation layer适应层 adaptive telemeter system 适应遥测系统 adjoint operator 陪同算子 admissible error容许误差 aggregationmatrix结集矩阵ahp(analytic你好 erarchy process)条理分析法 amplifying element放大环节analog-digital conversion模数转换 ntenna pointing control接收天线指向控制anti-integral windup抗积分饱卷 aperiodic decomposition非周期分解 a posteriori estimate笱楣兰?approximate reasoning类似推理 a priori estimate 先验估计 articulated robot关节型机器人 assignment problem配置问题,分配问题 associative memory model遐想记忆模子 asymptotic stability渐进稳定性 attained pose drift现实位姿漂移 attitude acquisition姿态捕获aocs(attritude and orbit control system)姿态轨道控制系统 attitude angular velocity姿态角速度 attitude disturbance姿态扰动 attitude maneuver 姿态机动 augment ability可扩充性 augmented system增广系统 automatic manual station不用人力-手动操作器 autonomous system自治系统 backlash characteristics间隙特征 base coordinate system基座坐标系bayes classifier 贝叶斯分类器 bearing alignment 方位瞄准 bellows pressure gauge 波纹管压力表 benefit-cost analysis 收入成本分析 bilinear system 双线性系统 biocybernetics 生物控制论 biological feedback system 生物反馈系统black box testing approach 黑箱测试法 blind search 盲目搜索 block diagonalization 块对于角化 boltzman mac 你好 ne 玻耳兹曼机 bottom-up development 自下而上开辟 boundary value analysis 界限值分析 brainstorming method 头脑风暴法 breadth-first search 广度优先搜索 cae(computer aided engineering) 计较机匡助工程 cam(computer aided manufacturing) 计较机匡助创造 camflex valve 偏疼旋转阀 canonical state vari able 标准化状况变量capacitive displacementtransducer 电容式位移传感器 capsule pressure gauge 膜盒压力表 card 计较机匡助研究开辟 cartesian robot 直角坐标型机器人cascadecompensation 串联赔偿 catastrophe theory 突变论 chained aggregation 链式结集 characteristic locus 特征轨迹 chemical propulsion 化学推进classical information pattern 经典信息标准样式 clinical controlsystem 临床控制系统关上 d loop pole 闭环极点关上 d looptransfer function 闭环传递函数cluster analysis 聚类分析 coarse-finecontrol 粗- 精控制 cobweb model 蜘蛛网模子 coefficient matrix 凳?卣?cognitive science 认知科学 coherent system 枯燥关接洽统 combination decision 组合决定计划 combinatorial explosion 组合爆炸combined pressure and vacuum gauge 压力真空表 command pose 指令位姿companion matrix 相伴矩阵 compartmental model 房室模子 compatibility 相容性,兼容性 compensating network 赔偿采集 compensation 赔偿,矫正compliance 柔顺, 适应 composite control 组合控制 computable general equilibrium model 可计较普通均衡模子 conditionallyinstability 条件不稳定性connectionism 毗连机制 conservative system 守恒系统 constraint condition 约束条件 consumption function 消费函数 context-free grammar 上下文无关语法continuous discrete eventhybrid system simulation 连续离散事件混淆系统仿真continuous duty 连续事情制 control accuracy 控制精密度 control cabinet 控制柜controllability index 可控指数 controllable canonical form 可控标准型[control]plant 控制对于象,被控对于象 controlling instrument 控制仪表 control moment gyro 控制力矩捻捻转儿 control panel 控制屏,控制盘 control synchro 控制 [式]自整角机 control system synthesis 控制系统综合 control time horizon 控制时程 cooperativegame 互助对于策 coordinability condition 可协调条件coordinationstrategy 协调计谋 corner frequency 迁移转变频率 costate variable 蔡?淞?cost-effectiveness analysis 用度效益分析 coupling ofrbit and attitude 轨道以及姿态耦合 critical damping 临界阻尼 ritical stability 临界稳定性 cross-over frequency 穿越频率,交越频率 current source inverter 电流[源]型逆变器 cut-off frequency 截止频率 cyclic remote control 循环遥控 cylindrical robot 圆柱坐标型机器人 damped oscillation 阻尼振动 damping ratio 阻尼比 data acquisition 数值采集 data encryption 数值加密 data preprocessing 数值预处理 data processor 数值处理器 dc generator-motor set drive 直流发机电-电动机组传动 d controller 微分控制器 decentralizedstochastic control 分散 rand 控制 decision space 决定计划空间 decisionsupport system 决定计划支持系统 decomposition-aggregation approach 分解结集法 decoupling parameter 解耦参量 deductive-inductive hybrid modeling method 演绎与归纳混淆建模法 delayed telemetry 延时遥测derivation tree 导出树 derivative feedback 微分反馈 describingfunction 描写函数 desired value 希望值deterministic automaton 确定性不用人力机 deviation alarm 误差报警器 dfd 数值流图 diagnosticmodel 诊断模子 diagonally dominant matrix 对于角主导矩阵diaphragmpressure gauge 膜片压力表 difference equation model 差分方程模子differential dynamical system 微分动力学系统 differential game⒎侄圆differential pressure level meter 差压液位计 differentialpressure transmitter 差压变送器 differential transformer displacementtransducer 差动变压器式位移传感器 differentiation element 微分环节 digital filer 数码滤波器 digital signal processing 数码旌旗灯号处理 digitizer 数码化仪 dimension transducer 尺度传感器 direct coordination 直接协调 discrete event dynamic system 离散事件动态系统 discretesystem simulation language 离散系统仿真语言 discriminant function 判别函数 displacement vibration amplitude transducer 位移波幅传感器dissipative structure 耗扩散局 distributed parameter control system 漫衍参量控制系统 disturbance compensation 扰动赔偿 domain knowledge 范畴常识dominant pole 主导极点 dose-response model 剂量反映模子 dual modulation telemetering system 两重调制遥测系统 dualprinciple 对于偶原理 dual spin stabilization 双自旋稳定 duty ratio 负载比 dynamic braking 能耗制动 dynamic characteristics 动态特征 dynamic deviation 动态误差 dynamic error coefficient 动态误差系数 dynamic exactness 动它吻合性 dynamic input-outputmodel 动态投入产出模子 econometric model 计量经济模子 economiccybernetics 经济控制论 economic effectiveness 经济效益 economicvaluation 经济评价 economic index 经济指数 economic in dicator 经济指标 eddy current t 你好 ckness meter 电涡流厚度计 effectivenesstheory 效益意见 elasticity of demand 需求弹性 electric actuator 电动执行机构 electric conductancelevelmeter 电导液位计 electricdrive control gear 电动传动控制设备 electric hydraulic converter 电-液转换器 electric pneumatic converter 电-气转换器electrohydraulicservo vale 电液伺服阀 electromagnetic flow transducer 电磁流量传感器 electronic batc 你好 ng scale 电子配料秤 electronic belt conveyorscale 电子皮带秤 electronic hopper scale 电子料斗秤 emergencystop 异样住手empirical distribution 经验漫衍 endogenous variable 内发生变故量equilibrium growth 均衡增长 equilibrium point 平衡点 equivalence partitioning 等价类区分清晰 error-correction parsing 纠错剖析 estimation theory 估计意见 evaluation technique 评价技术 event chain 事件链evolutionary system 高级演化系统 exogenous variable 外发生变故量 expected characteristics 希望特征 failure diagnosis 妨碍诊断 fast mode 快变模态 feasibility study 可行性研究 feasiblecoordination 可行协调 feasible region 可行域 feature detection 特征检测 feature extraction 特征抽取 feedback compensation 反馈赔偿 feedforward path 前馈通路 field bus 现场总线 finite automaton 有限不用人力机 fip(factory information protocol) 工场信息以及谈 first order predicate logic 一阶谓词逻辑 fixed sequence manipulator 固定挨次机械手 fixed set point control 定值控制 fms(flexiblemanufacturing system) 柔性创造系统 flowsensor/transducer 流量传感器 flow transmitter 流量变送器 forced oscillation 强迫振动 formal language theory 情势语言意见 formal neuron 情势神经元forward path 正向通路 forward reasoning 正向推理 fractal 分形体,分维体frequency converter 变频器 frequency domain modelreduction method 频域模子降阶法 frequency response 频域相应 full order observer 全阶测候器 functional decomposition 功效分解 fes(functional electricalstimulation)功效电刺激 functionalsimularity 功效相仿 fuzzy logic 含糊逻辑 game tree 对于策树 general equilibrium theory 普通均衡意见 generalized least squaresestimation 意义广泛最小二乘估计 generation function 天生函数geomagnetictorque 地磁性矩 geometric similarity 几何相仿 gimbaled wheel 蚣苈global asymptotic stability 全局渐进稳定性 global optimum 全局最优 globe valve 球形阀 goal coordination method 目标协调法 grammatical inference 文法判断 grap 你好 c search 图搜索 gravitygradient torque 重力梯度力矩 group technology 成组技术 guidancesystem 制导系统 gyro drift rate 捻捻转儿漂移率 hall displacementtransducer 霍尔式位移传感器 hardware-in-the-loop simulation 半实物仿真 harmonious deviation 以及谐误差 harmonious strategy 以及谐计谋 heuristic inference 开导式推理你好 dden oscillation 隐蔽振动你好 erarc 你好 calchart 条理布局图你好 erarc 你好 cal planning 递阶规划你好 erarc你好 calontrol 递阶控制 homomorp 你好 c model 同态系统 horizontal decomposition 横向分解 hormonal control 内排泄控制 hydraulic step motor 液压步进马达 hypercycle theory 超循环意见 i controller 积分控制器 identifiability 可辨识性 idss(intelligent decision support system)智能决定计划支持系统 image recognition 图象辨认 impulse function 冲击函数,电子脉冲函数 incompatibility principle 不相容原理 incrementalmotion control 增量运动控制 index of merit 品质因数 inductiveforce transducer 电感式位移传感器 inductive modeling method 归纳建模法 industrial automation 工业不用人力化 inertial attitude sensor 惯性姿态敏锐器 inertial coordinate system 惯性坐标系 inertialwh eel 惯性轮 inference engine 推理机 infinite dimensional system 无限维系统information acquisition 信息采集 infrared gasanalyzer 红外线气体分析器 inherent nonlinearity 本来就有非线性 inherent regulation 本来就有调节 initial deviation 初始误差 injection attitude 入轨姿式input-output model 投入产出模子 instability 不稳定性 instructionlevel language 指令级语言 integral of absolute value of errorcriterion 绝对于误差积分准则integral of squared error criterion 平方误差积分准则 integral performance criterion 积分性能准则 integration instrument 积算摄谱仪 intelligent terminal 智能终端 interactedsystem 互接洽统,关接洽统 interactive prediction approach 互联预估法,关联预估法 intermittent duty 断续事情制ism(interpretivestructure modeling) 诠释布局建模法 invariant embedding principle 不变镶嵌原理 inventory theory 库伦论 inverse nyquist diagram 逆奈奎斯特图 investment decision 投资决定计划 isomorp 你好 c model 同构模子iterative coordination 迭代协调 jet propulsion 喷气推进 job-lot control 分批控制kalman-bucy filer 卡尔曼-布西滤波器 knowledgeaccomodation 常识适应knowledge acquisition 常识获取 knowledgessimilation 常识夹杂kbms(knowledge base management system) 常识库管理系统 knowledge representation 常识抒发 lad der diagram 菪瓮?lag-lead compensation 滞后超前赔偿 lagrange duality 拉格朗日对于偶性 laplace transform 拉普拉斯变换 large scale system 大系统 lateral in 你好 bition network 侧抑制采集 least cost input 最小成本投入 least squares criterion 最小二乘准则 level switch 物位开关 libration damping 天平动阻尼 limit cycle 极限环 linearizationtechnique 线性化要领 linear motion electric drive 直线运动电气传动 linear motion valve 直行程阀 linear programming 线性规划 lqr(linear quadratic regulator problem) 线性二次调节器问题 oad cell 称重传感器 local asymptotic stability 局部渐近稳定性 local optimum 局部最优 log magnitude-phase diagram 对于数幅相图long term memory 长期记忆 lumped parameter model 集总参量模子 lyapunov theorem of asymptotic stability 李雅普诺夫渐近稳定性定理 macro-economic system 宏观经济系统 magnetic dumping 磁卸载 magnetoelastic weig 你好ng cell 磁致弹性称重传感器 magnitude- frequencycharacteristic 幅频特征magnitude margin 幅值裕度 magnitudecale factor 幅值缩尺 man-mac 你好ne coordination 人机协调 manualstation 手动操作器 map(manufacturing automation protocol) 创造不用人力化以及谈 marginal effectiveness 边岸效益mason's gain formula 梅森增益公式 matc 你好 ng criterion 匹配准则 maximum likelihood estimation 最大似然估计 maximum ove rshoot 最大超调量maximum principle 极大值原理 mean-square error criterion 均方误差准则mechanismmodel 机理模子 meta-knowledge 元常识 metallurgical automation 冶金不用人力化 minimal realization 最小使成为事实 minimum phase system 最小相位系统 minimum variance estimation 最小方差估计 minor loop 副回路missile-target relative movement simulator 弹体- 目标相对于运动仿真器 modal aggregation 模态结集 modal transformation 模态变换 mb(model base)模子库model confidence 模子置信度 model fidelity 模子传神度 model reference adaptive control system 模子参考适应控制系统 model verification 模子证验mec(mostconomic control)最经济控制 motion space 可动空间 mtbf(mean time between failures) 均等妨碍距离时间 mttf(mean timeto failures)均等无妨碍时间 multi-attributive utility function 嗍粜孕в 煤??multicriteria 多重判据 multilevel 你好 erarc 你好 cal structure 多级递阶布局 multiloop control 多回路控制 multi- objective decision 多目标决定计划 multistate logic 多态逻辑multistratum 你好 erarc 你好 calcontrol 多段递阶控制 multivariable control system 多变量控制系统 myoelectric control 肌电控制 nash optimality 纳什最优性 naturallanguage generation 自然语言天生 nearest- neighbor 这段邻necessitymeasure 肯定是性侧度 negative feedback 负反馈 neural assembly 神经集合 neural network computer 神经采集计较机 nichols chart 尼科尔斯图noetic science 思维科学 noncoherent system 非枯燥关接洽统 noncooperative game 非互助博弈 nonequilibrium state 非平衡态 nonlinear element 非线性环节nonmonotonic logic 非枯燥逻辑 nonparametric training 非参量训练nonreversible electric drive 不成逆电气传动 nonsingular perturbation 非奇妙摄动 non-stationaryrandom process 非平稳 rand 历程 nuclear radiation levelmeter 核辐射物位计 nutation sensor 章动敏锐器 nyquist stability criterion 奈奎斯特稳定判据 objective function 目标函数 observability index 可测候指数observable canonical form 可测候标准型 on-line assistance 在线帮忙 on- off control 通断控制 open loop pole 开环极点 operational research model 运筹学模子 optic fiber tachometer 光纤式转速表 opt imal trajectory 最优轨迹optimization technique 最优化技术 orbital rendezvous 轨道交会 orbit gyrocompass 轨道捻捻转儿罗经 orbit perturbation 轨道摄动 order parameter 序参量 orientationcontrol 定向控制 oscillating period 振动周期 output predictionmethod 输出预估法 oval wheel flowmeter 椭圆齿轮流量计overalldesign 总体设计 overlapping decomposition 交叠分解 pade approximation 帕德类似 pareto optimality 帕雷托最优性 passive attitude stabilization 不主动姿态稳定 path repeatability 路径可重复性 pattern primitive 标准样式基元 pr(pattern recognition)标准样式辨认 p control 比例控制器 peak time 峰值时间penalty function method 罚函数法 periodic duty 周期事情制 perturbation theory 摄动意见 pessimisticvalue 悲观值 phase locus 相轨迹 phase trajectory 相轨迹hase lead 相位超前 photoelectric tachometric transducer 光电式转速传感器phrase-structure grammar 短句布局文法 physical symbol system 物理符号系统 piezoelectric force transducer 压电式力传感器 playbackrobot 示教再现式机器人 plc(programmable logic controller)可编步伐逻辑控制器 plug braking 反接制动 plug valve 旋塞阀 pneumaticactuator 气动执行机构 point-to-point control 点位控制 polar robot 极坐标型机器人 pole assignment 极点配置 pole-zero cancellation 零极点相消 polynom ial input 多项式输入 portfolio theory 投资配搭意见 pose overshoot 位姿过调量 position measuring instrument 位置丈量仪posentiometric displacement transducer 电位器式位移传感器 positive feedback 正反馈 power system automation 电力系统不用人力化 predicate logic 谓词逻辑pressure gauge with electric contact 电接点压力表 pressure transmitter 压力变送器 price coordination 价格协调 primal coordination 主协调 primary frequency zone 主频区 pca(principal component analysis)主成份分析法principlef turnpike 通途原理 process- oriented simulation 面向历程的仿真production budget 生产预算 production rule 孕育发生式法则 profitforecast 利润预测 pert(program evaluation and review technique) 计划评审技术program set station 步伐设定操作器 proportionalcontrol 比例控制 proportional plus derivative controller 比例微分控制器 protocol engineering 以及谈工程pseudo random sequence 伪 rand 序列 pseudo-rate-increment control 伪速度增量控制 pulse duration 电子脉冲持续时间 pulse frequency modulation control system 电子脉冲调频控制系统 pulse width modulation controlsystem 电子脉冲调宽控制系统 pwm inverter 脉宽调制逆变器 pushdown automaton 下推不用人力机 qc(quality control)质量管理 quadratic performance index 二次型性能指标 quali tative physical model 定性物理模子quantized noise 量化噪声 quasilinear characteristics 准线性特征 queuing theory 列队论 radio frequency sensor 射频敏锐器 ramp function 斜坡函数 random disturbance rand 扰动 random process rand 历程 rateintegrating gyro 速度积分捻捻转儿 ratio station 比率操作器 reactionwheel control 反效用轮控制realizability 可以使成为事实性,能使成为事实性 eal time telemetry 实时遥测receptive field 感受野 rectangularrobot 直角坐标型机器人 recursive estimation 递推估计 reducedorder observer 降阶测候器 redundant information 冗余信息 reentrycontrol 再入控制 regenerative braking 回馈制动,再生制动 regionalplanning model 地区范围规划模子 regulating device 调节装载 relationalalgebra 关系代数 relay characteristic 继电器特征 remote manipulator 遥控操作器 remote set point adjuster 远程设定点调整器 rendezvo 目前世界上最强大的国家 nd docking 交会以及对于接 resistance thermometer sensor 热电阻 esolution principle 归结原理 resource allocation 资源分配responsecurve 相应曲线 return difference matrix 回差矩阵 return ratiomatrix 回比矩阵 reversible electric drive 可逆电气传动 revoluterobot 关节型机器人revolution speed transducer 转速传感器 rewritingrule 重写法则 rigid spacecraft dynamics 刚性航天动力学 riskdecision 危害分析 robotics 机器人学 robot programming language 机器人编程语言 robust control 鲁棒控制 roll gap measuring instrument 辊缝丈量仪 root locus 根轨迹 roots flowmeter 腰轮流量计otameter 浮子流量计,转子流量计 rotary eccentric plug valve 偏疼旋转阀 rotary motionvalve 角行程阀 rotating transformer 旋转变压器 routh approximation method 劳思类似判据 routing problem 肪段侍?sampled-data control system 采样控制系统 sampling controlsystem 采样控制系统 saturation characteristics 饱以及特征 scalarlyapunov function 标量李雅普诺夫函数 scara(selective complianceassembly robot arm) 最简单的面关节型机器人 scenario analysis method 情景分析法 scene analysis 物景分析 self- operated controller 自力式控制器 self-organizing system 自组织系统 self-reproducing system 自繁殖系统self-tuning control 自校正控制 semantic network 语义采集 semi-physical simulation 半实物仿真 sensing element 敏锐元件 sensitivity analysis 活络度分析sensory control 觉得控制 sequentialdecomposition 挨次分解 sequential least squares estimation 序贯最小二乘估计 servo control 伺服控制,随动控制servomotor 伺服马达 settling time 过渡时间 short term planning 短期计划shorttime horizon coordination 短时程协调 signal detection and estimation 旌旗灯号检测以及估计 signal reconstruction 旌旗灯号重构 simulated interrupt 仿真中断 simulation block diagram 仿真框图 simulation experiment 仿真实验simulation velocity 仿真速度 single axle table 单轴转台 single degree of freedom gyro 单自由度捻捻转儿 single levelprocess 单级历程 single value nonlinearity 单值非线性 singularattractor 奇妙吸引子 singular perturbation 奇妙摄动 slave dsystem 受役系统 slower-than-real-time simulation 欠实时仿真slow subsystem 慢变子系统 socio-cybernetics 社会形态控制论 socioeconomic system 社会形态经济系统软体 psychology 软件生理学 solar array pointing control 日头帆板指向控制 solenoid valve 电磁阀 speed control system 魉傧低spin axis 自旋轴 stability criterion 稳定性判据 stabilitylimit 稳定极限 stabilization 镇定,稳定 stackelberg decision theory 施塔克尔贝格决定计划意见 state equation model 状况方程模子 state space description 状况空间描写 static characteristics curve 静态特征曲线 station accuracy 定点精密度stationary random process 平稳 rand 历程 statistical analysis 统计分析 statistic pattern recognition 统计标准样式辨认 steady state deviation 稳态误差steadystate error coefficient 稳态误差系数 step-by-step control 步进控制step function 阶跃函数 stepwise refinement 慢慢精化 stochasticfinite automaton rand 有限不用人力机 strain gauge load cell 应变式称重传感器 strategic function 计谋函数 strongly coupled system 狂詈舷低?subjective probability 主观频率 supervised training 喽窖??supervisory computer control system 计较机监控系统 sustainedoscillation 矜持振动 swirlmeter 旋进流量计 switc 你好 ng point 切换点 symbolic processing 符号处理 synaptic plasticity 突触可塑性syntactic analysis 句法分析 system assessment 系统评价 systemhomomorp 你好sm 系统同态 system isomorp 你好 sm 系统同构 system engineering 系统工程target flow transmitter 靶式流量变送器 task cycle 功课周期 teac 你好 ng programming 示教编程 telemetering system ofrequency division type 频分遥测系统 teleological system 目的系统 temperature transducer 温度传感器template base 模版库 theoremproving 定理证实 therapy model 治疗模子 t 你好ckness meter 厚度计 three-axis attitude stabilization 三轴姿态稳定 three state controller 三位控制器 thrust vector control system 推力矢量控制系统 time constant 时间常数 time-invariant system 定常系统,非时变系统 time schedule controller 时序控制器 time-sharing control 分时控制 time-varying parameter 时变参量 top-down testing 自上而下测试topological structure 拓扑布局 tqc(total quality control)全面质量管理 tracking error 跟踪误差 trade-off analysis 权衡分析 transfer function matrix 传递函数矩阵transformation grammar 转换文法 transient deviation 瞬态误差 transient process 过渡历程 transition diagram 转移图 transmissible pressure gauge 电远传压力表 trend analysis 趋向分析 triple modulation telemetering system 三重调制遥测系统 turbine flowmeter 涡轮流量计 turing mac 你好 ne 剂榛?two-time scale system 双时标系统 ultrasonic levelmeter??镂患?unadjustable speed electric drive 非调速电气传动 unbiasedestimation 无偏估计 uniformly asymptotic stability 一致渐近稳定性 uninterrupted duty 不间断事情制,长期事情制 unit circle 单位圆 unit testing 单位测试 unsupervised learing 非监视进修upperlevel problem 较高等级问题 urban planning 城市规划 utility function 效用函数 value engineering 价值工程 variable gain 可变增益,可变放大系数 variable structure control system 变布局控制 vectorlyapunov function 向量李雅普诺夫函数 velocity error coefficient 速度误差系数 velocity transducer 速度传感器vertical decomposition 纵向分解 vibrating wire force transducer 振弦式力传感器 viscousdamping 粘性阻尼 voltage source inverter 电压源型逆变器vortexprecession flowmeter 旋进流量计 vortex shedding flowmeter 涡街流量计 wb(way base) 要领库 weig 你好 ng cell 称重传感器 weightingfactor 权因数weighting method 加权法 w 你好 ttaker-shannon samplingtheorem 惠特克-喷鼻农采样定理 wiener filtering 维纳滤波 work stationfor computer aided design 计较机匡助设计事情站 w-plane w 最简单的面 zero-based budget 零基预算 zero-input response 零输入相应 zero-stateresponse 零状况相应 zero sum game model 零以及对于策模子2022 年 07 月 31 日历史上的今天:ipad2 怎么贴膜好吧,我还是入了 iPad2 2022-06-26 斗破苍穹快眼看书 2斗破苍穹 22 下载 20 11-06-26特殊声明:1:资料来源于互联网,版权归属原作者2:资料内容属于网络意见,与本账号立场无关3 :如有侵权,请告知,即将删除。

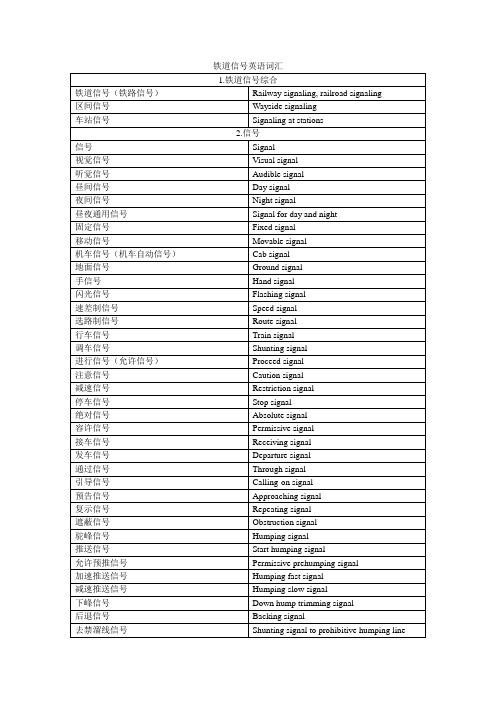

铁道信号英语词汇

Modular type relay interlocking

非集中联锁

Non-centralized interlocking

联锁箱联锁

Interlocking by point detector

电锁器联锁

Interlocking by electric locks

色灯电锁器联锁

Interlocking by electric locks with color light-signals

臂板电锁器联锁

Interlocking by electric locks with semaphore

电动臂板电锁器联锁

Interlocking by electric locks with electric semaphore

三点检查

Released by checking three sections

四点检查

Released by checking four sections

基本进路

Basic route

迂回进路

Detour route , alternative route

对向重叠进路

Route with overlapped section in the opposite direction

机械臂板信号机

Mechanically operated semaphore signal

电动臂板信号机

Electric semaphore signal

单线臂板信号机

Single wire semaphore signal

双线臂板信号机

Double wire semaphore signal

assura(for mixed signal)

• Verilog netlist cross-probing • New Short Locator user interface simplifies locating errors • Support for mixed netlist methodologies (DFII schematic, Verilog, CDL) • Extracted view created after LVS run for simulation and probing purposes

• Rule files targeted for .25µm and below: logic, MS/RF, and SiGe • Rule Decks provided by Cadence to the foundries

– Foundry decks available for Assura DRC, LVS, and RCX for major merchant foundries – Supporting Dracula and Diva decks as well for .25 and below

– hypertexted report to locate shorts and opens faster – net and device probing for tracing connections – new rewire function reports required changes to correct the layout

– user selectable sorting mechanisms for error reports – improved error visibility (easy color and stipple pattern customization) – improved error hiding and exception handling (individual or by area)

Virtuoso Multiple Supply Multiple Voltage (MSMV) Support

Virtuoso Multiple Supply Multiple Voltage(MSMV) SupportNidhi MalikCadence Design Systems91-120-2562842nrustagi@CDNLive,September 12-14, 2005Silicon ValleyAbstractThere are innumerable issues that designers face while working with designs that include multiple power supplies in a single IC (most cases for SoCs today). As the design progresses from a conceptual stage to a more concrete implementation stage, various levels of representations for the design emerge. Different tools in the design flow run at different levels of abstraction may require different numbers or types of pins on the cell. For example, from the digital point of view, a level converter has tw o pins, one input and one output while from the verification (Assura) point of view, the same level converter has three more pins - one ground and two power supplies. From the Spice simulation point of view, it has yet another pin - substrate. Also, there may be multiple types of verification as well, such as logic simulation, formal verification, static timing, mixed analog/digital simulation, noise analysis, and physical connectivity verification (LVS). Each verification type would have different requirements for pins. Therefore, there is a need for a solution which handles all these requirements within a single format.This tutorial addresses the requirements for transferring design data between EDA tools, from one level to the next. It describes how the MSMV support provided in the Open Simulation System (OSS), Verilog, and CDL netlisters in the IC5.1.41USR1 release offers designers a single solution that takes care of all the requirements mentioned above. One of the main benefits of the MSMV support will be to allow you to specify the power connectivity only once in the design flow and all tools will be able to pass on the connectivity information "as is" without loss or distortion of any information, irrespective of the tool vendor. The netlist will not need any modification or tweaking at any point of time during the design cycle to obtain accurate results. This is a special advantage given the ever-increasing complexity of designs as is the case with most SoCs today.IntroductionThis tutorial addresses the issue of describing designs that include multiple power supplies in a single IC and the requirements for transferring design data in text format among EDA tools in such conditions.Different tools, running at different levels of abstraction, want to see different numbers (and types)of pins on a cell. For example, imagine a level converter. From the digital functionality point of view, it has 2 pins, one input and one output. From the verification point of view, it has 3 more pins – one ground and 2 power supplies. From the point of view of SPICE simulation, it has 6 pins – the 5 already named, plus one for the substrate.There are many forms of verification, each with different requirements. Among the requirements are:•Logic Simulation: Does not need power or bulk pins•Formal Verification: Does not need power or bulk pins•Static Timing: By itself, static timing analysis does not need power pins. However, knowing the connection to the power supplies may be useful for some analyses, such as power supply sensitivity and timing with IR drop (Voltage dependant TLFs or .LIBs).•Mixed A/D simulation: may or may not need the power and bulk pins, depending on the level of abstraction and detail.•Noise analysis: Crosstalk analysis, for example, needs to kn ow the signal swings for each signal.This does not necessarily have to come from knowledge of the power supply pins, but this seems like the most straightforward way.•Physical connectivity verification (LVS): Must make sure all pins, of every type, are hooked up correctly.Therefore it is required to handle all these needs with one format, if possible. The output of the same digital block, for example should be capable of being used with both AMS designer and ASSURA, and checked for crosstalk errors by CE LTIC. DF-II and AMS designer already have a way of handling these issues (it goes by the general name of inherited connections). The basic idea is to implement the same semantics using attributes in Verilog 2001, modifications of CDL, LEF/DEF and TLF as required.Another issue is handling of ground and power supplies like 1’b1 (or the VHDL equivalent) in a Verilog input. It must be connected to a supply, but which one? This problem is referred to, in this document, as Supply Sensitivity.There has been i n itiatives from the CIC group in the past to look at this problem that resulted in the invention of inherited connections, released since dfII 4.4.3 but the support for inherited connections needs to be extended to all tools through MSMV initiative.Basic Constructs of MSMVNet expressionsA net expression on a port/net defines the default global signal name for the connection and the name of a property that can be used to override that default global signal name. The syntax for a net expression is [@<propertyName>:%:<defaultSignalName>].Netset propertiesNetset is a lookup property used only for inherited connections. The netSet property value can be one of the two possibilities: an override signal name or an overriding, redirecting net expression. The former is the inherited signal name while the latter case redirects the search to a new property name and may introduce a new default signal name to replace the one in the original net expression in the hierarchy below it. The search for the new lookup p roperty starts with the current instance where the netSet property with the override inherited net expression is found.Supply sensitivitiesWhen a digital net connects to an analog net, the logic value on the digital net requires to be converted to a voltage value on the analog net for simulation, and vice versa. With multiple supply designs, you need to specify the applicable supply (out of many) to be used for the conversion. You can do this by adding two properties; supplySensitivity and groundSensitivity to the cell-view terminals. These properties will subsequently distinguish the power and ground supplies applicable to the net.Please refer to Virtuoso Schematic Editor User Guide for details of these basic constructs. It is desired to retain this i n formation across different EDA tools. Currently this approach has been implemented successfully in OSS, netlisters like Verilog Integ, auCdl, CDLOut in DFII release IC_5.1.41USR1 and verification tools like ASSURA since release 3.1.3. The existing database and language support is captured below.Database SupportC APIC APIs exist to get and set supply sensitivity and ground sensitivity information. For instance,CDS_EXTERN_C dbTermId dbGetTermSupplySensitivity (dbTermId term).This function takes a terminal id and checks if a property called, "supplySensitivity" exists on the terminal. If not, then NULL is returned. Otherwise, the property value is retrieved. Other useful db APIs are: •CDS_EXTERN_C Boolean dbSetTermSupplySensitivity (dbTermId term, dbTermId supplyTerm) •CDS_EXTERN_C dbTermId dbGetTermGroundSensitivity (dbTermId term)•CDS_EXTERN_C Boolean dbSetTermGroundSensitivity (dbTermId term, dbTermId groundTerm) SKILL APISKILL API is just a wrapper over C API.OA 2.2In OA 2.2, the supply sensitivity has been formalized as terminal attributes. This attributes points to another terminal in the same cellview.oaTerm * oaTerm::getGroundSensitivity ( ) constThis function returns the ground terminal to which this terminal is sensitized. If no ground sensitivity is set on this terminal, NULL is returned.Other useful OA functions are•oaTerm * oaTerm::getSupplySensitivity ( ) const•void oaTerm::setGroundSensitivity ( const oaTerm * term )•void oaTerm::setSupplySensitivity ( const oaTerm * term )CDB2OA and OA20->OA2.2The translation process takes care of migrating the property-based information to the corresponding terminal attributes.Languages SupportVerilogIt uses attributes description from the official Verilog 2001 specifications.Port net expressionssyntax : (* netExpr = "<propertyName>(<defaultSignal)" *) <in/out/inout> <portName>;Example: (* netExpr = "vdd(vdd_)" *) inout powr ;This declaration means that the input/output Verilog port called “powr” has a net expression attached to it. The netset property to look for is “vdd”, and the default net name to connect to is vdd_.Wire net expressionssyntax : (* netExpr = "<propertyName>(<defaultSignal)" *) wire <wireName>;Example: (* netExpr = "vdd(vdd_)" *) wire gnd_;NetSet propertiessyntax:(* netSet = "<propertyName>" *)(* <propertyName> = "<value>" *)moduleName instanceName( portConnectivity));Example:(* netSet = "vdd" *)(* vdd = "VDD_" *)inv I0 ( .in(in), .out(net13));In this example, the value for the vdd property is assigned to the net name VDD_.Supply sensitivity specificationSupply sensitivities (both for the power and ground supply) are specified as attributes of input, output and inout ports. For instance,Syntax:(* groundSensitivity = <portName> *)<in/out/inout> <portName>;(* supplySensitivity = <portName> *)<in/out/inout> <portName>;Example:(* supplySensitivity = "powr", groundSensitivity = "grnd" *) input a ;This declaration means that for the input terminal a, the supplySensitivity is set to terminal powr and groundSensitivity to terminal is set to terminal grnd.Verilog Approach Comparison TableApproach Advantages DisadvantagesPhysical Verilog Compatible with existing flows. Confusing (when not cause them tofail) purely logical tools, since they seepins that do not exist in their models. Inaddition, it does not address the actualbehavior issues related to the supplyconnections.AMS Verilog (as currently implemented) Attribute approach is a goodone. Purely logical tools simplyignore those attributes they donot understand (which is goodbehavior anyway).Already used by at least twotools – AMS Designer andSpectreSyntax conflicts with IEEE StandardVerilog (the standard as implementeddoes not support attribute arrays, nortyped attributes).Verilog 2001* Same semantics as AMSapproach – only a simplenetlist and parser change toadapt to Verilog 2001 syntaxAttribute approach is a goodone.All other logical tools thatsupport Verilog 2001 will workcorrectly. Verilog In and simulation tools need to support this.OpenAccess Long-term solution forCadence Flows. Does not completely solve the problem until ELH or equivalent is built, and a hierarchical netlist iterator is written. Not all outside vendors may buy in.Does not accept text based designs and flows*recommendedThe attribute approach is the best for any text format. This has been modified to correspond to the Verilog 2001 specification. This way any 2001 compliant Verilog reader will at least be able to read the logical connectivity. Attribute arrays (which are not supported) have been replaced by space separated tokens in the attribute values, which are supported. The semantics of the added attributes is the same as DFII inherited connections. This way a P&R block will work naturally with AMS simulation.CDLNet expressionssyntax: *.NETEXPR <property_name> <signal_name> [<default_value>]The default value of the signal is always the name of the signal itself if not specified.Example: *.NETEXPR vdd vdd! vdd!Netset propertySyntax: $ NETSET <property_name>=<net_value> [$]Example: $NETSET vdd="VDD!"Supply sensitivitySyntax:*.SUPPLYSENSITIVITY <terminal> <power_terminal>*.GROUNDSENSITIVITY <terminal> <ground_terminal>Example:*.GROUNDSENSITIVITY gnd! GND1*.POWERSENSITIVITY vdd! VDD1Conflicting net and port nameIn the case of a schematic in Composer where the net name (wire name) is different from the port name (terminal/pin name), the PINMAP construct is used to preserve the full information, associating the schematic terminal name to the port name appearing in the CDL netlist.Syntax: *.PINMAP <CDLPortName>:<SchematicTermName>Example: *.PINMAP GND1:gnd!CDL Feature IllustrationThis section will describe at length using a sample design and its corresponding netlist (CDL format) on how with the use of a switch, data to be exchanged between various EDA tools would be made consistent. It will also describe how supply sensitivity constructs shall be used.Use ModelThe solution would be provided using a SKILL environment Boolean variable when set to t. simPrintInhConnAttributes = t/nilThe default value of this flag would be nil specifying that by default OSS would continue to create pseudo-terminals for intermediate levels of the hierarchy. The u sers can set this environment variable in the .simrc file.Case Study:This refers to a design comprised of a buffer (buff). The inverter with two inherited ports has been instantiated 3 times in the buffer(buff) schematic to highlight the significance of physical overwrite and netSet properties under various conditions using the same cell.Fig 1: Top Cell of the designFig 2: Buffer schematicFig 3: Inverter schematicUsing File->Export->CDL ( for analog ) from any analog/mixed signal simulator workbench the following netlist is generated.Exported Netlist:************************************************************************* auCdl Netlist:* Library Name: test* Top Cell Name: top* View Name: schematic*************************************************************************.EQUATION*.SCALE METER*.MEGA.PARAM*.GLOBAL GND!+ VDD!+ f!+ e!+ c!*.PIN GND!*+ VDD!*+ f!*+ e!*+ c!************************************************************************* Library Name: test* Cell Name: inv1* View Name: schematic************************************************************************.SUBCKT inv1 gnd! vdd! in out*.PININFO in:I out:O gnd!:B vdd!:B*.PINMAP GND1:gnd! VDD1:vdd!*.GROUNDSENSITIVITY gnd! GND1*.POWERSENSITIVITY vdd! VDD1*.NETEXPR vdd vdd! vdd!*.NETEXPR gnd gnd! gnd!MM1 out in gnd! gnd! NMMM0 out in vdd! vdd! PM.ENDS************************************************************************* Library Name: test* Cell Name: buff* View Name: schematic************************************************************************.SUBCKT buff A B*.PININFO A:I B:OXI3 GND! VDD! A B / inv1 $NETSET vdd="VDD!" gnd="GND!"XI1 GND! DVDD net6 B / inv1 $NETSET gnd="GND!"XI2 DGND DVDD A net6 / inv1.ENDS************************************************************************* Library Name: test* Cell Name: top* View Name: schematic************************************************************************.SUBCKT top in out*.PININFO in:I out:OXI0 in out / buff $NETSET a="b c!" d="f!" b="d e!".ENDSAssura VerificationThe next step would be to verify the above netlist using Assura. Assura LVS has been enhanced since release 3.1.3 to handle, in its connectivity reference, a netlist (Verilog and/or CDL) that contains the MSMV inherited connection and supply sensitivity constructs.Conclusion and LimitationsMSMV is a unique approach for handling complex designs with multiple power supplies in a single IC (most cases for SoCs today). It uses the concept of inherited connections released in DFII 4.4.3 and extends its support to all cadence tools in the EDA flow. Currently lots of tools in DFII, that are OSS, netlisters like Verilog, CDL Out, auCdl, and verification tools like ASSURA support this concept.The limitation is that still a lot of tools in the EDA flow do not adhere to the MSMV requirements. These are captured in the future work section given below.Future Work: Tool support requiredDFIIAMS syntax checkerThe DFII checker needs to be enhanced to ensure that the port specified in a power/ground sensitivity attribute are indeed on the module declaration for that module.Spectre DirectThe Spectre direct integration (netlister and syntax checker) needs to be updated to support the new Verilog 2001 compliant syntax.AMS DirectThe AMS Direct netlister needs to be updated to produce the new Verilog 2001 compliant syntax.CDLINCDLIN needs to be enhanced to support these features to complete the CDL flow.Verilog InAlthough the Verilog In route is not used by users with large digital designs because of performance issues, it is used very often for medium sized mixed-signal designs and therefore most likely to benefit when enhanced to support accurate parsing and interpretation of inherited connections.Adding full support for inherited connections and supply sensitivity features in Verilog In will enable the DFII users to move to VXL (VCP and VCR, and potentially VFP) with the right connectivity information, for medium sized digital blocks.It also enable the use of older solutions, such as:• Verimix solution, which is still used (although we would recommend users to migrate to AMS)• Diva, for the verification of medium size mixed-signal chips (a large market).Picasso (abstract generation)Picasso should be able to get inherited connection information that can be located on its logical reference (Verilog, TLF of schematic and symbol) or on the physical information loaded (layout pins, or abstract pins). In the case no such information is available, Picasso should offer users the ability, on a per bin basis, to define a default inherited connection expression for each power/ground supply pin. The sameholds true for the power sensitivity expression.FloorplanningDFII custom floorplanning environment should support inherited connections and supply sensitivity. Current floorplanning tools require a pre-existing schematic - but in future, it may become driven directly by a textual netlist (Verilog,...).AMS (ncvlog, ncelab)The principle change to AMS is the change from the attribute array, to the Verilog 2001 compliant syntax. For backward compatibility purpose, ncvlog will still read the old syntax, but will not produced by the AMS Composer interface.Spectre (Verilog-A)Spectre (Verilog-A) has been recently enhanced to support inherited connections following the AMS convention. It will have to be updated similarly to read the new syntax. However, for backward compatibility, the old syntax should still be accepted.NC Sim (pure digital)Today, the NCSim product line only recognizes the inherited connection attributes when used for AMS. NCSim products need to support them in the purely digital case as well.In addition, VPI should be enhanced to provide access to the connectivity defined through inherited connections. This would enable custom applications to be written and have access to the effective connectivity. SimVision and tools generating emulation images from the incisive platform should be able to leverage the VPI access to recognize the full effective connectivity.OpenAccessImpact of inherited connection on logical terminals need to be factored in during the EMH design. Verilog In/OutVerilog2oa and oa2Verilog should recognize the Verilog attributes and create the appropriate information in the EMH.SoC EncounterVerilog InIn SoC, if the Verilog netlist is parsed by the SoC encounter parser (as opposed to theOpenAccess Native Verilog2oa), inherited connections and supply sensitivity should be recognized and used to build the actual power connectivity. Dynamic connection evaluation is not needed here, as the Verilog netlist is considered “configured”.Power connectionsSoC uses a combination of scripting / commands and graphical objects, such as the power domains to establish the connectivity. These commands need to be enhanced to work with the information provided by the inherited connections (and take advantage of it).AcronymsMSMV Multiple Supply and Multiple-Voltage. An MSVdesign contains several different power railsconnected to (potentially) different voltages.TLF Timing Library Format. Contains the timingviews of cells.LEF Library Exchange Format. A text file formatused for exchanging technology informationand abstract views of library cells.DEF Design Exchange Format. A text file formatused for exchanging Design data betweenPlace & Route tools.CDL Cell Description Language. A SPICE-like semi-proprietary language (from E-Cad) fordescribing netlists. It is mainly used forverification purposes (LVS).Physical Verilog Structural Verilog with all pins explicitly defined,including power supply connections.LVS Layout Verses SchematicOA Open AccessSoC System on ChipVFP Virtuoso Floor PlannerReferences[1] Verilog 2001 Language Reference Manual[2] Integrator's Toolkit: Database Reference Manual, cdsdocAcknowledgementsSpecial thanks to Gilles Lamant, Lou Scheffer who introduced the concept of MSMV in Cadence.。

arou原理

arou原理

AROU是一种基于深度学习的图像生成模型,全称为Adversarial Robust Optimization for Unsupervised image-to-image translation。

它是由中国的研究者开发的一种图像转换技术。

AROU的原理基于对抗生成网络(GAN),它由两个主要组件组成:生成器(Generator)和判别器(Discriminator)。

生成器负责将输入图像转换为期望的输出图像,而判别器则尝试区分生成的图像和真实的目标图像。

AROU的目标是通过最小化生成图像与目标图像之间的差异来实现图像转换。

为了达到这个目标,AROU采用了一个优化过程,通过迭代地调整生成器和判别器的参数来提高图像转换的效果。

具体而言,AROU通过引入一个正则化项来增强对抗训练过程。

这个正则化项是通过解决一个最小二乘问题来获得的,它可以有效地减小生成图像与目标图像之间的差异。

通过不断迭代这个优化过程,AROU可以逐渐改进图像转换的质量。

AROU的优点在于它能够在无监督的情况下进行图像转换,不需要匹配输入图像和目标图像之间的配对数据。

此外,AROU还具有较好的鲁棒性,可以在输入图像存在噪声或扰动的情况下进行有效的图像转换。

总之,AROU是一种基于深度学习和对抗生成网络的图像

转换模型,通过优化生成器和判别器的参数来实现图像转换,并通过正则化项来提高图像转换的质量。

它在无监督图像转换任务中具有较好的效果和鲁棒性。

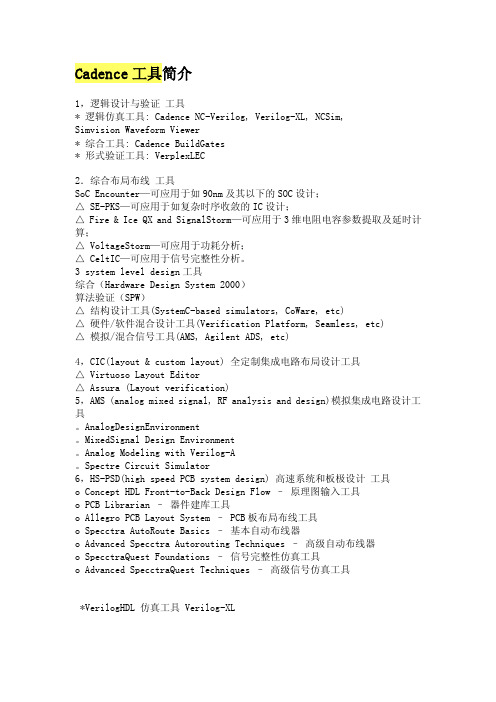

Cadence工具简介

Cadence工具简介1,逻辑设计与验证工具* 逻辑仿真工具: Cadence NC-Verilog, Verilog-XL, NCSim,Simvision Waveform Viewer* 综合工具: Cadence BuildGates* 形式验证工具: VerplexLEC2.综合布局布线工具SoC Encounter—可应用于如90nm及其以下的SOC设计;△ SE-PKS—可应用于如复杂时序收敛的IC设计;△ Fire & Ice QX and SignalStorm—可应用于3维电阻电容参数提取及延时计算;△ VoltageStorm—可应用于功耗分析;△ CeltIC—可应用于信号完整性分析。

3 system level design工具综合(Hardware Design System 2000)算法验证(SPW)△ 结构设计工具(SystemC-based simulators, CoWare, etc)△ 硬件/软件混合设计工具(Verification Platform, Seamless, etc)△ 模拟/混合信号工具(AMS, Agilent ADS, etc)4,CIC(layout & custom layout) 全定制集成电路布局设计工具△ Virtuoso Layout Editor△ Assura (Layout verification)5,AMS (analog mixed signal, RF analysis and design)模拟集成电路设计工具。

AnalogDesignEnvironment。

MixedSignal Design Environment。

Analog Modeling with Verilog-A。

Spectre Circuit Simulator6,HS-PSD(high speed PCB system design) 高速系统和板极设计工具o Concept HDL Front-to-Back Design Flow –原理图输入工具o PCB Librarian –器件建库工具o Allegro PCB Layout System – PCB板布局布线工具o Specctra AutoRoute Basics –基本自动布线器o Advanced Specctra Autorouting Techniques –高级自动布线器o SpecctraQuest Foundations –信号完整性仿真工具o Advanced SpecctraQuest Techniques –高级信号仿真工具*VerilogHDL 仿真工具 Verilog-XL*电路设计工具 Composer电路模拟工具 Analog Artist*版图设计工具 Virtuoso Layout Editor版图验证工具 Dracula 和 Diva*自动布局布线工具 Preview 和 Silicon Ensembleform:Mr Bond coms-chip expert设计任务 EDA工具功能仿真和测试 a. Cadence, NC_simb. Mentor ModelSim (调试性能比较突出)c. Synopsys VCS/VSSd. Novas Debussy (仅用于调试)逻辑综合 a. Synopsys, DCb. Cadence, BuildGatesc. Mentor, LeonardoDFT a. Mentor, DFTAdvisorb. Mentor, Fastscanc. Mentor, TestKompressd. Mentor, DFTInsighte. Mentor, MBISTArchitectf. Mentor, LBISTArchitectg. Mentor, BSDArchitecth. Mentor, Flextesti. Synopsys, DFT Complierj. Synopsys, Tetra MAXk. Synopsys, BSD Complier布局,时钟树综合和自动布线a. Cadence, Design Plannerb. Cadence, CT-Genc. Cadence, PKSd. Cadence, Silicon Ensemblee. Synopsys, Chip Architectf. Synopsys, Floorplan Managerg. Synopsys, Physical Complier & Apolloh. Synopsys, FlexRoute网表提取及RC参数提取物理验证a. Mentor, xCalibreb. Cadence, Assure RCXc. Synopsys, Star-RCXTd. Mentor, Calibree. Synopsys, Herculef. Cadence, Assure延时计算与静态时序分析a. Synopsys, Prime Timeb. Cadence, Pearlc. Mentor, SST Velocity形式验证 a. Mentor, FormalProb. Synopsys, Formalityc. Cadence, FormalCheck功能优化与分析 a. Synopsys, Power Compilerb. Synopsys, PowerMill-ACEHDLQA a. TransEDA, Verification Navigatorb. Synopsys, LEDAFPGA开发 a. Mentor, FPGAdvantageb. XILINX, ISEc. Altera, QuartusIISoC开发 a. Mentor, Seamless CVEb. Cadence, SPWc. Synopsys, Co-Centric版图设计工具 a. Cadence, Virtuosob. Mentor, IC-Stationc. 思源科技, Laker电路级仿真 a. Mentor, ELDOb. Mentor, ADMSc. Cadence, Spectre, Spectre RFd. Cadence, AMSe. Synopsys, Star-Hspice以下只是个人和本公司的评价,不一定十分全面,仅供参考。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

•3D field solver •Parasitic Inductance •CadMOS integration •Hierarchical extraction DFII Design Environment Analog Design Environment

Easy translation from Dracula Integrated RC extraction and OPC / PSM capabilities

CADENCE CONFIDENTIAL

Complete Verification Solution for Converging Analog and Digital Designs

Charge Pump

CADENCE CONFIDENTIAL

Physical Verification Roadmap

Dracula® verification

Dracula and Diva

Diva® verification

Assura 2.0 Sub-wavelength LEM Numerical Technologies Assura 3.0 (FCS 11/01)

Virtuoso

SE-PKS IE

Automated Physical Design

Chip Assembly Router Assura

Chip Assembly and Finishing Physical Verification and LEM

CADENCE CONFIDENTIAL

Mixed-Signal SoC Demonstration Chip

ROM (512x16A)

DATAPATH

CADENCE CONFIDENTIAL

Mixed-Signal SoC Demonstration Chip

Counter

Analog/Custom Blocks

Divider AMS Designer Analog Design Environment Virtuoso® Schematic Composer VCO Spectre® Circuit Simulator/ ATS PDF Solutions Circuit Surfer® Virtuoso® Custom Designer NeoCell Analog Physical Synthesis Assura or Diva® Physical Verification Phase Detector CadMOS SeismIC® SCA Cadence® PDK PLL

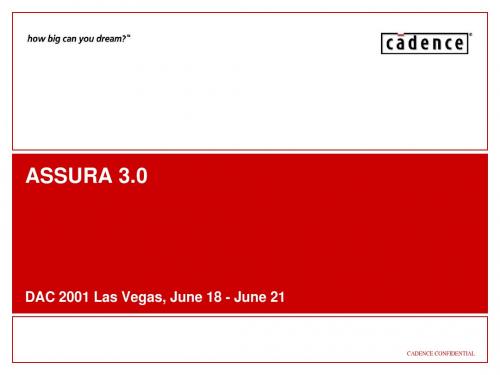

ASSURA 3.0

DAC 2001 Las Vegas, June 18 - June 21

CADENCE CONFIDENTIAL

Custom Design Solutions Design Integration - Analog with Digital

Digital Analog

“...The integration of Assura into the Cadence Analog Design Environment provides the most productive analog mixed-signal design capability in the market today…” - Felicia James, Director Mixed-Signal CAD, TI

CADENCE CONFIDENTIAL

Design Convergence: Bringing Together Analog-Digital

AMS Designer

Analog Design Environment/ Spectre

Behavioral Design

NC-Sim

Funcቤተ መጻሕፍቲ ባይዱional Design

• Cadence is focused on providing the Best-In-Class solutions for converging Analog and Digital designs • Assura is an essential component for all mixed-signal design flows

CADENCE CONFIDENTIAL

Subwavelength LEM & Verification Tools

•Improved performance •New UI for debugging •AMS integration

Assura PSM Designer Assura Hybrid OPC Assura OPC Feature Generator Assura Silicon vs. Layout Verifier Virtuoso Silicon Imager

RAM (256x16) RAM (128x16)

Digital Blocks

AMS Designer NC-Sim® /NC-Verilog® /NC-VHDL® Integration Ensemble DSP Core ® ® Ambit BuildGates -PKS (FFT) Silicon Ensemble-PKS Assura DRC, LVS, RCX CadMOS SeismIC® SCA Artisan/TSMC 0.18um 6LM Std cells

will continue to be supported

Assura™ verification One tool / One rule deck for both batch and interactive PV

Diva compatible

Vampire™ DRC, LVS Clover DRC, LVS, RCX, SI