电子设计毕业设计-CMOS二进制四位可预置可逆计数器

四进制二位设计模7计数计数器

四进制是一种基于4个数字的计数系统,数字分别是0、1、2、3。

一个二位的四进制计数器可以用来计数从00到33的所有数字。

在设计一个四进制二位计数计数器时,我们可以使用两个触发器和逻辑门来实现。

下面是一种可能的设计:

设计一个触发器,可以存储一个四进制位的值。

这可以是一个D触发器,它有一个数据输入(D)和一个时钟输入(CLK),以及一个输出(Q)。

连接两个触发器,形成一个二位计数器。

将第一个触发器的时钟输入(CLK)连接到一个时钟源或计时器。

将第一个触发器的输出(Q)连接到第二个触发器的数据输入(D)。

这样,第二个触发器将根据第一个触发器的输出进行更新。

为了实现计数逻辑,我们需要使用逻辑门。

使用与门和非门来生成适当的时钟信号和数据输入信号,以实现四进制计数。

以下是逻辑门的连接:

将第一个触发器的输出(Q)连接到一个与门的一个输入。

将第一个触发器的输出(Q)连接到一个非门。

将非门的输出连接到另一个与门的一个输入。

将时钟源或计时器连接到另一个与门的一个输入。

将第二个触发器的时钟输入(CLK)连接到与门的输出。

这个逻辑电路的作用是:当第一个触发器的输出为3时,它会激活非门,使得与门的输出为1,将时钟信号传递给第二个触发器,使其计数。

否则,与门的输出为0,第二个触发器的时钟输入保持不变,不进行计数。

这样,当时钟源或计时器的时钟信号输入到该电路时,二位四进制计数器将以顺序计数的方式显示从00到33的数字。

4位同步二进制加法计数器计数最大值

4位同步二进制加法计数器是一种常见的数字电路,用于实现二进制计数。

它可以将二进制数字表示为电信号,并且在每次输入脉冲时进行递增。

下面将详细介绍4位同步二进制加法计数器及其计数的最大值。

一、4位同步二进制加法计数器的原理1. 4位同步二进制加法计数器由4个触发器组成,每个触发器对应一个二进制位。

当输入一个脉冲时,每个触发器根据前一位的状态以及输入脉冲的信号进行状态转换。

这样就实现了二进制数的递增。

2. 触发器之间通过门电路连接,用于控制触发器状态的变化。

这些门电路可以根据具体的设计选择不同的逻辑门,常见的有AND门、OR 门、NOT门等。

3. 4位同步二进制加法计数器是同步计数器,即所有触发器同时接收输入脉冲,确保计数的同步性。

二、4位同步二进制加法计数器的计数最大值1. 4位二进制数的表示范围是0~15,因此4位同步二进制加法计数器的计数最大值为15。

2. 在计数到15后,再输入一个脉冲,计数器将重新从0开始计数,即实现了循环计数。

三、4位同步二进制加法计数器的应用1. 4位同步二进制加法计数器常用于数字电子钟、信号发生器等数字电路中,用于实现计数和定时功能。

2. 它还可以作为其他数字电路的组成部分,用于构建更复杂的逻辑功能。

3. 在数字系统中,计数器是十分重要的组件,它能够实现数字信号的计数和控制,广泛应用于各种数字系统中。

4位同步二进制加法计数器是一种重要的数字电路,通过它可以实现对二进制数的递增计数。

其计数的最大值为15,应用领域广泛。

希望本文内容能够对读者有所启发。

四、4位同步二进制加法计数器的工作原理4位同步二进制加法计数器是一种晶体管数字集成电路,它利用触发器和逻辑门等基本元件构成,能够实现二进制数字的加法计数。

在4位同步二进制加法计数器中,每个触发器代表一个二进制位,通过输入脉冲的控制,能够实现对二进制数的递增计数。

具体来说,当输入一个脉冲信号时,4位同步二进制加法计数器会根据触发器之间的连线和逻辑门的作用,根据之前的状态和输入脉冲的信号进行状态转换,从而实现二进制数的递增。

实验四位计数器设计样本

实验四 4 位计数器设计1.实验目学习quartusii 和modelsim用法;学习原理图和veriloghdl混合输入设计办法;掌握4 位计数器设计设计及仿真办法。

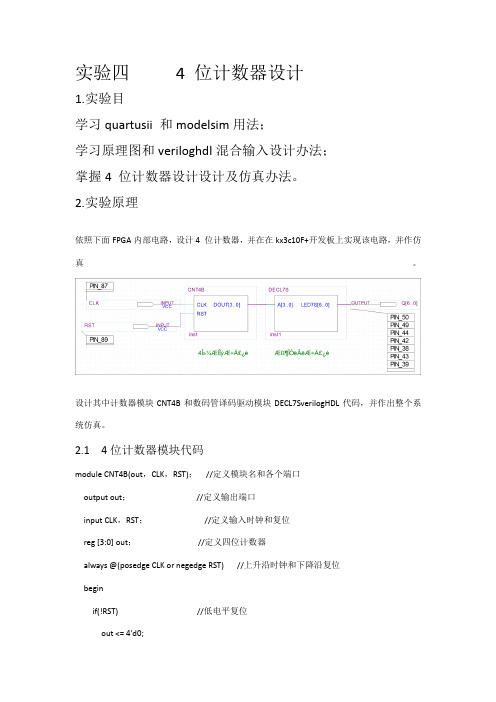

2.实验原理依照下面FPGA内部电路,设计4 位计数器,并在在kx3c10F+开发板上实现该电路,并作仿真。

设计其中计数器模块CNT4B和数码管译码驱动模块DECL7SverilogHDL代码,并作出整个系统仿真。

2.1 4位计数器模块代码module CNT4B(out,CLK,RST);//定义模块名和各个端口output out;//定义输出端口input CLK,RST;//定义输入时钟和复位reg [3:0] out;//定义四位计数器always @(posedge CLK or negedge RST) //上升沿时钟和下降沿复位beginif(!RST) //低电平复位out <= 4'd0;elseout <= out + 1;//每一种clk计数endendmodule效果图:2.2七段数码管代码module segled(out1,a);//定义模块名和输入输出端口input [3:0]a;//输入一种3位矢量output [6:0]out1;//输出一种6位矢量reg [6:0]out1;//reg型变量用于always语句always@(a) //敏感信号abegincase(a) //case语句用于选取输出4'b0000:out1<=7'b0111111;4'b0001:out1<=7'b0000110;4'b0010:out1<=7'b1011011; 4'b0011:out1<=7'b1001111; 4'b0100:out1<=7'b1100110; 4'b0101:out1<=7'b1101101; 4'b0110:out1<=7'b1111101; 4'b0111:out1<=7'b0000111; 4'b1000:out1<=7'b1111111; 4'b1001:out1<=7'b1101111; 4'b1010:out1<=7'b1110111; 4'b1011:out1<=7'b1111100; 4'b1100:out1<=7'b0111001; 4'b1101:out1<=7'b1011110; 4'b1110:out1<=7'b1111001; 4'b1111:out1<=7'b1110001; endcaseendendmodule //模块结束效果图:2.3综合模块代码// Copyright (C) 1991- Altera Corporation// Your use of Altera Corporation's design tools,logic functions// and other software and tools,and its AMPP partner logic// functions,and any output files from any of the foregoing// (including device programming or simulation files),and any// associated documentation or information are expressly subject // to the terms and conditions of the Altera Program License// Subscription Agreement,Altera MegaCore Function License// Agreement,or other applicable license agreement,including,// without limitation,that your use is for the sole purpose of// programming logic devices manufactured by Altera and sold by // Altera or its authorized distributors. Please refer to the// applicable agreement for further details.// PROGRAM "Quartus II 64-Bit"// VERSION "Version 13.1.0 Build 162 10/23/ SJ Web Edition" // CREATED "Tue Apr 11 22:35:09 "module cou(CLK,RST,Q);input wire CLK;input wire RST;output wire [6:0] Q;wire [3:0] SYNTHESIZED_WIRE_0; CNT4B b2v_inst(.CLK(CLK),.RST(RST),.out(SYNTHESIZED_WIRE_0)); segled b2v_inst1(.a(SYNTHESIZED_WIRE_0),.out1(Q));endmodule效果图:3.实验设备kx3c10F+开发板,电脑。

单片机课题设计(可预置可逆4位计数器)

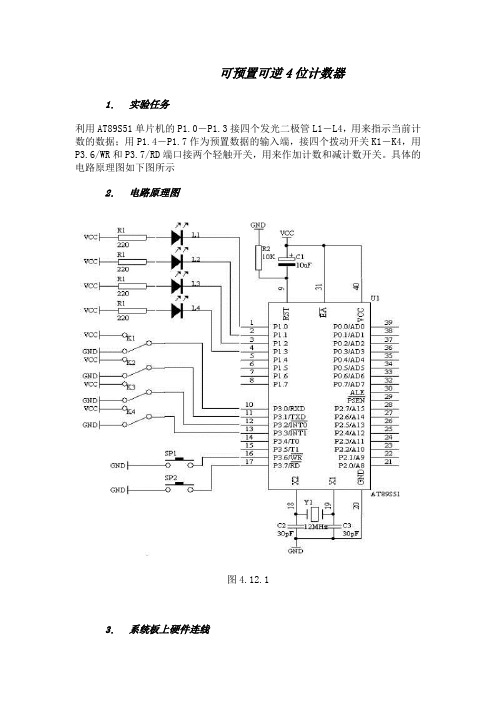

可预置可逆4位计数器1.实验任务利用AT89S51单片机的P1.0-P1.3接四个发光二极管L1-L4,用来指示当前计数的数据;用P1.4-P1.7作为预置数据的输入端,接四个拨动开关K1-K4,用P3.6/WR和P3.7/RD端口接两个轻触开关,用来作加计数和减计数开关。

具体的电路原理图如下图所示2.电路原理图图4.12.13.系统板上硬件连线(1.把“单片机系统”区域中的P1.0-P1.3端口用8芯排线连接到“八路发光二极管指示模块”区域中的L1-L4上;要求:P1.0对应着L1,P1.1对应着L2,P1.2对应着L3,P1.3对应着L4;(2.把“单片机系统”区域中的P3.0/RXD,P3.1/TXD,P3.2/INT0,P3.3/INT1用导线连接到“四路拨动开关”区域中的K1-K4上;(3.把“单片机系统”区域中的P3.6/WR,P3.7/RD用导线连接到“独立式键盘”区域中的SP1和SP2上;4.程序设计内容(1.两个独立式按键识别的处理过程;(2.预置初值读取的问题(3.LED输出指示5.程序框图图4.12.26.汇编源程序COUNT EQU 30HORG 00HSTART: MOV A,P3ANL A,#0FHMOV COUNT,AMOV P1,ASK2: JB P3.6,SK1LCALL DELY10MSJB P3.6,SK1INC COUNTMOV A,COUNTCJNE A,#16,NEXT MOV A,P3ANL A,#0FHMOV COUNT,A NEXT: MOV P1,AWAIT: JNB P3.6,WAIT LJMP SK2SK1: JB P3.7,SK2LCALL DELY10MSJB P3.7,SK2DEC COUNTMOV A,COUNTCJNE A,#0FFH,NEX MOV A,P3ANL A,#0FHMOV COUNT,A NEX: MOV P1,AWAIT2: JNB P3.7,WAIT2 LJMP SK2DELY10MS: MOV R6,#20MOV R7,#248D1: DJNZ R7,$DJNZ R6,D1RETEND7.C语言源程序#include <AT89X51.H>unsigned char curcount;void delay10ms(void){unsigned char i,j;for(i=20;i>0;i--)for(j=248;j>0;j--);}void main(void){curcount=P3 & 0x0f;P1=~curcount;while(1){if(P3_6==0){delay10ms();if(P3_6==0){if(curcount>=15) {curcount=15; }else{curcount++; }P1=~curcount;while(P3_6==0); }}if(P3_7==0){delay10ms();if(P3_7==0){if(curcount<=0) {curcount=0; }else{curcount--; }P1=~curcount;while(P3_7==0); }}}}。

实验三四位二进制计数器计数、译码与显示.doc

实验三四位二进制计数器计数、译码与显示一、实验目的1 学习并掌握用VHDL语言、语法规则2 掌握VHDL语言进行二进制计数器的设计3 掌握译码显示电路的设计4 掌握顶层文件的设计5 掌握综合性电路的设计、仿真、下载、调试方法。

二实验仪器设备1 PC机一台2 EDA教学实验系统,1套3 CPLD实验装置,1套三实验内容实验内容:(1) 设计7段译码显示电路程序;(参考实验一)(2) 设计四位二进制计数器,进行计数;(3) 进行顶层电路设计;(4) 对计数值,用7段显示器进行显示;(5) 进行电路功能仿真与下载。

四. 实验操作步骤1 开机,进入MAX+PLUSⅡ CPLD开发系统。

2 在主菜单中选NEW,从输入文件类型选择菜单中选文本编辑文件输入方式,进行文本编辑。

对7段译码显示电路、四位二进制计数器、顶层电路分别进行编辑、保存与仿真。

3 打开Assign主菜单,选择计划使用的CPLD芯片。

4 点击编译按钮,对顶层电路进行编译。

5 点击Floorplan Editor子菜单,为设计的电路分配芯片引脚。

6进行芯片下载与硬件测试。

建议输入信号引脚为:时钟信号:73脚或31脚(8K板) 42脚或44脚(10K板)使能信号、复位信号选,第一组DIP开关或第二组DIP开关或第三组DIP开关,相应引脚参考讲义;LED七段(a,b,c,d,e,f,g)输出分配也必须与实验装置的相关端匹配,具体引脚参考实验讲义。

(见表功,如可选引脚13、14、15、16、18、19、20(8K板)或16、17、18、19、21、22、23(10K板))。

设计参考框图如下:五. 实验程序1、四位二进制计数器译码程序library IEEE;use IEEE.std_logic_1164.all;entity sysegd isport (x: in std_logic_vector(3 downto 0);s : out std_logic_vector (6 downto 0));end entity;architecture bin27seg_arch of sysegd isbeginprocess(x)begincase x(3 downto 0) iswhen "0000" => s <= "1111110"; -- 0when "0001" => s <= "0110000"; -- 1when "0010" => s <= "1101101"; -- 2when "0011" => s <= "1111001"; -- 3when "0100" => s <= "0110011"; -- 4when "0101" => s <= "1011011"; -- 5when "0110" => s <= "1011111"; -- 6when "0111" => s <= "1110000"; -- 7when "1000" => s <= "1111111"; -- 8when "1001" => s <= "1111011"; -- 9when "1010" => s <= "1110111"; -- Awhen "1011" => s <= "0011111"; -- bwhen "1100" => s <= "1001110"; -- cwhen "1101" => s <= "0111101"; -- dwhen "1110" => s <= "1001111"; -- Ewhen "1111" => s <= "1000111"; -- Fwhen others => NULL;end case;end process;end architecture;2、四位二进制计数器计数程序library IEEE;use IEEE.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity segd7 isport (clk,en : in std_logic;x : buffer std_logic_vector (3 downto 0)); end entity;architecture one of segd7 isbeginprocess(clk)beginIF (CLK'EVENT AND clk='1') thenif en='1' thenIF (x="1111") THENx<="0000";ELSEx <= x+'1';END IF;end if;end if;end process;end architecture;3、四位二进制计数器顶层文件library ieee;use ieee.std_logic_1164.all;entity segdtop isport(clk,en :in std_logic;s : out std_logic_vector (6 downto 0)); end segdtop;architecture behave of segdtop issignal temp1:std_logic_vector(3 downto 0);component segd7port(clk,en : in std_logic;x : buffer std_logic_vector (3 downto 0)); end component;component sysegdport (x: in std_logic_vector(3 downto 0);s : out std_logic_vector (6 downto 0));end component;beginu0:segd7 port map(clk,en,temp1);u1:sysegd port map(temp1,s);end behave;六. 实验结果图1、四位二进制计数器译码程序图2、四位二进制计数器计数程序图3、四位二进制计数器顶层文件。

数电课程设计论文四位二进制加计数器(缺0100,0101,0110,1000,1001)

成绩评定表课程设计任务书摘要本文描述了四位二进制同步加法计数器的功能,并且缺省了状态0100,0101,0110,1000,1001。

计数器初始状态从0000开始,每来一个CP脉冲计数器就加1,当增加到0011时,直接跳到状态0111;再来一个CP脉冲,计数器直接跳到状态1010;当计数器加到1111时,给高位进位的同时计数器归零。

本课程设计分别通过QuartusⅡ和multisim软件设计实现此计时器。

在QuartusⅡ软件中先用VHDL语言描述此计数器,编译完成后,进行波形仿真,最后下载到试验箱中。

在multisim软件中首先设计实现此计数器功能的电路图,然后运行仿真电路图,通过LED灯亮灭的顺序和逻辑分析仪的波形变化情况验证电路图的正确性。

关键词:四位二进制加计数器;QuartusⅡ软件;multisim软件;目录1课程设计目的 (1)2课程设计实现框图 (1)3实现过程 (1)3.1QuartusⅡ实现过程(VHDL) (1)3.1.1建立工程 (2)3.1.2VHDL源程序 (5)3.1.3编译和仿真过程 (6)3.1.4引脚锁定与下载 (9)3.1.5仿真结果分析 (10)3.2Multisim实现过程(电路设计) (11)3.2.1设计原理 (11)3.2.2基于Multisim的设计电路图 (15)3.2.3逻辑分析仪显示的波形 (16)3.2.4仿真结果分析 (16)4设计体会 (17)5参考文献 (18)1课程设计目的1、了解数字系统设计方法。

2、熟悉VHDL语言及其仿真环境、下载方法。

3、熟悉Multisim环境。

4.设计实现四位二进制加计数器(缺0100,0101,0110,1000,1001)。

2课程设计实现框图图1所示是四位二进制同步加法计数器的结构示意框图。

CP是输入计数脉冲,所谓计数,就是计CP脉冲个数,每来一个CP脉冲,计数器就加一个1,随着输入计数脉冲个数的增加,计数器中的数值也增大,当计数器计满时再来CP脉冲,计数器归零的同时给高位进位,即要送给高位进位信号,图中的输出信号C就是要送给高位的进位信号。

可预置数的4位计时器电路图

可预置数的4位计时器电路图计时器在数字电路中是一个常见的电子元件,它用于计算时间和频率。

本文将介绍一个可预置数的4位计时器电路图设计,可以用于实现许多计时器应用。

本设计使用CMOS技术,具有低功耗和高可靠性等优点。

下面,我们将讨论该电路的各个方面以及如何构建它。

设计要求该电路需要满足以下要求:1.实现可预置数值的计时器功能。

2.4个7段数码管用于显示计数结果。

3.使用 CMOS 技术实现,具有低功耗和高可靠性。

电路原理这个电路是由两个主要部分组成: 一个实现可预置计数的计数器和一个7段显示器。

计数器被控制以完成计数任务,而7段显示器用于显示数码。

可预置计数器可预置计数器使用74LS161集成电路(U1~U4)实现。

这是一个4位计数器,每个计数器有一个时钟输入和Ripple Up/Down控制。

此外,它还有4个可读/可写的并行加载预置输入。

这些输入用于预加载计数器,以便从预定值开始计数。

是可预载入计数器的简单示意图:可预载入计数器每个计数器的载入输入 (Pr) 被连接到 AND 门电路,用于根据 Pr-enable 输入和计数器控制信号的状态来控制数字的预置。

这些控制信号由另外一个74LS161( U5) 生成。

4位计数器的所有输出( Q0~Q3) 都被连接到 BCD数码显示器的输入端。

通过将计数器的二进制值转换成对应的BCD值,就可以控制显示器显示正确的数字。

BCD数码显示器本电路采用常见的共阴极式4位BCD数码管(段选型),其极性为共阴极,因此控制开关使能数字的输出。

每个数字字形由7个LED数码管组成,数字点由一个小LED指示灯表示。

数码管七段输入端是相应位置的数字选择器输入。

使用7447译U4的输出。

码器驱动数码管。

输入信号由计数器的BCD(Q0Q3)输出提供。

选通信号来自计数器U1BCD数码显示器电路图根据上述电路原理和设计要求,下面是可预置数的4位计时器电路的完整电路图:74LS161可预置计数器:Pr5 = /UD0 & /ISEL2 Pr4 = /UD0 & ISEL2Pr3 = /UD1 & /ISEL2 Pr2 = /UD1 & ISEL2Pr1 = /UD2 & /ISEL2 Pr0 = /UD2 & ISEL2U5和U6的接法如下:CP1 = /ISEL0 & /ISEL1CP2 = /ISEL0 & ISEL1CP3 = ISEL0 & /ISEL1CP4 = ISEL0 & ISEL17486异或门的接法如下:/UD0 = CP0 ^ CP1 /UD1 = CP1 ^ CP2/UD2 = CP2 ^ CP3 /UD3 = CP3 ^ CP4数码管(4个)和7447译码器的接法如下:7447 a b c d e f g--------|--|---|---|----|---|---|---NUM0 |0 |0 |0 |0 |0 |0 |1NUM1 |1 |0 |0 |1 |1 |1 |1NUM2 |0 |0 |1 |0 |0 |1 |0NUM3 |0 |0 |0 |1 |1 |1 |0NUM4 |1 |0 |0 |1 |1 |0 |0NUM5 |0 |1 |0 |1 |1 |0 |0NUM6 |0 |1 |0 |0 |0 |0 |0NUM7 |0 |0 |0 |1 |1 |1 |1NUM8 |0 |0 |0 |0 |0 |0 |0NUM9 |0 |0 |0 |1 |1 |0 |0总结本文介绍了一个可预置数的4位计时器电路图,该电路使用CMOS技术,具有低功耗和高可靠性等优点。

《设计一个四位可逆二进制计数器》的实验报告

实验七设计一个四位可逆二进制计数器一、实验目的

掌握中规模集成计数器的使用方法及功能测试方法。

二、实验内容及要求

用D触发器设计一个异步四位二进制可逆计数器。

三、设计过程

(1)根据题意列出加计数状态表和驱动表,如下表所示。

(2)用卡诺图化简,如下图所示。

求得各位触器的驱动信号的表达式

11Q D

00Q D =

(2)用卡诺图化简,如下图所示。

求得各位触器的时钟方程的表达式

23Q CP =

12Q CP =

01Q CP =

CP

CP

(3)根据题意列出减计数状态表和驱动表,如下表所示。

33Q D =

22Q D =

11Q D =

00Q D =

(2)用卡诺图化简,如下图所示。

求得各位触器的时钟方程的表达式

23Q CP =

12Q CP =

01Q CP =

CP CP =0

由上分析可知:加减计数只在于时钟CP 的不同,若要使一个电路能够可逆计数,增设一控制开关,就可实现。

设K =1时为加计数,设K =0时为减计数,

加法:CP n = 1-n Q K 减法:CP n = 1-n Q K 则有:CP n =1-⊕n Q K

(或如 K=0时为加法: CP n =1-∙n Q K

K=1时为 减法: CP n =

1-n KQ =1

-n Q K 则有:

CP n =1-⊕n Q K

)

四、可逆计数器逻辑图如下:

四、实验用仪器、仪表

数字电路实验箱、万用表、74LS74、CC4030 五、实验步骤 六、实验数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CD4510BMS, CD4516BMSCMOS Presettable Up/Down CountersCD4510BMS Presettable BCD Up/Down Counter and the CD4516BMS Presettable Binary Up/Down counter consist of four synchronously clocked D-type flip-flops (with a gating structure to provide T -type flip-flop capability)connected as counters.These counters can be cleared by a high level on the RESET line,and can be preset to any binary number present on the jam inputs by a high level on the PRESET ENABLE line.The CD4510BMS will count out of non-BCD counter states in a maximum of two clock pulses in the up mode,and a maximum of four clock pulses in the down mode.If the CARRY IN input is held low,the counter advances up or down on each positive-going clock transition.Synchronous cascading is accomplished by connecting all clock inputs in parallel and connecting the CARRY OUT of a less significant stage to the CARRY IN of a more significant stage.The CD4510BMS and CD4516BMS can be cascaded in the ripple mode by connecting the CARRY OUT to the clock of the next stage.If the UP/DOWN input changes during a ter-minal count,the CARRY OUT must be gated with the clock,and the UP/DOWN input must change while the clock is high.This method provides a clean clock signal to the sub-sequent counting stage. (See Figures 13, 14.)These devices are similar to types MC14510 and MC14516.The CD4510BMS and CD4516BMS are supplied in these 16-lead outline packages:Features•High Voltage Types (20V Rating)•CD4510BMS - BCD Type •CD4516BMS - Binary Type •Medium Speed Operation -fCL = 8MHz Typ. at 10V•Synchronous Internal Carry Propagation •Reset and Preset Capability•100% Tested for Quiescent Current at 20V •5V, 10V and 15V Parametric Ratings•Standardized Symmetrical Output Characteristics •Maximum Input Current of 1µA at 18V Over Full Pack-age Temperature Range; 100nA at 18V and +25o C •Noise Margin (Over Full Package/Temperature Range)-1V at VDD = 5V -2V at VDD = 10V - 2.5V at VDD = 15V •Meets All Requirements of JEDEC Tentative Standard No.13B,“Standard Specifications for Description of ‘B’ Series CMOS Devices”Applications•Up/Down Difference Counting •Multistage Synchronous Counting •Multistage Ripple Counting •Synchronous Frequency DividersPinoutCD4510BMS, CD4516BMSTOP VIEWFunctional DiagramBraze Seal DIP *H4W †H45Frit Seal DIP*FBF †H1F Ceramic Flatpack H6W*CD4510B Only†CD4516B Only14151691312111012345768PRESET ENABLEQ4P4P1CARRY INQ1VSSCARRY OUTVDD Q3P3P2Q2UP/DOWN RESETCLOCK Q1Q2Q3Q4611142P1P2P3P4412133CARRY OUT7CARRY IN5RESETCLOCK UP/DOWN 1015PRESET ENABLEVDD = 16VSS = 819Data SheetDecember 1992File Number3338Absolute Maximum Ratings Reliability InformationDC Supply Voltage Range, (VDD). . . . . . . . . . . . . . . .-0.5V to +20V (Voltage Referenced to VSS Terminals)Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to VDD +0.5V DC Input Current, Any One Input. . . . . . . . . . . . . . . . . . . . . . . . .±10mA Operating Temperature Range . . . . . . . . . . . . . . .-55o C to +125o C Package Types D, F, K, HStorage Temperature Range (TSTG). . . . . . . . . . .-65o C to +150o C Lead T emperature (During Soldering) . . . . . . . . . . . . . . . . .+265o C At Distance1/16±1/32Inch(1.59mm±0.79mm)from case for 10s Maximum Thermal Resistance. . . . . . . . . . . . . . . .θjaθjc Ceramic DIP and FRIT Package . . . .80o C/W20o C/W Flatpack Package. . . . . . . . . . . . . . . .70o C/W20o C/W Maximum Package Power Dissipation (PD) at +125o CFor T A = -55o C to +100o C (Package Type D, F, K) . . . . . .500mW For T A = +100o C to +125o C (Package Type D, F, K) . . . . .DerateLinearity at 12mW/o C to 200mW Device Dissipation per Output Transistor. . . . . . . . . . . . . . . .100mW For T A = Full Package Temperature Range (All Package Types) Junction T emperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+175o CTABLE1.DC ELECTRICAL PERFORMANCE CHARACTERISTICSPARAMETER SYMBOL CONDITIONS(NOTE 1)GROUP ASUBGROUPS TEMPERATURELIMITSUNITSMIN MAXSupply Current IDD VDD = 20V, VIN = VDD or GND1+25o C-10µA2+125o C-1000µAVDD = 18V, VIN = VDD or GND3-55o C-10µA Input Leakage Current IIL VIN = VDD or GND VDD = 201+25o C-100-nA2+125o C-1000-nAVDD = 18V3-55o C-100-nA Input Leakage Current IIH VIN = VDD or GND VDD = 201+25o C-100nA2+125o C-1000nAVDD = 18V3-55o C-100nA Output Voltage VOL15VDD = 15V, No Load1, 2, 3+25o C, +125o C, -55o C-50mV Output Voltage VOH15VDD = 15V, No Load (Note 3)1, 2, 3+25o C, +125o C, -55o C14.95-V Output Current (Sink)IOL5VDD = 5V, VOUT = 0.4V1+25o C0.53-mA Output Current (Sink)IOL10VDD = 10V, VOUT = 0.5V1+25o C 1.4-mA Output Current (Sink)IOL15VDD = 15V, VOUT = 1.5V1+25o C 3.5-mA Output Current (Source)IOH5A VDD = 5V, VOUT = 4.6V1+25o C--0.53mA Output Current (Source)IOH5B VDD = 5V, VOUT = 2.5V1+25o C--1.8mA Output Current (Source)IOH10VDD = 10V, VOUT = 9.5V1+25o C--1.4mA Output Current (Source)IOH15VDD = 15V, VOUT = 13.5V1+25o C--3.5mA N Threshold Voltage VNTH VDD = 10V, ISS = -10µA1+25o C-2.8-0.7V P Threshold Voltage VPTH VSS = 0V, IDD = 10µA1+25o C0.7 2.8VFunctional F VDD = 2.8V, VIN = VDD or GND7+25o C VOH>VDD/2VOL <VDD/2VVDD = 20V, VIN = VDD or GND7+25o CVDD = 18V, VIN = VDD or GND8A+125o CVDD = 3V, VIN = VDD or GND8B-55o CInput Voltage Low(Note 2)VIL VDD = 5V, VOH > 4.5V, VOL < 0.5V1, 2, 3+25o C, +125o C, -55o C- 1.5VInput Voltage High(Note 2)VIH VDD = 5V, VOH > 4.5V, VOL < 0.5V1, 2, 3+25o C, +125o C, -55o C 3.5-VInput Voltage Low (Note 2)VIL VDD = 15V, VOH > 13.5V,VOL < 1.5V1, 2, 3+25o C, +125o C, -55o C-4VInput Voltage High (Note 2)VIH VDD = 15V, VOH > 13.5V,VOL < 1.5V1, 2, 3+25o C, +125o C, -55o C11-VNOTES: 1.All voltages referenced to device GND,100%testing being im-plemented.2.Go/No Go test with limits applied to inputs.3.For accuracy,voltage is measured differentially to VDD.Limit is0.050V max.TABLE2.AC ELECTRICAL PERFORMANCE CHARACTERISTICSPARAMETER SYMBOL CONDITIONS(NOTE 1, 2)GROUP ASUBGROUPS TEMPERATURELIMITSUNITSMIN MAXPropagation Delay Clock to Q Output TPHL1TPLH1VDD = 5V, VIN = VDD or GND9+25o C-400ns10, 11+125o C, -55o C-540nsPropagation Delay Preset or Reset to Q TPHL2TPLH2VDD = 5V, VIN = VDD or GND9+25o C-420ns10, 11+125o C, -55o C-567nsPropagation Delay Clock to Carry Out TPHL3TPLH3VDD = 5V, VIN = VDD or GND9+25o C-480ns10, 11+125o C, -55o C-648nsPropagation Delay Carry In to Carry Out TPHL4TPLH4VDD = 5V, VIN = VDD or GND9+25o C-250ns10, 11+125o C, -55o C-338nsPropagation Delay Preset or Reset to Carry Out TPHL5TPLH5VDD = 5V, VIN = VDD or GND(Note 3)9+25o C-640ns10, 11+125o C, -55o C-864nsTransition Time TTHLTTLH VDD = 5V, VIN = VDD or GND9+25o C-200ns10, 11+125o C, -55o C-270nsMaximum Clock Input Fre-quency FCL VDD = 5V, VIN = VDD or GND9+25o C2-MHz10, 11+125o C, -55o C 1.48-MHzNOTES:1.CL = 50pF, RL = 200K, Input TR, TF < 20ns.2.-55o C and +125o C limits guaranteed, 100% testing being implemented.3.Reset to Carry Out (TPLH) only.TABLE3.ELECTRICAL PERFORMANCE CHARACTERISTICSPARAMETER SYMBOL CONDITIONS NOTES TEMPERATURELIMITSUNITS MIN MAXSupply Current IDD VDD = 5V, VIN = VDD or GND1, 2-55o C, +25o C-5µA+125o C-150µAVDD = 10V, VIN = VDD or GND1, 2-55o C, +25o C-10µA+125o C-300µAVDD = 15V, VIN = VDD or GND1, 2-55o C, +25o C-10µA+125o C-600µA Output Voltage VOL VDD = 5V, No Load1, 2+25o C, +125o C, -55o C-50mVOutput Voltage VOL VDD = 10V, No Load1, 2+25o C, +125o C, -55o C-50mVOutput Voltage VOH VDD = 5V, No Load1, 2+25o C, +125o C, -55o C4.95-VOutput Voltage VOH VDD = 10V, No Load1, 2+25o C, +125o C, -55o C9.95-V Output Current (Sink)IOL5VDD = 5V, VOUT = 0.4V1, 2+125o C0.36-mA-55o C0.64-mA Output Current (Sink)IOL10VDD = 10V, VOUT = 0.5V1, 2+125o C0.9-mA-55o C 1.6-mA Output Current (Sink)IOL15VDD = 15V, VOUT = 1.5V1, 2+125o C 2.4-mA-55o C 4.2-mA Output Current (Source)IOH5A VDD = 5V, VOUT = 4.6V1, 2+125o C--0.36mA-55o C--0.64mAOutput Current (Source)IOH5BVDD = 5V, VOUT = 2.5V1, 2+125o C --1.15mA -55o C--2.0mA Output Current (Source)IOH10VDD = 10V, VOUT = 9.5V1, 2+125o C --0.9mA -55o C--1.6mA Output Current (Source)IOH15VDD =15V, VOUT = 13.5V1, 2+125o C --2.4mA -55o C--4.2mA Input Voltage Low VIL VDD = 10V , VOH > 9V , VOL < 1V 1, 2+25o C, +125o C, -55o C -3V Input Voltage High VIH VDD = 10V , VOH > 9V , VOL < 1V 1, 2+25o C, +125o C, -55o C+7-V Propagation Delay Clock to Q Output TPHL1TPLH1VDD = 10V 1, 2, 3+25o C -200ns VDD = 15V 1, 2, 3+25o C -150ns Propagation Delay Preset or Reset to Q TPHL2TPLH2VDD = 10V 1, 2, 3+25o C -210ns VDD = 15V 1, 2, 3+25o C -160ns Propagation Delay Clock to Carry Out TPHL3TPLH3VDD = 10V 1, 2, 3+25o C -240ns VDD = 15V 1, 2, 3+25o C -180ns Propagation Delay Carry In to Carry Out TPHL4TPLH4VDD = 10V 1, 2, 3+25o C -120ns VDD = 15V 1, 2, 3+25o C -100ns Propagation Delay Preset or Reset to Carry Out TPHL5TPLH5VDD = 10V 1, 2, 3, 4+25o C -320ns VDD = 15V 1, 2, 3, 4+25o C -250ns Transition TimeTTLH TTHL VDD = 10V 1, 2, 3+25o C -100ns VDD = 15V 1, 2, 3+25o C -80ns Maximum Clock Input Fre-quencyFCLVDD = 10V 1, 2+25o C 4-MHz VDD = 15V1, 2+25o C 5.5-MHz Minimum Hold Time Preset Enable to JNTHVDD = 5V 1, 2, 3+25o C -70ns VDD = 10V 1, 2, 3+25o C -40ns VDD = 15V1, 2, 3+25o C -40ns Minimum Data Setup Time Preset Enable to JNTSVDD = 5V 1, 2, 3+25o C -25ns VDD = 10V 1, 2, 3+25o C -10ns VDD = 15V1, 2, 3+25o C -10ns Minimum Data Hold Time Clock to Carry InTHVDD = 5V 1, 2, 3+25o C -60ns VDD = 10V 1, 2, 3+25o C -30ns VDD = 15V1, 2, 3+25o C -30ns Minimum Clock Hold Time Clock to Up/DownTHVDD = 5V 1, 2, 3+25o C -30ns VDD = 10V 1, 2, 3+25o C -30ns VDD = 15V1, 2, 3+25o C -30ns Input Capacitance CINAny Input1, 2+25o C-7.5pFNOTES:1.All voltages referenced to device GND.2.The parameters listed on Table 3are controlled via design or process and are not directly tested.These parameters are characterized on initial design release and upon design changes which would affect these characteristics.3.CL = 50pF, RL = 200K, Input TR, TF < 20ns.4.Reset to Carry Out (TPLH) only.TABLE 3.ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)PARAMETER SYMBOL CONDITIONSNOTES TEMPERATURELIMITSUNITS MIN MAXTABLE4.POST IRRADIATION ELECTRICAL PERFORMANCE CHARACTERISTICSPARAMETER SYMBOL CONDITIONS NOTES TEMPERATURELIMITSUNITS MIN MAXSupply Current IDD VDD = 20V, VIN = VDD or GND1, 4+25o C-25µA N Threshold Voltage VNTH VDD = 10V, ISS = -10µA1, 4+25o C-2.8-0.2V N Threshold VoltageDelta∆VTN VDD = 10V, ISS = -10µA1, 4+25o C-±1V P Threshold Voltage VTP VSS = 0V, IDD = 10µA1, 4+25o C0.2 2.8V P Threshold VoltageDelta∆VTP VSS = 0V, IDD = 10µA1, 4+25o C-±1VFunctional F VDD = 18V, VIN = VDD or GND1+25o C VOH >VDD/2VOL <VDD/2VVDD = 3V, VIN = VDD or GNDPropagation Delay Time TPHLTPLH VDD = 5V1, 2, 3, 4+25o C- 1.35 x+25o CLimitnsNOTES: 1.All voltages referenced to device GND.2.CL = 50pF, RL = 200K, Input TR, TF < 20ns.3.See Table 2 for +25o C limit.4.Read and RecordTABLE5.BURN-IN AND LIFE TEST DELTA PARAMETERS +25o C PARAMETER SYMBOL DELTA LIMIT Supply Current - MSI-2IDD± 1.0µAOutput Current (Sink)IOL5± 20% x Pre-Test Reading Output Current (Source)IOH5A± 20% x Pre-Test ReadingTABLE6.APPLICABLE SUBGROUPSCONFORMANCE GROUP MIL-STD-883METHOD GROUP A SUBGROUPS READ AND RECORDInitial Test (Pre Burn-In)100% 50041, 7, 9IDD, IOL5, IOH5AInterim Test 1 (Post Burn-In)100% 50041, 7, 9IDD, IOL5, IOH5AInterim Test 2 (Post Burn-In)100% 50041, 7, 9IDD, IOL5, IOH5A PDA (Note 1)100% 50041, 7, 9, DeltasInterim Test 3 (Post Burn-In)100% 50041, 7, 9IDD, IOL5, IOH5A PDA (Note 1)100% 50041, 7, 9, DeltasFinal Test100% 50042, 3, 8A, 8B, 10, 11Group A Sample 50051, 2, 3, 7, 8A, 8B, 9, 10, 11Group B Subgroup B-5Sample 50051, 2, 3, 7, 8A, 8B, 9, 10, 11, Deltas Subgroups 1, 2, 3, 9, 10, 11 Subgroup B-6Sample 50051, 7, 9Group D Sample 50051, 2, 3, 8A, 8B, 9Subgroups 1, 2 3NOTE:1. 5% Parameteric, 3% Functional; Cumulative for Static 1 and 2.TABLE7.TOTAL DOSE IRRADIATIONCONFORMANCE GROUPS MIL-STD-883METHODTEST READ AND RECORDPRE-IRRAD POST-IRRAD PRE-IRRAD POST-IRRADGroup E Subgroup 250051, 7, 9Table 41, 9Table 4TABLE 8.BURN-IN AND IRRADIATION TEST CONNECTIONSFUNCTION OPENGROUNDVDD9V ± -0.5VOSCILLATOR50kHz25kHzCD4510BMS Static Burn-In 1(Note 1)2, 6, 7, 11, 141,3-5,8-10,12,13,1516Static Burn-In 2(Note 1)2, 6, 7, 11, 1481,3-5,9,10,12,13,15, 16Dynamic Burn-In (Note 1)-1, 3, 4, 8, 9, 12, 1310, 162, 6, 7, 11, 14155Irradiation (Note 2)2, 6, 7, 11, 1481,3-5,9,10,12,13,15, 16NOTES:1.Each pin except VDD and GND will have a series resistor of 10K ± 5%, VDD = 18V ± 0.5V2.Each pin except VDD and GND will have a series resistor of 47K ±5%; Group E, Subgroup 2, sample size is 4 dice/wafer, 0 failures,VDD = 10V ± 0.5VLogic DiagramsFIGURE 1.CD4510BMSP QQPE C TP1*4Q169RESET *P Q Q PE CTP2*12Q211P Q Q PE C TP3*13Q314P Q Q PE C TP4*3Q42PRESET *ENABLE 115CLOCK *7CARRY OUTU/DQ4Q3Q4U/D Q2U/D Q3U/D U/D Q2Q3U/D Q2Q3Q3Q4Q4Q4Q3Q3Q2Q2Q15CARRY IN *10UP/DOWN *Q1U/D U/DVDDVSS*ALL INPUTS ARE PROTECTEDBY CMOS PROTECTION NETWORKU/DQ4Q2Q2FIGURE 2.CD4516BMSTRUTH TABLECL CI U/D PE R ACTION X1X 00NO COUNT 0100COUNT UP 0000COUNT DOWN X X X 10PRESET XXXX1RESETX = DON’T CARELogic Diagrams (Continued)P QQPE C TP1*4Q169RESET *P Q Q PE CTP2*12Q211P Q Q PE C TP3*13Q314P Q Q PE C TP4*3Q42PRESET *ENABLE 115CLOCK *7CARRY OUTU/D Q3Q4U/D U/DU/D Q2Q3U/D Q2Q3Q4Q4Q3Q3Q2Q2Q15CARRY IN *10UP/DOWN *Q1U/D U/DVDDVSS*ALL INPUTS ARE PROTECTED BY CMOS PROTECTION NETWORKU/D Q2Q2Q2Q3Q4Q2Typical Performance CharacteristicsFIGURE 3.TYPICAL OUTPUT LOW (SINK) CURRENTCHARACTERISTICSFIGURE 4.MINIMUM OUTPUT LOW (SINK) CURRENTCHARACTERISTICSFIGURE 5.TYPICAL OUTPUT HIGH (SOURCE)CURRENTCHARACTERISTICSFIGURE 6.MINIMUM OUTPUT HIGH (SOURCE)CURRENTCHARACTERISTICSFIGURE 7.TYPICAL TRANSITION TIME vs LOADCAPACITANCE FIGURE 8.TYPICAL PROPAGATION DELAY TIME vs LOADCAPACITANCE FOR CLOCK-TO-Q OUTPUTS10V5VAMBIENT TEMPERA TURE (T A ) = +25o CGATE-TO-SOURCE VOL TAGE (VGS) = 15V51015151********DRAIN-TO-SOURCE VOL TAGE (VDS) (V)O U T P U T L O W (S I N K ) C U R R E N T (I O L ) (m A )10V5VAMBIENT TEMPERA TURE (T A ) = +25o CGATE-TO-SOURCE VOL TAGE (VGS) = 15V510157.55.02.510.012.515.0DRAIN-TO-SOURCE VOL TAGE (VDS) (V)O U T P U T L O W (S I N K ) C U R R E N T (I O L ) (m A )-10V-15VAMBIENT TEMPERATURE (T A ) = +25o CGATE-TO-SOURCE VOLT AGE (VGS) = -5V0-5-10-15DRAIN-TO-SOURCE VOL TAGE (VDS) (V)-20-25-30-5-10-15O U T P U T H I G H (S O U R C E ) C U R R E N T (I O H ) (m A )-10V-15VAMBIENT TEMPERATURE (T A ) = +25o C-5-10-15DRAIN-TO-SOURCE VOLT AGE (VDS) (V)-5-10-15O U T P U T H I G H (S O U R C E ) C U R R E N T (I O H ) (m A )GATE-TO-SOURCE VOLT AGE (VGS) = -5VAMBIENT TEMPERATURE (T A ) = +25o CLOAD CAPACITANCE (CL) (pF)40608010020050100150200SUPPL Y VOLT AGE (VDD) = 5V10V15VT R A N S I T I O N T I M E (t T L H ) (n s )25020015010050020406080100LOAD CAPACITANCE (CL) (pF)P R O P A G A T I O N D E L A Y T I M E (t P L H , t P H L ) (n s )AMBIENT TEMPERATURE (T A ) = +25o CSUPPLY VOLTAGE (VDD) = 5V10V15VFIGURE 9.TYPICAL MAXIMUM CLOCK INPUT FREQUENCY vsSUPPLY VOLTAGE FIGURE 10.TYPICAL DYNAMIC POWER DISSIPATION vsFREQUENCYTypical Performance Characteristics(Continued)05SUPPL Y VOL TAGE (VDD)AMBIENT TEMPERA TURE (T A ) = +25o C LOAD CAPACITANCE (CL) = 50pF1015M A X I M U M C L O C K I N P U T F R E Q U E N C Y (f C L M A X ) (M H z )510152010V 5V10V 8642864210410310P O W E R D I S S I P A T I O N P E R G A T E (P D ) (µW )SUPPLY VOLTS (VDD) = 15VAMBIENT TEMPERATURE (T A )tr, tf = 20ns = +25o C 86421028642INPUT FREQUENCY (fCL) (kHz)011864210864210286421038642104CL = 15pFCL = 50pF Test Circuit and WaveformFIGURE 11.POWER DISSIP ATION TEST CIRCUIT AND INPUT WAVEFORM14151691312111012345768CLCLCLCL CL100µFID500µFPULSE GENERATOR50%10%90%20ns VDD20nsVARIABLE WIDTHVSSAcquisition SystemFIGURE 12.TYPICAL 16 CHANNEL, 10 BIT DATA ACQUISITION SYSTEM16 CHANNEL MULTIPLEXERCD4067SELECT INPUTSSAMPLE AND HOLD10 BIT A/DCONVERTERCONVERSIONLOGICQ1Q4CD4516BMSAMPLI-FIERCLOCKPRESET ENABLEENDCLOCKSTART ANALOGDATA INPUTSPARALLEL DATAOUTPUTSPRESET INPUTSNOTE:This acquisition system can be operated in the random access mode by jamming in the channel number at the present inputs, or in the sequential mode by clocking the CD4516BMS.Timing DiagramsFIGURE 13.CD4510BMSFIGURE 14.CD4516BMS12345678987654321967CLOCK CARRY IN UP/DOWN PE P1P2P3P4Q1Q2Q3Q4CARRY OUTCOUNTRESET5678910111213141598765432115CLOCK CARRY IN UP/DOWN PE P1P2P3P4Q1Q2Q3Q4CARRY OUTCOUNTRESETVDD VSS11All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.Intersil semiconductor products are sold by description only.Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time with-out notice.Accordingly,the reader is cautioned to verify that data sheets are current before placing rmation furnished by Intersil is believed to be accurate and reliable.However,no responsibility is assumed by Intersil or its subsidiaries for its use;nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.For information regarding Intersil Corporation and its products,see web site Sales Office HeadquartersNORTH AMERICA Intersil CorporationP. O. Box 883, Mail Stop 53-204Melbourne, FL 32902TEL:(321) 724-7000FAX: (321) 724-7240EUROPE Intersil SAMercure Center100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111FAX: (32) 2.724.22.05ASIAIntersil (Taiwan) Ltd.7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of ChinaTEL: (886) 2 2716 9310FAX: (886) 2 2715 3029FIGURE 15.CASCADING COUNTER PACKAGES*CARRY OUT lines at the 2nd,3rd,etc.,stages may have a negative-going glitch pulse resulting from differential delays of different CD4010/16BMS IC’S.These negative going glitches do not affect proper CD4029BMS operation.However,if the CARRY OUT signals are used to trigger other edge-sensitive logic devices,such as FF’S or counters,the CARRY OUT signals should be gated with the clock signal using a 2-input OR gate such as CD4071BMS.UP/D RPE CL Q1Q2Q3Q4CI CO J1J2J3J4CD4510/16BMS UP/D RPE CL Q1Q2Q3Q4CI CO J1J2J3J4UP/D RPE CL Q1Q2Q3Q4CI CO J1J2J3J4*UP/DOWN PRESET ENABLECLOCK RESETPARALLEL CLOCKINGCD4510/16BMS CD4510/16BMS Ripple Clocking Mode:The up/down control can be changed at any count.The only restriction on changing the up/down control is that the clock input to the first counting stage must be high.For cascading counters operating in a fixed up-count or down-count mode,the OR gates are not required between stages, and CO is connected directly to the CL input of the next stage with CI grounded.UP/D RPE CL Q1Q2Q3Q4CI CO J1J2J3J4UP/D RPE CL Q1Q2Q3Q4CI CO J1J2J3J4UP/D RPE CL Q1Q2Q3Q4CI CO J1J2J3J4UP/DOWN PRESET ENABLECLOCK RESET1/4 CD4071BRIPPLE CLOCKINGCD4510/16BMS CD4510/16BMS CD4510/16BMS CD4510BMS, CD4516BMS。