推荐-基于FPGA出租车计费系统的设计 精品

课程设计——基于FPGA的出租车计价器设计1

××大学××学院××课程设计基于FPGA的出租车计价器设计学生姓名学号所在系专业名称班级指导教师成绩××大学××学院二○一一年六月摘要:本文介绍了一个以Altera公司的CycloneII可编程逻辑芯片EP2C5T144C8为控制核心、运用VHDL硬件描述语言附加一定外围电路组成的出租车计费器系统。

本设计论文主要介绍了出租车计费器系统的组成及工作原理,简述了在EDA平台上用单片FPGA器件构成该数字系统的设计思想和实现过程。

同时,详细论述了人机交互驱动模块、驱动模块、计程模块、计费模块、译码动态扫描模块等的设计方法与技巧。

利用FPGA芯片实现一些功能较复杂的电子产品设计,不仅可以增加系统设计的灵活性,利用它进行产品开发,不仅成本低、周期短、可靠性高,而且具有完全的知识产权。

同时,在进行SOPC设计的时候,我们可以自由调用NIOS资源模块构建软核,从而减小了系统的功耗,实现产品的强大功能。

关键字:FPGA,VHDL,EP2C5T144C8,SOPCAbstract:Th is paper introduces a Altera company to CycloneII programmable logic chips EP2C5T144C8 as control core, useing VHDL hardware description language add a certain peripheral circuit of the message accounting device system of a taxi. This design paper mainly introduced the message accounting device taxi system composition and working principle, this paper expounds on the platform in EDA using single pill FPGA components, the digital system design thought and the implementation process. At the same time, discusses the human-computer interaction driver modules, driving module, taxi module, billing module, decode dynamic scanning module design methods and skills. Use the FPGA chip realize some function is more complex electronic product design, not only can increase the flexibility of the system design, use it for product development, not only the low cost, short cycle, high reliability, and with full intellectual property rights. Meanwhile, during the SOPC design, we can free calls NIOS resource module building soft nuclear, thus reduce power consumption, realizing products of the system of the powerful features.Key words: FPGA,VHDL,EP2C5T144C8,SOPC目录前言1.系统功能软件介绍 (1)1.1 QuartusII软件介绍 (1)1.2 FPGA芯片介绍 (1)1.3 硬件描述语言介绍 (2)2.总体方案设计 (3)2.1 系统框图 (4)2.2 基于MCU的出租车计费器 (4)2.3 基于FPGA的出租车计费器 (5)2.4 总体设计方案 (5)3.单个模块设计 (6)3.1 人机交互驱动模块 (6)3.1.1人机交互模块 (6)3.1.2人机交互模块仿真 (7)3.2 4x4矩阵键盘驱动模块设计 (7)3.2.1 4x4矩阵键盘模块 (8)3.2.2 4x4矩阵键盘仿真图 (7)3.3 二进制BIN转换成BDC(10进制)模块 (9)3.4 FILTER驱动模块设计 (9)3.5 PLS模块驱动设计 (10)3.5.1 PLS模块设计 (10)3.5.2 PLS模块设计仿真图 (11)3.6 出租车控制驱动模块设计 (11)3.7 顶层模块 (12)4.系统功能 ............................ 错误!未定义书签。

基于FPGA的出租车计费器课程设计程序

设计题目:出租车计费器一、设计实验条件QuartusII7.2二、设计目标1.实现计费功能。

按行驶里程计费,起步价为6.00元,并在车行驶3km后按1.2元/km计费,当计费器达到或超过20元时,每千米加收50%的车费,车停止和暂停时不计费;2.现场模拟汽车的起动、停止、暂停和换挡等状态;3.设计数码管动态扫描电路,将车费和路程显示出来,各有两位小数。

三、设计报告的内容1.前言伴随中国经济的腾飞,城市化的进程也随之加快。

虽然人们出行的选择趋于多样化,但是出租车作为一种重要的交通工具,也为很多人作为出行的选择。

大城市里出租车已经相当普及,但是在中小城市出租车依然处于快速发展的阶段。

出租车的计费方式也在发生变化,由只能显示里程的方式变为现在的自主计费和打印发票及语音提示的智能化方式;根据出租车行业的发展需求,国内许多生产厂商也制造出不同类型的计价器,传统的出租车计费器经过十几年的使用,在稳定性,成本等方面都具有一定的优势。

利用FPGA设计出满足出租车不同计费需求的计费器,去满足当地出租车的计费需求。

这个课题在实现计费功能的同时,也解决了传统出租车计费器系统的不足。

出租车的需求不断的增大,因此,出租车计费器的需求也将不断增大,计程车的服务也显得越来越重要,因此出租车计费器也就应运而生了。

2.设计主体(1)设计原理:假设出租车有启动键、停止键、暂停键和档位键。

启动键为脉冲触发信号,当它为一个脉冲是,表示汽车已启动,并根据车速的选择和基本车速发出相应频率的脉冲(计费脉冲)实现车费和路程的计数,同时车费显示起步价;当停止键为高电平时,表示汽车熄火,同时停止发出脉冲,此时车费和路程计数清零;当暂停键为高电平时,表示汽车暂停并停止发出脉冲,此时车费和路程计数暂停;档位键用来改变车速,不同档位对应着不同的车速,同时路程计数的速度也不同。

出租车计费器可分为两大模块,即控制模块和译码显示模块,系统框图如图1所示,控制模块实现了计费和路程的技术,并且通过不同的档位控制车速。

基于FPGA的出租车计费系统设计报告

(封面)XXXXXXX学院题目:基于FPGA的出租车计费系统设计院(系):专业班级:学生姓名:指导老师:时间:年月日目录1.引言 (2)2.实验任务及要求 (2)3.模块功能 (2)4.设计说明 (3)5.实验结果 (4)6.一些问题和改进 (4)7.心得与体会 (4)8.附录··················································摘要介绍了出租车计费器系统的组成及工作原理,简述了在EDA平台上用FPGA器件构成该数字系统的设计思想和实现过程。

论述了分频模块,速度获取模块,计费模块,进制转换模块,显示模块等的设计方法与技巧。

一、引言随着EDA技术的高速发展,电子系统的设计技术发生了深刻的变化,大规模可编程逻辑器件CPLD/FPGA的出现,给设计人员带来了诸多方便。

利用它进行产品开发,不仅成本低、周期短、可靠性高,而且具有完全的知识产权。

本文介绍了一个以Altera公司可编程逻辑芯片cyclone2系列的EP2C35F672C6的fpga芯片为控制核心、附加一定外围电路组成的出租车计费器系统。

随着社会的不断进步,人们生活水平的不断提高,出租车逐渐成为人们日常生活不可缺少的交通工具。

而计价器作为出租车的一个重要组成部分,关系着出租车司机和乘客双方利益,起着重要的作用,因而出租车计价器的发展非常迅猛二、实验任务及要求1.能实现计费功能,计费标准为:按行驶里程收费,起步费为10.00元,并在车行3公里后再按2元/公里,车起启动后停止等待时为每分钟1元(程序中为显示功能,设置为每10秒1元)。

基于FPGA的出租车计价系统设计

2021年 2期第23卷(总第126期)No. 2, 2021General No. 126, Vol.23淮南师范学院学报JOURNAL OF HUAINAN NORMAL UNIVERSITY基于FPGA 的出租车计价系统设计李营,吕兆承,陈帅,余钱坤(淮南师范学院电子工程学院,安徽淮南232038)[摘要]当前出租车计价器精度不高且可扩展性弱,文章根据LCD1602液晶显示屏工作原理及实际出租车计价原理,设计提出了一种新的出租车计价系统。

设计原理主要是采用FPGA 芯片,利用Verilog HDL 最终在LCD1602液晶显示屏端完成出租车计价显示功能。

系统仿真结果表明,该系统计价功能可靠。

[关键词]出租车计价;FPGA ;Verilog HDL ;LCD1602液晶显示[中图分类号]TP311 [文献标识码]A [文章编号]1009-9530(2021)02-0139-041引言出租车是人们日常出行的重要工具,其载客出 行均需计费,市面上常用的计费器大多由单片机控 制实现计费。

单片机虽然价格低廉,但精度差且可扩展性弱。

而FPGA 具有编程灵活性高、功能易拓展等 特点。

故本文采用层次化建模方法,利用Verilog HDL 基于FPGA 设计实现出租车计价器系统并进 行仿真,仿真结果表明该系统功能稳定,计价准确。

2出租车计价器系统设计2.1出租车计费系统技术指标以FPGA 为主体设计出租车计费系统,其计费 标准如表1所示。

表1出租车计费标准根据表中的相关技术指标,系统设计要求如下。

白天 6:00—23:00深夜 23:00—6:00总额汽车行驶 里程计费起步价格8.00元起步价格12.00元1元/km (超过4 km )2元/km (超过4 km )1.5元/km (超过20 km 超价 收费)3元/km (超过20 km 超价收费 )等候时间 费用1元/5 min (车速低于12 km/h 不到1 h) 20元/h (车速低于12 km/h 超过1 h)(1) 设置加减档功能:白天行驶超过4 km ,每公里加1.00元。

(完整word版)基于FPGA技术出租车计费器的设计(EDA技术)

EDA课程设计题目: 基于FPGA的出租车计费器的设计学院:通信与电子工程学院班级:电子101班学号:2010131019姓名: 何经国指导老师:周喜权日期:2013年12月20日摘要本文以Altera公司的DE2开发板为中心,Quartus Ⅱ软件作为开发平台,使用Verilog HDL 语言编程,设计了一个出租车计费的计费器模型。

在程序描述的过程中,用了行为描述方式和结构描述方式二种描述方式对计费器进行描述。

该计费器能动态扫描电路,将车费和路显示出来,各有两位小数.整个自动控制系统由三个主要电路构成:里程和车费计算、译码和动态显示。

最后给出了仿真的波形,并硬件实现。

关键词:出租车计费Verilog HDL Quartus Ⅱ目录摘要 (I)第1章概述 (1)1。

1 设计目的 (1)1。

2 设计背景 (1)1.3 设计意义 (1)第2章工作原理 (3)第3章设计过程 (4)3。

1 设计方案 (4)3。

1.1 计算里程和车费模块 (4)3。

1。

2 七段显示译码器模块 (7)3.1。

3 动态显示模块 (8)3。

1。

4 设计出租车计费器电路 (11)3。

2 硬件实现 (13)3.2。

1 引脚锁定 (13)3.2。

2 编程下载 (15)第4章仿真过程 (16)4.1 建立工程 (16)4。

2 建立Verilog HDL文件 (17)4。

3 建立波形文件 (18)4.4 仿真结果 (19)结论 (22)参考文献 (23)第1章概述1。

1 设计目的通过基于EDA技术出租车计费器的设计,理解可编程逻辑器件的设计原理及工作流程,学习EDA软件Quartus Ⅱ功能与使用方法,了解Verilog HDL语言逻辑编程设计基本过程。

1。

2 设计背景随着我国经济社会的全面发展,各大中小城市的出租车营运事业发展迅速,出租车已经成为人们日常出行选择较为普通的交通工具。

出租车计价器是出租车营运收费的专用智能化仪表,是使出租车市场规范化、标准化的重要设备。

最新-基于CPLD/FPGA的出租车计费器 精品

基于CPLD/FPGA的出租车计费器

摘要介绍了出租车计费器系统的组成及工作原理,简述了在平台上用单片器件构成该数字系统的设计思想和实现过程。

论述了车型调整模块、计程模块、计费模块、译码动态扫描模块等的设计方法与技巧。

关键词/硬件描述语言出租车计费器+软件数字系统

随着技术的高速发展,电子系统的设计技术和工具发生了深刻的变化,大规模可编程逻辑器件/的出现,给设计人员带来了诸多方便。

利用它进行产品开发,不仅成本低、周期短、可靠性高,而且具有完全的知识产权。

本文介绍了一个以公司可编程逻辑芯片712884-15为控制核心、附加一定外围电路组成的出租车计费器系统。

1系统组成

基于/的出租车计费器的组成如图1所示。

各部分主要功能如下1计数器对车轮传感器送来的脉冲信号进行计数每转一圈送一个脉冲。

不同车型的车轮直径可能不一样,通过设置1对车型做出选择,以实现对不同车轮直径的车进行调整。

2计数器对百米脉冲进行累加,并输出实际公里数的码给译码动态扫描模块。

每计满500送出一个脉冲给计数器。

设置2实现起步公里数预制。

3计数器实现步长可变即单价可调的累加计数,每500米计费一次。

设置3用来完成超价加费、起步价预制等。

4译码/动态扫描将路程与费用的数值译码后用动态扫描的方式驱动数码管。

5数码管显示将公里数和计费金额均用四位数码管显示三位整数,1位小数。

2功能模块设计

出租车计费器由车型调整模块、计程模块、计费模块、译码动态及扫描等模块组成,整个系统采用模块化设计,首先用编写功能模块,然后用顶层原理图将。

基于FPGA的出租车计费系统设计

www�ele169�com | 5电子电路设计与方案0 引言FPGA(Field Programmable Gate Array)是在PAL、GAL 等可编程器件的基础上进一步发展的产物。

FPGA 由可编程逻辑功能块、片内互联线、输入输出块构成,通过修改布线实现可编程。

可使用框图或者Verilog HDL 来设计FPGA,Verilog HDL 推出已经有 20 多年,拥有广泛的设计群体,成熟的资源比 VHDL 丰富,因此本次设计采用 Verilog HDL 语言。

而出租车是日常出行中必不可少的交通工具,基于出租车的附属品市场前景也是十分广阔。

本文基于FPGA 设计模拟了一款出租车计费系统,具有开发周期短,设计灵活等优势[1]。

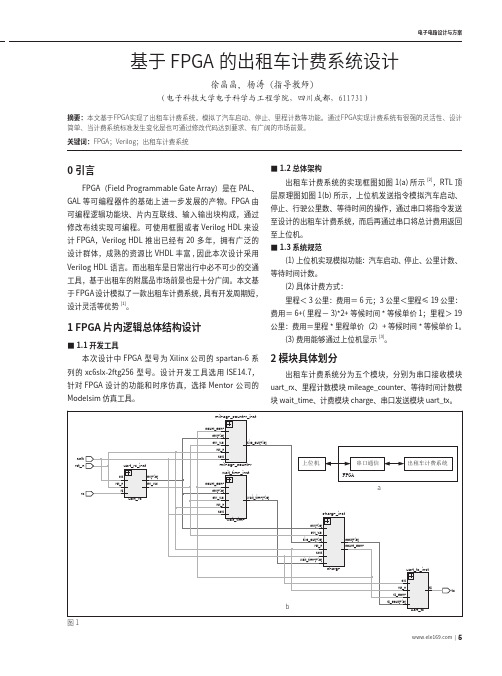

1 FPGA 片内逻辑总体结构设计■1.1 开发工具本次设计中 FPGA 型号为 Xilinx 公司的 spartan-6 系列的 xc6slx-2ftg256 型号。

设计开发工具选用 ISE14.7,针对FPGA 设计的功能和时序仿真,选择 Mentor 公司的■1.2 总体架构出租车计费系统的实现框图如图1(a)所示[2],RTL 顶层原理图如图1(b)所示,上位机发送指令模拟汽车启动、停止、行驶公里数、等待时间的操作,通过串口将指令发送至设计的出租车计费系统,而后再通过串口将总计费用返回至上位机。

■1.3 系统规范(1) 上位机实现模拟功能:汽车启动、停止、公里计数、等待时间计数。

(2) 具体计费方式:里程<3公里:费用=6元;3公里<里程≤19公里:费用=6+(里程-3)*2+等候时间*等候单价1;里程>19公里:费用=里程*里程单价(2)+等候时间*等候单价1。

(3) 费用能够通过上位机显示[3]。

2 模块具体划分出租车计费系统分为五个模块,分别为串口接收模块uart_rx、里程计数模块mileage_counter、等待时间计数模基于FPGA 的出租车计费系统设计徐晶晶,杨涛(指导教师)(电子科技大学电子科学与工程学院,四川成都,611731)摘要:本文基于FPGA实现了出租车计费系统,模拟了汽车启动、停止、里程计数等功能。

基于FPGA的出租车计费器设计论文 精品

基于FPGA的出租车计费系统的设计摘要随着我国市场经济的发展,交通也越来越便利,特别是计程车,以快捷、方便的特点早已盛行各个城市,成为城市交通的重要工具。

计程车市场从90年代初的起步阶段到现在已经进入了高峰期。

随着城市化水平的提高和人民生活水平的改善,计程车的服务也就显得越来越重要。

因此计程车计价器也就应运而生了。

本文分析了当前国内外出租车计费系统的基本组成和工作原理及主要的两种设计方式:基于单片机的设计方式和基于FPGA的设计方式;并对这两种实现方式的优点和缺点进行分析,比较后确定本系统的方案:基于FPGA的出租车计费系统的设计。

在本设计中主要是通过VHDL语言来编程实现计费系统的四个功能块:分频模块,控制模块,计量模块和译码显示模块,最后使用MAX+PLUSII软件来对程序进行仿真,以模拟实现出租车的启动,停止以及等待等过程中的计时,计程和计费功能。

并将各功能模块的结果通过动态译码扫描模块输出到显示模块进行显示。

即通过显示模块显示出租车所行驶的路程,出租车等待的时间和出租车分别在等待过程中的费用和行驶过程中的费用。

关键字:CPLD/FPGA;VHDL语言;MAXPLUS II;出租车;计费器Design of taxi meter Based on FPGAAbstractAs China's market economy develops,more and more convenient transport,particularly taxis, to fast, convenient features have long been popular in various cities and become an important tool for urban traffic. Taxi market in the early 1990s,the initial stage up to now has entered a peak period. With the level of urbanization and the improvement of people's living standards improve, taxi services will become increasingly important. Taxi meter therefore it has emerged.This paper analyses the current domestic and foreign taxi billing system and the basic working principle and the two main design; Based on the design of microcontroller andFPGA-based design; and both the strengths and the ways Shortcomings of the analysis,comparison of the system established after the programme: FPGA-based billing system for taxis.In this design mainly through the VHDL language programming billing systems of the four function blocks:the frequency modules, control module, the measurement modules and decoding modules, the final use of MAX + PLUSII software to simulate the procedures to Simulation of the realization of a taxi start, stop and wait in the course of time, and so on, including-and billing functions。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

南京大学金陵学院本科毕业院系信息科学与工程系专业电子信息科学与技术题目基于FPGA出租车计费系统的设计提交日期20XX年6月3 日摘要通过出租车计费系统的设计,详细介绍了如何使用硬件描述语言Verilog HDL设计复杂逻辑电路的步骤和过程,以及应用美国ALTERA公司的Quartus II 9.0软件进行系统设计、仿真和下载实现的方法。

通过设计,可以看到在EDA平台上用CPLD器件构成该数字系统的设计思想和实现过程。

论述了计费模块、时钟模块、动态显示模块、计费形式判断模块、控制模块等的设计方法和技巧。

关键词:CPLD/FPGA; 电子自动化设计; Verilog HDL硬件描述语言; 出租车计费器; Quartus II 9.0软件ABSTRACTTaxi billing system through the design, details how to use the hardwaredes-cription language Verilog HDL design plexity and the process logic and the applicatio-n of the U.S. pany's Quartus II 9.0 ALTERA software system design, simulation, anddownload the realization of the method. By design, you can see in the EDA platform usi-ng CPLD devices constitute the digital system design and implementation process. Discuss-es the billing module, clock module, dynamic display module, billing forms to judge mod-ule, control module and other design methods and techniques.Keywords: CPLD/FPGA; EDA; Verilog HDL; Taxi Billing Machine; Quartus II 9.0目录第一章引言随着科技日新月异的发展,科技带来的改变无处不在。

尤其是计算机技术带来了人类科技的许多重大的飞跃,特别是集成电路的应用已经渗透到生产和生活中的各个方面,有力的推动了社会的发展。

近几年,中国集成电路产业取得了飞速发展。

中国集成电路产业已经成为全球半导体产业关注的焦点,即使在全球半导体产业陷入有史以来程度最严重的低迷阶段时,中国集成电路市场仍保持了两位数的年增长率,凭借巨大的市场需求、较低的生产成本、丰富的人力资源,以及经济的稳定发展和宽松的政策环境等众多优势条件,以京津唐地区、长江三角洲地区和珠江三角洲地区为代表的产业基地迅速发展壮大,制造业、设计业和封装业等集成电路产业各环节逐步完善。

采用FPGA设计ASIC(Application Specific Integrated Circuit,集成电路界被认为是一种为专门目的而设计的集成电路)电路,用户不需要投片生产,就能得到合用的芯片,FPGA内部有丰富的触发器和I/O引脚,FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一,FPGA采用高速CHMOS 工艺,功耗低,可以与CMOS、TTL电平兼容。

其性能和效率不断提高,应用范围越来越广,在计算机应用领域已占日益重要的地位。

它的应用程度已经成为衡量一个国家科学技术水平的一项重要指标。

出租车计费器就是FPGA的一个可行的应用。

现在市面上的出租车计价器品种繁多,功能强大。

作为一个的课题,我本着从大处着眼,从小处入手的原则,对FPGA的应用做了一些初步的尝试和探讨。

我利用FPGA芯片、32.768KHz晶振、七段LED数码管,初步实现了市面上的出租车计费器的一些基本功能。

第二章Verilog HDL硬件语言简介Verilog HDL和VHDL是目前世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。

前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。

两种HDL均为IEEE标准。

Verilog HDL就是在使用广泛的C语言的基础上发展起来的一种硬件描述语言(HDL:Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

它是GDA(Gateway Design Automation)公司的Phil Moorby在1983年提出,经过不断的完善和发展,直至1995年才成为IEEE标准,即IEEE Standard 1364-1995。

IEEE 20XX 年重新修订了Verilog HDL的IEEE标准。

此前硬件描述语言通过IEEE标准的只有VHDL(1987)。

2.1 Verilog HDL语言的特点1.Verilog HDL最大特点是易学易用。

只要有C语言的编程经验,可以在一个较短的时间内很快的学习和掌握。

2.Verilog HDL设计与工艺无关。

可以使其设计好的模块重复使用,大大方便复杂电子系统的设计,缩短了设计的周期。

3.Verilog HDL简单而优美。

描述硬件单元的结构简单且易读。

相比较而言,VHDL的描述长度是Verilog HDL的两倍。

2.2 Verilog HDL语言的基本结构一个电子系统或电路,通常要对输入的信号进行处理得到输出信号,Verilog HDL就是用语言来描述输入和输出的借口和内部处理功能的实现。

一个设计部论是简单还是复杂,都用Verilog HDL模块来表示。

模块的基本结构如下:module 模块名(端口列表);<端口定义属性,如input,output等><逻辑功能描述>endmodule其中<模块名>是模块唯一的标识符;<端口列表>列出端口名称,<端口定义属性>指明端口是属于输入、输出还是双向端口,这些端口用来与其它模块进行连接。

<逻辑功能描述>是模块设计中最重要的部分,可使用不同形式的过程块来实现。

下面看个简单的例子。

例1.1 上升沿触发D触发器(时序电路)module dff(q,clk,data);input clk,data;output q;reg q;always@(posedge clk)beginq=data;endendmodule从上面的例子可以看出:(1)Verilog HDL程序是由模块构成的,每个模块的内同都是嵌在module和endmodule两个语句之间,每个模块实现特定的功能,模块可以进行层次嵌套;(2)每个模块要进行端口定义,<端口列表>说明输入输出或双向端口,这些端口用与其他模块进行连接;(3)Verilog HDL程序的书写格式自由,一行可以写几个语句,一个语句可以分多行写;(4)除了endmodule语句为,每个语句和数据定义的最后必须有分号;(5)可以用//*……*//或//……对Verilong HDL程序的任何部分作注释;(6)Verilog HDL对大小写敏感,空格很重要,是用来界定各个标志的,关键字都是以小写形式表示。

2.3 CPLD/FPGA的设计流程用HDL语言开发CPLD/FPGA的完整流程为:图1.21.文本编辑:用任何文本编辑器都可以进行,也可以用专用的HDL编辑环境。

2.功能仿真:将文件调入HDL仿真软件进行功能仿真,检查逻辑功能是否正确。

3.逻辑综合:将源文件调入逻辑综合软件进行综合,即把语言综合成最简的布尔表达式和型号的连接关系。

4.布局布线:将.edf文件调入CPLD/FPGA厂家提供的软件中进行布线,即把设计好的逻辑安放到CPLD/FPGA内。

5.时序仿真:需要利用在布局布线中获得的精确参数,用仿真软件验证电路的时序。

6.编程下载:确认仿真无误后,将文件下载到芯片中通常以上过程可以都在CPLD/FPGA厂家提供的开发工具(如QuartusII,ISE 中完成。

下面我们以Altera公司的QuartusII 9.0软件来简单说明一下CPLD/FPGA的开发流程。

下图是一个典型的基于QuartusII的CPLD/FPGA开发流程。

图1.2 基于QuartusII的典型CPLD/FPGA设计流程(1)建立工程是每个开发过程的开始,QuartusII(QII)以工程为单元对设计过程进行管理。

(2)建立顶层图。

可以这样理解,顶层图是一个容器,将整个工程的各个模块包容在里面编译的时候就将这些模块整合在一起。

(3)采用ALTERA公司提供的LPM宏功能模块。

QII软件环境里包含了大量的常用功能模块,例如计数器、累加器、比较强、译码器等等;在充分利用已有模块的基础上,通过,一个设计中一般只有极少部分的模块需要自己从零设计。

(4)自己建立功能模块。

可以用硬件描述语言也可以用原理图的输入方法。

可以把它们独立的当做一个工程来设计,并生产模块符号(Symbol),然后再顶层图中使用这个模块的符号,并将源文件(实现该模块的原理图或HDL文件)拷到顶层图所在的工程目录下。

(5)将顶层图的各个功能模块用两线连起来。

这个过程类似电路图设计,把各个芯片连接起来,组成电路系统。

(6)系统的功能原理图至此已经基本出炉了,下一步要为该设计选择芯片载体,才能真正在物理上实现系统的功能。

这一步的主要工作是:(1)选择芯片型号;(2)为顶层图的各个输入输出信号分配芯片管脚;(3)设置编译选项,目的是让编译器知道更多的信息。

(7)编译。

这个过程类似软件开发里的编译,在类似QII这样的集成环境里面,这些过程都是一气呵成,集成环境自动完成了几个步骤的工作。

(8)编译后生成*.sof或*.pof文件,前者可以通过JTAG下载到CPLD/FPGA内部,设计无误的话技能实现预期的功能,但断电后CPLD/FPGA里的这些信息会丢失;后者可以下载到CPLD/FPGA的配置芯片(EEPROM或FLASH芯片),掉电后这些配置信息不会丢失,重新上电以后通过该配置芯片对CPLD/FPGA的内部RAM进行配置.(9)对于复杂的设计,工程编译了以后可以采用QII的仿真功能或者其他仿真软件(ModelSim)对设计反复进行仿真和验证,知道满足要求。

第三章Quartus II 9.0软件的简介3.1 主要功能Quartus II 9.0 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。