自动售饮料机 Verilog语言

ISE自动售货机、秒表

自动售货机一、电路图及说明a)整体电路图(其中的D触发器有异步复位、置位端,0有效)b)局部模块说明i.输入信号“整形”模块这一模块中,只要输入信号在时钟的某个上升沿为1,则在输入回到0后第2个时钟上升沿,该模块将开始输出一个时长恰为1时钟周期的正脉冲。

实际售货机中,我们难以精确控制硬币传感器发出的脉冲时长,因此可使传感器给出大于1时钟周期的脉冲,并用这一模块整形。

这一模块的等效verilog代码为:module shaping(in,out,clk);input in,clk;output out;reg a,b,out;always @(posedge clk)beginb<=a;a<=in;if((a&&(~b))==1)out<=1;else out<=0;endendmoduleii.状态机模块(售货机本体)利用D触发器作寄存器,配合加法器,直接计算出已投币的量。

(也可以按同步时序状态机的方式来设计,但这会使得电路图可读性差)一旦在某一时钟上升沿输出饮料,则下一时钟上升沿使所有寄存器清零,饮料和找零输出全部停止。

reset键可随时异步清零所有寄存器。

该模块还可带有一小灯随时钟信号闪烁,以指示开机与否,并给出可视的时钟上升沿。

等效verilog代码:(使用状态机写法)module vending(in1,in0_5,drink,change,reset,state,clk_1Hz);input in1,in0_5,reset,clk_1Hz;output drink,change;output[15:0] state;reg drink,change;reg[15:0] state,next_state;parameter //定义状态名称及对应编码s0 =16'b0000_0000_0000_0000, //已投入0元;s0_5 =16'b0000_0000_0000_0101, //已投入0_5元s1 =16'b0000_0000_0001_0000,s1_5 =16'b0000_0000_0001_0101,s2 =16'b0000_0000_0010_0000;//由时钟控制次态always @(posedge clk_1Hz)beginif(reset) state <=s0;else state <=next_state;end//定义状态转换关系always @(state,in1,in0_5)case(state)s0: //若现态为已投入0元begindrink <=0; change <=0;if(in1) next_state <=s1;//若当前输入为投入1元else if(in0_5) next_state <=s0_5;else next_state <=s0;ends0_5:begindrink <=0; change <=0;if(in1) next_state <=s1_5;else if(in0_5) next_state <=s1;else next_state <=s0_5;ends1:begindrink <=0; change <=0;if(in1) begin n ext_state <=s2; endelse if(in0_5) next_state <=s1_5;else next_state <=s1;ends1_5:begindrink <=1; change <=0;if(in1) next_state <=s1;else if(in0_5) next_state <=s0_5;else next_state <=s0;ends2:begindrink <=1; change <=1;if(in1) next_state <=s1;else if(in0_5) next_state <=s0_5;else next_state <=s0;enddefault: next_state <=s0;endcaseassign power_on=clk_1Hz;endmoduleiii.分频模块这次实验中为观察方便,将50MHz时钟分到了1Hz。

自动售饮料机设计和原理

十.自动售饮料机1.实验目的了解自动售货机的工作流程以及各个工作状态,以及其test_bench,最后在Robei可视化仿真软件经行功能实现和仿真验证。

2.实验原理自动售货机的信号定义:clk:时钟输入;reset:为系统复位信号;half_dollar:代表投入5角硬币;one_dollar:代表投入1元硬币;half_out:表示找零信号;dispense:表示机器售出一瓶饮料;collect:该信号用于提示投币者取走饮料。

当reset=0时,售货机处于工作状态,此时连续往售货机中投硬币(可以是5毛也可以是一元),投入最后一枚硬币时,如果之前投入的硬币总和为2.5元则可以取走一瓶饮料,如果少于2.5元则继续投币,如果为3元则显示可以取出一瓶饮料而且找零显示信号为高电平。

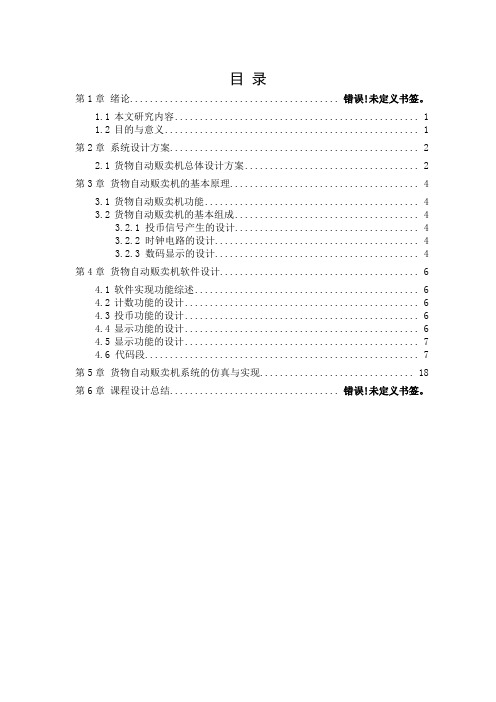

投入硬币的总额自动售饮料机给出的信号<2.5元继续投币=2.5元可以取出一瓶饮料=3元可以取出一瓶饮料,并且找零3.实验内容3.1 sell模块的设计1)新建一个模型命名为sell,类型为module,同时具备4输入3 输出,每个引脚的属性和名称参照下图2-10-1经行对应的修改。

图2-10-1 sell引脚的属性图2-10-2 sell界面图2)添加代码。

点击模型下方的Code添加代码。

代码:parameter idle=0,half=1,one=2,one_half=3,two=4;reg[2:0] D;always @(posedge clk)beginif(reset)begindispense=0; collect=0;half_out=0; D=idle;endcase(D)idle:if(half_dollar)D=half;else if(one_dollar)D=one;half:if(half_dollar)D=one;else if(one_dollar)D=one_half;one:if(half_dollar)D=one_half;else if(one_dollar)D=two;one_half:if(half_dollar)D=two;else if(one_dollar)begindispense=1;collect=1;D=idle;endtwo:if(half_dollar)begindispense=1;collect=1;D=idle;endelse if(one_dollar)begindispense=1;collect=1;half_out=1;D=idle;endendcaseend3)保存模型到一个文件夹(文件夹路径不能有空格和中文)中,运行并检查有无错误输出。

verilog自动售货机课程设计

verilog自动售货机课程设计一、课程目标知识目标:1. 学生理解Verilog硬件描述语言的基本语法和结构;2. 学生掌握利用Verilog设计简单的数字电路,如自动售货机逻辑控制单元;3. 学生了解自动售货机的工作原理及其在数字电路设计中的应用;4. 学生能够识别并描述自动售货机系统的各个模块及其功能。

技能目标:1. 学生能够运用Verilog语言编写自动售货机的基本控制代码;2. 学生通过实际操作,能够模拟自动售货机的运行流程,完成商品选择、支付及出货过程;3. 学生能够利用仿真工具对自动售货机的设计进行验证和调试,解决基本问题。

情感态度价值观目标:1. 学生培养对数字电路设计和Verilog编程的兴趣和热情;2. 学生通过团队协作,培养沟通能力和合作精神;3. 学生在设计过程中,认识到科技对生活的改变,增强创新意识和服务社会的责任感。

课程性质:本课程为电子信息类学科实践课程,结合理论知识,强调学生的动手能力和实际问题解决能力。

学生特点:学生为高中年级,具有一定的电子信息技术基础和编程经验,对新鲜事物充满好奇。

教学要求:注重理论与实践相结合,通过项目驱动的教学方式,引导学生主动探索,提高学生的实践操作能力。

在教学过程中,关注学生的学习反馈,及时调整教学策略,确保课程目标的实现。

将目标分解为具体的学习成果,以便于后续的教学设计和评估。

二、教学内容1. 自动售货机工作原理介绍:分析自动售货机的系统结构,包括投币模块、选择模块、出货模块等,让学生理解各个模块的功能和相互关系。

教材关联章节:第五章 数字电路设计与应用,第3节 自动售货机实例。

2. Verilog基础知识回顾:回顾Verilog的基本语法、数据类型、运算符等,为后续编程打下基础。

教材关联章节:第三章 Verilog语言基础,第1-3节。

3. 自动售货机控制逻辑设计:指导学生利用Verilog编写自动售货机的控制代码,包括投币、选择商品、出货等模块。

自动投币售货机的控制系统设计verilog

工学院二级项目报告二级项目题目:自动投币售货机的控制系统设计指导教师:系别:电子工程系专业:通信工程完成时间:2017年9月目录1. 项目内容与要求 (3)2. 画出投币售货机的控制系统的状态表,状态图,和状态编码方式 (4)3. 用Verilog实现售货机的控制系统描述,并进行仿真 (5)3.1 time.v (5)3.2 state.v (7)3.3 仿真 (10)4. 用C/C++语言实现售货机的有限状态机,并进行测试和仿真 (11)4.1 gcov代码 (11)4.2 仿真 (14)1. 项目内容与要求投币售货机的接收中国的硬币1元和5角,当售货机收到1.5元时出货,无法找零。

(1.5元可以是3个5角,或是1个1元和1个5角)项目以仿真形式完成。

1.画出投币售货机的控制系统的状态表,状态图,和状态编码方式。

2.用Verilog实现售货机的控制系统描述,并进行仿真。

要求仿真测试中给出Code Coverage数据,Code Coverage概念可见PDF 文档。

3.用C/C++语言实现售货机的有限状态机,并进行测试和仿真。

同样要求有测试的Code Coverage数据,具体的工具可用gcc自带的gcov或者是VC的coverage工具4.秋季学期开学前,每个小组需提交一份项目的报告,并作PPT陈述。

2.画出投币售货机的控制系统的状态表,状态图,和状态编码方式3.用Verilog实现售货机的控制系统描述,并进行仿真3.1 time.v`timescale 1ns/1nsmodule times;reg T;reg clk;reg reset;wire A;wire P;state FSM(T,reset,clk,A,P);initial beginreset=0;clk = 0;#80 reset=1;#20 $stop;endalways #10 clk=~clk; initial beginT=1;#20;T=1;#20;T=0;#20;reset=~reset;T=1; #20T=0;#20;endstate uut(.reset(reset),.clk(clk),.T(T),.A(A),.P(P));endmodule3.2 state.vmodule state(T,clk,reset,A,P);input T,clk,reset;output A,P;reg A,P;reg[2:0]y,Y;parameter[2:0] start=2'b000,half=2'b001,one=2'b010,reject=2'b011,paid=2'b100;always @(negedge reset or posedge clk)if(reset==0)y<=start;else y<=Y;//Define the next state always@(T or y) beginY = 3'b000 ;A=0;P=0;case(y)start:beginif(T) Y=one;else if(!T) Y=half;A=1;P=0;endhalf:beginif(T) Y=paid;else if(!T) Y=one;A=1;P=0;endone:beginif(T) Y=reject;else if(!T) Y=paid;A=1;P=0;endreject:beginif(T) Y=reject;else if(!T) Y=paid;A=0;P=0;endpaid:beginif(T) Y=one;else if(!T) Y=half;A=1;P=1;endendcaseendendmodule3.3 仿真4.用C/C++语言实现售货机的有限状态机,并进行测试和仿真4.1 gcov代码-: 0:Source:fsm.c-: 0:Graph:fsm.gcno-: 0:Data:fsm.gcda-: 0:Runs:10-: 0:Programs:1-: 1:#include <stdio.h>-: 2:-: 3:typedef enum //定义状态-: 4:{-: 5: START, //初始-: 6: STATE1, //收入0.5 RMB-: 7: STATE2, //收入1.0 RMB-: 8: REJECT, //找零-: 9: PAID, //出货-: 10:}STATE;-: 11:10: 12:int main()-: 13:{10: 14: int input = 0;10: 15: int input0 = 0; //投入零钱不符合要求时,用于保存原有数据10: 16: int a=1 ;-: 17:10: 18: STATE current_state = START;-: 19:116: 20: while(a<=1)-: 21: {-: 22:96: 23: switch(current_state) //状态转换情况-: 24: {-: 25: case START:-: 26:18: 27: input0 = input;18: 28: printf("accepting\n");18: 29: scanf("%d",&input);-: 30:-: 31:18: 32: if(input == 0)-: 33: {9: 34: current_state = STATE1;9: 35: printf("receive 0.5 RMB\n");-: 36: }9: 37: else if(input == 1)-: 38: {1: 39: current_state = STATE2;1: 40: printf("receive 1.0 RMB\n");-: 41: }-: 42: else-: 43: {8: 44: printf("error,return your money\n");8: 45: input = input0;-: 46: }18: 47: break;-: 48:-: 49: case STATE1:-: 50:23: 51: input0 = input;23: 52: printf("accepting\n");23: 53: scanf("%d",&input);-: 54:23: 55: if(input == 0)-: 56: {#####: 57: current_state = STATE2;#####: 58: printf("receive 1.0 RMB\n");-: 59: }23: 60: else if(input == 1)4.2 仿真输入1元,1元,售货机出货物,且找零输入2元,不符合投币要求,显示错误,退出程序此时代码覆盖率为62.30%,输入不同,代码率也会有所变化所能得到的最高代码覆盖率为95.08%,情况之一如下,输入2 0 1 1 1 1 0 0 2 1 2 最后三行为所生成文件。

基于FPGA自动售货机

摘要本课题是基于Verilog HDL语言的小型自动售货机。

采用Verilog HDL在ModelsimSE6.2B软件平台进行编译和仿真。

在此次设计中,主要采用有限状态机(FSM)的设计,在投币选货状态和找零状态在这两个状态间进行转移。

从而实现货物的选择、货币运算、出货控制、余额显示以及找零等功能。

该售货机系统能够识别两种硬币,两种纸币。

有五种不同价格的商品可供选择,并且通过显示译码电路,可在LED显示器显示余额,同时具备找零、机器存有硬币不足LED 亮起报警、缺货LED亮起报警等功能。

现代的自动售货机有使用方便快捷,可以全天候24小时工作,占地少,成本低,维护简单等优点,有着广阔的前景。

采用FPGA方式用Verilog HDL硬件描述语言,设计简易的自动售货机,其编程简单,开发周期短,硬件运行速度快,开发成本低,稳定性高等优点。

关键词:自动售货机; Verilog HDL;有限状态机;Modelsim;ABSTRACTThis topic design a simple vending machine is based on the FPGA chip. EP2C35 chip, and DE2 development board for the hardware platform, the use of Verilog HDL to compile and simulation in the Quartus Ⅱ software platform, and through the DE2 development achieve the basic functions of a Si mple vending machine.board by to download code to the chip. In this design,it used of finite state machine (FSM) design, choice of goods state, shipment status and give change coin state in the three inter-state transfer, in order to achieve the choice of goods, monetary operations, the cargo control, features such as display and give change. The vending machine system to identify three kinds of coins, there are five kinds of goods at different prices to choose from, and by showing decoding circuit, in DE2 onboard LED display shows the balance, both functions give change. Modern vending machines are convenient, it can work 24 hours a day, covers an area of small, low cost, simple maintenance, there are broad prospects. Manner with the use of FPGA hardware description language Verilog HDL, design simple vending machine, the programming is simple, short development cycles, fast hardware, the development of low cost, high stability.Key words: vending machines; Verilog HDL; Finite state machine; FPGA; DE2 development board;目录绪论..............................................................1 第一章系统方案设计...............................................31.1 人机交换界面设计..........................................31.2 系统方案设计..............................................41.2.1 系统方案确定..........................................5 第二章系统各模块硬件设计.........................................72.1 DE2开发板介绍.............................................72.2 自动售货机各模块设计.....................................82.2.1 自动售货机主体设计...................................82.2.2 LED显示设计方案.....................................92.2.3 货币输入信号设计方案................................102.2.4 出货显示设计方案....................................11 第三章系统的软件设计............................................123.1 EDA工具软件介绍.........................................133.2 软件设计总方案...........................................143.3 售货机主芯片程序设计方案................................153.4 BCD-LED七段数码显示译码器...............................173.5 硬币输入信号程序设计方案................................183.6 出货显示程序设计方案....................................193.7 自动售货机各部分组合连接设计............................20 第四章调试及仿真...............................................214.1 用Quartus Ⅱ完成PFGA设计步骤...........................214.2 自动售货机波形仿真结果..................................214.2.1 自动售货机波形仿真..................................214.2.2 输入信号处理程序波形仿真............................234.2.3 BCD-LED七段数码显示译码器波形仿真..................234.2.4 出货显示译码器波形仿真..............................244.2.5 自动售货机主芯片程序仿真波形.......................254.3 下载、仿真及测试..........................................25 结论..............................................................26 致谢.............................................................27 参考文献..........................................................28 附录1(程序源代码)...............................................29 附录2(整体设计原理图)...........................................35绪论自动售货机最早出现在二十世纪五、六十年代的西欧,英国是较早实行自动售货机售货的国家之一。

基于Verilog的火车自动售票机系统设计

基于Verilog的火车自动售票机系统设计1. 简介火车自动售票机系统是一种方便乘客购买车票并实现自动进出站的设备。

本文档描述了基于Verilog的火车自动售票机系统的设计。

2. 设计概述火车自动售票机系统设计包括以下模块:- 输入模块:接收乘客输入的车票和支付信息。

- 处理模块:处理乘客输入的信息,验证支付信息和票务信息的一致性。

- 控制模块:控制进站和出站的门、屏幕显示、票务信息更新等。

- 存储模块:保存车票和支付信息的数据库。

3. 模块详细说明3.1 输入模块输入模块接收乘客输入的车票和支付信息。

它包括以下功能:- 车票扫描:通过光学扫描实现对车票信息的读取。

- 支付输入:乘客可以通过键盘或触摸屏输入支付信息。

3.2 处理模块处理模块负责验证乘客输入的支付信息和票务信息的一致性。

它包括以下功能:- 支付信息验证:验证支付信息的合法性和是否与车票信息一致。

- 票务信息验证:验证车票的有效性和余票数量。

3.3 控制模块控制模块管理进站和出站的门、屏幕显示和票务信息更新。

它包括以下功能:- 门控制:控制进站和出站的门的打开和关闭。

- 屏幕显示:显示车票信息、支付信息和操作指引。

- 票务信息更新:更新车票的使用状态和余票数量。

3.4 存储模块存储模块保存车票和支付信息的数据库。

它包括以下功能:- 车票信息存储:保存车票相关的信息,如车次、座位号等。

- 支付信息存储:保存支付信息,如支付方式、金额等。

4. 系统功能流程基于Verilog的火车自动售票机系统的功能流程如下:1. 乘客将车票放入输入模块进行扫描。

2. 乘客输入支付信息。

3. 处理模块验证支付信息和票务信息的一致性。

4. 控制模块控制进站门的打开和关闭。

5. 乘客通过进站门进入站台。

6. 屏幕显示乘客的车票信息和操作指引。

7. 控制模块控制出站门的打开和关闭。

8. 乘客通过出站门离开站台。

5. 总结本文档描述了基于Verilog的火车自动售票机系统的设计。

基于FPGA的自动售货机

目录第1章绪论.......................................... 错误!未定义书签。

1.1本文研究内容 (1)1.2目的与意义 (1)第2章系统设计方案 (2)2.1货物自动贩卖机总体设计方案 (2)第3章货物自动贩卖机的基本原理 (4)3.1货物自动贩卖机功能 (4)3.2货物自动贩卖机的基本组成 (4)3.2.1 投币信号产生的设计 (4)3.2.2 时钟电路的设计 (4)3.2.3 数码显示的设计 (4)第4章货物自动贩卖机软件设计 (6)4.1软件实现功能综述 (6)4.2计数功能的设计 (6)4.3投币功能的设计 (6)4.4显示功能的设计 (6)4.5显示功能的设计 (7)4.6 代码段 (7)第5章货物自动贩卖机系统的仿真与实现 (18)第6章课程设计总结.................................. 错误!未定义书签。

第1章绪论1.1本文研究内容本次设计的是一个货物自动贩卖机。

货物自动贩卖机主要是由以下几个部分构成,电源电路、数码显示、时钟脉冲、投币脉冲、闸门时间控制等,各部件形成一个简单的饮料自动提取机系统。

本设计采用EDA技术,通过FPGA实现了数字电子钟电路的设计,并完成对电路的功能进行仿真。

1.2目的与意义本系统用于模拟现实生活中的自动售货贩卖机。

可以模拟四种商品的买卖、存贮、控制等等功能。

并模拟买家模式和管理模式,可以分开进行商品买卖的模拟和商品上架的模拟。

第2章系统设计方案2.1饮料自动提取机总体设计方案自动售货机控制系统设计主要有四个功能模块,一个为货币:该模块能完成硬币处理,余额计算。

一个为分频模块:功能主要是实现各个部分的操作。

一个为售货器模块:该模块主要是负责进行货物的管理。

最后一个是控制模块:主要负责进行商品买卖控制。

图2.1饮料提取机的系统组成框图设计思路:首先,我们对于物品存储进行模拟,共有商品买卖和商品管理两个模式。

verilog代码编写的coffee机

自动售咖啡机1.客户需求<1>只售咖啡<2>三元一杯,接收硬币5角和1元<3>不找零钱<4>售货机中杯子永远用不完2.工作流程图5.代码<1>数据通道module datapath(equal,ld_sum,sel,clr,clk);//数据通道顶层output equal;input ld_sum,clr,clk,sel;wire[1:0] M_A;wire[2:0] A_R,R_C;mux m1(M_A,sel,1,2);//低电平选择1add m2(A_R,M_A,R_C);//r代表2位regs m3(R_C,A_R,clk,clr,ld_sum); compare m4(equal,R_C,6);//后面的常量endmodulemodule mux(out,sel,a,b);//数据选择器output[1:0] out;input sel;input[1:0]a,b;reg [1:0] out;always@(a or b or sel)beginif(!sel) out<=a;else out<=b;endendmodulemodule add(out,r,p);//加法器output [2:0] out;input [1:0] r;input [2:0] p;assign out=p+{0,r};endmodulemodule regs(dout,din,clk,clr,ld);//寄存器output[2:0] dout;input[2:0] din;input clk,clr,ld;reg[2:0] dout;always@(posedge clk )beginif(clr) dout<=0;else if(ld) dout<=din;else dout<=dout;end endmodulemodule compare(equal,a,b);//比较器output equal;input [2:0] a,b;assign equal=(a>=b)? 1:0; endmodule<2>控制单元:modulecontrl(p_cup,i_coffe,ld_sum,sel,clr,reset,clk,c 1,c2,equal,start,p_ready,i_ready);output p_cup,i_coffe,ld_sum,sel,clr;inputclk,c1,c2,p_ready,i_ready,reset,start,equal; reg p_cup,i_coffe,ld_sum,sel,clr;reg[3:0] present_state,next_state; parameterIdle=4'b0000,Wait=4'b0001,Add_a=4'b0010, Add_b=4'b0011,Place_cup=4'b0100,Inject_co ffe=4'b0101,Clear_up=4'b0110;always@(posedge clk or negedge reset) beginif(!reset) present_state<=Idle;else present_state<=next_state;endalways@(present_state or c1 or c2 or p_ready or i_ready or start)begincase(present_state)Idle:beginp_cup<=0;i_coffe=0;ld_sum=0;sel=0;clr=1;if(!start) next_state<=Idle;else next_state<=Wait;endWait:beginp_cup<=0;i_coffe=0;ld_sum=0;sel=0;clr=0;if(c2) next_state<=Add_a;else if(c1) next_state<=Add_b;else next_state<=Wait;endAdd_a:beginp_cup<=0;i_coffe=0;ld_sum=1;sel=0;clr=0;next_state<=Add_b;endAdd_b:beginp_cup<=0;i_coffe=0;ld_sum=1;sel=0;clr=0; if(!equal) next_state<=Wait;else next_state<=Place_cup;endPlace_cup:beginp_cup<=1;i_coffe=0;ld_sum=0;sel=0;clr=0; if(!p_ready) next_state<=Place_cup;else next_state<=Inject_coffe;endInject_coffe:beginp_cup<=0;i_coffe=1;ld_sum=0;sel=0;clr=0; if(!i_ready) next_state<=Inject_coffe;else next_state<=Clear_up;endClear_up:beginp_cup<=0;i_coffe=0;ld_sum=0;sel=0;clr=1; next_state<=Wait;endendcaseendendmodulemodulecoffe(P_cup,I_coffe,Clk,Reset,C1,C2,P_ready, I_ready,Start);//咖啡机顶层output P_cup,I_coffe;input Clk,Reset,C1,C2,P_ready,I_ready,Start; wire ld_sum,sel,clr,equal;contrln1(P_cup,I_coffe,ld_sum,sel,clr,Reset,Clk,C1, C2,equal,Start,P_ready,I_ready);//控制单元datapath n2(equal,ld_sum,sel,clr,Clk);//数据通道顶层endmodule6.综合后的图形:7.仿真图像8.相关问题分析:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

自动售饮料机 Verilog语言

(1)分频模块(实现1s灯变换一次)

module half_clk(

input clk_in,

input rst,

output reg clk_out

);

reg [24:0]count;

always @(posedge clk_in or posedge rst )

if(rst) begin clk_out<=0; count<=0; end

else begin

if(count==24999999) begin clk_out<= ~clk_out; count<=0; end

else count<=count+1;

end

endmodule

(2)实现模块

module toubi(rst,clk,K1,K2,K5,L0,L1,L2,L3,L4) input rst,clk,K1,K2,K5;

output reg L0,L1,L2,L3,L4;

reg [2:0]state;

parameter

s0=3'b000;

s1=3'b001;

s2=3'b010;

s3=3'b011;

s4=3'b100;

always @(posedge clk or posedge rst)

if(rst) begin state<=s0;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end else

case(state)

s0:if(k1==1) begin

state<=s1;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k2==1) begin

state<=s2;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k5==1) begin

state<=s0;L0<=1;L1<=0;L2<=0;L3<=0;L4<=0; end s1:if(k1==1) begin

state<=s2;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k2==1) begin

state<=s4;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k5==1) begin

state<=s0;L0<=1;L1<=1;L2<=0;L3<=0;L4<=0; end s2:if(k1==1) begin

state<=s3;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k2==1) begin

state<=s4;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k5==1) begin

state<=s0;L0<=1;L1<=0;L2<=1;L3<=0;L4<=0; end s3:if(k1==1) begin

state<=s4;L0<=0;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k2==1) begin

state<=s0;L0<=1;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k5==1) begin

state<=s0;L0<=1;L1<=0;L2<=0;L3<=1;L4<=0; end s4:if(k1==1) begin

state<=s0;L0<=1;L1<=0;L2<=0;L3<=0;L4<=0; end

else if(k2==1) begin

state<=s0;L0<=1;L1<=1;L2<=0;L3<=0;L4<=0; end

else if(k5==1) begin

state<=s0;L0<=1;L1<=0;L2<=0;L3<=0;L4<=1; end

endcase

endmodule

(3)top模块

module toubitop(

input rst,clk,K1,K2,K5;

output reg L0,L1,L2,L3,L4;

);

wire clk_out;

half_clk A1(clk,rst,clk_out);

toubi A2(clk_out,rst,K1,K2,K5,L0,L1,L2,L3,L4); endmodule

(4)测试模块

`timescale 1ms / 1ms

////////////////////////////////////////////////////////////////////

////////////

// Company:

// Engineer:

//

// Create Date: 15:02:00 12/10/2013

// Design Name: toubitop

// Module Name: D:/Xilinx/shiyan2/kkk/test.v

// Project Name: kkk // Target Device: // Tool versions: //

Description: //

// Verilog Test Fixture created by ISE for module: toubitop

//

// Dependencies: //

// Revision:

// Revision 0.01 - File Created

// Additional Comments: //

////////////////////////////////////////////////////////////////////

////////////

module test;

// Inputs

reg clk;

reg rst;

reg K1;

reg K2;

reg K5;

// Outputs

wire L0;

wire L1;

wire L2;

wire L3;

wire L4;

// Instantiate the Unit Under Test (UUT)

toubitop uut (

.clk(clk),

.rst(rst),

.K1(K1),

.K2(K2),

.K5(K5),

.L0(L0),

.L1(L1),

.L2(L2),

.L3(L3),

.L4(L4)

);

always #500 clk=~clk;

initial begin

// Initialize Inputs

clk = 0;

rst = 0;

K1 = 0;

K2 = 0;

K5 = 0;

// Wait 100 ns for global reset to finish

#100 rst=1;

#100 rst=0;

#1000 K1=1;

#1000 K1=0;

#1000 K1=1;

#1000 K1=0;

#1000 K2=1;

#1000 K2=0;

#1000 K2=1;

#1000 K2=0;

// Add stimulus here

end

endmodule