45nm工艺库的版图规则

45nm工艺库的版图规则(ppt,课件)

AS=AD =105n×W

重要

90 50

3 50

50

50

55

单位:nm

最小尺寸

W

90

L

50

Poly伸出有源区

50

扩散层伸出poly

105

Poly与有源区间距

50

扩散层与阱边缘间距

55

Contact hole and Via hole (接触孔和通孔)

可获得的Contact hole and Via hole metal1/diff 接触孔 metal1/poly 接触孔 metal1/metal2 通孔 metal2/metal3 通孔

Description Minimum width of poly Minimum spacing of poly AND active Minimum poly extension beyond active Minimum enclosure of active around gate Minimum spacing of field poly to active Minimum Minimum spacing of field poly

Value 70 nm 25 nm 45 nm none

Description Minimum spacing of nimplant/ pimplant to channel Minimum spacing of nimplant/ pimplant to contact Minimum width/ spacing of nimplant/ pimplant Nimplant and pimplant must not overlap

45nm节点的应力工程和版图环境的影响

高性能的芯片上 又得 到了新 的参

F 电路性 能 的影 响是可调整 的 , 对

要 在设计阶段就考虑 由版图引入 的

壬 移率变化 的系统性影响 。

行 版本的紧凑型模型引入 了扩散长度

I型来模拟 S I 莫 T 对沟道区域 的影响。 型基于版 图对被隔离晶体管的紧凑 参 数做 了修改; 例如 , 扩散矩形的长

如果可 以适 众所周知, 机械 应力可 以改变硅材料 的能隙 性能方面扮演 了越来越重要 的角色 。 n 沟道晶体管 和载流子迁移率 , 电应力传感器是这一效应的 当控制应力 ,由于提高了载流子 (一 压

甲阴 电于 , 追 晶 体官 甲明 P J 移 建

应力和迁移宰蜜化 ( %)

50 . 0 E + 强

3箬 . 3 E + 蓦 0

56 + o .E 0 0 0 0 .E o

TF  ̄惺 棚T n E

图 2 对一个库单 元进行机械应 力模拟得到的 . 应力分量 。右下 图所示为在上述应 力场的作 用下迁移率的变化。

- WX .chn + A s iam ag.  ̄V i com

册 极距离附近各个扩散边缘 的距离。 ) 模型并没有考虑像附近扩散这样 D 吏 ,或者更复杂的扩散图案。 应

图 5 ( 0表面处与压应 力时 ,在【1 】 向可 以获得 最大的空穴迁移率 ( F T 。 .1 ) 1 1 1方 nE )

chi nam ag. n cor

. ÷

维普资讯

了引入硅 SGe ̄3 i j I 晶格失配形成 的压 大影响。 单元 中每个 晶体管来说 , h 对 上面标注的 和(1 ) 1 0表面取向中纵向  ̄ pE F T的 SD区域采用 e i 。 / SGe 数字是以不考虑版图效 应时的驱 动电流位基 准 , 拉应力都是最优的。 : ,由于没有应力工程技术可 以获 9 单轴应力 ,技术人 员只 能采用具 e 势应力方 向的应力分布 来近似理 Z 的效果 。然而 ,多种 无意 和有 力 复合之后的结果是三维的应 力分 ! 展示 了对 一个库单元模 拟的三个

解析45NM纳米CPU制作工艺

解析45NM纳米CPU制作工艺CPU的发展史也可以看作是制作工艺的发展史。

如果想要提高CPU的性能,那么更高的频率、更先进的核心以及更优秀的缓存架构都是不可或缺的,而此时自然也需要以制作工艺作为保障。

几乎每一次制作工艺的改进都能为CPU发展带来最强大的源动力,无论是Intel还是AMD,制作工艺都是发展蓝图中的重中之重,如今处理器的制造工艺已经走到了45纳米的新舞台,它将为新一轮CPU高速增长开辟一条康庄大道。

很多用户都对不同的CPU的制作工艺非常熟悉,然而如果问他们什么是制作工艺,65纳米、45纳米代表的是什么,有什么不同,这些问题他们未必能够准确地解答,下面我们就一起来详细了解一下吧。

一、铜导互连的末代疯狂:45纳米制作工艺几乎每一次制作工艺的改进都会给CPU发展带来巨大的源动力。

以如今炙手可热的Pentium4为例,从最初的0.18微米到随后的65纳米,短短四年中我们看到了惊人的巨变。

如今,45纳米制作工艺再一次突破了极限,这也被视为是铜导互连技术的最终畅想曲。

1.制作工艺的重要性早期的微处理器都是使用0.5微米工艺制造出来的,随着CPU频率的增加,原有的工艺已无法满足产品的要求,这样便出现了0.35微米以及0.25微米工艺,不久以后,0.18微米、0.13微米以及90纳米制造的处理器产品也相继面世。

另外一方面,早期芯片内部都是使用铝作为导体,但是由于芯片速度的提高,芯片面积的缩小,铝线已经接近其物理性能极限,所以芯片制造厂商必须找出更好的能够代替铝导线的新的技术,这便是我们常说的铜导技术。

铜导线与铝导线相比,有很大的优势,具体表现在其导电性要优于铝,而且电阻小,所以发热量也要小于现在所使用的铝,从而可以有效地提高芯片的稳定性。

我们今天所要介绍的65纳米技术也是向着这一方向发展。

Intel在IDF 2007上骄傲地展示45nm工艺光刻蚀是目前CPU制造过程当中工艺非常复杂的一个步骤,其过程就是使用一定波长的光在感光层中刻出相应的刻痕,由此改变该处材料的化学特性。

Soc设计课程实验报告

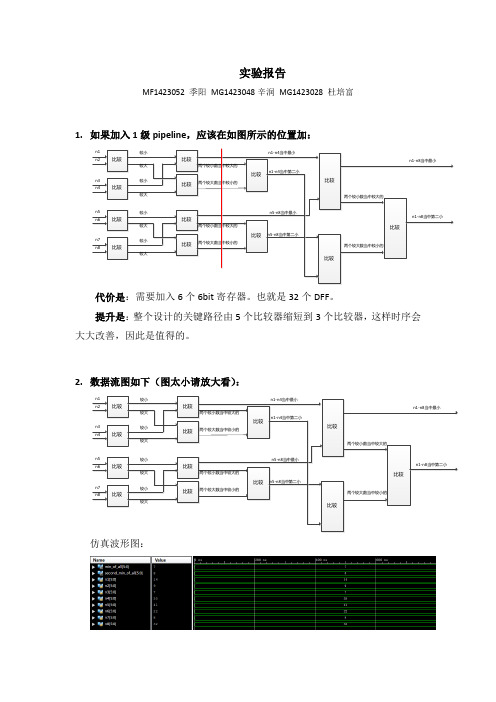

实验报告MF1423052 季阳MG1423048辛润MG1423028 杜培富1.如果加入1级pipeline,应该在如图所示的位置加:代价是:需要加入6个6bit寄存器。

也就是32个DFF。

提升是:整个设计的关键路径由5个比较器缩短到3个比较器,这样时序会大大改善,因此是值得的。

2.数据流图如下(图太小请放大看):仿真波形图:可知,输入是14,9,7,55,41,22,8,32,输出是7和8。

可知功能正确。

综合过后,资源使用率如下:可以看到,用了13个6bit比较器和20个6bit选择器。

综合过后,得到该纯组合逻辑的输入输出延迟为:可以看出,输入输出时延为11.741ns。

3.如果加入2级pipeline,应该在如图所示的位置加:代价是:需要加入10个6bit寄存器,也就是60个DFF。

提升是:整个设计的关键路径由3个比较器缩短到2个比较器,花的比较器多了28个,时序提升相比一级pipeline的设计较少,因此综合考虑起来是不值得的。

4.面积最小的设计:面积最小的设计假设8个数据是串行输入,前两个数比较一下大小,将小的写入Min寄存器,大的写入Max寄存器。

第三个数分别与这两个寄存器里面的数比较,留下较小的两个值。

数据依次进入,最终留在寄存器中的就是8个当中最小的2个数。

仿真波形图:可以看到,输入的输入依次是:33,17,9,5,3,5,9,17,输出是3和5,可知功能正确。

综合过后,资源使用率如下:可以看到,用了1个5bit计数器,24个寄存器,2个6bit比较器,3个6bit 选择器。

跟之前最快的设计相比,虽然这个设计用的比较器少了11个,选择器少了17个,但是多了1个5bit计数器和24个寄存器。

所以到底面积是大了还是小了还需要进一步验证。

因此,将这两个设计在Design Compiler下进行综合,综合工艺库为TSMC 45nm标准单元库。

下面比较其面积。

速度最快的设计面积占用:面积最小的设计面积占用:由结果可知:最快的设计占用面积是399.84,面积最小的设计占用268.128。

45nm铜工艺面临的挑战

45nm铜工艺 面临的挑战作者:Peter Singer, Semiconductor International主编 摘要:本文综述了铜工艺即将面临的各种变化,包括扩散阻障层(barrier)、电镀添加剂、覆盖层以及与多孔超低k电介质之间的整合等。

随着半导体向45nm工艺的深入发展,铜工艺技术不可避免地要发生一些变化。

TaN扩散阻障层物理气相沉积(PVD)技术可能将被原子层沉积(atomic layer deposition,ALD)技术所取代,之后可能还会引进钌阻障层技术。

钌阻障层技术不再需要电镀种子层,但是其发展状况将取决于研究结果的进展程度。

电镀槽中的有机“添加剂”也可能会有所变化,因为有些添加剂最终会被包埋在铜中。

尽管有机添加剂的使用可以使沉积得到的铜填充没有任何缝隙,同时在密集区不会产生沉积过度的情况,因此不会给CMP带来额外负担,从而减小了CMP难度,但是包埋在铜里的杂质会提高电阻系数,并且使铜在退火时不太容易形成大金属颗粒。

铜工艺也有电致迁移这个严重的可靠性问题,它通常发生在铜导线顶部与电介质相接的交界处。

可能的解决办法是在铜表面选择性地沉积上一层钴钨磷化物(cobalt tungsten phosphide,CoWP)或钴钨硼化物(cobalt tungsten boride,CoWB),最终取代Si(C)N覆盖层,使铜原子迁移受到限制。

金属颗粒边界、缺陷和表面造成的电子散射问题也会逐渐突显出来,因为导线尺寸很小时电子散射效应会使电阻升高。

解决办法包括增大金属颗粒、减少缺陷数量和增加金属表面光滑度等。

当然,我们还需要将铜和多孔超低k介电材料整合在一起,该需求会进一步增加铜工艺的复杂度。

其中一个问题是这些多孔材料需要一些孔洞密封工艺,人们对其与沉积在上面的扩散阻障碍层之间的相互作用感到担心,不知道两者之间是否能够相互兼容。

铜工艺基础自1990年代中期IBM、Intel、AMD和其他IC制造商决定用铜制工艺取代铝工艺以来,铜工艺的主要优点基本保持不变。

45纳米

突进中的困惑

45纳米我们天天说45nm制程,但真正明白其含义的朋友恐怕并不多,这里我们首先来明确下这个概念。 45nm(1μm=1000nm,1nm为10亿分之一米)不是指的芯片上每个晶体管的大小,也不是指用于蚀刻芯片形成电路 时采用的激光光源的波长,而是指芯片上晶体管的栅极宽度,衡量半导体制程的参数很多,比如芯片上晶体管和 晶体管之间导线连线的宽度,简称线宽。(此处应为连线的高度,线宽在一个技术时代里(比如45nm工艺)是可 以不断缩小的,而线的高度是不变的)。半导体业界也经常用线宽这个工艺尺寸来代表硅芯片生产工艺的水平。早 期的连线采用铝,后来很多国外的大公司采用铜导线了。

我们知道,一般的晶体管可分为低电阻层、多晶硅栅极和二氧化硅电介层。其中,二氧化硅电介层在65纳米 时代已降低至相当于五层原子的厚度,再进一步缩小则会遭遇电介层的漏电而达到极限。

但是,对业界影响深远的摩尔定律并没有因此而失去效力。经历千万次的试验,英特尔将一种熔沸点和强度 都极高且抗腐蚀性的新型金属铪(Hf)运用到芯片处理技术当中,创造出英特尔45纳米高K金属栅极硅制程技术层, 替换二氧化硅电介层。

英特尔®多路(Wide)动态执行,每时钟周期可传递更多的指令,从而节省执行时间并提高电源使用效率。

英特尔®智能功效管理,旨在为笔记本电脑提供更高的节能效果及更卓越的电池使用效率。

Intel 常见65nm 45nm工艺CPU汇总表

T7500 Merom 2.20GHz 800MHz 4MB 65nm 34W Socket P

T7400 Merom 2.16GHz 667MHz 4MB 65nm 34W Socket M

T7300 Merom 2.00GHz 800MHz 4MB 65nm 34W Socket P

超低电压版酷睿双核

型号 核心 频率 前端总线 二级缓存 制造工艺 功率 主板接口

U2500 Yonah 1.20GHz 533MHz 2MB 65nm 9W Socket M

U2400 Yonah 1.06GHz 533MHz 2MB 65nm 9W Socket M

M410 Yonah 1.46 GHz 533MHz 1MB 65nm 27W Socket M

超低电压版酷睿赛扬M

型号 核心 频率 前端总线 二级缓存 制造工艺 功率 主板接口

M523 Merom 933MHz 533MHz 1MB 65nm 5W Socket P

T7250 Merom 2.00GHz 800MHz 4MB 65nm 34W Socket P

T7250 Merom 2.00GHz 800MHz 2MB 65nm 34W Socket P

T7200 Merom 2.00GHz 667MHz 4MB 65nm 34W Socket M

M530 Merom 1.73 GHz 533MHz 1MB 65nm 31W Socket P

M520 Merom 1.60 GHz 533MHz 1MB 65nm 31W Socket P

M450 Yonah 2.00 GHz 533MHz 1MB 65nm 27W Socket M

版图设计规则

精选课件

14

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

精选课件

15

设计规则举例

精选课件

16

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

• 版图的设计有特定的规则,规则是集成

电路制造厂家根据自已的工艺特点而制定

的。因此,不同的工艺就有不同的设计规

则。设计者只有得到了厂家提供的规则以

后,才能开始设计。

精选课件

7

设计规则(design rule)

两种规则: (a) 以λ(lamda)为单位的设计规则—相对单位 (b) 以μm(micron)为单位的设计规则—绝对单位 如果一种工艺的特征尺寸为S μm,则λ=S/2 μm, 选用λ为单位的设计规则主要与MOS工艺的成比例 缩小有关。

设计规则主要包括各层的最小宽度、层与层之 间的最小间距、最小交叠等。ห้องสมุดไป่ตู้

精选课件

8

设计规则(design rule)

1、最小宽度(minWidth) 最小宽度指封闭几何图形的内边之间的距离

在利用DRC(设计规则检查)对版图进行几何规则检查时,对于宽度低 于规则中指定的最小宽度的几何图形,计算机将给出错误提示。

原始层

poly

diff

精选课件

23

Layer Processing(层处理命令)

•Relational Commands (关系命令)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Metal1

Rule 7.1 7.2 7.3 7.4 Description Minimum width Minimum spacing Minimum overlap of any contact Minimum spacing when either metal line is wider than 10 lambda um 0.065 0.065 0.035/0

Rule POLY.1 POLY.2 POLY.3 POLY.4 POLY.5

Value 50 nm 140 nm 50nm 70 nm 50 nm

Description Minimum width of poly Minimum spacing of poly AND active Minimum poly extension beyond active Minimum enclosure of active around gate Minimum spacing of field poly to active

可获得的Contact hole and Via hole metal1/diff 接触孔 metal1/poly 接触孔 metal1/metal2 通孔 metal2/metal3 通孔

通孔尺寸 Cut(通孔): overlap (复盖) : 65 x 65 5 65 35/90

minimum spacing(间距): diff接触孔与poly间距:

POLY.6

75 nm

Minimum Minimum spacing of field poly

50 50

140

70

50

75

Rule WEL L.1 WEL L.2 WEL L.3 WEL L.4

Valu e none 225 nm 135 nm 200 nm

Description saveDerived: nwell/pwell must not overlap Minimum spacing of nwell/pwell at different potential Minimum spacing of nwell/pwell at the same potential Minimum width of nwell/pwell

0.035

Contact to Active

Rul e 6.1 6.2 6.3 6.4 Description Exact contact size Minimum active overlap Minimum contact spacing Minimum spacing to gate of transistor um 0.065x0.065 0.005 0.075 0.035

Description Minimum width of metal1 Minimum spacing of metal1 Minimum enclosure around contact on two opposite sides Minimum enclosure around via1 on two opposite sides Minimum spacing of metal wider than 90 nm and longer than 900 nm

Rule ACTIVE.1 ACTIVE.2 ACTIVE.3 ACTIVE.4

Value 90 nm 80 nm 55 nm none

Description Minimum width of active Minimum spacing of active Minimum enclosure/spacing of nwell/pwell to active saveDerived: active must be inside nwell or pwell

相同阱

0 or 135

不同阱

0 or 225

gatepolys fieldpolys 140

Poly

50

Well 200

75

80

Active N+,P+ 90

75

Metal1

Poly 35 Metal2 65 M1 or M2 35 35 65

65

con/via1

70

Implant可与well同样大小

um 0.070 0.070 0.035/0

Lambda

3 2 1.5 4

Metal2

Rule 9.1 9.2 9.3 9.4

Description Minimum width Minimum spacing Minimum overlap of via1 Minimum spacing when either metal line is wider than 10 lambda

Rule CONTACT.1 CONTACT.2 CONTACT.3 CONTACT.4 CONTACT.5

Value 65 nm 75 nm none 5 nm 5 nm

Description Minimum width of contact Minimum spacing of contact saveDerived: contact must be inside active or poly or metal1 Minimum enclosure of active around contact Minimum enclosure of poly around contact

M1

M3

设计规则

• lamda规则

– 最小尺寸以lamda的倍数来规定

• 微米规则

– 直接用具体的微米、纳米等单位来规定

• Grid

– 由具体工艺规定 – 分辨率 – 0.18mm工艺为45nm,45nm工艺为2.5nm – 版图中所绘制的矩形、互连线等尺寸必须是它 的倍数

1)Intra-Layer Design Rules 层内设计规则 单位:nm

Rule METALINT.1

Value 70 nm

Description Minimum width of intermediat e metal Minimum spacing of intermedi ate metal Minimum enclosure around via 1 on two opposite sides Minimum enclosure around via [2-3] on two opposite sides Minimum spacing of metal wider than 90 nm and longer than 900 nm Minimum spacing of metal wider than 270 nm and longer than 300 nm Minimum spacing of metal wider than 500 nm and longer than 1.8um Minimum spacing of metal wider than 900 nm and longer than 2.7 um

Select

Rule

4.1 4.2 4.3 4.4

Description

Minimum select spacing to channel of transistor to ensure adequate source/drain width Minimum select overlap of active Minimum select overlap of contact Minimum select width and spacing (Note: P-select and N-select may be coincident, but must not overlap) (not illustrated)

NCSU PDK45Байду номын сангаасm 版图规则

工艺流程

• 与版图的对应关系 • 了解一定的工艺流程背景知识有助于画好 版图

gate-oxide TiSi2 AlCu SiO2 Tungsten

poly

p-well n-well

SiO2 p+

n+

p-epi p+

VDD M2

VDD

M4 Vin Vout Vout2

METALINT.2

70 nm

METALINT.3

35 nm

METALINT.4

35 nm

METALINT.5

90 nm

METALINT.6

270 nm

METALINT.7

500 nm

METALINT.8

900 nm

METALINT.9

1500 nm

Minimum spacing of metal wider than 1500 nm and longer than 4.0 um

70

重要

最小宽度 Poly 50 metal1 65 有源区(扩散区,N+,P+) 90 Contact or Via Hole 65

最小间距 75/140 65 80 65

2)Inter-Layer Design Rules 层间设计规则

Transistors

单位: nm

50 70 50 65 90 5

METAL1.6

METAL1.7 METAL1.8 METAL1.9

270 nm

500 nm 900 nm 1500 nm

Minimum spacing of metal wider than 270 nm and longer than 300 nm

Minimum spacing of metal wider than 500 nm and longer than 1.8um Minimum spacing of metal wider than 900 nm and longer than 2.7 um Minimum spacing of metal wider than 1500 nm and longer than 4.0 um