基于130nm工艺的Uart IP数字后端设计

ADuM1300

二、产品特性

� � � � � � � � � 多方向三通道隔离 电平转换功能 工作电压:3V/5V 隔离电压:2500V 工作温度:125℃ 传输速率:1M/10M/90Mbps 传输延迟:32ns. 瞬态共模抑制能力:25KV/us SOIC-16 宽体无铅封装

第1页/共 7 页

�

低功耗: 5 V operation 1.2 mA /通道 @ 0 Mbps to 2 Mbps 3.5 mA /通道 @ 10 Mbps 32 mA /通道 @ 90 Mbps 3 V operation 0.8 mA /通道 @ 0 Mbps to 2 Mbps /通道 @ 10 Mbps 2.2 mA mA/ 20 mA /通道 @ 90 Mbps

10

VE2

六、应用说明

1、ADuM130x 真值表

VIx 输入 高电平 低电平 X X X X VEx 输入 高或悬空 高或悬空 低电平 高或悬空 低电平 X VDD1 状态 有效 有效 有效 无效 无效 有效 VDD2 状态 有效 有效 有效 有效 有效 无效 VOx 输出 高电平 低电平 高阻状态 高电平 高阻状态 不确定

声 明

本中文资料是根据 ADI 官方提供的英文数据手册相关内容翻译和直接引用而得。仅用于帮助工程师更 快更好的了解该芯片基本功能,译文中可能存在文字组织或翻译错误,不对文档中存在的翻译差异及由此 产生的错误负责。最终解释权归北京晶圆智通科技有限公司所有,未经本公司授权,任何单位及个人不得 非法修改、拷贝和盈利。本公司拥有对此资料所有权及修改权且无需提前通知客户的权利。如需涉及更准 确性的资料,请参考原始英文版本资料。 /static/imported-files/data_sheets/ADuM1300_1301.pdf 版本信息 题目:三通道数字隔离器——ADuM130x 来源:北京晶圆智通科技有限公司 更新时间:2009-11 V1.3

数字电路后端设计中的一些概念

天线效应:小尺寸的MO S 管的栅极与很长的金属连线接在一起,在刻蚀过程中 ,这根金属线有可能象一根天线一样收集带电粒子 ,升高电位,而且可以击穿 MO S 管的栅氧化层,造成器件的失效。

这种失效是不可恢复的。

不仅是金属连线 ,有时候多晶硅也可以充当天线。

Antenna Ratio(N 冷 G J 二铲包J A rea丫A rea(G K ) MO S 管的输入端开始算起,直至到达该回路最顶层金属线之下的所有金属互连线 (N i ,j ,i 为互连节点所属的金属层号,j 为金属层上的互连节点编号)的面积总和。

在这些金属互连线上将会累积电荷并导致输入端MO S 管栅氧化层出现可能被击穿的潜在危险。

而顶层金属线之下连至输出端晶体管栅极的金属线并不会被计算在内,这是因为在芯片的制造过程中其上多余的游离电荷可以通过低阻的输出端 MO S 管顺畅泻放。

同理,顶层金属线也不会对 A R 的值做出任何贡献,因其最后被刻蚀完成的同时,就标志着从输入 MO S 管到 输出MO S 管的通路正式形成,多余的电荷此时全部可以通过输出端得到泻放。

栅氧化层面积 A re a ga t e则是指各个输入端口所连接到的不同晶体管 (GK )的栅氧化层的面积总和。

以图1所 A 口聞门缸R 日込严铲Z Totallnpu tPorL-X 怕日* 工[inpuu+A 上 匕厲口 12 # inpct (2 )EM (电迁移):电迁移是指金属材料中存在大电流的情况下,金属离子在电流作用下出现宏观移动的现象,日常生活中的家用电线等金属导线由于没有良好 这里的导体面积 A r e a m e t a l 是指从图 1 M eta!3 l\ 实Pli A ri te nn a 的计门的散热能力,稍大的电流强度就会导致保险丝熔断而断路,移现象。

集成电路芯片中的金属连线则不同:它们有良好的散热环境,通常能够承受高达105A/cm2(约为普通家用电线承受极限的100倍)以上的电流强度和由此导致的大约100°C的高温。

基于FPGA的UART设计综述

四川师范大学本科毕业设计基于FPGA的UART设计学生姓名院系名称专业名称班级学号指导教师完成时间基于FPGA的UART设计电子信息工程专业摘要:UART(通用异步收发器)是一种应用广泛,协议简单,易于调试的串行传输接口。

FPGA是能高密度,低消耗完成所需要的逻辑功能的一种在线可编程器件,是现在业内提高系统集成度最佳技术之一,其可反复配置,且使用灵活。

VHDL 是描述电路功能或行为的一种硬件语言。

本文首先阐述了运用FPGA实现UART接口的意义。

接着介绍了UART的波特率发生器,发送功能和接收三大核心功能的理论知识。

FPGA的工作原理,配置模式以及VHDL语言实现状态机的相关理论基础。

给出了运用VHDL语言将UART三大功能嵌入在FPGA上的模块化设计方法。

设计包括四大模块:顶层模块,波特率发生器,UART接收器,UART发生器。

在FPGA片上集成UART主要功能,减少了电路板体积,同时电路也增加了可移植和反复配置功能,有效提高了电路的集成度和灵活性。

最后运用Quartus ii 9.1实现了其功能仿真。

关键词:FPGA UART VHDL 有限状态机The Design of Universal Asynchronous Receiver Transmitter Based on FPGAAbstract:UART (Universal Asynchronous Receiver Transmitter) is a widely used, simple protocol, easy to debug serial transmission interface. FPGA is capable of high-density, low-cost needed to complete a line of programmable logic devices, is now one of the industry's best technologies to improve system integration, which can be repeated to configure and use and flexible. VHDL description of the circuit function or behavior is a hardware language. This paper first describes the use of FPGA to realize the significance of the UART interface. Then introduced the theory of knowledge UART baud rate generator, sending and receiving three core functions. FPGA works, configuration mode and the VHDL-based state machine theory. Gives the UART using VHDL language to three functions embedded in the FPGA design. Design includes four modules: the top-level module, baud rate generator, UART receivers, UART generator. Integrated on-chip UART FPGA basic functions, reducing board space, the circuit also increases the portability and repeated configuration capabilities, improve the integration and flexibility of the circuit. Finally, the use of Quartus ii 9.1 implements its functional simulation.Key Words:FPGA ;UART ;VHDL;FSM目录摘要: (I)Abstract: (II)1 绪论 (1)1.1 课题背景 (1)1.2 课题研究现状 (2)1.3 课题研究内容与主要工作 (3)1.4 课题内容结构 (3)2 UART理论基础 (4)2.1 接口技术简介 (4)2.2 UART基本结构 (4)2.3 UART数据帧格式 (5)2.4 涉及到的理论计算 (6)3 设计工具 (7)3.1 课题硬件平台——FPGA (7)3.2 设计工具QuartusII简介与使用 (7)3.3 VHDL语言简介 (7)4 UART实现方案 (8)4.1 系统总体结构 (8)4.2 顶层模块设计 (8)4.3 波特率发生模块设计 (9)4.4 接收模块 (10)4.5 发送模块设计 (12)5 UART设计的仿真与验证 (15)5.1波特率发生模块仿真 (15)5.2 接收模块仿真 (15)5.3 发送模块仿真 (16)6 总结 (17)参考文献 (18)致谢 (19)附录 (20)基于FPGA的UART设计1 绪论在计算机的数据通信中,外设一般不能与计算机直接相连,它们之间的信息交换主要存在以下问题:(1)速度不匹配。

BF6910(BF6911)ASXX规格书

3.1 引脚图 ....................................................................................................................................................... 6 3.2 引脚描述 ................................................................................................................................................... 6

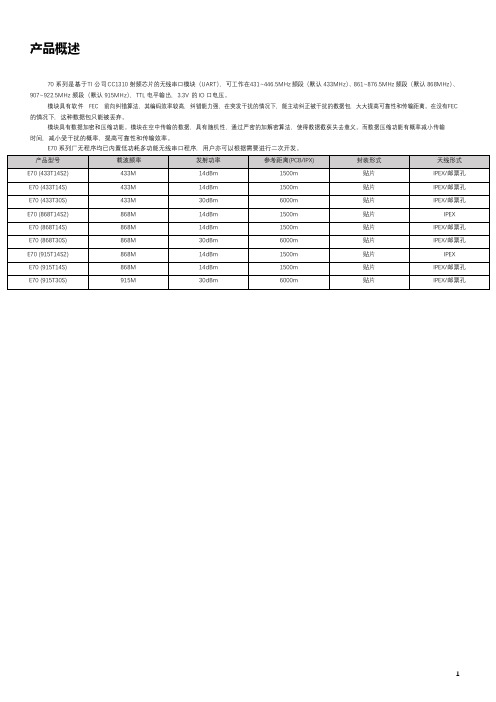

E70是基于CC1310射频芯片的无线串口模块(UART)-透明传输方式

产品概述70系列是基于TI公司CC1310射频芯片的无线串口模块(UART),可工作在431~446.5MHz频段(默认433MHz)、861~876.5MHz频段(默认868MHz)、907~922.5MHz频段(默认915MHz),TTL电平输出,3.3V的IO口电压。

模块具有软件FEC前向纠错算法,其编码效率较高,纠错能力强,在突发干扰的情况下,能主动纠正被干扰的数据包,大大提高可靠性和传输距离。

在没有FEC 的情况下,这种数据包只能被丢弃。

模块具有数据加密和压缩功能。

模块在空中传输的数据,具有随机性,通过严密的加解密算法,使得数据截获失去意义。

而数据压缩功能有概率减小传输时间,减小受干扰的概率,提高可靠性和传输效率。

E70系列厂无程序均已内置低功耗多功能无线串口程序,用户亦可以根据需要进行二次开发。

1.产品特点●【超低功耗】:接收电流仅为8mA,休眠电流仅为2uA。

可以使用电池供电,功耗优势明显。

●【定点发射】:支持地址功能,主机可发射数据到任意地址、任意信道的模块,达到组网、中继等应用方式:例如:模块A需要向模块B(地址为0x0001,信道为0x80)发射数据AA BB CC,其通信格式为:000180AA BB CC,其中0001为模块B地址,80为模块B信道,则模块B可以收到AA BB CC (其它模块不接收数据)。

详见指令传输模式。

●【广播监听】:将模块地址设置为0xFFFF或者0x0000;可以监听相同信道上的所有模块的数据传输;发送的数据,可以被相同信道上任意地址的模块收到,从而起到广播和监听的作用。

●【前向纠错】:模块具有软件FEC前向纠错算法:其编码效率较高,纠错能力强,在突发干扰的情况下,能主动纠正被干扰的数据包,大大提高可靠性和传输距离;在没有FEC的情况下,这种数据包只能被丢弃。

●【参数保存】:用户设置好参数以后,模块参数将会保存,断电不丢失,重新上电后模块会按照设置好的参数进行工作。

SoC设计方法与实现 第12章 后端设计 课件PPT

信号完整性

信号完整性随着深亚微米制程在不断进步而成为SoC 设计首要考虑的问题之一

互连线上的耦合电容、电阻增大 电流密度更高、电压更低

信号完整性是指一个信号能对电路产生正确的响应

信号具有特定电压下所要求水平

信号完整性问题主要表现为串扰、压降和电迁移

串扰

串扰:Crosstalk 信号线之间存在耦合电容

存在于同一层间及不同层间

信号线与衬底之间存在耦合电容 串扰

延迟:两条信号线同时翻转会导致信号比预先的变快或变慢 噪声:一条信号线的翻转会给相邻的线路中注入电压针刺型干扰

串扰引起的延迟和噪声主导信号完整性

对电路的时序和功能有极为重要的影响

压降

压降:IR drop 电源网络上瞬间的电流的抽取造成基本单元上的电压下降

短路或开路

信号完整性的检查和修正

芯片制造厂与EDA公司合作开发检查规则

对串扰的消除的方法

定义高速信号、模拟信号 通常是增加两条金属线的距离(Spacing) 加隔离线(Shielding) 综合阶段,减少非关键路径上的驱动尺寸

对于压降和电迁移消除的方法

对版图进行动态功耗、静态功耗分析 修改版图的布局,改进电源及高速信号线宽度

时钟树综合流程

使用EDA工具自动生成时钟树

缓冲器的插入

根据寄存器的位置和数量,决定插入缓冲器的 层数、驱动力的大小和位置

时钟线的布线

时钟线的优先级高于一般信号线,所以先布时钟线

From placement Set clock constraints

Perform clock tree synthesis

通过在布局密度较低的区域插入一些冗余金属块, 使其表面平坦,提高芯片良率。

基于DSP+FPGA的UART设计与实现

基于DSP+FPGA的UART设计与实现摘要:UART作为RS232协议的控制接口得到广泛的应用,将UART功能集成在DSP和FPGA芯片组成的系统中,可使整个系统更为灵活、紧凑,减小电路体积,提高系统的可靠性和稳定性。

本文提出了一种基于DSP和FPGA 系统的UART 实现方法。

关键词:通用异步收发器;DSP;FPGA1 引言通用异步收发器(Universal Asynchronous Receiver/Transmitter,通常称作UART)是一种串行异步收发协议,应用十分广泛。

UART可以和各种标准串行接口,如RS232、RS485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。

一般UART 由专用芯片来实现,但专用芯片引脚较多,内含许多辅助功能,在实际使用时往往只需要用到UART 的基本功能,使用专用芯片会造成资源浪费和成本提高[1]。

在DSP和FPGA组成的系统中,利用DSP芯片完成UART数据收发控制,FPGA完成UART数据具体的收发时序,二者利用EMIF接口配合,即可实现UART通信功能。

这样设计可以大大减少电路体积、简化电路,也提高了系统的灵活性,使整个系统更加紧凑、稳定且可靠。

2 UART原理UART是一种串行数据总线,用于全双工异步通信。

工作原理是将数据的二进制位按位进行传输。

基本的UART 只需要两条信号线(收、发)和一条地线就可以完成数据的互通,接收和发送互不干扰。

在UART通信协议中,信号线上的状态位高电平代表“1”,低电平代表“0”。

图1 UART数据传输格式UART 数据传输格式如图1所示,一个字符由起始位、数据位、校验位和停止位组成(其中校验位可选)。

其中各位的含义如下:起始位:一位逻辑“0”信号,表示字符数据传输的开始;数据位:5~8位可选的逻辑“0”或“1”。

数据位的发送顺序为:先发送数据的最低位,最后发送最高位;校验位:包括奇校验或偶校验两种方式,即数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验)。

UART串口通信设计实例

UART串口通信设计实例UART(Universal Asynchronous Receiver/Transmitter)是一种串口通信的协议,通过UART可以实现两个设备之间的数据传输。

在本文中,我们将设计一个基于UART的串口通信系统,并用一个实例来说明如何使用UART进行数据传输。

串口通信系统设计实例:假设我们有两个设备:设备A和设备B,它们之间需要通过串口进行数据传输。

设备A是一个传感器,负责采集环境温度信息;设备B是一个显示屏,负责显示温度信息。

首先,我们需要确定使用的UART参数,包括波特率、数据位数、校验位和停止位等。

假设我们选择的参数为9600波特率、8位数据位、无校验位和1个停止位。

接下来,我们需要确定数据的格式。

在本例中,我们选择使用ASCII码来表示温度值。

ASCII码是一种常用的字符编码方式,将字符与数字之间建立了一一对应的关系。

假设我们将温度的数据范围设置为-10到50,那么ASCII码表示为0x30到0x39和0x2d(负号)。

现在,我们可以开始设计串口通信系统的流程了:1.设备A采集环境温度信息,并将温度值转换成ASCII码格式。

2.设备A将ASCII码格式的温度值按照UART协议发送给设备B。

3.设备B接收UART数据,并将ASCII码格式的温度值转换成温度值。

4.设备B将温度值显示在屏幕上。

接下来,我们将详细介绍每个步骤的实现细节:1.设备A采集环境温度信息,并将温度值转换成ASCII码格式。

设备A可以使用温度传感器读取环境温度,并将读取的温度值转换成ASCII码。

例如,如果读取到的温度值为25,ASCII码格式为0x32和0x352.设备A将ASCII码格式的温度值按照UART协议发送给设备B。

设备A可以通过UART发送函数将ASCII码格式的数据发送给设备B。

发送函数会将数据按照UART协议的要求进行传输,包括起始位、数据位、校验位和停止位等。

3.设备B接收UART数据,并将ASCII码格式的温度值转换成温度值。

SkyWater PDK 130nm SCMOS开源芯片设计说明书

Tim Edwards Open Circuit DesignefablessThe New Age of Open Source SiliconSVP Analog & Platform October 8, 2021Introduction to the SkyWater PDK130nm SCMOS130nm SCMOS https:///google/skywater-pdkThe "Caravel" harness chipThe "Caravel" harness chipRISC-VprocessorThe "Caravel"harness chipRISC-V processor user project areaYour project here!https:///open_mpw_shuttle_project_mpw_oneYour project here!PDK = "Process Design Kit"SKY130SKY130130nmSKY130130nm minimum-length transistor*transistorlength =130nm"feature size"*caveat: for obscure reasons, the minimum size devicein the SKY130 process is actually 150nm. . .Bloomington MinnesotaPublic repository DocumentationPDK Library and filesPublic repository DocumentationPDK Library and filesCommunityPublic repository Documentationhttps://.readthedocs.build PDK Library and filesCommunityPublic repositoryDocumentationhttps://.readthedocs.build PDK Library and fileshttps:///google/skywater-pdkCommunityPublic repositoryDocumentationhttps://.readthedocs.build PDK Library and fileshttps:///google/skywater-pdkCommunityslackhttps://join.skywater.toolsopen_pdks/open_pdkshttps:///RTimothyEdwards/open_pdkshttps:///RTimothyEdwards/open_pdksopen_pdks/open_pdksmagicopenlane ...xschemngspice Open-source PDK repositoryopen_pdks Makefileopen_pdks Steps to installing the SKY130 PDK1. Clone the repository"git clone https:///RTimothyEdwards/open_pdks"2. Run "cd open_pdks"3. Run "configure --enable-sky130-pdk"4. Run "make"5. Run "sudo make install"Tools Currently Supported by Open_PDKs Magic /magicTools Currently Supported by Open_PDKs Klayouthttps://www.klayout.deTools Currently Supported by Open_PDKsOpenlanehttps:///The-OpenROAD-Project/OpenLaneTools Currently Supported by Open_PDKs Xschem https:///StefanSchippers/xschemTools Currently Supported by Open_PDKs Netgen /netgenTools Currently Supported by Open_PDKs Ngspice https://Tools Currently Supported by Open_PDKsiveriloghttps://qflow/qflowIRSIM/irsimxcircuit/xcircuitxycehttps://fun fact: These slides were drawn with xcircuit!SkyWater SKY130 Libraries1. Digital standard cellssky130_fd_sc_hd sky130_fd_sc_hdllsky130_fd_sc_hs sky130_fd_sc_ms sky130_fd_sc_ls sky130_fd_sc_lp sky130_fd_sc_hvl2. Primitive devices / analogsky130_fd_pr3. I/O cellssky130_fd_io4. 3rd-party librariessky130_ml_xx_hdsky130_sram_macrosPDK (e.g., SKY130) Installed Filesystem Structure/usr/share/pdk/sky130A/SkyWater SKY130 Installed Filesystem Structure/usr/share/pdk/sky130A/libs.tech/libs.ref/SkyWater SKY130 Installed Filesystem Structure/usr/share/pdk/sky130A/libs.ref/libs.tech/xschem/openlane/magic/SkyWater SKY130 Installed Filesystem Structure/usr/share/pdk/sky130A/libs.ref/libs.tech/xschem/openlane/magic/sky130_fd_sc_hd/sky130_fd_pr/sky130_fd_io/SkyWater SKY130 Installed Filesystem Structure/usr/share/pdk/sky130A/libs.ref/libs.tech/xschem/openlane/magic/sky130_fd_sc_hd/sky130_fd_pr/sky130_fd_io/spice/mag/lib/lef/verilog/gds/ngspice/Open PDKs Project Filesystem Structureproject_root/ e.g., "my_sky130_project"Open PDKs Project Filesystem Structuree.g., "my_sky130_project "verilog/openlane/mag/spice/xschem/project_root /Open-Source EDA Toolse.g., "my_sky130_project "project_root /mag/xschem/xschemrc .magicrc /usr/share/pdk/sky130A/Open PDKs Project Filesystem Structurelibs.tech/magic/xschem/sky130A.magicrc xschemrcOpen-Source EDA ToolsOpen PDKs Project Filesystem StructureProject Management/usr/share/pdk/scripts/project_manager.py(work in progress)Layers SKY130Layers5 layers of aluminum metalUnderstanding the SkyWater PDKLayersTitanium Nitride (TiN)aka "Local interconnect"sky130_fd_sc_hd__nand2_2localinterconnect(blue)localinterconnect(blue)strapped withmetal1(purple)Layerspoly contactnitride polycut layer(NPC)via1via2via3via40.36µm 0.36µm 0.845µm 0.845µm 1.26µmmetal1metal2metal3metal4metal5mconback-end metal stack0.1µm local interconnect。

uart的基本编程步骤

uart的基本编程步骤UART(通用异步收发传输)是一种常见的串行通信协议,用于在微控制器和外部设备之间进行数据传输。

下面是UART的基本编程步骤:1. 初始化UART,首先,你需要在微控制器上初始化UART模块。

这通常涉及设置波特率(通信速率)、数据位、停止位和校验位等参数。

这些参数的设置取决于你的具体应用需求和外部设备的要求。

2. 配置引脚,UART通常使用两个引脚进行数据传输,一个用于发送(TX),一个用于接收(RX)。

你需要在微控制器上配置这些引脚,并确保它们与外部设备正确连接。

3. 发送数据,要发送数据,你需要将要发送的数据加载到UART发送缓冲区。

一旦数据被加载,UART模块将自动开始发送数据。

你需要确保发送的数据符合UART的规范,并且在发送数据之前,需要检查发送缓冲区是否为空,以避免数据丢失。

4. 接收数据,接收数据与发送类似,你需要设置接收缓冲区,并在接收到数据后从中读取数据。

同样,你需要检查接收缓冲区是否有新的数据可用,以避免数据丢失。

5. 中断处理(可选),在一些情况下,你可能需要使用中断来处理UART的发送和接收。

这可以帮助你及时响应数据的到来或发送完成等事件。

6. 错误处理,最后,你需要考虑如何处理可能出现的错误,比如数据丢失、校验错误等。

这可能涉及到错误标志的检查和相应的处理流程。

总的来说,UART的基本编程步骤包括初始化UART模块、配置引脚、发送数据、接收数据、中断处理(可选)和错误处理。

在实际编程中,你需要根据具体的微控制器型号和外部设备的通信协议要求来进行相应的设置和处理。