集成电路设计基础作业题解答

1+X集成电路理论练习题含参考答案

1+X集成电路理论练习题含参考答案一、单选题(共40题,每题1分,共40分)1、在电子产品测试中需保证测试环境稳定,其中使用环境稳定是指()。

A、使用人员操作得当B、硬件的工作参数稳定C、软件的工作参数稳定D、模拟真实用户使用时的场景正确答案:D2、以全自动探针台为例,关于上片的步骤,下列所述正确的是:( )。

A、打开盖子→花篮放置→花篮下降→花篮到位→花篮固定→合上盖子B、打开盖子→花篮放置→花篮到位→花篮下降→花篮固定→合上盖子C、打开盖子→花篮放置→花篮下降→花篮固定→花篮到位→合上盖子D、打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子正确答案:D答案解析:以全自动探针台为例,上片的步骤为:打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子。

3、转塔式分选机设备进行编带后,进入( )环节。

A、上料B、测试C、外观检查D、真空包装正确答案:C答案解析:转塔式分选机设备芯片检测工艺的操作步骤一般为:上料→测试→编带→外观检查→真空包装。

4、通常情况下,一个内盒中装入的DIP管装芯片( )颗。

A、3000B、1000C、5000D、2000正确答案:D答案解析:一般情况下,一个内盒中装入的DIP管装芯片2000颗。

5、元器件的引线直径与印刷焊盘孔径应有()的合理间隙。

A、0.1~0.4mmB、0.2~0.3mmC、0.1~0.3mmD、0.2~0.4mm正确答案:D6、在电子电路方案设计中最简单的显示平台是()。

A、OLEDB、LCDC、LEDD、数码管正确答案:C7、平移式分选机进行料盘上料时,在上料架旁的红色指示灯亮的含义是( )。

A、上料机构故障B、上料架上有料盘C、上料架上有空料盘D、上料架上没有料盘正确答案:B答案解析:平移式分选机进行料盘上料时,上料架上是否有料盘可以通过上料架旁的传感器进行检测。

当传感器指示灯为红色时,表明上料架上还有料盘,可以继续进行上料,当传感器指示灯为绿色时,表明上料架上无料盘,停止上料。

集成电路设计基础 课后答案

班级:通信二班姓名:赵庆超学号:200712012977,版图设计中整体布局有哪些注意事项?答:1版图设计最基本满足版图设计准则,以提高电路的匹配性能,抗干扰性能和高频工作性能。

2 整体力求层次化设计,即按功能将版图划分为若干子单元,每个子单元又可能包含若干子单元,从最小的子单元进行设计,这些子单元又被调用完成较大单元的设计,这种方法大大减少了设计和修改的工作量,且结构严谨,层次清晰。

3 图形应尽量简洁,避免不必要的多边形,对连接在一起的同一层应尽量合并,这不仅可减小版图的数据存储量,而且版图一模了然。

4 在构思版图结构时,除要考虑版图所占的面积,输入和输出的合理分布,较小不必要的寄生效应外,还应力求版图与电路原理框图保持一致(必要时修改框图画法),并力求版图美观大方。

8,版图设计中元件布局布线方面有哪些注意事项?答:1 各不同布线层的性能各不相同,晶体管等效电阻应大大高于布线电阻。

高速电路,电荷的分配效应会引起很多问题。

2 随器件尺寸的减小,线宽和线间距也在减小,多层布线层之间的介质层也在变薄,这将大大增加布线电阻和分布电阻。

3 电源线和地线应尽可能的避免用扩散区和多晶硅布线,特别是通过较大电流的那部分电源线和地线。

因此集成电路的版图设计电源线和地线多采用梳状布线,避免交叉,或者用多层金属工艺,提高设计布线的灵活性。

4 禁止在一条铝布线的长信号霞平行走过另一条用多晶硅或者扩散区布线的长信号线。

因为长距离平行布线的两条信号线之间存在着较大的分布电容,一条信号线会在另一条信号线上产生较大的噪声,使电路不能正常工作。

、5 压点离开芯片内部图形的距离不应少于20um,以避免芯片键和时,因应力而造成电路损坏。

集成电路设计习题答案-章精品

集成电路设计习题答案-章精品CH11.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律?晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。

MOORE 定律2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。

拥有设计人才和技术,但不拥有生产线。

特点:电路设计,工艺制造,封装分立运行。

环境:IC产业生产能力剩余,人们需要更多的功能芯片设计3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义?MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。

意义:降低成本。

4.集成电路设计需要哪四个方面的知识?系统,电路,工具,工艺方面的知识CH21.为什么硅材料在集成电路技术中起着举足轻重的作用?原材料来源丰富,技术成熟,硅基产品价格低廉2.GaAs和InP材料各有哪些特点? P10,113.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触?接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触4.说出多晶硅在CMOS工艺中的作用。

P135.列出你知道的异质半导体材料系统。

GaAs/AlGaAs, InP/ InGaAs, Si/SiGe,6.SOI材料是怎样形成的,有什么特点?SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。

特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低7. 肖特基接触和欧姆型接触各有什么特点?肖特基接触:阻挡层具有类似PN结的伏安特性。

欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。

8. 简述双极型晶体管和MOS晶体管的工作原理。

P19,21CH31.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。

意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。

射频与通信集成电路设计习题参考答案

RL (1 Q2 ) RS

Q RS 1 50 1 0.816

RL

30

X Lp

X L' (1

1 Q2

)

QRL (1

1 Q2

)

61.24

Q L ' L ' QRL

RL

L QRL 15 0.81630 15 0.63nH 2π 2.4109

LP

X Lp

61.24 2π 2.4109

Qn=2 4.58nH

2.91nH

1.53pF

(b)

(b)

Qn=2

2.44nH

2.61pF

3.76pF

Qn=2

1.79pF

1.69nH

2.22nH

6

东南大学《射频集成电路设计基础》课程

(二)计算法 1)L 型匹配网络计算

L

j15

L’

LP

C

0(RL)

C

习题参考答案 Z. Q. LI RL(1+Q2)

(a)

(b)

L=0.64nH C=1.09pF

C=1.67pF L=4.06nH

5

东南大学《射频集成电路设计基础》课程

2)具有最大节点品质因数为 2 的 T 型匹配网络

习题参考答案 Z. Q. LI

Qn=2 947.6fF

890.9fF

2.9nH

(a) 3)具有最大节点品质因数为 2 的型匹配网络 (a)

(d) ZIN 2Zo ,

1 ΓIN = 3

2.7 请将下图中 Smith 圆图上的曲线与它们的性质对应起来,并填入到下表中。

曲线性质

曲线编号

某频率点上的 LC 网络阻抗匹配

射频集成电路与系统 RFIC习题_参考答案

L=0.64nH

C=1.09pF

( b)

C=1.67pF

L=4.06nH

5

东南大学《射频集成电路设计基础》课程

习题参考答案 Z. Q. LI

2)具有最大节点品质因数为 2 的 T 型匹配网络

Qn=2 947.6fF 890.9fF

4.58nH

Qn=2 2.91nH

2.9nH

1.53pF

(a) 3)具有最大节点品质因数为 2 的型匹配网络 (a)

d 2

d

o

(a) Zin jZo tan d j300 tan 60 j300 3 (b) Zin jZo tan d j300 tan120 j300 3

o

(c) Zin jZo cot d j 300 cot 60 j100 3

(b)

Qn=2 2.44nH

2.61pF

3.76pF

(b)

Qn=2 1.79pF

1.69nH

2.22nH

6

东南大学《射频集成电路设计基础》课程

习题参考答案 Z. Q. LI

(二)计算法 1)L 型匹配网络计算

L j15 0(RL)

L’ C

C

LP

RL(1+Q2)

RL (1 Q2 ) RS

东南大学《射频集成电路设计基础》课程

习题参考答案 Z. Q. LI

2012 年(春) RFIC 习题 参考答案

第二章

2.4 无耗传输线特征阻抗 Z0 为 300Ω,如下图所示,当线长分别为及时,计算终端短 路和开路条件下的输入阻抗。

解: 当负载短路,即 ZL =0 时,Zin =jZo tand 当负载开路,即 ZL = 时,Zin =-jZo cotd 半波长,Zin =ZL 1/4 波长,Zin =Zo 2 /ZL

射频集成电路设计基础参考答案

=

C--C---e-2-q-

2

R2

;

而

Ceq

=

C----C-1---1+--C---C--s---s ≈ C----C-1---1-+-C---C--2---2

故有

Rp

≈

C-----1--C-+---1--C-----2

2

R2

以上推导均假设串并转换过程中电路 Q 值足够大 转换前后的电阻值之间仅为 Q2 的关系

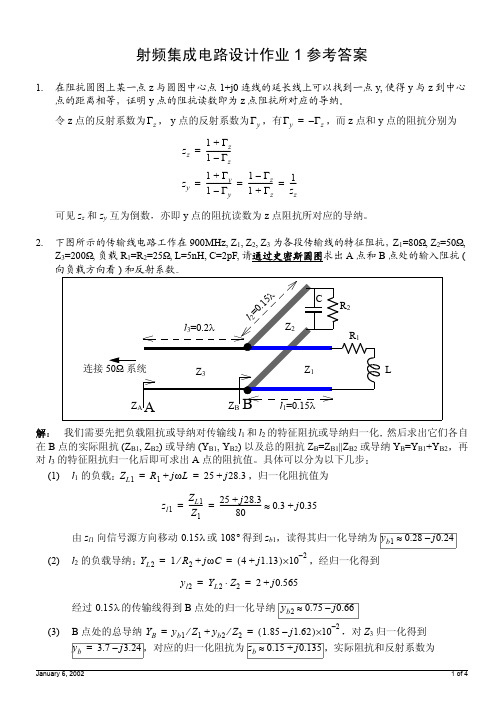

yl2 = YL2 ⋅ Z2 = 2 + j0.565

经过 0.15λ 的传输线得到 B 点处的归一化导纳 yb2 ≈ 0.75 – j0.66

(3) B 点处的总导纳 YB = yb1 ⁄ Z1 + yb2 ⁄ Z2 = (1.85 – j1.62)×10–2 对 Z3 归一化得到 yb = 3.7 – j3.24 对应的归一化阻抗为 zb ≈ 0.15 + j0.135 实际阻抗和反射系数为

射频集成电路设计作业 1 参考答案

1. 在阻抗圆图上某一点 z 与圆图中心点 1+j0 连线的延长线上可以找到一点 y, 使得 y 与 z 到中心 点的距离相等 证明 y 点的阻抗读数即为 z 点阻抗所对应的导纳

令 z 点的反射系数为Γz y 点的反射系数为Γy 有Γy = –Γz 而 z 点和 y 点的阻抗分别为

而电容值保持不变

(2) 由 Q2 = ωC2R2 = ω-----C--1--s--R----s Q = ωCpRp = ω-----C----1e--q---R----s 及 Ceq = C----C-1---1+--C---C--s---s 可得

Q = ω-----C----1e--q---R----s = ω-----C--1--s--R----s C-----1--C--+--1--C-----s = Q21 + C-C----1s

重理工集成电路设计原理思考题、作业、提问答案大全

重理工集成电路设计原理思考题、作业、提问答案大全重理工集成电路设计原理思考题、作业、提问答案大全1-1思考题典型PN结隔离工艺与分立器件NPN管制造工艺有什么不同(增加了哪些主1-1-1.1-1-1.典型典型PNPN结隔离工艺与分立器件结隔离工艺与分立器件NPNNPN管制造工艺有什么不同管制造工艺有什么不同()要工序要工序)?增加工序的的目的是什么?答:分立器件NPN管制造工艺:外延→一氧→一次光刻→B掺杂→二氧→二次光刻→P掺杂→三氧→三次光刻→金属化→四次光刻。

典型PN结隔离工艺:氧化→埋层光刻→埋层扩散→外延→二氧→隔离光刻→隔离扩散、推进(氧化)→基区光刻→基区扩散、再分布(氧化)→发射区光刻→发射区扩散、氧化→引线孔光刻→淀积金属→反刻金属→淀积钝化层→光刻压焊点→合金化及后工序。

增加的主要工序:埋层的光刻及扩散、隔离墙的光刻及扩散。

目的:埋层:1、减小串联电阻;2、减小寄生PNP晶体管的影响。

隔离墙:将N型外延层隔离成若干个“岛”,并且岛与岛间形成两个背靠背的反偏二极管,从而实现PN结隔离。

管的电极是如何引出的?集电极引出有什么特殊要求?1-1-2.NPN1-1-2.NPN管的电极是如何引出的?集电极引出有什么特殊要求?答:集成电路中的各个电极均从上表面引出。

要求:形成欧姆接触电极:金属与参杂浓度较低的外延层相接触易形成整流接触(金半接触势垒二极管)。

因此,外延层电极引出处应增加浓扩散。

典型PN结隔离工艺中隔离扩散为什么放在基区扩散之前而不放在基区扩1-1-3.1-1-3.典型典型PNPN结隔离工艺中隔离扩散为什么放在基区扩散之前而不放在基区扩散或发射区扩散之后?答:由于隔离扩散深度较深,基区扩散深度相对较浅。

放在基区扩散之前,以防后工序对隔离扩散区产生影响。

1-1作业典型PN结隔离工艺中器件之间是如何实现隔离的?1-1-1.1-1-1.典型典型PNPN结隔离工艺中器件之间是如何实现隔离的?答:在N型外延层中进行隔离扩散,并且扩穿外延层,与P型衬底连通,从而将N型外延层划分为若干个“岛”;同时,将隔离区接最低电位,使岛与岛之间形成两个背靠背的反偏二极管,从而岛与岛互不干涉、互不影响。

电子技术相关 《数字集成电路基础》作业答案

《数字集成电路基础》作业答案第一次作业1、查询典型的TTL与CMOS系列标准电路各自的VIH、VIL、VOH和VOL,注明资料出处。

2、简述摩尔定律的内涵,如何引领国际半导体工艺的发展。

第二次作业1、说明CMOS电路的Latch Up效应;请画出示意图并简要说明其产生原因;并简述消除“Latch-up”效应的方法。

答:在单阱工艺的MOS器件中(P阱为例),由于NMOS管源与衬底组成PN结,而PMOS 管的源与衬底也构成一个PN结,两个PN结串联组成PNPN结构,即两个寄生三极管(NPN 和PNP),一旦有因素使得寄生三极管有一个微弱导通,两者的正反馈使得电流积聚增加,产生自锁现象。

影响:产生自锁后,如果电源能提供足够大的电流,则由于电流过大,电路将被烧毁。

消除“Latch-up”效应的方法:版图设计时:为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;工艺设计时:降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。

为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。

工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数;具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。

2、什么是器件的亚阈值特性,对器件有什么影响?答:器件的亚阈值特性是指在分析MOSFET时,当Vgs<Vth时MOS器件仍然有一个弱的反型层存在,漏源电流Id并非是无限小,而是与Vgs呈现指数关系,这种效应称作亚阈值效应。

影响:亚阈值导电会导致较大的功率损耗,在大型电路中,如内存中,其信息能量损耗可能使存储信息改变,使电路不能正常工作。

3、什么叫做亚阈值导电效应?并简单画出logI D-V GS特性曲线。

答:GS在分析MOSFET时,我们一直假设:当V GS下降到低于V TH时器件会突然关断。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五次作业、改正图题所示TTL 电路的错误。

如下图所示:解答:(a)、B A B A Y ••=•=0,A,B 与非输出接基极,Q 的发射极接地。

从逻辑上把Q 管看作单管禁止门便可得到B A Y •=。

逻辑没有错误!若按照题干中所示接法,当TTL 与非门输出高电平时,晶体管Q 的发射结要承受高压,必然产生巨大的电流。

为了不出现这种情况,可以在基极加一电阻或者在发射极加一二极管。

但发射极加二极管后会抬高输出的低电平电压。

所以只能在基极加一大电阻,实现分压作用。

另外一种方法是采用题(a )图中的A 输入单元结构。

&&≥111(b)、要实现由,我们可以使用线与+得到和B A B A 。

但题干中的线与功能不合理。

若其中一个为高电平且另外一个为低电平时,高电平输出降会往低电平输出灌电流,从而容易引起逻辑电平混乱。

为了消除这一效应,可以在各自的输出加一个二极管。

(c)、电阻不应该接地,应该接高电平 (d)、电阻不应该接VCC ,而应该接低电平、试分析图题(a ),(b)所示电路的逻辑功能。

解答:图(a )中,单元1实现了A 的电平输入,B 是A 的对称单元。

功能单元2实现了A 和B 输入的或逻辑功能单元4充当了Q8管的泄放网络,同时抬高了Q3,Q4管的输入逻辑电平,另外该单元还将或的结果传递给了Q8管功能单元3中的Q8管实现了非逻辑,Q6和Q7复合管加强了输出级的驱动能力。

综上所述,(a )电路实现功能为B A Y +=,即或非的功能图(b)中,Q1,Q2管依然实现传递输入的功能,Q3,Q4管实现或非的功能 Q6管和Q5管以及R5,R7共同组成的泄放网络实现了电压的传递Q9管实现了非功能,Q7,Q8管依然是用来驱动负载的。

Q9管和Q7,Q8轮流导通 综上所述,(b )实现的功能为B A B A Y +=+=第六次作业:已知一ECL 电路如图题所示,其Vcc=0V ,V EE =-,V BEF =,V BB =-,逻辑摆幅V L =且对称于参考电压,各管的I E,MAX =5mA ,并假设输入和输出的逻辑电平V i ,V o 相互匹配,且忽略基极电流的影响。

(1)试计算电阻R3,R4的数值 (2)试确定电阻R1,R2,和R E 值解答电路的逻辑功能如下:(1)、当A 输入为高电平V OH 时,Q1,Q2的发射极c 点电位被钳制住,Q1管放大,Q2管截止。

(2)、当A 输入为低电平V OL 时,V BB 将c 点电位钳制在-,此时Q1管截止,Q2管放大。

Q3和Q4是单管禁止门射极跟随器,只是起电平传递的作用,并不会改变a 、b 点电位的输出极性和相位。

因为逻辑电平摆幅为V L =,且对称于参考电压,则V OH =-, V OL =-。

当时=V V i 8.0-e 点被钳位在-,所以Q2管截止,此时a 点输出属于低电平逻辑。

V V Y 6.1-=上的电流达最大。

,此时通过大情况的=比点的电位为这种情况下E RE i C R V V V V V V C )0.26.1(6.1-=--=mA I V V V V R MAX E RE E 59.2)5.4(6.1,==---=,而上的电压降为Ω==580,MAXE RE E I V R 所以Ω===-=+-=+=16058.08.08.06.18.0,1mAVI V R V V V Y MAXE a e a 。

所以以输出为低电平逻辑,所此时当时=V V i 6.1-Q1管截止, a 点为逻辑高电平。

输出为高电平即Y V V V V a e ,8.08.0-=-=。

此时通过R 3的电流最大。

Ω==74057.33mAVR 故有 Q2管导通Ω=====-=-=18631.48.0,31.45805.20.28.02mAVR d b mA R V I V V V E RE RE BB C 点为低电平逻辑。

,此时,为了保证电平逻辑正常,当d 点电平为高逻辑电平的时Q4管的电流达到最大值I E,MAX 。

故有V V R 7.3)5.4(8.04=---=,Ω===74057.3,44mAVI V R MAXE R 综上所述:Ω=Ω==Ω=Ω=5807401861604321E R R R R R ,,,、已知图题中ECL 门电路的V +=3V ,V -=-3V ,V BEF =,R1=R2=500Ω,R E =2k Ω,假定平V i 和V o 的高低电平预地电平对称,并且当输入为低电平时的空载功耗为20mW 。

(1)、计算电阻R4和R5,忽略基极电流的影响 (2)、确定逻辑摆幅,忽略基极电流的影响解答若A 、B 的输入都为低电平的情况下Q1,Q3管截止,Q2管导通。

R E 两端的电压为,通过R E 的电流为mA kR V I E RE RE 15.123.2===。

通过电阻R 2的电流I R2=I RE =,R 2上的电压降为V R2=R 2×I R2=,Q4管发射极电压为3--=,此时V o 输出为低电平,便可列出方程:V R R R V V V OL 3)3(725.1554-•+--=.....................................①若A 、B 中有一个输入是高电平,则Q2管被截止,此时V O 输出为高逻辑电平。

同样可以列出方程V R R R VV V OH 333.2545-•++=……………………………. ②由于V o ,V i 的高电平和低电平相对地对称,所以有OL OH V V -=...............................................................................③又因为在双输入都为低电平的情况下,电路的空载功耗为20mW ,可以得到如下方程mW V R R VV V mA 2063725.1615.154=•+++•………………④上述四个方程联立可得到:V V V V R k R OL OH L 33.0)165.0(165.08673.145=--=-=Ω==,逻辑摆幅,、图题是一个早期ECL 电路 (1)、计算输出X 处的V OH 和V OL (2)、若要求V Y =V X ,试计算R1的值。

解答:(1)当A 输入为高电平V OH 时,Q2管截止,X 输出为高电平;V V V CC OH 5.08.0=-=当A 输入为低电平时,Q1管截止,Q2管放大,X 输出为低电平。

V V b Q 3.01754208.02.33.14=•--=所以输出低电平为V V V b Q OL 5.08.04-=-=(2)若要使得V X =V Y ,则1754202.38.04202.38.01•+-=•+-R V OH ,解得R 1=145Ω第七次作业:、图题所示的I 2L 反相器,I 0=10uA ,除8.0=R α外,其他数据采用标准的晶体管数据。

(1)设仅有一个集电极(C 1)连到同类反相电路,试计算C 1处的V OH 和V OL ; (2)设有三个集电极每个都接到一个负载门上,试计算C 1处的V OH 和V OL ;解答:晶体管参数默认取值为mV V R R NPN CES ES B 50(600400=Ω=Ω=-本征饱和压降),,,R CS 忽略不计。

(1)、C1接负载门的情况当A 输入是高电平时输出C1是低电平,后级输入管截止,当前级的NPN 管饱和导通。

由于C1的负载是同类的反相电路,后级PNP 管处于临界饱和状态,C1的低电平V OL =V CES-NPN (当前NPN 管的本征饱和压降)+I E ×R E =V CB-PNP (PNP 管临界饱和下的集电极-基极电压) +I E ×R E 。

所以V OL =50+12mV当A 输入是低电平时输出C1是高电平,后级输入管饱和导通,当前级的NPN 管截止。

由于C1的负载是同类反相电路,后级PNP 管处于深饱和状态,C1的高电平V OH =V BE-NPN +I B ×R B ≈ (2)、三个集电极输出C1,C2,C3都接到一个负载门当输入A 为低电平时,当前NPN 管截止,C1,C2,C3各自的PNP 管电流灌如各自的NPN 管,对逻辑高电平没有影响。

V OH (多负载输出)= V OH (单负载输出)=当输入A 为高电平时,当前NPN 管要吸收三个PNP 管集电极注入的电流,NPN 管41=-=ααβ,忽略PNP 管临界饱和与深饱和带来的共基放大倍数的影响。

NPN 管正常条件下集电极承载的最大电流为40μA>10μA ×3。

V OL =V CES-NPN (当前NPN 管的本征饱和压降)+I E ×R E =50mV+40μA ×600Ω=74mV、A 、B 、C 、D 为四个变量,设计一个I 2L 电路以实现“与或非”的电路功能,即CD AB Y +=D C B A CD AB Y •••=•=电路图略、试设计一个简单的I 2L 电路以完成3输入变量A 、B 、C 的逻辑功能C A F B A F +=+=21和C A C A F B A B A F •=+=•=+=21,电路图略、试用I 2L 电路画出CD AB F +=的电路图CD==F•+ABCDAB电路图略、给定一个由6个I2L门组成的网络的版图,如图题所示,通过变换这些门的位置去减少高度。

假定在每个门的矩形中,集电极对基极距离相等,则图题所示的网络的版图高度是5这次作业电子版的图太难画了,什么时候给大家一个书面版的!。