A new BICS for CMOS operational amplifiers by using oscillation test techniques

空气介质天线(英文)

Compact Low Cost Antenna for Passive RFID Transponder Yuri Tikhov*, Yongjin Kim, and Young-Hoon MinSamsung Advanced Institute of TechnologyP.O. Box 111, Suwon 440-600, Korea, http://www.sait.samsing.co.krE-mail: tikhov@sait.samsung.co.krThis work discloses a new compact planar antenna for low cost RFID passive transponders. The proposed antenna takes advantage of its unique topology in order to assure conjugate matching with essentially complex impedance of the electronic chip directly embedded into radiator. Good performance is predicted theoretically and confirmed experimentally over an operating bandwidth of actual RFID system.IntroductionMarket research predicts that worldwide revenues from Radio Frequency Identification (RFID) transponders will jump to $2.8 billion in 2009 [1]. RFID transponder is a tag device that can respond by sending a content of its embedded memory by backscatter communication to interrogator (reader). A passive RFID transponder (tag) has no battery, instead it gets all the needed energy from the carrier signal of the reader.Generally, the transponder comprises an Application Specific Integrated Circuit (ASIC) connected to an antenna. Planar antennas for RFID tags with substantially small electrical size are strongly focused in recent years. Because nowadays the antenna size of even a quarter wavelength is precluded in many applications. Another challenge is an extremely low cost requirement in most consumer applications. While it is expected that a tag will cost a few cents in a very mass production, today the best cost is in order of magnitude higher than a projected target. Of course the cost of tags has been driven down mainly by CMOS technology for very small ASIC itself and the effective process of mounting the chip into the tag. At the same time the cost of antenna becomes also rather important. It might be ridiculous in conventional cases, but now even a bulk per tag of conductive material, such as copper or silver ink used for a huge volume production, should be reduced to a minimum.The authors have recently introduced a novel small planar antenna for RFID and a wireless sensor transponder that can operate over enhanced bandwidth without any affect on radiation pattern, gain, and polarization purity [2]. Reported antenna comprises a thin metal layer formed on a surface of thin flexible dielectric substrate, and an original slot pattern within said layer. Antenna based on the slot pattern demonstrates very good radiation performances but generally suffers from the fact that it requires substantial amount of conductive material to form a ground layer.In this paper our idea of small slot-based antenna [2] is extended to its strip-based topological realization. We propose an antenna configuration that consumes substantially less conductive material then our previous one and at the same time can operate without affect on characteristics of RFID tag.Antenna StructureThe strip pattern is formed on the surface of a flexible dielectric substrate. The photograph of realized UHF transponder prototype is shown in Fig. 1. ASIC has been flip-chip bonded directly into radiating element of the antenna. ASIC can be seen as a centrally placed dark spot in Fig. 1.Since the overall required size of antenna issubstantially less than a quarterwavelength, the length of the main strip isall the more so shorter. Taking into accountthe fact that for the case of electricallysmall antenna the phase difference of theelectromagnetic field along the radiatingpart is small, the clockwise andcounterclockwise convolute strip armsprovide the antenna with uniqueelectromagnetic features. Indeed, there are Fig. 1.Photo of assembled transponder.six sectors at each end of the main stripwith the flow of electric current being in the same direction as at the main radiating strip. While the opposite flow with substantially low amplitude exist only on two sectors. A consequent unique alteration in a field distribution supports the resonant features of the radiator. At the same time a useful part of the current at terminating strip arms is reclaimed successfully, thereby increasing the area of antenna that effectively participates in the radiation phenomenon.An additional circle strip (Fig.1) has been created in order to match the antenna impedance with the impedance of the transponder ASIC. Impedance matching between ASIC and antenna is critical on overall RFID system performance [3]. Namely the mismatch very strongly affect a read range – a maximum operating distance between interrogator and transponder. Because the power radiated by interrogator is rather limited due to certain safety regulations and other legislation. And passive transponder extracts its operating power by rectifying interrogation signal delivered by the antenna. Rectifier circuit is a part of ASIC and comprises diodes (such as Schottky diodes) and capacitors, resulting in the complex input impedance with substantial capacitive reactance. Typically the impedance of ASIC comes to a few or tens of active Ohms and a few hundreds of reactive (capacitive) Ohms. Thus the ratio of the reactance to the resistance is very high. The combination of circle strip and convolute strip arms provides the compact antenna with specified ratio of inductive reactance to the resistance. Thereby it assures direct conjugate matching between antenna and ASIC of passive RFID transponder over operating bandwidth.MeasurementMeasurements of electrically small antennas are basically impeded because every sort of cable connection between antenna and Network Analyzer generally disturbs the field near the antenna. Such field disturbance is very severe in the case of antennas with non-traditional feeding by means of direct chip inlet into small radiator. Consequently special measures are required to obtain sufficiently accurate experimental verification of transponder antenna.To overcome this problem, instead of measurement of full antenna, a half of antenna structure has been measured with metal plate of substantial electrical size replacing the E-symmetry-plane. The impedance of a half-antenna with metal plate amounts to a half of impedance of the full antenna. The photograph of the measurement setup is shown in Fig.2. The metal plate is composed of a stainless steel part (1m x 1m) and a brass part (16cm x 16cm). The composition of two parts is chosen for convenience of assembling with replaceable features of small brass part. The cable of Network Analyzer is hidden under the metal plate.Fig. 2.Measurement setup. Fig.3. Half-antenna mounted on the plate.The adjacent metallization of antenna is soldered to brass plate as shown in Fig. 3. The feeding point of antenna is soldered to a central pin of SMA connector. The pin of SMA connector passes through the circular hole in the plate thereby forming a small 50-Ohm section of coaxial line. Since the antenna possesses a mechanical flexibility it has been fixed in normal position to metal plate by two foam posts. The dielectric permittivity of the foam material is close to one of air, so the posts almost do not affect electromagnetic field distribution.The measurements have been performed with Agilent 8722ES Network Analyzer. It should be noted that Network Analyzer has been pre-calibrated without input SMA connector of the test structure. So the reference plane is somewhat below the surface of the metal plate. Besides the coaxial connector itself superinduces capacitive reactanceFig. 4. Comparison of simulated and measured impedance of test structure:symbols –measurement,dashed simulation.Fig. 5. De-embedded impedanceof half-antenna.into the object under test. Therefore resulting resonant frequency must be shifted down.The effect of additional reactance and shift of reference plane has been simulated by HFSS [4]. Fig. 4 shows a comparison between simulated and measured results. Excellent agreement between theoretical prediction and experiment is observed. Fig. 5 shows the half-antenna impedance after de-embedding of reference plane and parasitic reactance of the SMA connector. It can be observed that if double both real and imaginary part of impedance of half-antenna (2.97+j133.6 Ohms @ 915 MHz) those are very close to complex impedance of designed full antenna.The simulated return loss of full antenna ifloaded by specified impedance of actualRFID tag chip is shown in Fig. 6. It hasbeen assumed that complex impedance ofthe chip is constant 6-j270 Ohm. It isobserved that achieved operatingbandwidth of the antenna is 14.4 MHz(1.6%) at the level of –10dB return loss.Actual overall size of antenna is 7.2cm x4.1cm. It amounts to 0.220λ×0.130λ,where 0λ is the wavelength in a free spaceat the center frequency of 915 MHz.As expected, the radiation patterndemonstrates omnidirectional properties inthe principal H-plane. The radiation null isobserved at the longitudinal axis of the main strip. The achieved peak gain value is +1.7dBi. The simulated radiation efficiency amounts to 83 percent and takes into account both metal and dielectric losses. The polarisation of antenna is substantially linear since an orthogonal field is negligible. Besides the small size precludes from a phase shift between orthogonal field components being sufficient for substantially elliptical polarisation.ConclusionA new low cost planar antenna has been proposed for compact passive transponder. The antenna impedance has been directly conjugate matched with essentially complex impedance of the electronic chip inlet over the 1.6-% bandwidth. Precise prototyping and accurate measurements guarantee a veracity of the results.References[1] A. Nogee, “RFID tags and chips,” RFID Journal , , pp. 1-2,Jan. 2005.[2] Y. Tikhov, Y.J. Kim, and Y.H. Min, “Electrically Small Antenna for RFID andWireless Sensor Transponders,” Proc. of International Symposium on Antennas and Propagation, ISAP2005, Seoul, Korea, August 3-5, 2005, vol. 3, pp. 1041-1044.[3] K. V .S. Rao, P. V. Nikitin, and S. F. Lam, “Antenna Design for UHF RFID Tags: AReview and a Practical Application,” IEEE Trans. Antennas Propag ., vol. 53, no.12, pp. 3870-3876, Dec. 2005.[4] High-Frequency Structure Simulator, HFSS v. 9.2, trademark of Ansoft Corporation,Four Station Square, Pittsburgh, PA 15219-1119, USA.Fig. 6. Simulated return loss of full antenna terminated by ASIC chip of RFID transponder.。

应用光伏学题库

一、选择题(在下列每题的四个选项中,只有一个选项是符合试题要求的。

请把答案填入答题框中相应的题号下。

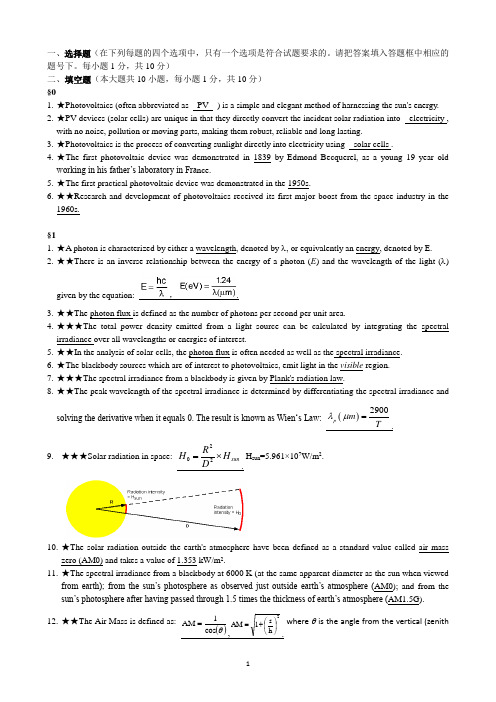

每小题1分,共10分)二、填空题(本大题共10小题,每小题1分,共10分)§01. ★Photovoltaics (often abbreviated as PV ) is a simple and elegant method of harnessing the sun's energy.2. ★PV devices (solar cells) are unique in that they directly convert the incident solar radiation into electricity , with no noise, pollution or moving parts, making them robust, reliable and long lasting.3. ★Photovoltaics is the process of converting sunlight directly into electricity using solar cells .4. ★The first photovoltaic device was demonstrated in 1839 by Edmond Becquerel, as a young 19 year old working in his father‘s laboratory in Fra nce.5. ★The first practical photovoltaic device was demonstrated in the 1950s.6. ★★Research and development of photovoltaics received its first major boost from the space industry in the 1960s.§11. ★A photon is characterized by either a wavelength, denoted by λ, or equivalently an energy, denoted by E.2. ★★There is an inverse relationship between the energy of a photon (E ) and the wavelength of the light (λ) given by the equation: ,.3. ★★The photon flux is defined as the number of photons per second per unit area.4. ★★★The total power density emitted from a light source can be calculated by integrating the spectral irradiance over all wavelengths or energies of interest.5. ★★In the analysis of solar cells, the photon flux is often needed as well as the spectral irradiance.6. ★The blackbody sources which are of interest to photovoltaics, emit light in the visible region.7. ★★★The spectral irradiance from a blackbody is given by Plank's radiation law.8. ★★The peak wavelength of the spectral irradiance is determined by differentiating the spectral irradiance and solving the derivative when it equals 0. The result is known as Wien‗s Law: ()2900p m T λμ=.9. ★★★Solar radiation in space: sun H D R H ⨯=220.H sun =5.961×107W/m 2.10. ★The solar radiation outside the earth's atmosphere have been defined as a standard value called air masszero (AM0) and takes a value of 1.353 kW/m 2.11. ★The spectral irradiance from a blackbody at 6000 K (at the same apparent diameter as the sun when viewedfrom earth); from the sun‘s photosphere as observed just outside earth‘s atmosphere (AM0); and from the sun‘s photosphere after having passed through 1.5 times the thickness of earth‘s atmosphere (AM1.5G).12. ★★The Air Mass is defined as: θ is the angle from the vertical (zenithangle).13. ★★When the sun is directly overhead, the Air Mass is 1.14. ★The standard spectrum at the Earth's surface is called AM1.5G (the G stands for global and includes bothdirect and diffuse radiation) or AM1.5D (which includes direct radiation only), these calculations give approximately 970 W/m 2 for AM1.5G 。

bios恢复默认值(BIOSrestoresdefaultvalues)

bios恢复默认值(BIOS restores default values)BIOS restores default valuesBoot press DELETE button to enter BIOS, in Load, Default, Configuration, Load, Optimized, Configuration, these two, select which of which can be reduced to factory settings, do not forget to save F10 exit.The load fail-safe defaults loads the CMOS default value of the bios.The load optimized defaults loads the default COMS value of the optimized, and this setting is relatively useful for setting the speed of the main board.Generally speaking, the two, can not find the previous one, behind the line, see the different brand setting method of the motherboard is different, but the same ah.If you like hands-on, physics settings are most direct ~!Take down the battery on the motherboard directly, and then install it to restore it!There are usually two waysA: the old motherboard may only install the motherboard battery back, it has cleared the CMOS memory effectTwo: new motherboard (usually after 2004), should be used to clear the CMOS jumper, you just jump the cap to pick up, youcanBIOS in one or two DEFAUT options, LOAD once you can, and do not have much troubleThe above 1 and 2 answer need to disassemble the box, more troublesome; third answer also did not say very clear, for computer beginners, a bit difficult; the following is my answer: for all applicable:Boot, and so on when the display of English, and constantly press the keyboard on the Del key or Delete key, enter the BIOS settings interface, to find load, Optimized, Defaults entries, this item means "restore factory settings."".Move the cursor to the item with the arrow keys, press the "Enter" key, then move the cursor to Save & Exit Setup, press the "Enter" key, and appear in the dialog box" The back is "Y", and if "N", press "Y" directly, then enter. At this time to complete; if it is to display the BIOS menu interface, directly move the cursor to the "Exit" menu, below one for "Load Setup Defaults", press "Enter" button, select "Exit Saveing Chang" click "Enter" button, the dialog box that appears "?" The back is "Y", and if "N", press "Y" directly, then enter.DELL series computer, restart the computer, see the blue DELL logo screen, the upper right corner of the screen will be prompted: F2=Setup, F12=Boot Menu (highlighted), then quickly press F2 or the corresponding button, you can enter the BIOS settings.Optiplex desktop series:How do I get into BIOS?1. turn on or restart the computer;2. when you see the DELL icon, press the "F2" button immediately to enter the system settings (BIOS)";Restore BIOS original functionalityIn the BIOS interface, respectively, according to Caps Lock, Num Lock (CAPS) (digital lock) and Scroll Lock (scroll lock) "button, lit the keyboard on the Caps Lock, Num Lock (caps lock) (digital lock) and Scroll Lock (scroll lock)" three lights, and then according to the following 3 key combinations:Alt+E - clears (releases) interrupts resources and starts redistribution next time. After you press this combination key, you'll hear a crisp "Bi -" sound.Alt+F - restore factory settings. After you press this combination key, you'll hear a crisp "Bi -" sound.Alt+B - reboot.Clear Password method 1: after the password input box appears, enter the password, press the Ctrl key and the Enter key at the same time.Clear PassWord method two: use MB on the PSWD jumper, pull outthe boot system, set the password blank in BIOS, turn off the system, and plug back into the PSWD jumper.Dimension series desktops:How do I get into BIOS?1. turn on or restart the computer;2. when you see the DELL icon, press the "F2" button immediately to enter the system settings (BIOS)";Restore BIOS original functionalityIn the BIOS interface, respectively, according to Caps Lock, Num Lock (CAPS) (digital lock) and Scroll Lock (scroll lock) "button, lit the keyboard on the Caps Lock, Num Lock (caps lock) (digital lock) and Scroll Lock (scroll lock)" three lights, and then according to the following 3 key combinations:Alt+E - clears (releases) interrupts resources and starts redistribution next time. After you press this combination key, you'll hear a crisp "Bi -" sound.Alt+F - restore factory settings. After you press this combination key, you'll hear a crisp "Bi -" sound.Alt+B - reboot.Or set the Reset Config Data on the BIOS interface - which is equivalent to the above "Alt+E"".Latitude series notebooks:How do I get into BIOS?1. turn on or restart the computer;2. when you see the DELL icon,Press the "F2" button immediately to enter the system settings (BIOS)";Restore BIOS original functionalityLatitude C; CP; CS series system: restart the computer, press "F2" to enter the BIOS settings state, press Alt+F to restore the original settings of CMOS. After you press this combination key, you'll hear a crisp "Bi -" sound;L series system: restart the computer, press "F2" to enter the BIOS settings, press F9 to restore the original settings of CMOS.Inspiron series notebooksHow do I get into BIOS?1. turn on or restart the computer;2. when you see the DELL icon, press the "F2" button to enter the system settings (BIOS);Restore BIOS original functionalityRestart the computer, press F2 to enter the BIOS settings, and press Alt+F to restore the CMOS original settings. After you press this combination key, you'll hear a crisp "Bi -" sound;For some different versions of BIOS, you can restore the original CMOS settings by pressing F9.。

科技英语写作练习6-7-8

科技英语写作练习6-7-8练习6I.1. This image, it will be noticed, is a real image.2. This device, it is said, was commercially available three years ago.OR: This device is said to have been commercially available.3. This technical problem, we hope, will be solved soon.4. These systems will be presented in what the author hopes is a concise manner.5. 210 is approximately 1000, a fact that we think is very useful in the study of digital electronics.6. A resistor of say 100 ohms should be used here.7. Velocity is, we have noted before, a vector.II.1.No circuit has no resistance. OR: There is not a single circuit but has any resistance.2.None of those textbooks have/has mentioned this point.3.All of these x values cannot satisfy the equation.4.Neither of the two conditions is satisfied.5.In the preceding chapter, we discussed all kinds of force.6.This paper describes a new method for designing aircraft.7.By the end of the last century, the company had manufactured 5,000 radars.8.Since 2002, this research institute has been developing a special kind of robot.9.All the computers in our laboratory are not very good in quality.10.The students are familiar with none of these parameters.III.1.In section 1-2, the concept of force was introduced.2.As early as the 1940s, it was found that semiconductors are very useful.3.This result can also be arrived at in another way.4.At that time no use was made of this phenomenon.OR: At that time, this phenomenon was made no use of.5.This point will be dealt with in the next section.IV.这台机器的性能比那台好得多。

音译汉翻译

1 The transistor is what started the evolution of the modern computer industry in motion.晶体管开启了现代电脑工业的革命2 The storage cell only requires one capacitor and one transistor, whereas a flip-flop connected in an array requires 6 transistors.存储单元仅需要一个电容和晶体管,并而不像触发器整列那样需要6个晶体管3 There hase been a never ending series of new op amps released each year since then, and their performance and reliability has improved to the point where present day op amps can be used for analog applications by anybody.从此以后每年都有新系列的运放发布,他们的性能和可靠性得到了提升,如今任何人都能用运放来设计模拟电路。

4 This is capable of very high speed conversion and thus can accommodate high sampling rates, but in its basic form is very power hungry.它具有高速转换能力,从而能适应高速采样速率,但它的基本形式非常耗电。

5 During the “on” period , energy is being stored within the core material of the inductor in the form of flux.在”on”阶段,能量以涌浪形式存储在电感的核芯材料里面6 The design goal of frequency synthesizers is to replace multiple oscillators in a system, and hence reduce board space and cost.频率合成器的设计目标是取代系统中多个振荡器,从而减小板卡面积和成本。

汉译英_高级职称

The mistake escaped my notice.

9.只有在显微镜下才能看见红血球。

A microscope is needed (for us) to see red cells.

10.2000年奥运会将在悉尼举行。

Sydneywill host (be the host city for) the 2000 Olympic Games.

After a careful check of the blueprint, they made comments on his design.

6.据说在质量方面这种仪器是优越的。

It is said that this instrument is high in quality.

2.不同国家的社会习俗往往大相径庭。

Social customs are usually different from country to country.

3.我们应该尽我们最大的努力防止这类事故再次发生。

We should do our best to prevent this kind of accident from happening again.

At the end of this century, the world population will be over six billion.

2.去年,这个国家的工农业总产值为两千亿美元。

Last year, the general output value of industry and agriculture of this country was two hundred billion dollars.

八年级英语科技发明原理深奥解析单选题40题(答案解析)

八年级英语科技发明原理深奥解析单选题40题(答案解析)1.The most important part of a computer is the _____.A.keyboardB.mouseC.monitorD.processor答案:D。

“keyboard”是键盘,“mouse”是鼠标,“monitor”是显示器,“processor”是处理器。

在计算机中,处理器是最重要的部分,因为它负责执行指令和处理数据。

2.Inventions can make our lives _____.A.easierB.harderC.busierD.worse答案:A。

“easier”是更容易,“harder”是更难,“busier”是更忙,“worse”是更糟。

发明通常会让我们的生活更容易。

3.The light bulb is a great _____.A.inventionB.discoveryC.creationD.production答案:A。

“invention”是发明,“discovery”是发现,“creation”是创造,“production”是生产。

电灯泡是一项伟大的发明。

4.A new type of robot can help people do _____ jobs.A.dangerousB.easyC.interestingD.boring答案:A。

“dangerous”是危险的,“easy”是容易的,“interesting”是有趣的,“boring”是无聊的。

新型机器人可以帮助人们做危险的工作。

5.The telephone was invented by _____.A.Thomas EdisonB.Alexander Graham BellC.Guglielmo MarconiD.James Watt答案:B。

托马斯·爱迪生发明了电灯等,亚历山大·格拉汉姆·贝尔发明了电话,古列尔莫·马可尼发明了无线电,詹姆斯·瓦特改良了蒸汽机。

(11) Components in Your New Rig_Info&Q&As (68)

Zener diode

Schematic symbol of a Zener diode. Since a diode only passes current in one direction, look for the one-way arrow plus a “Z” to indicate it is a Zener diode.

E6A15…

•

Free electrons are the majority charge carriers in N-type semiconductor material.

E6A17…

•

•

P-type semiconductor material contains fewer free electrons than pure germanium or silicon crystals. E6A18… The names of the three terminals of a field-effect transistor are gate, drain, and source.

Amateur Radio Extra Class

Components in Your New Rig

• E6B01…

The principal characteristic of a Zener diode is a constant voltage under conditions of varying current.

E4A10…

+0.7 V

Amateur Radio Extra Class

Components in Your New Rig

•

•

•

Alpha cutoff frequency indicates the frequency at which a transistor grounded base current gain has decreased to 0.7 of the gain obtainable at 1 kHz. E6A09… A depletion-mode FET is a FET that exhibits a current flow between source and drain when no gate voltage is applied. E6A10… In Figure E6-2, the schematic symbol for an N-channel dual-gate MOSFET is number 4.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A new BICS for CMOS operational amplifiers by usingoscillation test techniquesJ.Font *,R.Picos,M.Roca,E.Isern,E.Garcı´a-Moreno Grup de Tecnologia Electro`nica,Universitat de les Illes Balears,Ctra.Valldemossa,km.7.5,07122Palma de Mallorca,Spain Received 15November 2002;accepted 8April 2003AbstractIn this paper,we present a built-in current sensor to test operational amplifiers that takes advantage of previous results where the negativesupply current has been taken as the test observable using the Oscillation-test technique.The sensor is applied to a variable-length chain of OTAs considering an exhaustive analysis of catastrophic defects (opens,shorts),Gate Oxide Short and Floating Gate defects.We analyse the sensitivity of both frequency and amplitude of the current consumption.Results show that the proposed sensor provides 97%fault coverage,as the previous results suggested.q 2003Elsevier Ltd.All rights reserved.Keywords:Current sensor;Oscillation-test-technique;Operational transconductance amplifier;Fault models;Built-in current sensor1.IntroductionThe growing use of analog blocks within IC,combined with the ever-reducing technology sizes,has been motivating the development of several approaches for testing these analog sections embedded in digital systems [1–3].One of the more promising techniques is the oscillation test strategy,OTS (also known as oscillation-based test,OBT)[4–7].The central idea of this technique is to convert the circuit under test (CUT)into an oscillator during the test mode.This is accomplished by adding a feedback block to the CUT and activating it in the test mode to induce self-sustained oscillations,using a convenient starting set-up.It has been reported that the presence of defects affects the oscillation frequency [4],and so it can be used to distinguish between faulty and defect-free circuits.Most of the results reported for this technique use the output voltage as the test observable [4–7].It is a well known fact that current has been shown to be a very effective test observable not only for digital circuits [8–11],but also for analog ones [12,13].In Ref.[14],OTS was used to detect the defects in a two-stageoperational transconductance amplifier (OTA).In that work,a comparison of merits between supply current and output voltage as test observables was performed.The results showed that the maximum fault coverage was achieved when the peak value of the negative supply current was used as the test observable.Thus,the next logical step seems to be the implementation of a current sensor to test the CUT when using OTS.An on-chip sensor would be preferable to an off-chip sensor due to the best signal-to-noise ratio that can be achieved,as well as for its greater speed.However,it has the drawback of an extra area consumption.This problem can be alleviated by using a sensor that can be configured to monitor several analog blocks.The test structure proposed here is based on sequentially testing structures formed by one,two and three blocks of three OTAs each.Hence,as many OpAmps as desired can be tested in a simultaneous way just by adapting the sensor,as explained in this work.The rest of the paper is organized as follows.Section 2presents an overview of the OTS.Section 3provides us with the needed DFT modifications.Section 4explains the proposed Built-In Current Sensor (BICS).Section 5presents the results obtained with the sensor and,finally,main conclusions are highlighted in the last section.0026-2692/03/$-see front matter q 2003Elsevier Ltd.All rights reserved.doi:10.1016/S0026-2692(03)00158-7Microelectronics Journal 34(2003)919–926/locate/mejo*Corresponding author.Tel.:þ34-971-173-227,fax:þ34-971-173-426.E-mail address:vdfsjfr0@uib.es (J.Font).2.Oscillation-test strategy overviewFig.1shows the block diagram of a generic oscillation-test strategy.OTS consists of adding an external circuitry to the CUT to convert it an oscillator,whose oscillating frequency depends upon the external components of the feedback block,as well as on internal components of the CUT.Any fault will potentially manifest itself by deviating the oscillation frequency from its nominal value,even in most cases causing loss of oscillation.Therefore,that deviation may be employed to detect the fault [4].The oscillation frequency of the output voltage has not been the only parameter considered to detect a hard fault of the CUT.OBT was applied in Ref.[6]to two parameters of the test signal:frequency and amplitude.The integration of the output voltage provided test information of the former parameters.In Ref.[14],it was proposed to test an OTA by monitoring,in addition to the output voltage,another test signal:the supply current.Moreover,additional parameters of both output voltage V o ðt Þand supply current I ss ðt Þwere measured,such as the oscillating frequency,amplitude (or peak-to-peak value),peak value and average value over a period of time (DC value).For each parameter it was determined a tolerance band due to design and technol-ogy tolerances and power supply fluctuations.This tolerance band,which is the threshold to discriminate between good and faulty circuits,was calculated from a Monte Carlo analysis.It has been demonstrated in Ref.[14]that the optimal choice of parameters to test the OTA is to measure the maximum peak of the supply current.Since we have to determine whether the peak current falls inside or outside the tolerance band,the current sensor has to contain a window comparator as the pass/fail stage.3.Design for testability (DFT)In order to make the circuit testable,the designer must take into account the necessary modifications in the original design.There are two kinds of modifications.The first ones concern the changes at each OTA,while the second kind of modifications are related to the external feedback network.3.1.Reconfigurable OpAmpThe modifications the designer needs to introduce into each OTA are summarized in Fig.2.The control block (Ctrl block)allows the following possibilities.In normal mode ðon =off ¼0Þ;V fext_1and V fext_2are connected to the inverting and non-inverting inputs of the OTA,respectively.In test mode ðon =off ¼1Þ;the OTA has to be isolated from the rest of the circuit.Now,two different cases for the inputs in test mode are considered.The first case ðc =f ¼1Þcorresponds to the first OTA of the chain,which is set as a level comparator with a voltage reference,with no feedback.The second case ðc =f ¼0Þconcerns the remaining OTAs,which are set in a gain-one follower configuration.3.2.Feedback networkAs it has been mentioned before,the goal is to use the OTS to test a chain of OTAs (Fig.3).We have considered a chain composed of three blocks,where each block is made of three OTAs.Depending on the control signals S 1;S 2we force oscillations in one,two or three blocks.This is carried out by setting the first OpAmp as a comparator and the rest of the chain as cascaded followers connected to a RC network at the end.4.Proposed built-in current sensorThis section is devoted to describe the structure of the current sensor (Fig.4).First,the basichigh-performanceFig.1.Oscillation test strategy of a testablecircuit.Fig.2.DFT reconfigurable OpAmp.J.Font et al./Microelectronics Journal 34(2003)919–926920sensor is presented,and then it is shown how this sensor can be used with a variable current level.4.1.High-performance sensorThe proposed sensor (Fig.4)is based on a push–pull OTA in a feedback configuration and a controllable sensing resistance.Usually,the current sensing is done by measuring the voltage drop across a passive element [8,15],thus making it difficult to scale if a high-range measurement is desired.Also,process variations (as high as a 20%in some cases)make it difficult to perform an accurate measurement.By contrast,the sensor proposed here uses MOS transistors as the sensing element.These transistors are part of a feedback system,along with an OTA.This feedback improves parameter stability against process variations,thus allowing us a greater accuracy than stand-alone passive elements.The use of transistors also allows us to easily scale the circuit by changing its sensing resistance.The biasing stage of the OTA is represented by MR1and MR2,which set the reference voltage V ref :In the normal mode,the voltage reference V ref is set to V DD ;thus effectively switching off the sensor.Transistors M1–M9form a basic OTA in a push–pull configuration.The current of the CUT (our test observable)flows through MS1-MS2-(MSi),causing a small voltage drop V in ;which is sensed at the gate of M2.The MS i s also mirror the current through M5,providing an amplified copy of our test observable.The Ctrl block turns on/off one or more of the transistors (MS1…MSi)depending on its inputs S 1…S n :At the output of the OTA a scaled copy of the current consumption of the CUT is obtained.Both this current or the output voltage (Vout)can be used as the sensor output.In the case presented here,only two sensing transistors are used (MS1and MS2),with four possible test configurations including sensor switch-off.4.2.Controllable sensing resistanceControllable sensing resistance is a valuable add-on for current testing,because of the high rangeofFig.3.Reconfigurable Phase Shift Oscillator composed by either three,six or nineOpAmps.Fig.4.Schematics of the proposed BICS,including controllable sensing resistance.J.Font et al./Microelectronics Journal 34(2003)919–926921variability of the probing current signals for test.This controllable sensing resistance allows us a greater flexibility to measure different ranges of current and we can also fine-trigger the threshold to account for process variation.Moreover,it makes possible to test more than one simple device with the same sensor,thus saving silicon area.In this proposed circuit,the sensing resistance is implemented by using the transistors named MS1-MS2in Fig.4.The size of these transistors has to be chosen for the different incoming test current levels,keeping in mind two facts:(1)the transistors are to be in the ohmic region ðV in ,V g -V th Þ;and (2)voltage drop ðV in Þhas to be minimized.Control of the sensing resistance is performed by connecting the gate of MSi to V g (in the case that S x ¼1)or to V DD (when S x ¼0).As a special case,if all the S x are zero the sensor is switched off.In this case all the gates of MS x are connected to V DD to allow the CUT to function with the minimum possible performance degradation in normal mode.All possible control cases for our CUT are shown in Table 1.5.Results 5.1.Fault modelsIn this work,we have injected an exhaustive list of faults into the netlist extracted from the OTA layout to evaluate the merits of the test method proposed.As the defects introduced are catastrophic,loss of oscillation is expected in most cases.The schematics of the operational amplifier used in the simulations is shown in Fig.5.Its netlist has been obtained from the first release of analog and mixed-signal benchmark circuits [16]and it has been implemented in a 0.35m m technology.A short and an open at the drain/source of each MOS transistor have been simulated,as well as at each component of the compensating network.The hard open is simulated by adding a high resistance (R s ¼100M V )in series with the faulty component.The hard short is simulated as a very small resistor(R p ¼1V )in parallel with the component to be faulted.The total number of hard faults in our two-stage compensated OpAmp is 21:two times the total number of internal components (9MOS devices plus the resistor and the compensating capacitor)minus one,because the open at R c is the same one as that at C c :Moreover,MOS floating gate defects modelled with a zero value current source have been introduced (Fig.6)for HSPICE simulations,as proposed in Ref.[17].We get HSPICE convergence and starting-up DC continuity by imposing an initial gate voltage of 0V.This fault model fulfils two necessary conditions for this defect:first,we force current to be zero,and second,we assure voltage discontinuity between the terminals of the null-current source.We simulate the presence of Gate Oxide Shorts (GOS)defects by using the electrical model des-cribed in Ref.[18].In this unidimensional model two parameters are used to describe the defect.The first parameter models the oxide short position withinTable 1Gate voltage for the transistors MS2and MS1for the four possible control states S 2S 1Gate voltage Sensor stateMS2MS100Vdd Vdd OFF 01Gnd Vg ON 10Vg Gnd ON 11VgVgON Fig.6.Floating gate model,with zero initial gatevoltage.Fig.5.Schematics of the OTA under test.J.Font et al./Microelectronics Journal 34(2003)919–926922the device along the transistor length,since it was shown that the width positions for a given length can be modelled through the second parameter.The GOS position is modelled through the parameter a;that takes a value between0(a gate-source oxide short)and 1(gate-drain oxide short).Any value of a between0 and1corresponds to a short between the gate and the channel.The second parameter of the model in Ref.[18]describes the effective resistance of the oxide short and is physically related to the defect size and conductive properties.It was also shown that this parameter can be used to model the defect position along the transistor width,thus compacting the defect model parameters.This second parameter is called R s as it is an effective resistance.Fig.7shows the equivalent electrical model for a MOS transistor with a GOS defect.It is composed of two transistors connected in series,with a resistor R s between the gate and their connection.The size of each device is modified by means of the parameter a;such that if the original fault free device has a length L;then in the faulty device the original transistor is splitted into two minor devices Na and Nb of length a L andð12aÞL for Na and Nb, respectively.Note that if the defect is a gate-source oxide short,then a¼0and the defect is simply a resistance between the gate and the source.In this paper,we have modelled the presence of a GOS with a¼0:5and R s¼1V in each device.Since we have been using the actual layout,some additional assumptions should be made for each kind of the previously listed defects.Actually,since each transistor from the schematics(Fig.5)is divided into smaller transistors in the layout(hereafter referred to as minor transistors),the real number of potential faults increases dramatically.For instance,M9is composed by a number of minor transistors in series,while all the others consist of a number of minor transistors in parallel.As far as opens and floats are concerned,we are only considering hard faults in the lines between transistor blocks,not considering probable defects for each minor transistor.In that way,we are opening all the minor transistors or injecting zero current to all the gates of the transistor block.On the other hand, the shorts at the transistor and the shorts at the minor transistors are equivalent.Regarding GOS defects,we also have to assume that the transistors are splitted into smaller ones.In this case,we simulated only a GOS in one of the minor transistors by using the model described before.It can be shown that,as all minor transistors are equivalent,an a¼0:5and R s¼1V GOS in a minor transistor has the same effect that an a¼0:5GOS in any other minor transistor.5.2.Description of the CUTResults have been generated by using a CUT composed by three blocks of three OTAs each,as shown in Fig.3.The control signals S1and S2select one of the four possibilities,as has been specified in Table2.The operational amplifiers have been configured as a multiple OpAmp phase-shift oscillator based on 3,6or9OpAmps,depending on the control signals. The oscillation frequency of the fault-free CUT depends on the number of OpAmps and the feedback network time constant RC.This frequency decreases when either the number of OpAmps or the product RC increases.For a resistor R¼2K V and a capacitor C¼0:5pF, the negative supply current(indicated as power consump-tion in Table2and Fig.8)for a CUT of three OpAmps has been found to present a mean of0.92mA(0.18mA peak to peak).For a CUT of six OpAmps,the mean current was 1.7mA(1.04mA peak to peak),and 2.7mA(0.8mA peak to peak)for a CUT of nine OpAmps.The degradation induced by the sensor has been made smaller than5%by taking length L¼0:5m m and widths of W1¼300and W2¼600m m for the transistors MS1and MS2,respectively.As far as the ground voltage errorðV inÞdue to the sensor is concerned,we obtain an oscillating voltage of margin[16mV,25mV](Fig.9),which represents a maximum virtual ground level raise(respect to ground level)of less than1%with respect to the supply voltage(3.3V).If we compute the equivalent sensing resistance of both MS1and MS2transistors,working in the linear zone,for the three different CUT configurations,we obtain that the maximum input voltage(virtual ground level V in of the CUT)of our sensor through the above transistors isalways Fig.7.GOS electrical model.Table2Current consumption for the three blocks of OTAs without sensorS2S1#of OpAmps Includedin the CUT Power consumption of each CUT without sensor(mA)00Sensor off–0130.92mA106 1.70mA119 2.7mAJ.Font et al./Microelectronics Journal34(2003)919–926923the same.For a CUT of three,six and nine OpAmps,the equivalent resistance are 62,31and 21V ,for S 1S 2¼01,10,and 11,respectively.5.3.Fault coverageTo evaluate the fault coverage of the proposed sensor when using the oscillation-test technique for a set of OpAmps configured as a phase-shift oscillator,an exhaustive set of faults (opens,shorts,floating gates and GOS defects)has been analyzed.The faults have been injected in the extracted layout of each OTA under test,considering the assumptions made in Section 5.1.We have verified that any open,short,or floating gate defect in any of the OpAmps configured as followers (in the OpAmp-chain,all the OpAmps except the first one)impacts our test observable in a similar way.In other words,except in the first OpAmp of the chain (set up as a comparator),the effect of the same fault is similar in any OTA.So,for our purposes,it should be sufficient to simulate defects in the first OpAmp and in any other one of the chain.Once this assumption is made,the results of testing the three-OpAmp CUT can be extended to the other CUT schemes of six and nine OTAs.For the sake of simplicity and comprehension upon calculating the fault coverage,we have only counted nine GOS defects for each OpAmp,one GOS defect at only one minor transistor of each transistor.The output voltage of the sensor ðV out Þis shown in Fig.10for the fault-free case and for some faults.The fault simulation results for our CUT are presented in Table 3.The only undetected fault has been the short at the compensating resistor R c :Indeed,it seems reasonable as the short at the compensating resistor hardly changes the effect of the compensating network on the supply current.The other faults can be detected by using either peak-to-peak value of the observable or its oscillating frequency.By simultaneously observing these two parameters,a fault coverage greater than 97%is achieved.Otherwise,a 93%is obtained by observing only the peak-to-peak value and a 95%by observing the oscillatingfrequency.Fig.8.Current Consumption for Phase-Shift Oscillator in the cases with three,six and nine OpAmps.J.Font et al./Microelectronics Journal 34(2003)919–926924Fig.10.Sensor Output Voltage for the fault-free,open at M9located at OTA3,floating gate of M7in OTA2,short at M1in OTA1and short at M3inOTA1.Fig.9.Virtual Ground Level (Vin)raise for the CUT with the sensor activated in the cases with three,six and nine OpAmps.J.Font et al./Microelectronics Journal 34(2003)919–9269256.ConclusionsAn innovative BICS adaptable to different current ranges has been presented in this work with very good performance.This BICS,composed by an OTA and a controllable sensing resistance,has shown itself as a reliable I-V converter for our test observable (negative power supply current,I ss ).The output voltage of the sensor provides us a scaled copy of I ss ;where the scale factor is a function of the design parameters of the sensor and two control signals.A fault coverage greater than 97%can be achieved by applying OTS to a chain of three operational amplifiers configured as a phase-shift oscillator.Also,the area overhead is small and depends upon the number of OTAs in the oscillator:the greater the number of OTAs is,the smaller the area overhead will be.As it has been stated before,the fault coverage of opens,shorts and floating gates can be extended to chains of more OpAmps.By contrast,for three OpAmps,it has been found out that the behaviour of a GOS defect is different depending at which OTA the defect is located,so results obtained for three OpAmps cannot be extended.This way,further work should be devoted to GOS defects for chains longer than three OpAmps.References[1]C.Chalk,M.Zwolinski,Design for test technique for increasing theresolution of supply current monitoring in analog circuits,Electron.Lett.33(21)(1997)1746–1747.[2]D.Papakostas,A.Hatzopulos,Supply current testing in linear bipolarICs,Electron.Lett.30(2)(1994)128–130.[3]Eckersall,Erighton,et al.,Testing mixed signal ASICs through theuse of supply current monitoring,Proc.Eur.Test Conf.(1993)385–391.[4]K.Arabi,B.Kaminska,Design for testability of embedded integratedoperational amplifiers,IEEE J.Solid-State Circuits 33(4)(1998)573–581.[5]G.Huertas,D.Va´zquez,A.Rueda,J.L.Huertas,Oscillation-based test,Proc.IEEE VLSI India January (2000).[6]G.Huertas,D.Va´zquez,A.Rueda,J.L.Huertas,A practical method for reading test outcomes in oscillation-based test,Proc.Sixth IEEE Int.Mixed Signal Test.Workshop June (2000).[7]G.Huertas,D.Va´zquez,A.Rueda,J.L.Huertas,Effective oscillation-based test for application to a DMTF filter bank,Int.Test Conf.(1999)549–555.[8]B.Alorda,B.Bloechel,A.Keshavarzi,J.Segura,Transient currentoff-chip sensor circuit for digital IC production testing,Electron.Lett.38(18)(2002)1028–1029.[9]R.Picos,M.Roca, E.Isern,J.Segura, E.Garcı´a-Moreno,Experimental results on BIC sensors for transient current testing,J.Electr.Test:Theory Appl.16(2000)235–241.[10]ler,IDDQ testing in deep submicron integrated circuits,Proceedings of ITC99,IEEE Press,Piscataway,NJ,1999,pp.724–729.[11]Z.Chen,L.Wei,A.Keshavarzi,K.Roy,IDDQ testing for deep-submicron ICs:challenges and solutions,IEEE Des.Test Comput.March–April (2002)24–33.[12]J.Font,J.Ginard,E.Isern,M.Roca,J.Segura,E.Garcı´a-Moreno,A BICS for CMOS OpAmps by monitoring the supply current peaks,Proc.of Eighth IEEE On-line test workshop,France July (2002)94–98.[13]J.Font,J.Ginard,E.Isern,M.Roca,E.Garcı´a,Oscillation-test technique for CMOS OpAmps by monitoring supply current,DCIS 2001November (2001)167–172.[14]J.Font,J.Ginard,E.Isern,M.Roca,J.Segura,E.Garcı´a,Voltage and current testing of CMOS operational amplifiers by using the oscillation-test technique,IMSTW 02,Montreaux,Switzerland June (2002).[15]S.Dragic,I.Filanovsky,M.Margala,Low-voltage analog currentdetector supporting at-speed BIST,Proc.ISCAS 02,Scottsdale,Arizona May (2002)I-593–I-596.[16]B.Kaminska,et al.,Analog and Mixed-Signal Benchmark Circuits-First Release,International Test Conference,1997,pp.183–190./research/mad/benchmarks/benchmarks.html[17]A.M.Brossa,J.Figueras,Characterization of floating gate defects inanalog cells,ETW 99(1999)160–164.[18]J.Segura,C.De Benito,A.Rubio,J.F.Hawkins,A detailed analysisand electrical modeling of gate oxide shorts in MOS transistors,J.Electron.Test.:Theory Appl.8(1996)229–239.Table 3Fault coverage for the different kinds of defects in the three-OTA phase-shift oscillator FaultsPeak-to-peak Frequency Peak-to-peak &frequency Faultcoverage (%)Shorts (11£3)30303091Opens (10£3)303030100Floats(9£3)272727100GOS (9£3)222427100Fault coverage (%)939597J.Font et al./Microelectronics Journal 34(2003)919–926926。