vga显示实验报告

实验9 VGA显示控制器实验

实验9 VGA显示控制器实验1、实验目的:1)理解VGA显示的基本原理。

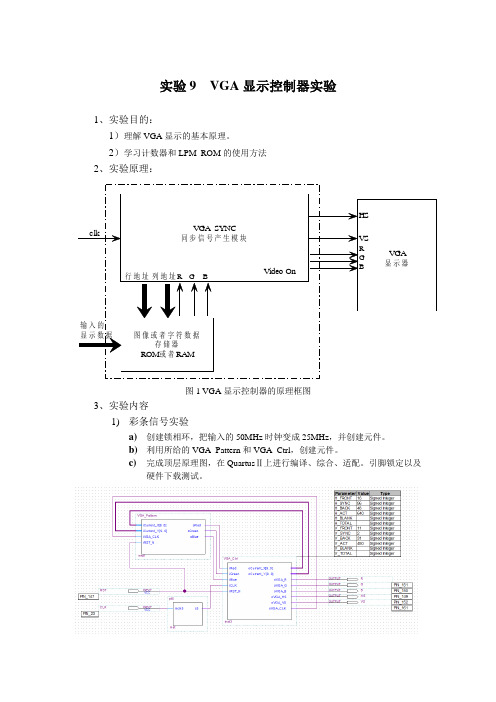

2)学习计数器和LPM_ROM的使用方法2、实验原理:图1 VGA显示控制器的原理框图3、实验内容1)彩条信号实验a)创建锁相环,把输入的50MHz时钟变成25MHz,并创建元件。

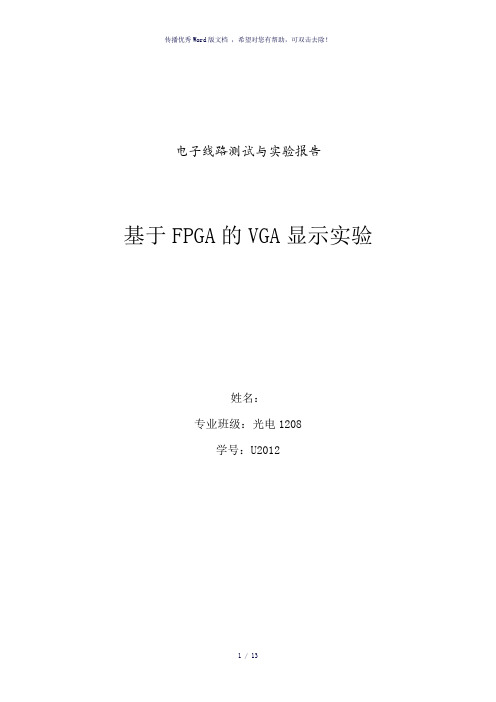

b)利用所给的VGA_Pattern和VGA_Ctrl,创建元件。

c)完成顶层原理图,在QuartusⅡ上进行编译、综合、适配。

引脚锁定以及硬件下载测试。

2)显示自己的姓实验。

修改VGA_Pattern,利用if语句控制相应区域的相应值,在QuartusⅡ上进行编译、综合、适配。

引脚锁定以及硬件下载测试。

3)显示数字实验a)创建lpm_rom,手动输入“0”的mif文件。

b)顶层文件为numTop.v,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

4)计数显示实验a)创建“1~9”的lpm_rom,mif文件已给出。

b)加入计数器。

c)完成顶层文件,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

5)数字钟实验在4)基础上加入位置控制,完成顶层文件,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

6)显示理工校徽实验(2)moduleVGA_Pattern(//HostSideoRed,oGreen,oBlue,iCurrent_X,iCurrent_Y,iVGA_CLK,iRST_N); // Host Sideoutput reg oRed;output reg oGreen;output reg oBlue;input [9:0] i Current_X;input [9:0] i Current_Y;// Control Signalinput iVGA_CLK;input iRST_N;always@(posedge iVGA_CLK or negedge iRST_N)beginif(!iRST_N)beginoRed <= 0;oGreen <= 0;oBlue <= 0;endelsebeginif((( iCurrent_Y>60)&& (iCurrent_Y <80))&&((iCurrent_X>200)&&(iCurrent_X <400)))beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelse if((( iCurrent_Y>80)&& (iCurrent_Y <240))&&((iCurrent_X>200)&&(iCurrent_X <240)))beginoRed <= 1;oGreen <= 0;oBlue <= 0;end/*else if((( iCurrent_Y>150)&& (iCurrent_Y <170))&&((iCurrent_X>260)&&(iCurrent_X <340)))/*else if((150 < iCurrent_Y < 170)&&(260<iCurrent_X < 340))beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelse if((( iCurrent_Y>170)&& (iCurrent_Y <240))&&((iCurrent_X>290)&&(iCurrent_X <310)))/*else if((170 < iCurrent_Y < 240)&&(290 < iCurrent_X < 310))beginoRed <= 1;oGreen <= 0;oBlue <= 0;end*/else if((( iCurrent_Y>240)&& (iCurrent_Y <260))&&((iCurrent_X>200)&&(iCurrent_X <400)))/*else if((240 < iCurrent_Y < 260)&&(150 < iCurrent_X < 450))*/beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelsebeginoRed <= 0;oGreen <= 0;oBlue <= 0;endendendendmodule(3)(4)module numTop1(CLK,RST,R,G,B,HS,VS); input CLK,RST;output R,G,B,HS,VS;wire clk25Mhz,vga_clk;wire [9:0]ram_data;wire [9:0] X,Y;wire [6:0] ram_addr;wire [3:0]COUNT;wire carry1;wire CLK1HZ;reg vga_data;assign ram_addr = {Y[5:2],X[4:2]};altPLL0 u1(CLK,clk25Mhz);VGA_Ctrl u2(.iRed(vga_data),.iGreen(vga_data),.iBlue(vga_data),.oCurrent_X(X),.oCurrent_Y(Y),// VGA Side.oVGA_R(R),.oVGA_G(G),.oVGA_B(B),.oVGA_HS(HS),.oVGA_VS(VS),.oVGA_CLK(vga_clk),// Control Signal.iCLK(clk25Mhz),.iRST_N(RST) ); demo_shuzi u17(ram_addr,vga_clk,ram_data[0]); ROM1 u21(ram_addr,vga_clk,ram_data[1]);ROM2 u14(ram_addr,vga_clk,ram_data[2]);ROM3 u15(ram_addr,vga_clk,ram_data[3]);ROM4 u6(ram_addr,vga_clk,ram_data[4]);ROM5 u7(ram_addr,vga_clk,ram_data[5]);ROM6 u8(ram_addr,vga_clk,ram_data[6]);ROM7 u9(ram_addr,vga_clk,ram_data[7]);ROM8 u10(ram_addr,vga_clk,ram_data[8]);ROM9 u11(ram_addr,vga_clk,ram_data[9]);/*demo_shuzi u3(ram_addr,vga_clk,ram_data);*/ GeneralCnt #(4,9) u4(CLK1HZ,RST,1,COUNT,carry1); ClkDiv #(26,50000000) u5(CLK,RST,CLK1HZ);always@(X,Y)if(X<32 && Y<64)vga_data=ram_data[COUNT];else if(X<64 && Y<64)vga_data=ram_data[COUNT];elsevga_data=0;endmodule//任意倍整数分频器module ClkDiv(clk_in,rst_n,clk_out);parameter MSB = 4, DIV_TIMES = 10;input clk_in,rst_n;output clk_out;reg clk_out;reg [MSB-1:0] count;always @(negedge rst_n or posedge clk_in)beginif(rst_n==0)begincount<=0;endelsebeginif(count < (DIV_TIMES-1))count<=count+1'b1;elsecount<=0;endendalways @(negedge rst_n or posedge clk_in) beginif(rst_n==0)beginclk_out<=1'b0;endelsebeginif(count<(DIV_TIMES>>1))clk_out<=1'b0;elseclk_out<=1'b1;endendendmodule//通用计数器module GeneralCnt(clk,reset_n,ena,cnt,carry_out);parameter MSB = 4, CNT_END = 9; input clk;input reset_n;input ena;output [MSB-1:0]cnt;output carry_out;reg [MSB-1:0]cnt;reg carry_out;//计数always@(posedge clk or negedge reset_n) beginif(!reset_n)cnt <= 0;else if(ena && cnt==CNT_END)cnt <= 0;else if (ena && cnt < CNT_END)cnt <= cnt + 1'b1;end//产生进位输出always@(posedge clk or negedge reset_n) begin if(!reset_n)carry_out <= 1'b0;else if(ena && cnt==CNT_END)carry_out <= 1'b1;elsecarry_out <= 1'b0;endendmodule。

华科基于FPGA的VGA显示实验

电子线路测试与实验报告基于FPGA的VGA显示实验姓名:专业班级:光电1208学号:U2012一、实验要求功能要求:利用Basys2实验板实现图片在VGA接口显示器上的显示。

基本要求:1)实现240*160以上像素的图片在VGA接口显示器上的显示;2)利用算法实现特定图片在VGA接口显示器上的放大、缩小旋转及其他动作的自动变换。

二、实验具体目标1.首先实现特定图片在显示器上的显示;2.图片自动旋转90度;3.实现图片的放大与缩小,同样通过一个按键实现;4.添加复位键,按下复位键后图片返回最初的状态。

三、实验原理1.VGA的显示原理在基于FPGA的VGA控制中,只需考虑行同步信号(HS),场同步信号(VS),以及红绿蓝三基色(R、G、B)这五个信号,即可实现对VGA显示的控制。

2.对图片的旋转与缩放操作对图片的旋转操作在本质上是对IP核ROM的输入地址addr进行变换的过程。

在这里,假定显示的坐标分别为x_vdn以及y_vdn,由于图片是160*40的,在正常的显示时,addr 与x_vdn以及y_vdn的对应关系应该为:addr=x_vdn+y_vdn*160即依次取像素点,图片正常显示。

要把图片顺时针旋转90度,那么相当于显示的图片是40*160的,重新考虑addr与两个坐标之间映射关系。

容易得到,此时:addr=(39-x_vdn)*160+y_vd对图片的缩放操作对图片的缩放操作则只考虑以下两种变化,即放大一倍,此时图片的大小为320*80;缩小一倍,此时图片的大小为80*20。

对于图片的放大一倍,则要考虑不同的像素点对显示信号的共用(在这里即为m信号)。

由通常的规则,按照顺序,构成一个正方形的每四个相邻的像素点共用一个m信号。

同时,在这里对x_vdn以及y_vdn的最后一位判断,并且形成不同的映射规则。

具体的映射规则在源代码中给出。

对于图片的缩小,则相对简单的多。

此时的映射关系为:addr=y_vdn*320+x_vdn*2;3.工程结构与解读如图,下图为系统的结构框图。

实验十 基于ROM的VGA显示

实验十基于ROM的VGA显示一、实验目的1.进一步掌握VGA显示器的工作时序及其控制电路的工作原理。

2.熟悉和掌握基于ROM的VGA显示原理以及ROM的使用方法。

3.培养分析系统、进行模块设计及独立解决实际问题的能力。

二、预习要求1.认真阅读实验指导,了解ROM的两种创建方法,以及利用BmpToMif软件从BMP格式图片生成MIF文件的方法。

2.掌握图像显示位置与寻址ROM的地址信号的映射方法。

3.用Verilog HDL语言编写代码并进行时序仿真。

三、实验内容1.设计VGA显示器的控制电路,使之控制显示器,完成相应的图形显示功能。

(1)用ROM实现重复图案的显示将指定的小尺寸图片(如80×60)在全屏幕范围内重复输出。

(2)在屏幕指定位置显示文字图像(3)实现简单的动画显示在屏幕上分时循环显示多幅指定图像,产生动画效果。

2.利用GW48 SOPC+实验开发系统实现设计的编程下载。

示例如图2. 1所示。

(a)重复图案的显示 (b)在指定位置显示文字图像 (c)简单的动画显示图2. 1 各种图形显示效果四、实验原理1.VGA显示原理(参见实验“VGA显示器的控制电路”)2.基于ROM的VGA显示原理基于ROM的VGA显示系统原理框图如图2. 2所示。

系统由4部分组成。

图2. 2 基于ROM的VGA显示系统原理框图VGA扫描核:提供符合VGA显示器标准的行同步和场同步信号,可以借鉴“VGA显示器的控制电路”实验中的vgacore模块。

地址转换函数:接收行列信号作为输入,以相同或不同映射关系输出寻址ROM的地址信号,以确定欲显示图像的颜色值。

ROM图形集合:由多块ROM组成,分别接收地址转换函数输出的地址信号,输出符合各种图形的RGB信号。

动态显示控制逻辑:监控时钟或其他信号量,根据控制逻辑,选择RGB信号组中的一组输出给显示器。

显示器接收行同步和场同步信号(h_sync、v_sync)及RGB颜色信号,输出稳定图像。

实验一 VGA显示模式的实现

实验报告(报告要存档,请单面打印)姓名陈梓杰学号201131120207 专业电子信息科学与技术班级2班一、设计/实验项目名称:VGA显示模式的实现基本内容描述:多功能计数器具有异步清零、同步使能功能,计数满12进位,进位位输出高电平。

清零端RST;使能端EN;进位输出COUT。

二、电路设计及原理多功能计数器VHDL程序如下所示:生成RTL电路图如下:多功能计数器实现12进制异步清零、同步使能功能。

异步清零RST、同步使能EN接按键,低电平触发有效。

在时钟上升沿,计数器计数到11时,计数器自动清零,开始下一个计数。

当异步清零RST为‘0’时,输出端DOUT218输出为“0000”,即异步清零RST为低电平时有效;否则,如果在上升沿时钟和同步计数使能ENA有效(ENA=‘1’)时,允许计数。

当计数达到“1011”时,表明已经达到12进制的最大值,向进位端COUT输出一个高电平,在下一个上升沿来到的时候,计数将清零,并重新开始计数。

另一种情况就是,当时钟为上升沿而同步计数使能ENA却无效(ENA=‘0’)时,计数功能是不允许的。

三、设计电路仿真与分析多功能计数器仿真图如下所示:由仿真图可看出,当RST和ENA同时为高电平时,允许计数,对时钟CLK的上升沿进行计数。

当计数到12进制的最大值(图中对应为“1011”)时,COUT端将输出一个高电平,表示有进位。

下一个上升沿到来时,计数将清零。

当RST为低电平时,计数清零,不依赖于上升沿时钟。

当ENA为低电平时,不允许计数,输出值保持不变,直到ENA为高电平时继续计数。

四、SIGNALTAP II硬件信号的采集与分析仿真分析通过后,将设计方案下载到FPGA中,通过SIGNALTAP II对多功能计数器进行采集,采集波形如下图所示:五、实验结论由仿真试验可知:(1)设计功能正确,实现4位12进制计数器的功能;(2)异步清零信号为低电平有效,同步使能ENA要保持高电平时才允许计数;(3)当计数达到12进制的最大值时,进位端COUT会输出一个高电平。

VGA实现显示器条纹显示

深圳大学实验报告课程名称:基于VHDL编程的FPGA设计实验名称:VGA控制器设计实现显示器条纹显示学院:信息工程学院专业:电子信息工程班级:组号:指导教师:报告人:学号:实验时间:2012 年10 月31 日星期三实验地点南区N413实验报告提交时间:2012.11.11图1 VGA接口信号基本时序图仿真波形布局布线后的仿真波形:仿真波形实验结果:ASM图实验过程分析:一、代码分析I. 时钟配置分析。

像素时钟配置要求为25Mhz。

在程序代码中可以通过两种方式实现25Mhz配置的时钟,第一种是通过上学期EDA中所学的二分频思想;第二种则是调用IP Core的内部时钟。

II. 水平扫描周期与垂直扫描周期的分析。

通过时序分析图,以及参数表,分别读出了水平与垂直周期下的高低电平所占时钟的个数,并且成功在代码段上实现出来。

III.8位颜色数据的读取规则。

在FPGA板子的VAG接口上,若端口R9,T8,R8,N8,P8,P6,U5,U4分别对应8位数据的低位到高位,那么红色对应的代码是00000111,绿色对应的代码是00111000,蓝色对应的代码是11000000。

二、仿真分析一个水平扫描周期占800个时钟,一个垂直扫描周期占521线,即521*800个时钟。

在水平同步信号HS以及垂直同步信号VS均为高电平状态时,将有颜色数据输出。

代码实现60线将出现一种颜色,即共有8条水平颜色带均匀出现在屏幕上,风别为红,蓝,绿,蓝,红,绿,红,蓝。

实验心得总结:通过这一次的实验,可以说对于FPGA是首次从理论过度到实践中去。

从一开始的完全一头雾水到最后做到较为透彻的理解,这一过程十分不容易。

首先是分频器的书写,这是上一学期EDA的内容,但是要用时,总是忘记得一干二净,当然通过这次的实验,可以说再也不会忘记如何书写分频器了。

其次,就是关于扫描周期的时钟参数不懂得如何去读出来,如何在代码上对应上去,当然最终也是在问同学,问老师,解决了问题。

vga显示

学生实验报告实验课名称:VHDL硬件描述语言实验项目名称:VGA显示专业名称:电子科学与技术班级:32050801学号:3205080127学生姓名:柯斌教师姓名:程鸿亮2010年_11月 13日组别_____________________同组同学李福来实验日期2011年11月13日实验室名称成绩_____一、实验名称:VGA显示二、实验目的与要求:通过对VGA接口的显示控制设计,理解VGA接口的时序工作原理,掌握通过计数器产生时序控制信号的方法以及用MEGEFUNCTION制作锁相环的方法。

三、实验内容:通过VHDL编程,在VGA显示器上实现竖形彩条的显示,显示模式为640×480 60Hz刷新率。

四、实验条件:1. WindowsXP操作系统2. QuartusII EDA开发系统3. 杭州康芯SOPC硬件开发平台五、实验原理:注:由于RGB[2..0]输出的是数字量,所以只能够显示8种色彩。

640×480 60Hz显示模式的时序。

按照每秒60帧的刷新速度来计算,所需要的时钟频率为:频率=60H z(帧数)×525(行)×800(每一行像素数)=25.2MHz所以我们通过开发系统的10MHz时钟资源,利用FPGA上的锁相环产生25MHz的频率即可。

虽然没有达到精确的25.2MHz的时钟频率(刷新率可能会是59Hz),但是并不会造成影响。

六、源代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;------------entity color isport ( clk : in std_logic;vs,hs :out std_logic;rgb : out std_logic_vector( 2 downto 0));end color;---------------architecture behave of color issignal rgbs : std_logic_vector( 2 downto 0);signal h,v : std_logic;beginprocess(clk)variable h_count : integer range 0 to 800 :=0;variable v_count : integer range 0 to 525 :=0;beginif (clk'event and clk='1')thenif (h_count=800) thenh_count:=1;if (v_count=525)thenv_count:=1;else v_count:=v_count+1;end if;else h_count:=h_count+1;end if;if h_count>8 AND H_COUNT<104 thenh<='0';else h<='1';end if;if v_count=3 or v_count=4 thenv<='0';else v<='1';end if;if (v_count > 33) and (v_count < 518) thencase h_count iswhen 152 to 231 => rgbs <= "011";when 232 to 311 => rgbs <= "100";when 312 to 391 => rgbs <= "100";when 392 to 471 => rgbs <= "011";when 472 to 551 => rgbs <= "011";when 552 to 631 => rgbs <= "100";when 632 to 711 => rgbs <= "100";when 712 to 791 => rgbs <= "011";when others => rgbs <= "ZZZ";end case;else rgbs <= "ZZZ";end if;end if;rgb <= rgbs;vs <= v;hs <= h;end process;end behave;七、实验结果与分析:1,trl:2,block:3,实验效果图:八,讨论和回答问题及体会:1,显示器是人机交换的窗口,通过本实验的操作及代码书写,不再觉得液晶显示器多么的神秘,原来通过自己亲身操作也可以实现显示自己想要的画面,本次实验使用的是640*480分辨率的显示器。

VGA学号显示程序实验报告

本科学生设计性实验报告项目组长学号成员专业_班级实验项目名称VGA学号显示控制电路设计指导教师及职称___开课学期2011 至2012 学年下学期上课时间2012 年 6 月27 日一、实验设计方案实验名称:VGA学号显示控制电路设计实验时间:2012年6月27日小组合作:是○否●小组成员:1、实验目的:学习VGA学号显示控制电路设计2、实验场地及仪器、设备和材料:场地:枫林实验室W201仪器、设备:试验箱一台、电脑一台3、实验思路(实验内容、数据处理方法及实验步骤等):3.1 实验原理:常见的彩色显示器一般由CRT(阴极射线管)构成,彩色是由R(红),G(绿),B(蓝)3基色组成。

显示采用逐行扫描的方式,阴极射线枪发出的电子束打在涂有荧光粉的荧光屏上,产生RGB三色基,最后合成一个彩色图像。

从屏幕的左上方开始自左向右的扫描,每扫完一行电子束回到下一行的最左端,每行结束后电子枪回扫的过程中进行消隐。

然后从新开始行扫描,消隐,直到扫描到屏幕的右下方,电子书回到屏幕的左上方重新开始新的图像扫描,并且在回到屏幕的左上方过程中进行消隐,在消隐的过程中不发射电子束。

每一行扫描结束时,用HS(行同步)信号进行同步;扫描完所有的行后用VS(场同步)信号进行同步。

VGA显示器总共需要五根信号线,分别为R\G\B三原色信号和行同步(HSYNC)、场同步(VSYNC)信号。

在通用的标准中,VGA的像素输出频率为25.175 MHz,行频率是31.496 KHz,场频率是59.94 Hz。

分辨率为640*480,即每行显示640个像素,每场显示480行。

这640*480是显示器的有效显示区(Visible area),除此之外,还有行、场消隐区(Back Porch),以及行、场同步区(Sync Pulse)以实现行列的同步操作。

如果利用实验室的液晶屏,可以增加分辨率至800*600,在这个标准下屏幕的刷新频率设为72Hz,行频率是48.08KHz。

vga接口显示

VGA接口显示实验QinZhanAo1.实验内容电脑屏幕背景为白色,在电脑屏幕中间显示一个空心的矩形,矩形颜色为红色。

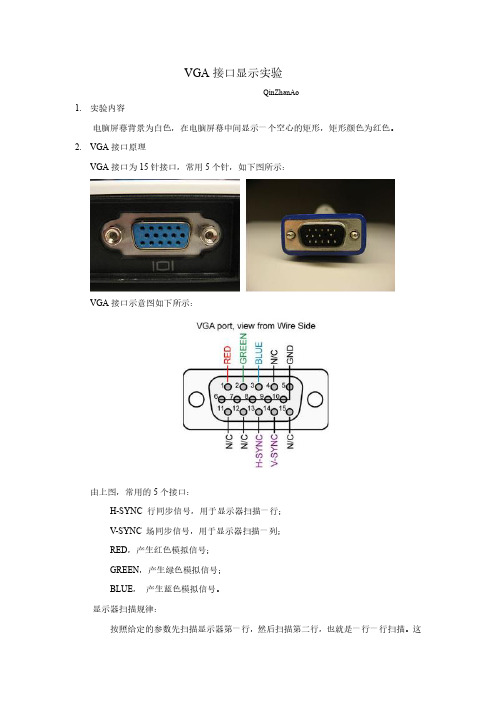

2.VGA接口原理VGA接口为15针接口,常用5个针,如下图所示:VGA接口示意图如下所示:由上图,常用的5个接口:H-SYNC 行同步信号,用于显示器扫描一行;V-SYNC 场同步信号,用于显示器扫描一列;RED,产生红色模拟信号;GREEN,产生绿色模拟信号;BLUE,产生蓝色模拟信号。

显示器扫描规律:按照给定的参数先扫描显示器第一行,然后扫描第二行,也就是一行一行扫描。

这里显然可以看出,在设计两个有效范围计数器时,场同步信号计数器是以行同步信号计数器为周期的。

显示器扫描参数如下表:本实验选择显示模式为800*600@60,需要注意的是时钟,也就是这里的40MHz是底线,驱动这一模式至少需要40MHz的时钟,板子上市50MHz,可以使用。

下面给出两个同步信号的时序图,并结合扫描参数表来进行说明。

行同步信号时序图如下图:场同步信号时序图如下图:800*600@60 模式:行同步信号上电拉高,在行同步计数为0时拉低Sync(a)个时间,即128个时钟周期,之后拉高,在行同步计数到1055时,行同步计数器清零,场同步计数器加1;场同步信号上电拉高,在场同步计数为0时拉低Sync(o)个时钟周期,场同步计数到627时清零。

参考显示器扫描参数表,需要注意的是,扫描有效范围只是800*600,也就是行的C段和列的Q段,给出RGB色值得范围必须在这里,也就是行计数在[216,1015],列计数在[27,626]。

3.调色RGB为光三原色,三原色全0为黑,全1为白,红色调配为R全1,其他两原色为0。

4.Verilog代码5.VCS仿真结果在标记处我们看到背景和矩形框的颜色配置是正确的。

6.上板测试结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VGA显示实验报告

●技术资料

对于普通的VGA 显示器,其引出线共含五个信号:●R、G、B:三基色信号。

●HS:行同步信号。

●VS:场同步信号。

VGA工业标准要求的频率:产生时钟频率25.175 MHz(像素输出的频率)行频31469 Hz 场频59.94 Hz(每秒图像刷新频率)

VGA显示的关键是行、场扫描时序的产生。

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

完成一行扫描的时间称为水平扫描时间,其倒数称为行频率;完成一帧(整屏)扫描的时间称为垂直扫描时间,其倒数称为场频率,即刷新一屏的频率,常见的有60Hz,75Hz等等。

标准的VGA显示的场频60Hz,行频31.5KHz。

行场消隐信号:是针对老式显像管的成像扫描电路而言的。

电子枪所发出的电子束从屏幕的左上角开始向右扫描,一行扫完需将电子束从右边移回到左边以便扫描第二行。

在移动期间就必须有一个信号加到电路上,使得电子束不能发出。

不然这个回扫线会破坏屏幕图像的。

这个阻止回扫线产生的信号就叫作消隐信号,场信号的消隐也是一个道理。

显示带宽:带宽指的显示器可以处理的频率范围。

如果是60Hz刷新频率的VGA,其带宽达640x480x60=18.4MHz,70Hz的刷新频率1024x768分辨率的SVGA,其带宽达1024x768x70=55.1MHz。

时钟频率:以640x480@59.94Hz(60Hz)为例,每场对应525个行周期(525=10+2+480+33),其中480为显示行。

每场有场同步信号,该脉冲宽度为2个行周期的负脉冲,每显示行包括800点时钟,其中640点为有效显示区,每一行有一个行同步信号,该脉冲宽度为96个点时钟。

由此可知:行频为525*59.94=31469Hz,需要点时钟频率:525*800*59.94约25MHz.

●字符显示原理

用液晶显示或者LED点阵屏,是用点阵的方式显示的,要显示汉字或字符的时候会用到字模,字模就是字在点阵上显示时对应的编码。

以字模的方式存储图形或者文字,每一个点都需要一个bit位来存储,该位为0代表该像素点不显示,为1代表显示。

这样,一个字节就可以存储8个像素点的显示情况。

一般采用宋体小四号的字符来做显示,这样一个英文字符刚好占8*16个像素;而汉字需要两倍,即16*16像素来显示一个汉字。

这样,存储一个英文字符每8个点需要1个字节存储,一共16行需要16个字节。

●核心代码

always @(CC or LL) begin

if (CC > 23) HS1=1'b0; else HS1=1'b1 ; // 行同步

if (LL > 479) VS1=1'b0; else VS1=1'b1 ; // 场同步

end

always @(lcount or LL) begin//lcount为当前X坐标,LL为当前Y坐标,两者确定一个像素点

GRBP = 0 ;

//规定一个长方形框架以显示字体

if(lcount>1 && lcount<376 && LL>1 && LL<479) GRBP = 3'b111;

if ((lcount > startX + offsetX)&&(LL > startY + offsetY)&&(lcount < startX + width + offsetX)&&(LL < startY + height + offsetY))

if (sss[16*(width - lcount + startX + offsetX)+(16 - LL + startY + offsetY)] == 1)

GRBP = 3'b000;

end

原理:if(lcount>1 && lcount<376 && LL>1 && LL<479) GRBP = 3'b111确定显示的背景框的大小,if (sss[16*(width - lcount + startX + offsetX)+(16 - LL + startY + offsetY)] == 1)

GRBP=3'b000;查找字模对应的位,如果为1,则显示出来。

●改进

可以用字库,显示大部分的汉字同时根据同样的原理,显示图片。