开关电源中MOSFET失效案例分析

MOSFET失效原因深度分析,附:失效预防措施

MOSFET失效原因深度分析,附:失效预防措施作为开关电源工程师,会经常碰到电源板上MOSFET无法正常工作,首先,要正确测试判断MOSFET是否失效,然后关键是要找到失效背后的原因,并避免再犯同样的错误,本文整理了常见的MOSFET 失效的几大原因,以及如何避免失效的具体措施。

用万用表简单检测MOS管是否完好测试MOS好坏用指针式万用表方便点,测试时选择欧姆R×10K 档,这时电压可达10.5V,红笔是负电位,黑笔是正电位。

测试步骤:MOS管的检测主要是判断MOS管漏电、短路、断路、放大。

其步骤如下:1、把红笔接到MOS的源极S上,黑笔接到MOS管的漏极上,好的表针指示应该是无穷大。

如果有阻值没被测MOS管有漏电现象。

2、用一只100KΩ-200KΩ的电阻连在栅极和源极上,然后把红笔接到MOS的源极S上,黑笔接到MOS管的漏极上,这时表针指示的值一般是0,这时是下电荷通过这个电阻对MOS管的栅极充电,产生栅极电场,由于电场产生导致导电沟道致使漏极和源极导通,故万用表指针偏转,偏转的角度大,放电性越好。

3、把连接栅极和源极的电阻移开,万用表红黑笔不变,如果移开电阻后表针慢慢逐步退回到高阻或无穷大,则MOS管漏电,不变则完好。

4、然后一根导线把MOS管的栅极和源极连接起来,如果指针立即返回无穷大,则MOS完好。

----------------------------MOSFET失效的六大原因1:雪崩失效(电压失效),也就是我们常说的漏源间的BVdss电压超过MOSFET的额定电压,并且超过达到了一定的能力从而导致MOSFET失效。

2:SOA失效(电流失效),既超出MOSFET安全工作区引起失效,分为Id超出器件规格失效以及Id过大,损耗过高器件长时间热积累而导致的失效。

3:体二极管失效:在桥式、LLC等有用到体二极管进行续流的拓扑结构中,由于体二极管遭受破坏而导致的失效。

4:谐振失效:在并联使用的过程中,栅极及电路寄生参数导致震荡引起的失效。

MOSFET的栅极失效分析

MOSFET的栅极失效分析摘要:随着MOSFET器件尺寸的减小和栅氧化层厚度的减薄,栅极失效变得愈发显著,对MOS器件和电路可靠性的影响也愈发严重,成为限制器件及电路寿命的主要因素之一。

本文从MOSFET的设计、封装、实际应用三方面来阐述MOSFET栅极失效的原因,同时提供几点解决方法。

关键词:MOSFET;栅极失效;封装1.引言MOSFET即金属-氧化物-半导体场效应晶体管,是一种用途广泛的电子器件。

MOSFET作为电压控制型器件,具有栅极输入阻抗高,驱动功率小,电流关断能力强,开关速度快,开关损耗小等优点,在功率电源、家用电器、无间断电源(UPS)和自动系统等方面应用广泛。

然而,MOSFET的栅氧在工艺设计中,会受到漏电流、导通电阻、功率损耗等参数的限制,导致MOSFET栅氧固有的脆弱性;此外,在封装制造过程中受到静电、应力、环境等因素的影响,也会对栅氧造成损坏,导致栅极失效,必须采取相应的制造控制措施,才能有效控制不良率,提升封装成品率。

2.MOSFET的栅氧层的限定栅极控制器件电流的开通和关断,多数用多晶硅材料制作而成,栅极下面就是栅氧化层,一般是SIO2,作为MOS的绝缘栅介质。

栅氧层厚度tox影响沟道电阻的大小()Cox=εs/tox,(ε介电常数)近而影响器件的功率损耗,从上式可以看出减小栅氧层厚度可以减小沟道电阻,减小功率损耗,但栅极氧化物击穿电压有一定的工业标准,厚度越小越容易发生击穿,导致栅极越容易失效;另一方面,高的tox则会导致大的功率损耗;因此栅氧厚度根据器件设计参数得到一个经验折中范围一般是1000埃-1500埃(1 Å =0.1nm)。

阈值电压V TH与衬底掺杂浓度和栅氧化层厚度有关,由下式可发现阈电压低的器件有可能导致栅氧层厚度低,越容易击穿。

此外,MOSFET工作当中的米勒电容Cgd引起米勒震荡造成高dv/dt,造成栅失效。

栅氧化层还会出现性能退化,其主要原因强电场使栅氧化层产生了漏电,漏电使的在氧化层中积蓄起很多电荷,导致氧化层击穿。

小贴士:开关电源中功率MOSFET管损坏模式及分析

小贴士:开关电源中功率MOSFET管损坏模式及分

析

本文将通过功率MOSFET管的工作特性,结合失效分析图片中不同的损坏形态,系统地分析过电流损坏和过电压损坏。

同时根据损坏位置不同,分析功率MOSFET管的失效发生在开通的过程中或发生在关断的过程中,从而为设计工程师提供一些依据,找到系统设计中的问题,提高电子系统的可靠性。

目前,功率MOSFET管广泛地应用于开关电源系统及其他功率电子电路中。

实际应用中,特别是在一些极端的边界条件下,如系统的输出短路及过载测试、输入过电压测试以及动态的老化测试中,功率MOSFET管有时候会发生失效损坏。

工程师将损坏的功率MOSFET管送到半导体原厂做失效分析后,分析报告的结论通常是过电性应力EOS,却无法判断是什幺原因导致MOSFET的损坏。

1 过电压和过电流测试电路

过电压测试的电路图如图1(a)所示,选用40 V的功率MOSFET:AON6240,DFN5?鄢6封装。

通过开关来控制,将60 V的电压直接加到AON6240的D极和S极,熔丝用来保护测试系统,功率MOSFET损坏后,将电源断开。

测试样品数量为5片。

过电流测试的电路图如图1(b)所示,选用40 V的功率MOSFET:AON6240,DFN5?鄢6封装。

首先合上开关A,用20 V的电源给大电容充电,电容C的容值为15 mF,然后断开开关A,合上开关B,将电容C的电压加到功率MOSFET管的D极和S极,使用信号发生器产生一个电压幅值。

MOSFET的失效模式分析

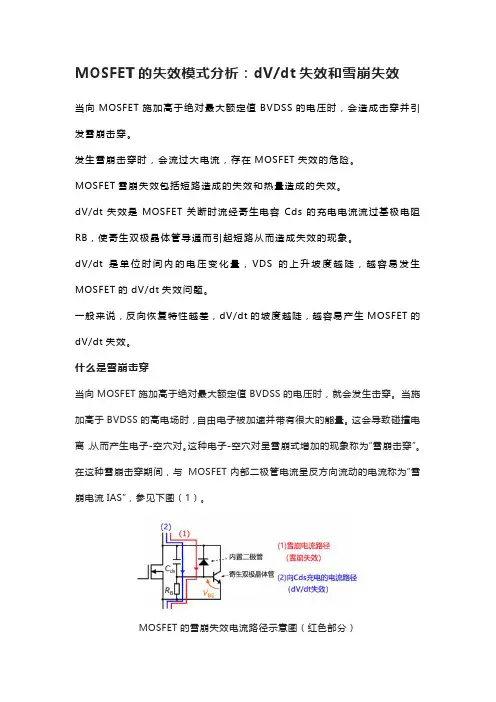

MOSFET的失效模式分析:dV/dt失效和雪崩失效当向MOSFET施加高于绝对最大额定值BVDSS的电压时,会造成击穿并引发雪崩击穿。

发生雪崩击穿时,会流过大电流,存在MOSFET失效的危险。

MOSFET雪崩失效包括短路造成的失效和热量造成的失效。

dV/dt失效是MOSFET关断时流经寄生电容Cds的充电电流流过基极电阻RB,使寄生双极晶体管导通而引起短路从而造成失效的现象。

dV/dt是单位时间内的电压变化量,VDS的上升坡度越陡,越容易发生MOSFET的dV/dt失效问题。

一般来说,反向恢复特性越差,dV/dt的坡度越陡,越容易产生MOSFET的dV/dt失效。

什么是雪崩击穿当向MOSFET施加高于绝对最大额定值BVDSS的电压时,就会发生击穿。

当施加高于BVDSS的高电场时,自由电子被加速并带有很大的能量。

这会导致碰撞电离,从而产生电子-空穴对。

这种电子-空穴对呈雪崩式增加的现象称为“雪崩击穿”。

在这种雪崩击穿期间,与MOSFET内部二极管电流呈反方向流动的电流称为“雪崩电流IAS”,参见下图(1)。

MOSFET的雪崩失效电流路径示意图(红色部分)雪崩失效:短路造成的失效如上图所示,IAS会流经MOSFET的基极寄生电阻RB。

此时,寄生双极型晶体管的基极和发射极之间会产生电位差VBE,如果该电位差较大,则寄生双极晶体管可能会变为导通状态。

一旦这个寄生双极晶体管导通,就会流过大电流,MOSFET可能会因短路而失效。

雪崩失效:热量造成的失效在雪崩击穿期间,不仅会发生由雪崩电流导致寄生双极晶体管误导通而造成的短路和损坏,还会发生由传导损耗带来的热量造成的损坏。

如前所述,当MOSFET处于击穿状态时会流过雪崩电流。

在这种状态下,BVDSS被施加到MOSFET并且流过雪崩电流,它们的乘积成为功率损耗。

这种功率损耗称为“雪崩能量EAS”。

雪崩测试电路及其测试结果的波形如下图所示。

此外,雪崩能量可以通过公式(1)来表示。

功率MOSFET的封装失效分析

第10卷 第1期 2008年1月

名企产品推介

Vol.10 No.1 Jan. 2008

个空洞小到某一程度 (如6%或3.5%) 时, △VDS都 能保持较低的水平 (如小于200 mV); 而当整体空 洞 或 最 大 单 个 空 洞 太 大 时 , △VDS的 状 况 就 不 稳 定, 因而不能保证其符合某一测试要求。

[2] 庄同曾. 集成电路制造 技 术 — —— 原 理 与 实 践 [M]. 北 京: 电子工业出版社, 1978.

(上接第77页)

若客户端因特殊原因没有完成第三步, 那 么 , 服 务 器 在 发 出SYN+ACK应 答 报 文 后 , 将 无 法收到客户端的ACK报文, 此时服务器端一般会 重 试 (再 次 发 送SYN+ACK给 客 户 端), 并 等 待 一 段时间后丢弃这个未完成的连接。

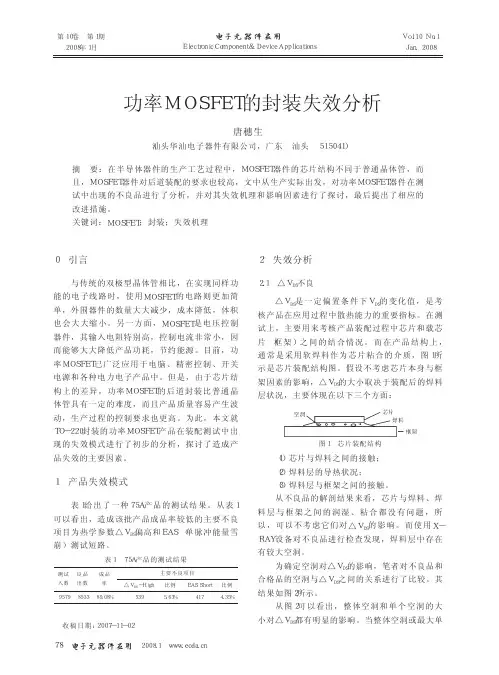

图1 芯片装配结构

(1) 芯片与焊料之间的接触; (2) 焊料层的导热状况; (3) 焊料层与框架之间的接触。 从不良品的解剖结果来看, 芯片与焊料、焊 料层与框架之间的润湿、粘合都没有问题, 所 以 , 可 以 不 考 虑 它 们 对△VDS的 影 响 。 而 使 用X- RAY设备对不良品进行检查发现, 焊料层中存在 有较大空洞。 为确定空洞对△VDS的影响, 笔者对不良品和 合格品的空洞与△VDS之间的关系进行了比较。其 结果如图2所示。 从图2可以看出, 整体空洞和单个空洞的大 小对△VDS都有明显的影响。当整体空洞或最大单

0 引言

与传统的双极型晶体管相比, 在实现同样功 能的电子线路时, 使用MOSFET的电路则更加简 单, 外围器件的数量大大减少, 成本降低, 体积 也会大大缩小。另一方面, MOSFET是电压控制 器件, 其输入电阻特别高, 控制电流非常小, 因 而能够大大降低产品功耗, 节约能源。目前, 功 率 MOSFET已 广 泛 应 用 于 电 脑 、 精 密 控 制 、 开 关 电源和各种电力电子产品中。但是, 由于芯片结 构上的差异, 功率MOSFET的后道封装比普通晶 体管具有一定的难度, 而且产品质量容易产生波 动, 生产过程的控制要求也更高。为此, 本文就 TO- 220封装的功率MOSFET产品在装配测试中出 现的失效模式进行了初步的分析, 探讨了造成产 品失效的主要因素。

AN-9067 llc mos 失效分析

在功率变换市场中,尤其对于通信/服务器电源应用,不 断提高功率密度和追求更高效率已经成为最具挑战性的 议题。对于功率密度的提高,最普遍方法就是提高开关 频率,以便降低无源器件的尺寸。零电压开关(ZVS)拓 扑因具有极低的开关损耗、较低的器件应力而允许采用 高开关频率以及较小的外形,从而越来越受到青睐 [1][2]。这些谐振变换器以正弦方式对能量进行处理,开 关器件可实现软开闭,因此可以大大地降低开关损耗和 噪声。在这些拓扑中,相移ZVS全桥拓扑在中、高功率 应用中得到了广泛采用,因为借助功率MOSFET的等效 输出电容和变压器的漏感可以使所有的开关工作在ZVS 状态下,无需额外附加辅助开关。然而,ZVS范围非常 窄,续流电流消耗很高的循环能量。近来,出现了关于 相移全桥拓扑中功率MOSFET失效问题的讨论[3]。这种 失效的主要原因是:在低反向电压下,MSOFET体二极 管的反向恢复较慢。另一失效原因是:空载或轻载情况 下,出现Cdv/dt直通。在LLC谐振变换器中的一个潜在 失效模式与由于体二极管反向恢复特性较差引起的直通 电流相关[5][6]。即使功率MOSFET的电压和电流处于安 全工作区域,反向恢复dv/dt和击穿dv/dt也会在如启动、 过载和输出短路的情况下发生。

开关电源。这会产生很大的反向恢复dv/dt,有时会击穿 MOSFET Q2。这样就会导致MOSFET失效,并且当采 用的MOSFET体二极管的反向恢复特性较差时,这种失 效机理将会更加严重。

图 6.

APPLICATION NOTE

(d) t3-t4

(e) t4-t5 LLC谐振半桥变换器的潜在失效工作模式

LLC谐振半桥变换器

LLC谐振变换器与传统谐振变换器相比有如下优势[7]:

宽输出调节范围,窄开关频率范围

开关电源中功率MOSFET损坏模式及分析

开关电源中功率MOSFET损坏模式及分析结合功率MOSFET管失效分析图片不同的形态,论述了功率MOSFET管分别在过电流和过电压条件下损坏的模式,并说明了产生这样的损坏形态的原因,也分析了功率MOSFET管在关断及开通过程中,发生失效形态的差别,从而为失效是在关断还是在开通过程中发生损坏提供了判断依据。

给出了测试过电流和过电压的电路图。

同时,也分析了功率MOSFET管在动态老化测试中慢速开通及在电池保护电路应用中慢速关断时,较长时间工作在线性区时,损坏的形态。

最后,结合实际的应用,论述了功率MOSFET通常会产生过电流和过电压二种混合损坏方式损坏机理和过程。

目前,功率MOSFET管广泛地应用于开关电源系统及其它的一些功率电子电路中,然而,在实际的应用中,通常,在一些极端的边界条件下,如系统的输出短路及过载测试,输入过电压测试以及动态的老化测试中,功率MOSFET有时候会发生失效损坏。

工程师将损坏的功率MOSFET送到半导体原厂做失效分析后,得到的失效分析报告的结论通常是过电性应力EOS,无法判断是什么原因导致MOSFET的损坏。

本文将通过功率MOSFET管的工作特性,结合失效分析图片中不同的损坏形态,系统的分析过电流损坏和过电压损坏,同时,根据损坏位置不同,分析功率MOSFET管的失效是发生在开通的过程中,还是发生在关断的过程中,从而为设计工程师提供一些依据,来找到系统设计的一些问题,提高电子系统的可靠性。

1 过电压和过电流测试电路过电压测试的电路图如图1(a)所示,选用40V的功率MOSFET:AON6240,DFN5*6的封装。

其中,所加的电源为60V,使用开关来控制,将60V的电压直接加到AON6240的D和S极,熔丝用来保护测试系统,功率M OSFET损坏后,将电源断开。

测试样品数量:5片。

过电流测试的电路图如图2(b)所示,选用40V的功率MOSFET:AON6240,DFN5*6的封装。

浅谈MOSFET产品失效分析及改善措施

( H u a t i a n T e c h n o l o g y c o . , L t d , T i a n s h u i 7 4 1 0 0 0 , C h i n a )

Ab s t r a c t :T h i s p a p e r ma i n l y d e s c r i b e s t h e a p p l i c a t i o n p r o s p e c t o f M OS F E T p r o d u c t s , t h e p a c k a g i n g p r o c e s s a n d t h e ma t t e r s n e e d i n g a t t e n t i o n ,t h r o u g h t h e a n a l y s i s a n d v e r i i f c a t i o n o f M OS F E T c i r c u i t

-

电 子 工 业 专 用 设 备

Hale Waihona Puke 封 装 工艺 与 设 备

1 M oS F E T 电 路 封 装 工 艺 及 注 意 事 项

传 统 集 成 电路 封 装 的主 要 工 艺有 减 薄 、 划 片、 上芯、 压焊 、 塑封 、 电镀 、 打 印、 切筋成 型、 测试 、 包

装 发货 , 其 封 装 流 程 如 图 1所 示 。

品。 镀 金 或 镀 银 的 晶圆 来料 时 已经 完 成 , 不 需 要 二 次减薄, 在 封 装 工 艺 上 需 要 注 意 二 个 方 面 的管 控 。

一

是在 上 芯 时要 求 采 用 的粘 片胶 含 银 量 要 比其 它

开关电源中功率MOSFET损坏模式及分析

开关电源中功率MOSFET损坏模式及分析功率MOSFET是一种常用于开关电源中的半导体器件,它起到了开关功率的关键作用。

然而,在特定的工作条件下,功率MOSFET也会发生损坏。

本文将对功率MOSFET的损坏模式进行分析。

功率MOSFET的损坏模式主要包括过压损坏、超温损坏、过电流损坏和静电损坏等。

首先,过压损坏是功率MOSFET最常见的损坏模式之一、当输入电压超过器件额定电压时,功率MOSFET可能会发生击穿现象,并导致永久损坏。

过压损坏通常是由于输入电压幅值过高或电压突变引起的。

为了避免过压损坏,可以采用电压稳压电路、电压限制器等电路保护措施。

其次,超温损坏也是功率MOSFET常见的损坏模式之一、当功率MOSFET长时间工作在超过其承受温度的条件下时,温度将升高导致器件内部结构变形,从而引起电性能下降或永久损坏。

超温损坏的原因主要包括功率MOSFET自身内部功率损耗过大、散热不良或环境温度过高等。

为了避免超温损坏,应根据功率MOSFET的热特性设计合理的散热系统,并控制输入功率使其在规定范围内。

此外,过电流损坏也是功率MOSFET常见的损坏模式之一、当输出电流超过功率MOSFET额定电流时,将导致器件内部的金属导线断裂或焦糊,进而导致器件永久损坏。

过电流损坏的原因主要包括负载过大、短路故障等。

为了避免过电流损坏,可以采用电流限制保护电路或过载保护电路等。

静电损坏也是功率MOSFET容易发生的损坏模式之一、静电放电会产生高压瞬态电流,这些电流可能会击穿功率MOSFET内部的绝缘层导致器件损坏。

为了避免静电损坏,通常在使用和维护功率MOSFET时需要注意防静电措施,如使用静电手环、电磁屏蔽等。

在实际设计和应用中,一般采取多种保护措施来降低功率MOSFET的损坏风险。

这些措施包括过压保护电路、超温保护电路、过电流保护电路、静电保护电路等。

通过合理选择和使用这些保护措施,可以有效地防止功率MOSFET的损坏并延长其使用寿命。

B01_陈桥梁_开关电源中MOSFET失效案例分析V1

Surge改善对策

减小BUS残压 Uinpk

改善变压器饱和度

增加变压器磁通面积 Ae

增加变压器匝数 N

减小MOSFET开通时间 Ton

变压器Core变大,和 原来的Bobbin不匹配

减小原边绕组的截面 积,增加导通损耗

减小原边激磁电感Lp, 通过略微增加气隙, 开关频率增加,开关 损耗增加

整改前surge电流波形 (220Vac, 1300V/90°)

抗雪崩能力测试电路

TJM–TC = PDM*ZθJC (t)

MOSFET雪崩能力

雪崩电流IAS和IAR :下图ID峰值 单次雪崩能量EAS:一次性雪崩期间所能承受的能量, 以Tch<=150℃ 为极限 重复雪崩能量EAR:所能承受以一定频率反复出现的雪崩能量, 以Tch<=150℃ 为极限

单次雪崩

Surge Case 3

700mA/32W LED PS Single stage Flyback

***11N70浪涌测试波形 输入电压:230Vac/50Hz,输出:32W 通道1: MOS 漏源电压(黄色, 200V/每格); 通道2: Z2 母线电压(绿色, 200V/每格); 通道3:MOS 漏源电流(粉色, 5A/每格); Time: 5μs/每格 漏源电压=832V 浪涌电压1400V/90º测试波形 母线电压=805V 最大漏源电流=8.3A

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Surge Case 3

700mA/32W LED PS Single stage Flyback

***11N70浪涌测试波形 输入电压:230Vac/50Hz,输出:32W 通道1: MOS 漏源电压(黄色, 200V/每格); 通道2: Z2 母线电压(绿色, 200V/每格); 通道3:MOS 漏源电流(粉色, 5A/每格); Time: 5μs/每格 漏源电压=832V 浪涌电压1400V/90º测试波形 母线电压=805V 最大漏源电流=8.3A

D2

S2

Cr Lr

Va

Ir

S1

Lm

D2

S2

Cr Lr

Va

Ir

S1

Lm

D1

D2

S2

Cr Lr

Va

Ir

S1

Lm

D1

D2

S2

Cr Lr

Va

Ir

S1

Lm

D1

D1

LLC变换器 ZCS状态下模态切换

D2

S2

Cr Lr

Va

Ir

S1

Lm

D2

S2

Cr Lr

Va

Ir

S1

Lm

D1

D2

S2

Cr Lr

Va

Ir

S1

Lm

D1

D2

230Vac输入满载,启动波形 负载:2.42A-30V

输入电压:230Vac/50Hz,输出:满载 通道1: MOS 漏源电压(黄色, 100V/每格); 通道2: MOS 门极驱动(绿色, 5V/每格); 通道3:MOS 漏源电流(粉红,2A/每格); Time: 10μs/每格 漏源电流=35.6A

PWM IC 1

输入电压:230Vac/50Hz, 输出:满载 通道1: MOS 漏源电压(黄色, 100V/每格); 通道2: MOS 门极驱动(绿色, 5V/每格); 通道3:MOS 漏源电流(粉红,2A/每格); Time: 100μs/每格

PWM IC 2

谢谢!Leabharlann S2Cr LrVa

Ir

S1

Lm

D1

D1

LLC变换器输出短路状态下波形

LLC变换器工作波形

主要内容

• 雪崩特性特性及失效分析 • 体二极管特性及失效分析 • 安全工作区及失效分析

MOSFET安全工作区(SOA)

案例:反激电源启动波形

230Vac输入满载,启动波形 负载:2.42A-30V

输入电压:230Vac/50Hz,输出:满载 通道1: MOS 漏源电压(黄色, 100V/每格); 通道2: MOS 门极驱动(绿色, 5V/每格); 通道3:MOS 漏源电流(粉红,2A/每格); Time: 100μs/每格 漏源电流=35.6A

Surge改善对策

减小BUS残压 Uinpk

改善变压器饱和度

增加变压器磁通面积 Ae

变压器Core变大,和 原来的Bobbin不匹配

增加变压器匝数 N

减小原边绕组的截面 积,增加导通损耗

减小MOSFET开通时间 Ton

减小原边激磁电感Lp, 通过略微增加气隙, 开关频率增加,开关

损耗增加

整改前surge电流波形 (220Vac, 1300V/90°)

5

雪崩能量和初始结温以及电流的关系

雪崩电流和雪崩时间的关系

MOSFET雪崩电流路径及影响

Vac 前馈

RCD

MOV10D561

• Surge浪涌 • 输入电压突变

简化后的Flyback Case 1

Vbus

L1

R1

C1

D1

Lm P1

TX1 S1

D2

R2 C2

Vds < Vav

Q1

简化后的Flyback Case 2

230Vac输入满载,启动波形 负载:2.42A-30V

输入电压:230Vac/50Hz,输出:满载 通道1: MOS 漏源电压(黄色, 100V/每格); 通道2: MOS 门极驱动(绿色, 5V/每格); 通道3:MOS 漏源电流(粉红,2A/每格); Time: 100μs/每格 漏源电流=35.6A

Channel 1:Vbus Channel 2:Vds Channel 3:Id

整改后surge电流波形 (220Vac, 1300V/90°)

主要内容

• 雪崩特性及失效分析 • 体二极管特性及失效分析 • 安全工作区及失效分析

MOSFET体二极管反向恢复电流

LLC变换器 ZVS状态下模态切换

抗雪崩能力测试电路

TJM–TC = PDM*ZθJC (t)

MOSFET雪崩能力

雪崩电流IAS和IAR :下图ID峰值 单次雪崩能量EAS:一次性雪崩期间所能承受的能量,

以Tch<=150℃ 为极限 重复雪崩能量EAR:所能承受以一定频率反复出现的雪崩能量,

以Tch<=150℃ 为极限

单次雪崩

重复雪崩

Vbus < Vav-Vsr

Vbus

L1

R1

C1

D1

Lm

Vsr

P1

TX1 S1

D2

R2 C2

Vds = Vav

Q1

简化后的Flyback Case 3

Vbus > Vav-Vsr

Vbus

L1

R1

C1

D1

Lm P1

TX1 S1

D2

R2 C2

Vds = Vav

Q1

MOSFET雪崩过程中失效

图: 浪涌测试波形 输入电压:230Vac/50Hz,输出:32W 通道1: MOS 漏源电压(黄色, 200V/每格); 通道2: Z2 母线电压(绿色, 200V/每格); 通道3:MOS 漏源电流(粉色, 5A/每格); Time: 10μs/每格

开关电源中MOSFET失效案例分析

陈桥梁 西安龙腾新能源科技发展有限公司

主要内容

• 雪崩特性及失效分析 • 体二极管特性及失效分析 • 安全工作区及失效分析

MOSFET雪崩能力

雪崩能力

雪崩电流 IAS,IAR

寄生BJT导通,MOSFET 趋 于开通。

雪崩能量 EAS,EAR

MOSFET局部元胞过热损 坏。