基于D触发器的四位格雷码加1计数器的设计

利用D触发器构成计数器

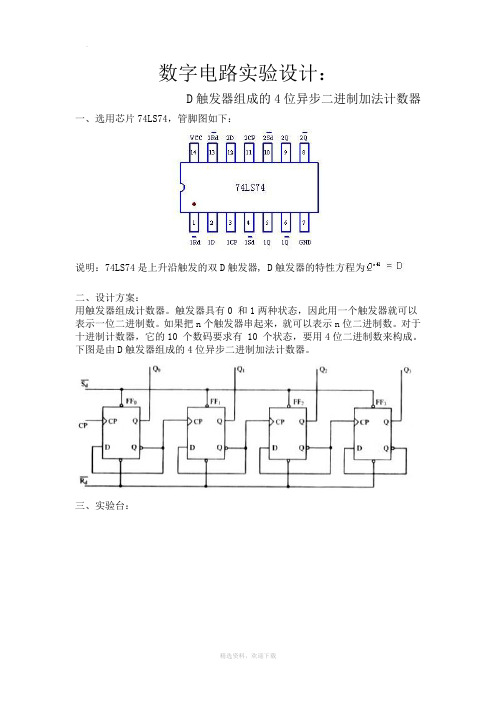

数字电路实验设计:D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为二、设计方案:用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:四、布线:1、将芯片(1)的引脚4、10连到一起,2、将芯片(2)的引脚4、10连到一起,3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,4、将芯片(1)的引脚10连到+5V;5、将芯片(1)的引脚1、13连到一起,6、将芯片(2)的引脚1、13连到一起,7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,8、将芯片(1)的引脚13连到+5V;9、将芯片(1)的引脚3接到时钟信号CP10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚1111、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚312、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚1113、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q314、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:接通电源on,默认输出原始状态0000每输入一个CP信号(单击CP),的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、1111。

利用D触发器构成计数器

数字电路实验设计:D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为二、设计方案:用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:四、布线:1、将芯片(1)的引脚4、10连到一起,2、将芯片(2)的引脚4、10连到一起,3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,4、将芯片(1)的引脚10连到+5V;5、将芯片(1)的引脚1、13连到一起,6、将芯片(2)的引脚1、13连到一起,7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,8、将芯片(1)的引脚13连到+5V;9、将芯片(1)的引脚3接到时钟信号CP10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚1111、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚312、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚1113、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q314、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:接通电源on,默认输出原始状态0000每输入一个CP信号(单击CP),的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、1111。

D触发器电路设计及计数器设计-文档资料

0

1

0

0

5

0

1

0

1

6

0

1

1

0

7

0

1

1

1

8

1

0

0

0

9

1

0

0

1

a

1

0

1

0

b

1

0

1

1

c

1

1

0

0

d

1

1

0

1

e

1

1

1

0

f

1

1

1

1

5V

Vcc QCC Q0 Q1 Q2 Q3 CTr LD 16 15 14 13 12 11 10 98

QCC Q0 Q1 Q2 Q3 E r

CR

74LS161 LD

CP D0 D1 D2 D3 EP

4、注意电路中的元件类型,如电路中有TTL 电路、又有CMOS 电路, 还有分立元件电路,要选择合适的电源,注意电平转换以及带负载 能力等问题。

5、有些故障是由于竞争和冒险造成的,应该尽量避免将组合电路的输 出直接作为触发器的时钟、异步复位和异步置数,或者在使用时进 行同步处理。

广告流水灯布线示范

动态调试与静态调试的区别在于时钟脉冲改由连续时钟脉 冲信号源提供,输出可由示波器观测也可采用逻辑分析仪进行 观测。用示波器进行动态调试的一般步骤如下:

1、把时序脉冲发生器输出的连续周期性脉冲信号接到时序逻 辑电路的时钟输入端,同时将电路中的特定节点接到系统 的显示部分作辅助检测电路。

时序电路调试技巧—动态调试

法。常用的调试步骤如下:

1、把经过消抖处理的手

动单次脉冲发生器输

利用D触发器构成计数器

数字电路实验设计:D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为二、设计方案:用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有 10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:四、布线:1、将芯片(1)的引脚4、10连到一起,2、将芯片(2)的引脚4、10连到一起,3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,4、将芯片(1)的引脚10连到+5V;5、将芯片(1)的引脚1、13连到一起,6、将芯片(2)的引脚1、13连到一起,7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,8、将芯片(1)的引脚13连到+5V;9、将芯片(1)的引脚3接到时钟信号CP10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚1111、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚312、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚1113、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q314、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:接通电源on,默认输出原始状态0000每输入一个CP信号(单击CP),的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、1111Welcome !!! 欢迎您的下载,资料仅供参考!。

利用D触发器构成计数器-d触发器 计数器

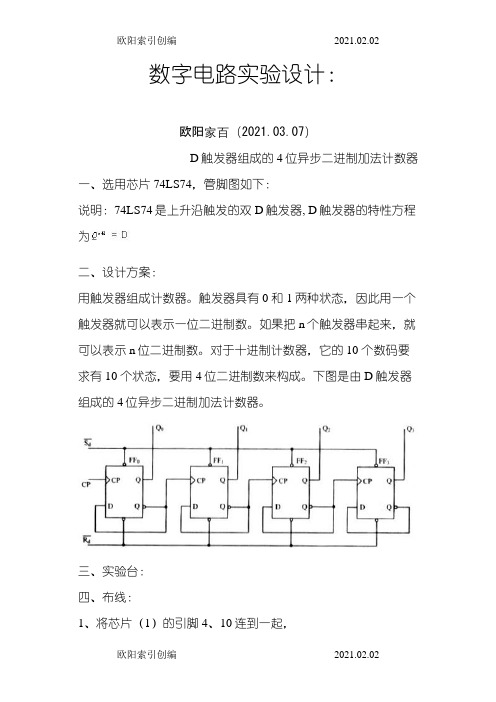

数字电路实验设计:欧阳家百(2021.03.07)D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为二、设计方案:用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有 10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:四、布线:1、将芯片(1)的引脚4、10连到一起,2、将芯片(2)的引脚4、10连到一起,3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,4、将芯片(1)的引脚10连到+5V;5、将芯片(1)的引脚1、13连到一起,6、将芯片(2)的引脚1、13连到一起,7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,8、将芯片(1)的引脚13连到+5V;9、将芯片(1)的引脚3接到时钟信号CP10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚1111、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚312、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚1113、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q314、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:接通电源on,默认输出原始状态0000每输入一个CP信号(单击CP),的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、1111。

利用d触发器构成计数器-d触发器计数器

D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:

说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为

二、设计方案:

用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以

表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有 10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:

D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:

说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为

二、设计方案:

用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以

表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有 10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:。

利用D触发器构成计数器-d触发器 计数器

数字电路实验设计:D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为二、设计方案:用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:四、布线:1、将芯片(1)的引脚4、10连到一起,2、将芯片(2)的引脚4、10连到一起,3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,4、将芯片(1)的引脚10连到+5V;5、将芯片(1)的引脚1、13连到一起,6、将芯片(2)的引脚1、13连到一起,7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,8、将芯片(1)的引脚13连到+5V;9、将芯片(1)的引脚3接到时钟信号CP10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚1111、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚312、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚1113、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q314、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:接通电源on,默认输出原始状态0000每输入一个CP信号(单击CP),的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、1111如有侵权请联系告知删除,感谢你们的配合!。

利用D触发器构成计数器

数字电路实验设计:D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为二、设计方案:用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:四、布线:1、将芯片(1)的引脚4、10连到一起,2、将芯片(2)的引脚4、10连到一起,3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,4、将芯片(1)的引脚10连到+5V;5、将芯片(1)的引脚1、13连到一起,6、将芯片(2)的引脚1、13连到一起,7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,8、将芯片(1)的引脚13连到+5V;9、将芯片(1)的引脚3接到时钟信号CP10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚1111、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚312、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚1113、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q314、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:接通电源on,默认输出原始状态0000每输入一个CP信号(单击CP),的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、1111。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

大作业4----基于D触发器的四位格雷码加1计数器的设计

一、状态图

Q4(t+1)Q3(t+1)Q2(t+1)Q1(t+1)

化简得到:

Q4(t+1)= Q4Q1+Q4Q2+Q3Q2Q1

Q3(t+1)= Q4Q2Q1+Q3Q1+Q3Q2

Q2(t+1)=Q2Q1+Q4Q3Q1+Q4Q3Q1

Q1(t+1)= Q4Q3Q2+Q4Q3Q2+Q4Q3Q2+Q4Q3Q2

根据D触发器的特性方程Q(t+1)=D,可得4个激励方程得D4=Q4Q1Q2+Q3Q2Q1

D3=Q4Q2Q1+Q3Q1 Q2

D2= Q2Q1+Q1(Q4⊙Q3)

D1=Q4(Q3⊙Q2)+Q4(Q3⊕Q2)=Q4⊕(Q3⊙Q2)

二、仿真

1、原理图

2、编译原理图

3、波形仿真

4、波形编译

5、设定I/O

6、生成逻辑符号

三、增加异步清零和计数使能

增加两个输入端,clr和EN,为1时两个端口有效。

module A(cp,state);

parameter

S0=4'b0000,S1=4'b0001,S2=4'b0011,S3=4'b0010,S4=4'b0110,

S5=4'b0111,S6=4'b0101,S7=4'b0100,S8=4'b1100,S9=4'b1000;

input cp;

output [4:1]state;

reg [4:1]state;

always@(posedge cp)

case(state)

S0: state<=S1;

S1: state<=S2;

S2: state<=S3;

S3: state<=S4;

S4: state<=S5;

S5: state<=S6;

S6: state<=S7;

S7: state<=S8;

S8: state<=S9;

S9: state<=S0;

default state<=S0;

endmodule

五、总结

D 型触发器的输入输出关系简单明了,通过状态图等画出卡诺图,得到输入输出关系是多位寄存器的基本结构。

HDL考虑现态和次态的关系。

通过这次大作业,更加深入了解了触发器,也巩固了之前有关卡诺图的知识。