USB数据采集板的测试系统

USB在随钻测量数据采集系统中的应用

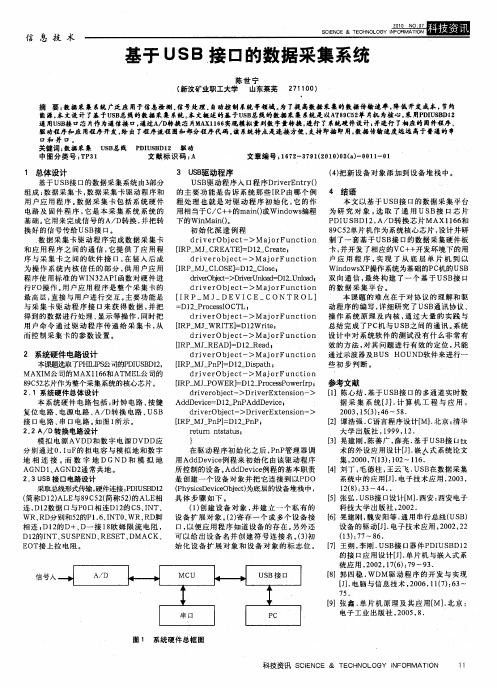

图 1 系 统 硬 件 结 构 圈

热插拔 、 无须 外接 电源 、 带宽 、 高 传输 速 度快 、 连接 多 可

个 设备 等优 点 , 主机 和 数 据 采 集 系 统 之 间 可 以 实现 在 简单 、 捷 、 向、 快 双 可靠 的连 接 和通 讯 _ 。井 下 检测 的 1 ]

片 IP 5 1 速 度 可 达 4 0 M p , S 18 , 8 b s 它完 全 符 合 U B . S20 规范 。采 用 IP 5 1可 以 快 速 开 发 出高 性 能 的 U B S 18 S 20 .设备 , 时 为 了满 足 速 度要 求 , 同 主控 制 芯 片选择 了

形方 式在计 算 机 上 显示 , 进 行 实 时处 理 。U B传输 并 S

速度 快而且 能 够保 证 数 据 的 无失 真 传 输 , 用 上 位机 利 的优 势对数 据 进行 全面 的 、 多方 位 的实时处 理与分 析 。

本设计 系统硬 件结 构 如图 1 所示 。

和井 口完成 的 。R 2 2接 口传 输 速 率 太 低 , S3 而并 口的 数据线 过 多且 传 输 距 离 太 短 。本 设 计 中采 用 U B进 S

1 1 器件选 择 .

U B控 制器 分为 两 大类 , 类是 集 成 了 U B接 口 S 一 S

的单 片 机 , C pes公 司 基 于 8 5 如 y rs 0 1的 E Z~U B系 S 列 、 ooo M t l 于 6 HC 8系列 的 6 HC 8B r a基 8 0 8 0 J 8等 , 种 这 控 制器 虽然 编程 简单 , 但需 要 购置专 门的开发 系统 , 投

基于USB总线的数据采集系统软件设计

1 基 于 US 的数 据 采 集 系统 B

基 于 US B总线 的数 据采 集 系统一 般 由主机 、 B US 控 制器 、 AD转换 及存 储 模块 构 成 , 基本 结 构 如 图 1 所

US B控 制器 ( y esE — B F ( Y7 6 0 3 ) ; C p s Z US X2 C C 8 1 ) 等

软 件 部 分 主 要 包 括 US B控 制 器 固件 程 序 、 B设 备 US 驱 动程 序 、 户 应用 程序 等 。 用

2 数 据 采 集 软件 系 统 设计

汪 红 童 小念

( 中南民族 大学 计算机 科 学学 院 武汉

407) 3 0 4

【 摘 要】在 现代 工 业控制 和科 学研 究过 程 中, 常需要 对数据 信 号进 行采 集 并加 以分 析 , 经 随着 总 线技 术 的发展 , US 以其 特有 的高速 、 B 方便 、 灵活 等优 势迅 速成 为 主要 的信 号传 输 总线 。在 对基 于 US 总线 的数 据采 集 系统 的 B 总体 结构进 行 综述 的基 础上 , 系统 的固件 程序 、 于 WD 的 US 对 基 M B驱 动程 序及 用 户 态应 用程 序 等软 件部 分设 计进行 了较 详 细的讨论 , 为上述 软件 部分 设计 对基 于 US 总线 系统设 计 非常关键 。 认 B

用。 ‘

换 之后 成为 数字 信 号 , 暂时保 存 在存储 器 中 , 被 然后 在 US B控制 器 的作 用下 , 过 总线 传输 到 主机 进 行后 期 通

基于USB的数据采集及其在线缆通断测试系统中的应用

真正的 即插 即用 (N ) P P 功能 。 S U B接 口优异 的性能 , 已经 成为最为 流行 的接 口技术 。

2系统组成

系统组成框 图如 图 1 示 。 所

图 1 系 统 组成 框 图

微 型计 算机 (C) 出测试命令 后 , 过 U B总 P 发 通 S 线, 命令数据送到 8C 1 0 5 单片机 , 单片机执行测试 命令, 通过接 口电路 , 发出测试数据, 测试数据通过 线 缆后 从线缆 另一 端送 回单 片机 , 片机 把接 受 的 单 测 试数 据处理 后经 过 U B接 口送 给 P P S C,C机 通过

3 单 片机 与 P . 2 C的 U B接 口电路 S U B接 口 电路 选 用 U B总 线 通 用 接 口芯 片 S S C 7, 图 3 示。 H3 2 如 所

P 口 O 一

的 A I主要 包 括 : 备 管理 A I数据 传输 A I中 P, 设 P、 P、

断处 理 A I P。

7 1l8来选 中各个锁存 器 。 4s3

对测试数据进行分析, 以直观 的界面形式显示测试

结果 。

收 稿 日期 :07 0— 5 2 0 — 8 2

基金项 目: 河北省 自然资金资助项 目《 多体交叉并行 高速数据采集理论与方法研究》项 目号 :20 00 1 ) ( F 0 70 7 4 作者 简介 : 李建科 ( 9 1 , , 17 一)男 河北 沙河人 , 河北经 贸大学信 息技术 学院讲 师 , 硕士 , 研究 方 向 : 测试计量及 仪器 ; 崔志勇

实际 中 , 采用 C 7 H32的单 项数 据流方式 进行单 片机 与 P C间的通讯 。 C端采用 V P C编程 , 设计 了形 象而直 观的界 面 , 图 4 示 。 如 所

基于USB数据采集技术的远程虚拟测试系统

1 5 0 , hn ;. e igE eti P we et Ree rhIsi t,e ig1 0 7 , ia 2 15C i a2 B in l r o r s & sa c t ue Un 0 0 5Chn ; j c c T n t B

3 Ex e i n n an n n e , i o igT c nc l ie st, xn 1 3 0 , i n ) . p rme t dTr i i gCe tr L a n n e h ia v r i Fu i 2 0 0Ch a a Un y

Ke r : r mot a u e n : La VI y wo ds e eme s r me t b EW : USB

0 引 言

随着 近年 来测 试技 术 、 络技 术 的发 展 以及功 能 需求 的不 断提 高 ,远 程测 试技 术得 到 快速 发展 。

另 外 ,测 试 技 术 的 不 断 革 新 也 促 使 新 的 网络 测 控 技

阐述 了 L b IW 开 发 平台 上网络化传 输 的实 现方 法 aVE

关 键 词 : 远程测试系统:L b I W;U B aV E S

中图分类号:T 7 P2 4

文献标识码 :A

Re mo ev ru lme s r m e ts se b s d O t it a a u e n y tm a e n USB d t o lc i n t c n l g a ac le to e h o o y

c b n t ru l nsr m e ttc o o n SB n e f c e hn l y me t hete d. S b sc nb s d om i a i ofvit a tu on i n e hn l gya d U i tra e t c o og e st r n U B u a e u e t ole tr a —i e d t thih s e d a d ta f rt he h s o c lc e ltm a aa g p e n r nse o t o tPC.Th a a t e a r n re e o e y w i e d t h n c n be ta se r d r m t l t f h

同步发电机USB专用数据采集系统的研制

第 5期

电气 电 子 教学 学 报 J OURNAL OF EEE

Vo . 2 No. I3 5 0c . Ol t2 0

21 0 0年 1 O月

同步发 电机 U B专用 数 据 采集 系统 的研 制 S

焦 盈盈 , 雷 勇 , 曾成 碧

( 四川 大学 电 气信 息 学院 , 四川 成都 6。 I J 5 罱 I

该 数 据采 集 系统 属 于开 放式 和 可修 改 的系 统 。 设 计方 案具有 可操作性 。可以根据 需要对 系统 的功 能进 行 添加和修 改 , 以达到不 同 的应 用 目的 。

我校 的 电机实验 室 由于运行 年代久 远和 资金 的

t m a a c l t n na y e e pe i nt lda a,s v h m nd pr v d on to orf r h rde e o a c n c l u a e a d a l s x rme a t a e t e a o i e c dii nsf u t e v l pme nt a a t tl s . Ke ywo d v r u li t ume t La VI r s: it a ns r n ; b EW ; a a a q s to s n hr ou ne a or d t c uiii n; y c on s ge r t

限制 , 与现 代先 进 技 术有 很 大 的差 距 。为 了 实现 电

机实验 室的现 代化 运 用需 求 , 们 以节 约 资 金 为前 我

提对其进 行 了改造 。

l 数 据 采 集 系统

1 )数 据 采 集 系 统 的 工 作 流 程

改造 前实验 室 同步发 电机运行 数据依 靠传 统的 电压表 和 电流 表 等 进 行 测 量 。这 种 测 量 读 数 误 差 大, 只能获 得有效 值 , 计算 麻烦 。本 文提 出的一种 基

基于USB接口的便携式数据采集系统的设计

基 于 US 接 1 便 携 式 数 据 采 集 系 统 的设 计 B 3的

De in o sg [Co e i nt nsr m e fD a a A c i ii n S t r s d o B nt ra e nv n e tu I nt t qu s to yse Ba e n US I e Y c o n

良好的人 机界 面。

关 键 词 :U B;数 据采 集 ;G I S PF;MD变 换器

中 图分 类 号 :T 24 P 7

Ab

文献 标 识 码 :B

文章 编 号 : 10 - 172 0 ) o o— 5 03 00 (0 8 m- o9 0

c : I d o de i y t m ch c u d be u e n t e o n f l . t e r s ar oc s s o h tu t r fa p ra e daa t nor er sgn a s s e whi o l s d i h pe i d t e h e e ch f u e n t e s r c u e o ot bl t

fe e c e 4 MHz Al t e lgial u c in fF r qu n y ar 0 l h c n t s o PGA a e r ai d by p o a mig o f o r e l r gr ze m n VHDL c de c e ie h on r fr a n o s whih r al s t e c t o e dig z ol

1研究背景与系统总要求

11数据采集设备的设计要求 .

一

根据数据采集器 的要求 ,对基于 U B的数据采集系统进行 方 S 案设计 。该数 据采集系统采 用两路 1 4位 4 MHz AD变换 0 的 /

基于USB接口的数据采集系统

关键 词 : 数据采 集 U B S 总线 中 图分 类号 : P 1 T 3

P IS D 2 驱 动 D U B 编号 :6 2 3 9 (0 oo() 0 1 - 1 1 7 - 7 12 1)3a- 0 1 0

1 总体设计

.

2 系统硬件 电路设计

本课题选取 了P II 公司的P I S D 2 HL S P DU B 1,

M AXI 公 司 的 MAXl 6 和 ATMEL 司 的 M 16 公

() 新 设 备 对 象 添 加 到 设 备 堆 栈 中 。 4把 U B S 驱动 程 序 入 口程 序 D ieE ty ) rv r n r ( 的主要功能是告诉 系统那些I RP由哪 个 例 4 结语 程 处 理 也 就 是 对 驱 动 程 序 初 始 化 , 的 作 它 本 文 以 基 于 US 接 口的 数 据 采 集 平 台 B 用相 当于 C c + man) Wid ws 程 为 研 究 对 象 , 取 了 通 用 US / + 的 i( 或 no 编 选 B接 口芯 片 下的 WiMan ) n i (。 P US D1 , D转 换 芯 片 MAX1 6 和 DI B 2 A/ 16 初 始 化 派 遣 例 程 8 C 2 片机 作 为 系统 核 心 芯 片 , 9 5单 设计 并 研 dr Ve Ob e t i r j c 一> M a o FUnc i n j r t O 制 了一 套 基 于 US 接 口的 数据 采 集 硬 件 板 B [ P MJ C E T ] D1 一 r ae I — — R A E= C et; R 2 卡 , 开 发 了相 应 的Vc + 发 环 境下 的 用 并 + 开 dr ve o c 一 >M a o Fu t o 户 应 用 程 序 , 现 了 从 底 层 单 片 机 到 以 i r bj t e j r nc i n 实 Ⅱ P MJ C O E = 一 ls ; R — — L S ] D1 C oe 2 Wid ws 操 作系统 为基 础的P 机的 U B n o XP C S d vr bet>D ieUnod i f eO j - r r la=D1. la l 双 向通 信 , 终 构 建 了一 个 基 于 US 接 口 c v 2Uno d 最 B di r r ve Obj c 一>Ma or et j Func i 的 数 据 采 集 平 台 。 t on [ R P—M —DEVI I J CE—C0NTR0L] 本 课 题 的难 点在 于 对 协 议 的 理 解 和 驱 D 1 一 oc s I CTL; 2 Pr e sO 动程 序 的编 写 , 细研 究 了US 通 讯 协议 、 详 B 通 dr v r i e Obj c 一>M a Or nc i 操 作 系统 原 理 及 内核 , 过 大 量 的 实 践 与 et j Fu t On 总结 完成 了P 机 与US 之 间 的 通讯 。 C B 系统 [ — — RT ]D 2 i } I MJW I E= 1 Wr e RP t dr V r i e Obj c 一>M a o Fu t O 设计 中对 系统 软 件 的 测 试 没 有 什 么 非 常有 et j r nc i n Ⅱ P MJ R A I D1 一 a ; R — — E D = 2 Re d 效 的 方法 , 其 问 题进 行 有 效 的 定 位 , 对 只能 dr ve Ob e t i r j c 一>M a o Func i n jr t O 通 过 示波 器 及B HOU US ND 件 来进行 一 软 [ P MJ P P = _ i a h I — — n ] D Ds t ; R 1 2 p 些 初步判断 。

FPGA和USB的双通道数据采集测试系统

传 到 计 算 机 中 。其 中系 统 的整 体 结 构 如采 集 系 统 是 信 号 与 信 息 处 理 系 统 不 可 缺 少 的 组

成部分 , 其 广 泛 应 用 于 微 电子 技 术 、 计 算 机 技 术 和 通 信 技 术 等 领 域 。本 文 所 述 系 统 充 分 利 用 了 现 场 可 编 程 门 阵列 的灵 活 性 和 通 用 串 行 总 线 ( US B) 体积 小 、 即插 即用 、 速

Hu a n g Yu a n wa n g,Ya n J i h o n g

( S c h o o l o f El e c t r o n i c En g i n e e r i n g,Un i v e r s i t y o f El e c t r o n i c S c i e n c e a n d Te c h n o l o g y o f Ch i n a , Ch e n g d u 6 1 1 7 3 1 ,Ch i n a ) Ab s t r a c t :Th i s p a p e r p r e s e n t s a s o l u t i o n o f d u a l c h a n n e l d a t a a c q u i s i t i o n s y s t e m h a r d wa r e i mp l e me n t a t i o n .Th e s y s t e m c o n s t i t u t e s FP GA

F P GA 和 U S B 的 双 通 道 数 据 采 集 测 试 系 统

黄远 望 , 严 济 鸿

( 电 子科 技 大 学 电子 工 程 学 院 , 成都 6 1 1 7 3 1 )

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

华中科技大学硕士学位论文USB数据采集板的测试系统姓名:付凌霄申请学位级别:硕士专业:信号与信息处理指导教师:李青侠20070609华中科技大学硕士学位论文摘要在欧洲粒子物理研究所(CERN)的大型离子对撞实验(ALICE)中,光子探测系统(PHOS)需要大量的数据采集板,该板完成光电转换所产生的电信号的处理、数据采集。

为了保证批量生产的数据采集板在PHOS系统中能正常工作,需要对每块板进行测试,而人工测试工作量大、效率低,因此需设计一个可对该板进行离线测试的测试系统,以高效完成对数据采集板的功能测试及故障诊断,减小测试难度。

本文根据数据采集板上的测试需求,结合虚拟仪器概念,从USB总线技术的基本原理出发,对USB体系结构、数据传输类型、USB设备相关概念等几方面进行了分析和阐述,提出了基于EZ-USB的测试系统方案。

该方案主要包括测试系统硬件设计、下位机固件程序和上位机应用程序的设计。

下位机固件程序采用嵌入式软件编程,通过前台的主循环程序和后台的中断服务程序实现,按照功能需求完成USB 传输,保证了测试系统数据传输的正确性和稳定性。

通过使用面向对象语言开发上位机应用软件可以实现测试界面和采集板之间的数据高效交换,此外通过图形用户界面还可以随时对数据采集板上FPGA工作状态进行控制,并对FPGA进行重新配置。

实验的测试结果表明,该测试系统可以对数据采集板进行离线测试,通过友好人机界面来操作测试系统,从而正确完成对数据采集板的工作状态控制、板上FPGA 的可重配置以及各类数据的采集、显示、存储、导出等功能,便捷高速而且降低了测试成本。

关键词:测试系统;EZ-USB;数据传输;下位机固件;上位机应用程序华中科技大学硕士学位论文AbstractThe Photon Spectrometer, subsystem in A Large Ion Collider Experiment (ALICE) of European Organization for Nuclear Research (CERN), requires a large number of data-acquiring modules to acquire signal from high-speed particle collision. To guarantee the batch FEE cards working normally in PHOS, testing for each card is necessary. It will have a great amount of w ork with low efficien cy to test manually. To decrease the test difficulty, a test system is designed to handle the function test and error diagnosis in mass production.In this thesis, the test system is composed of a PC equipped with Virtual Instrument as host and an EZ-USB-based microcomputer controller as the slave computer. As communication between the Host and the Slave Computer is via USB bus, system architecture and data transmission types of USB are mentioned first. According to the test demand, system hardware scheme, embedded firmware of slave computer and host application software are proposed respectively. By using the program of embedded system, the bottom firmware is implemented with the foreground procedures: main-loop, background procedures: servings for interrupt.The coordination of the firmware program in the slave computer and the hardware insure the reliability and stabilization of the data transmission in the test system. The host application is developed by object-oriented language with friendly Graphical User Interface (GUI). It insures efficient data exchange with slave controller with smart control to field status. The FPGA chip in slave sy stem can also be reconfigured by host PC flexibly.In mass production, the test system mentioned can be operated offline from the system bus of PHOS. All field statistics can transfer to host PC via USB link, which can be displayed in pellucid tables, stored/exported for farther scientific analysis. Compared with traditional manual testing, the test system reduces the cost sharply.Key words: Test system; EZ-USB; Data transfer; Bottom firmware; Host application华中科技大学硕士学位论文缩略语ALICE A Large Ion Collider ExperimentAPD Avalanche Photon DiodesCERN European Organization for Nuclear ResearchCSP Charge Sensitive PreamplifiersDCS Detector Control SystemDMA Direct Memory AccessFEE Front End ElectronicsFIFO First-in First-outFMD Forward Multiplicity DetectorFPGA Field-Programmable Gate ArrayGPIB General Purpose Interface BusGPIF General Programmable InterFaceHMPID High Momentum Particle Identification DetectorI2C Inter-Integrated CircuitITS Inner Tracking SystemIRP I/O request packetLHC The Large Hadron Collider project MUONSPEC Muon SpectrometerPCI Peripheral Component InterconnectPDU Protocol Data UnitPHOS PHOten SpectrometerPMD Photon Multiplicity DetectorPWO Lead-tungstate CrystalPXI PCI eXtensions for InstrumentationRCU Readout Control UnitSCL Serial Clock LineSDA Serial DataTOF Time-of-FlightTPC Time Projection ChamberTRU Trigger Region UnitsUSB Universal Serial BusVXI VME eXternted for Instrument独创性声明本人声明所呈交的学位论文是我个人在导师指导下进行的研究工作及取得的研究成果。

尽我所知,除文中已经标明引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写过的研究成果。

对本文的研究做出贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到,本声明的法律结果由本人承担。

学位论文作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,即:学校有权保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权华中科技大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

保密□,在_____年解密后适用本授权书。

本论文属于不保密□。

(请在以上方框内打“√”)学位论文作者签名:指导教师签名:日期:年月日日期:年月日华中科技大学硕士学位论文1 概述1.1 引言大型离子对撞实验(ALICE)合作组是由大学和研究所组成的一个合作组织,目前这个组织正筹备一个将在大型强子对撞机(LHC)上进行的大型实验,位于瑞士日内瓦近郊的欧洲原子能研究中心正在筹建这个对撞机。

LHC竣工后将是世界上最大的粒子加速器对撞机,届时将允许来自世界40余个国家的科学家在LHC上进行大量的以研究粒子的结构和物质性质为目的的重要实验。

ALICE实验装置包括内部跟踪系统(ITS),计时发射室(TPC),辐射跃迁探测器(TRD),光子探测系统(PHOS),高能粒子识别探测器(HMPID),光子多样性探测器(PMD),前向多样性探测器(FMD),μ介子分光计(MUONSPEC)等几个部分[1]。

其中PHOS包括有探测控制系统(DCS),可读控制单元(RCU),数据采集板(FEE)。