adf350 芯片

半导体传感器ADF4113BRUZ中文规格书

ADF4116/ADF4117/ADF4118Rev. D | Page 13 of 28 PHASE FREQUENCY DETECTOR (PFD)AND CHARGE PUMPThe PFD takes inputs from the R counter and N counter and produces an output proportional to the phase and frequency difference between them. Figure 28 is a simplified schematic of the PFD. The PFD includes a fixed delay element that sets the width of the antibacklash pulse. This is typically 3 ns. This pulse ensures that there is no dead zone in the PFD transfer function and gives a consistent reference spur level.00392-028Figure 28. PFD Simplified Schematic and Timing (In Lock)MUXOUT AND LOCK DETECT The output multiplexer on the ADF411x family allows the user to access various internal points on the chip. The state of MUXOUT is controlled by M3, M2, and M1 in the function latch. Figure 33 shows the full truth table. Figure 29 shows the MUXOUT section in block diagram form. 00392-029Figure 29. MUXOUT Circuit Lock DetectMUXOUT can be programmed for both digital lock detect and analog lock detect.Digital lock detect is active high. It is set high when the phase error on three consecutive phase detector cycles is less than 15 ns. It stays set high until a phase error greater than 25 ns isdetected on any subsequent PD cycle.The N channel, open-drain, analog lock detect should be operated with an external pull-up resistor of 10 kΩ nominal. When lock is detected, it is high with narrow low going pulses.INPUT SHIFT REGISTER The ADF411x family digital section includes a 21-bit input shiftregister, a 14-bit R counter, and an 18-bit N counter, comprising a 5-bit A counter and a 13-bit B counter. Data is clocked into the 21-bit shift register on each rising edge of CLK. The data is clocked in MSB first. Data is transferred from the shift register to one of four latches on the rising edge of LE. The destination latch is determined by the state of the two control bits (C2, C1) in the shift register. These are the two LSBs, DB1 and DB0, as shown in the timing diagram in Figure 2. The truth table for these bits is shown in Figure 34. Table 5 summarizes how the latches are programmed.Table 5. Programming Data LatchesControl Bits C2C1 Data Latch 00 R Counter 01 N Counter (A and B) 10 Function Latch 1 1 Initialization LatchADF4116/ADF4117/ADF4118Rev. D | Page 24 of 28INTERFACINGThe ADF411x family has a simple SPI®-compatible serial inter-face for writing to the device. CLK, DATA, and LE control the data transfer. When LE (latch enable) goes high, the 24 bits that are clocked into the input register on each rising edge of CLK are transferred to the appropriate latch. See Figure 2 for the timing diagram and Table 5 for the latch truth table.The maximum allowable serial clock rate is 20 MHz. This means that the maximum update rate possible for the device is 833 kHz or one update every 1.2 μs. This is more than adequate forsystems that have typical lock times in hundreds of microseconds. ADuC812 Interface Figure 38 shows the interface between the ADF411x family and the ADuC812 MicroConverter®. Since the ADuC812 is based on an 8051 core, this interface can be used with any 8051-based microcontroller. The MicroConverter is set up for SPI master mode with CPHA = 0. To initiate the operation, the I/O port driving LE is brought low. Each latch of the ADF411x family needs a 24-bit word. This is accomplished by writing three 8-bit bytes from the MicroConverter to the device. When the third byte has been written, the LE input should be brought high to complete the transfer.00392-038Figure 38. ADuC812 to ADF411x family Interface On first applying power to the ADF411x family, it requires three writes (one each to the R counter latch, the N counter latch, and the initialization latch) for the output to become active. I/O port lines on the ADuC812 are also used to control power-down (CE input) and to detect lock (MUXOUT configured as lock detect and polled by the port input). When operating in the mode described, the maximum SCLOCK rate of the ADuC812 is 4 MHz. This means that the maximum rate at which the output frequency can be changed is 166 kHz. ADSP-21xx InterfaceFigure 39 shows the interface between the ADF411x family and the ADSP-21xx digital signal processor. The ADF411x family needs a 21-bit serial word for each latch write. The easiest way to accomplish this using the ADSP-21xx family is to use the autobuffered transmit mode of operation with alternate framing. This provides a means for transmitting an entire block of serial data before an interrupt is generated.00392-039Figure 39. ADSP-21xx to ADF411x family Interface Set up the word length for 8 bits and use three memory locations for each 24-bit word. To program each 21-bit latch, store the three 8-bit bytes, enable the autobuffered mode, and write to the transmit register of the DSP . This last operation initiates the autobuffer transfer.。

ADF4351总结

ADF4351学习总结一,管脚说明CLK:串行时钟输入DATA:串行数据输入LE:加载使能CE:芯片使能SW:快速锁定开关Vp:电荷泵电源CPout:电荷泵输出CPGND:电荷泵接地AGND:模拟地AVdd:模拟电源AGNDVCO:VCO的模拟地RFoutA+:VCO输出RFoutA-:RFoutB-:TEMPRset:VREF:PDBRF:RFDVDD:MUXOUTSDVDD:锁相环路PFD频率RFVCODB28:频段选择;0,R0更新时执行VCO频段选择和相位同步(前提是R3中的相位再同步位使能)。

DB27:设置预分频器值。

0,预分频器值为4/5;1,预分频器值为8/9(RFout>3.6G)PHASE:设置RF输出相位,建议值为1.MOD:设置小数模数。

MOD=f(RFD)/RF输出端通道步进分辨。

[DB30:DB29]:设置噪声模式。

00:低噪声模式;11:低杂散模式。

DB25:参考倍频器。

0:倍频器禁用;1:倍频器使能(REFin<30MHZ)[DB24]:0:分频禁用;1:分频使能[DB23:DB14]:10位R分频器的值DB13:使能或禁用R4中的双缓冲[DB12:DB9]:用于设置电荷泵的电流I=25.5/RDB8:设置锁定检测功能(LDF),控制PFD周期数。

DB7:锁定检测精度位(DB7)设置锁定检测电路的比较窗口。

对于小数N分频,[DB7:DB8]=00;对于整数N分频,[DB7:DB8]=11.DB6:设置鉴相器极性。

0:反向有源滤波器1:无源环路滤波器或者同向有源环路滤波器。

DB51DB4:DB3:1:RFDB23DB22:1DB21DB18的占空0100DB23大DB11:1:VCO关断。

DB10:静音至检测到锁定(MTLD)。

1:切断RF输出级的电源电流,直到数字锁定检测电路检测到器件实现锁定为止。

DB9:设置辅助RF输出。

0:辅助RF输出为RF分频器的输出;1:辅助RF输出为VCO基频。

电压环控制策略

摘要在电力测试仪表及其校验装置中,往往要求高精度的工频恒流源,并且要求恒流源的输出幅值可调,市场上的恒流源在精度、稳定度、幅值、价格等方面无法同时满足要求,对于这一类恒流源往往需要自行设计。

本文首先给出了设计的性能参数,之后对恒流源的工作原理进行了分析,提出了高精度工频恒流源的设计方法,介绍了方案中关键电路的设计要点,详细说明了恒流源的单片机电路控制设计和软件校正的方法,最后给出试验数据和结论。

本人主要研制开发了电压信号源,提出了电压闭环控制策略。

通过电压信号控制电流源输出。

电流源最大输出功率在是300W,最大输出电流可以达到36A,输出频率可以在40至60Hz间变化。

先进的直接数字频率合成芯片(DDS)AD9851作为本文系统的信号发生芯片。

滤波电路采用了二阶有源低通滤波电路加一阶高通滤波电路的形式,有效滤除了AD9851输出信号时的高频噪音和直流分量,提高了正弦频率信号的质量。

所搭建的电路元件性能会受温度以及输出电流的影响,导致输出误差会大于0.1%。

针对这个问题,本文提出了电压环控制策略。

16位D/A芯片可以控制输出信号的增益,通过模拟乘法器对正弦波进行调制,就可以实现对正弦波幅值的控制。

最后,本人对电压电流转换电路、功率放大电路、硬件反馈电路构成的总电路进行了仿真,测了实验数据。

通过结果可以验证电流源设计的正确性,为整套装置的可行性提供了重要依据。

关键词:功率放大器,电压控制,模拟乘法器,模数转换,数模转换AbstractIn the power testing instrument and its calibration device,high precision constant current source is ofen needed .And constant current source output amplitude adjustment are also needed . Constant current source on the market can not meet the requirements of accuracy, stability, amplitude, prices, etc at the same time. This kind of constant current source is needed to be designed.This paper presents the performance parameters first ,then analyzes the working principle of the constant-current source ,puts forward the design method of the high-precision power-frequency constant-current source,introduces the key point of the significant circuit,gives the method of microcontroller circuit control design and software design ,finally gives test data and conclusionsMy work is mainly the research and development of the voltage source,and to propose closed loop voltage control strategy. The current source can output maximum power at 300W, the maximum current can reach 36A, the maximum output frequency can vary between 40 to 60Hz. In my paper,advanced direct digital synthesizer chip (DDS) AD9851 systems is the chip signal generator,its filter circuit is using the form of a second-order low-pass filter circuit and the first-order high-pass filter circuit in series, it can filter high-frequency noise and DC component effectively, and improve the quality of the sinusoidal frequency signal. The structure of circuit element properties will be affected by the temperature and output current.Thus,output signal can’t reach accuracy of 0.1%.In view of this problem, this paper introduces the voltage loop control strategy. 16-bit DA-chip can achieve the control of amplitude of sine wave. Through the modulation of the sine wave by analog multiplier , we can control the sine wave amplitude.Lastly, I operate a simulation of the total circuit which includes the voltage current converter, power amplifier, feedback hardware circuits, and gain the experimental data. The results can verify the correctness of the current source design ,and they provide an important basis for the feasibility of the entire device.Keyword:power magnifier,voltage control,analog multiplier,AD conversion,DA conversion目录摘要 (I)ABSTRACT ........................................................................................................................................... I I 1 绪论 (1)1.1恒流源的研究背景 (1)1.2恒流信号源的概念及技术指标 (1)1.3方案选择 (2)2 信号的产生 (5)2.1频率的控制 (5)2.1.1 设计基础 (5)2.1.2 频率控制的详细设计 (9)2.2AD9851输出滤波电路 (13)2.316位D/A转换芯片DAC8501 (15)2.4模拟乘法器 (17)2.4.1 模拟乘法器特性 (17)2.4.2 外部电路 (19)2.5档位切换电路 (20)3 功率放大 (22)3.1方案1 (22)3.2方案2 (22)4 信号反馈 (25)4.1信号调理电路 (25)4.2电压控制硬件工作原理 (27)4.3真有效值转换芯片的原理与应用 (27)4.3.1 AD637内部结构 (27)4.3.2 真有效值转换芯片标准电路 (28)4.3.3 高精度外部调整电路 (29)4.416位A/D采样芯片ADS8325 (30)4.5控制的策略 (33)5 软件设计 (34)5.1软件整体设计 (34)5.2中断设计 (34)6 仿真分析 (36)7 总结 (38)致谢 (39)附录 (40)附录1软件程序 (40)附录2电路总图 (53)参考文献 (54)1 绪论1.1 恒流源的研究背景恒流源是一种能向负载提供恒定电流的电源装置,输出的电流与外部影响无关,在外界电网电源产生波动和阻抗特性发生变化时仍能使输出电流保持恒定。

EADS 350MHz警用数字集群系统的创新

EADS 350MHz警用数字集群系统的创新1.引言欧洲宇航防务集团(EADS),作为国土安全防务与通信、商业飞机(空中客车)、直升飞机(欧洲直升机)及商业运载火箭(阿丽亚娜火箭)方面的全球领袖,于2005年4月宣布了对于诺基亚数字集群部门的并购,并于9月完成了并购,成立了欧洲最大的数字集群公司。

目前EADS已经在全球60多个国家提供了超过180个大型的数字集群网络,其中包括德国、芬兰、瑞典、比利时、西班牙等30个全国性的政府及公共安全网络,成为了TETRA市场首屈一指的领导者。

为了满足中国公安对于数字集群系统日益增长的需求,EADS于2006年5月率先推出了350MHz TETRA数字集群警用系统解决方案,该方案秉承了EADS系统的竞争优势:网络能够提供业内最高的安全性及可靠性,和业内业内首屈一指的高处理能力及高负荷的耐受能力;规模灵活,能够平滑扩展升级;提供全面的远程维护能力包括远程监控、远程参数及频率调整、远程软件升级,能够充分满足公共安全用户的要求,并提供更为经济方便的网络管理方式。

更重要的是,EADS的350MHz TETRA数字集群警用系统解决方案还在数字处理、软件无线电、移动终端等方面采用了多种创新技术,从而能够用最小的成本为中国公安用户实现最大的覆盖范围,达到最高的品质,能够充分满足公共安全用户的要求。

2.具备超大区覆盖和高速数据支持能力350MHz TETRA基站不同于公众移动通信网的容量受限,而数字集群专业移动通信网络特别是公共安全网络主要是覆盖受限的网络,网络规划主要考虑满足覆盖的要求,但是数字集群的基站通常均为小区覆盖。

当进行面状覆盖设计时,需要较多的基站才能满足覆盖要求。

由于网络中的用户数量相对较少,平均每个用户的覆盖成本相对较高。

因此,利用有限的资金达到最佳的覆盖范围一直都是公共安全用户和系统设计者考虑的关键问题之一。

基于对公共安全用户需求的考虑,EADS利用自身的技术优势,结合了目前数字处理技术和无线领域的最佳成果,研发了TB3 TETRA基站。

ADF4106的应用

摘要:ADF4106是ADI公司生产的高集成度PLL频率合成器,该芯片具有宽频带、低噪声、低功耗及低成本等优点。

本文介绍了该芯片的主要功能及其在RF系统中的应用。

关键词:双模锁相频率合成技术;可编程分频器;相位噪声;频率分频率引言频率合成器作为一种相位锁定装置,是一种频率稳定度较高的离散间隔型频率信号发生器。

它被广泛地应用在通信、雷达、仪器仪表、高速计算机及导航系统中。

在移动通信中,要求低功耗、低成本、大容量、高频频率合成芯片,为满足在输出较高频率的同时又能获得较小的输出频率间隔,大多采用双模技术的锁相环频率合成技术。

这里较为适用的合成芯片之一就是ADI公司的ADF4000系列,它不仅覆盖了0到3GHz的宽频率范围,而且ADF4106芯片最高工作频率可达6G Hz,ADF4107芯片最高工作频率可达7GHz。

ADF4106芯片的简介:ADF4106的主要特性如下:◆6.0GHz带宽;◆2.7V~3.3V电源电压;◆离散电荷泵VP在3V系统中可进行大范围调整;◆可编程双模分频器,P/P+1值分别为8/9、16/17、32/33、 64/65;◆可编程电荷泵流;◆模拟和数字锁相;◆-40 C ~+85 C工作温度;◆TSSOP-16、CSP-20封装。

ADF4106主要由一个低噪声数字鉴相器(PDF)、一个精密电荷泵、一个可编程参考分频器、可编程A(6bit)及B(13bit)分频计数器和一个双模分频器(P/P+1)构成。

在这里,随模式控制高、低电平的不同,双模分频器采用两个不同的分频模数P+1和P。

双模分频器的输出同时驱动两个可编程分频器,他们分别预置在A和B(A<B),并进行减计数。

在除A和除B分频器未计数到零时,模式控制为高电平,双模分频器输出频率为f0/(P+1)。

在输入A(P+1) 个周期之后,除A分频器计数到零,将模式控制变为分频器前面的与门使其停止计数。

此时,除B分频器还有B-A个数,双模分频器的模数变为P,输出频率为f0/P。

AMC7135-350mA-恒流LED驱动电路

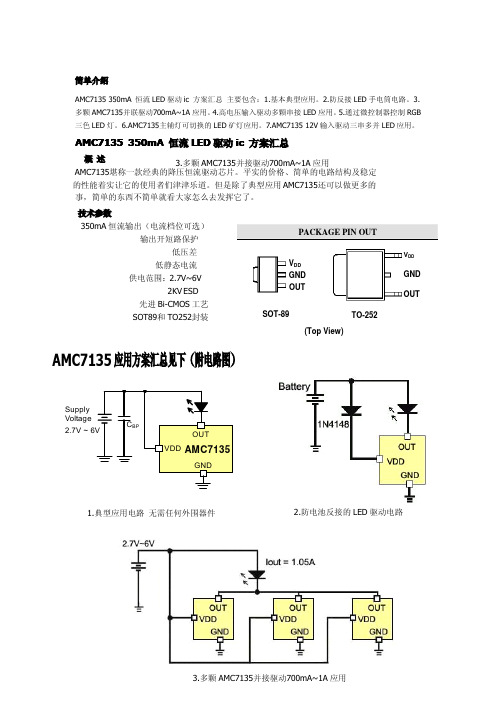

简单介绍AMC7135350mA 恒流LED 驱动ic 方案汇总主要包含:1.基本典型应用。

2.防反接LED 手电筒电路。

3.多颗AMC7135并联驱动700mA~1A 应用。

4.高电压输入驱动多颗串接LED 应用。

5.通过微控制器控制RGB 三色LED 灯。

6.AMC7135主辅灯可切换的LED 矿灯应用。

7.AMC713512V 输入驱动三串多并LED应用。

AMC7135350mA 恒流LED驱动ic 方案汇总概述AMC7135堪称一款经典的降压恒流驱动芯片。

平实的价格、简单的电路结构及稳定的性能着实让它的使用者们津津乐道。

但是除了典型应用AMC7135还可以做更多的事,简单的东西不简单就看大家怎么去发挥它了。

技术参数350mA 恒流输出(电流档位可选)输出开短路保护低压差低静态电流供电范围:2.7V~6V2KV ESD先进Bi-CMOS 工艺SOT89和TO252封装AMC7135应用方案汇总见下(附电路图)1.典型应用电路无需任何外围器件2.防电池反接的LED 驱动电路PACKAGE PIN OUTSupply VoltageV DD GND OUTSOT-89V DDGND OUTTO-252(Top View)3.多颗AMC7135并接驱动700mA~1A 应用3.多颗AMC7135并接驱动700mA~1A 应用4.输入12V驱动3颗串接白光LED应用(如负载改为红光LED VF=2V,该应用则可串5颗LED)5.通过微控制器及on/off装置配合7135实现RGB三色LED亮暗程度的控制。

达到多彩混色的功能。

6.矿灯所需的主灯及辅灯可切换照明电路7.输入电压12V ,采用78L05降压,配合7135实现1W LED 3串多并电路RECOMMENDED OPERATING CONDITIONSParameter Symbol Min Typ Max UnitSupply Voltage V DD 2.7 6 V Output Sink CurrentI OUT 400 mAOperating Free-air Temperature Range T A -40 +85℃DC ELECTRICAL CHARACTERISTICSV DD =3.7V, T A =25°C, No Load, ( Unless otherwise noted)Parameter Symbol Condition Min Typ Max UnitApplyPinV OUT =0.2V 340 360 380mA Output Sink Current I SINKV OUT =0.2V, Rank A 300 320 340 mA Load Regulation V OUT =0.2V to 3V3mA/VLine RegulationV DD = 3V to 6V,V OUT =0.2V3 mA/V Output Dropout Voltage V OUTL120mVOUTSupply Current ConsumptionI DD200 uAVDDNote 1: Output dropout voltage: 90% x I OUT @ V OUT =200mVVDDOUTGND BLOCK DIAGRAM。

ADF4110中文数据手册

班级040831学号04083104本科毕业设计(论文)外文资料翻译毕业设计题目大功率对讲机接收电路的设计外文资料题目ADF4110系列芯片数据手册学院机电工程学院专业自动化学生姓名庄伟源指导教师姓名李西安ADF4110系列芯片手册 1RF PLL频率合成器ADF4110、ADF4111、ADF4112、ADF4112特征ADF4110: 550 MHzADF4111: 1.2 GHzADF4112: 3.0 GHzADF4113: 4.0 GHz2.7 V到5.5 V电源独立的电荷泵电源(VP)允许扩展调谐电压,3 V系统可编程双模分频器8/9, 16/17,32/33, 64/65可编程电荷泵电流可编程Antibacklash脉宽3-Wire串行接口模拟和数字锁定检测硬件和软件关断模式应用无线电台(GSM, PCS, DCS,基站CDMA,的WCDMA)无线手机(GSM, PCS, DCS, CDMA,的WCDMA)无线LANS通信测试设备CATV设备概述该频率合成器可用于ADF4110 系列实施的上变频和下本振,无线接收器和发射器变频部分.他们由一个低噪声数字PFD(相位频率检测器),一个精密电荷泵,一个可编程参考分频器,可编程A和B计数器和一个双模预置分频器性(P / P+1).在A (6-bit)和B (13-bit)柜台,联与双模分频器性(P / P+1),实现一N 分(N = BP + A).此外,14-bit引用计数器(R柜),允许在PFD将REFIN频率可选输入.如果使用合成器与外部环路滤波器和VCO(压控振荡器)可以实现一个完整的PLL(锁相环)。

所有片内寄存器的控制是通过一个简单的3-wire接口。

该器件采用功率范围从2.7 V供应5.5 V和断电时,可在不使用.功能框图对应部分翻译:14-bit R counter 14位R计数器;REFERENCE 基准;PHASE FREQUENCY DETECTOR 鉴频鉴相器;CHARGE PUMP 充电泵;R COUNTER LATCH R计数器锁存;24-BIT INPUT REGISTER 24位输入寄存器;FUNCTION LATCH 功能锁存;A, B COUNTER LATCH A、B计数器锁存;LOCK DETECT 锁定检测;CURRENT SETTING 1 电流设置1;CURRENT SETTING 2 电流设置2;ADF4110系列芯片手册2FROM FUNCTION LATCH 来自功能锁存; PRESCALER P/P +1 前置分频器P/P+1; 13-BIT B COUNTER 13位B 计数器;REV:由ADI 公司提供的信息被认为是准确和可靠.但是,没有承担责任的模拟装置 使用,也没有侵犯任何专利或其它第三方权利这可能是由于它的使用.没有获发牌照以暗示或否则根据ADI 公司的任何专利或专利的权利.其中技术的方式,P.O.盒9106,诺伍德,MA 02062-9106, U.S.A. 电话:781/329-4700万维网网址: 传真:781/326-8703 ©模拟装置,Inc., 2000ADF4110系列芯片手册 3ADF4110/ADF4111/ADF4112/ADF4113——规格(AVDD = DVDD = 3 V 10%, 5 V 10%; AVDD ≤ VP ≤ 6.0 V; AGND = DGND = CPGND = 0 V; RSET = 4.7 k ; TA = TMIN to TMAX 除非额外注释)参数B电压B夹单位测试条件/评论RF特征(3 V)RF输入频率ADF4110ADF4110ADF4111ADF4112ADF4112ADF4113RF输入灵敏度最大允许预分频器输出频率33RF特征(5 V)RF输入频率ADF4110ADF4111ADF4112ADF4113ADF4113RF输入灵敏度最大允许预分频器输出频率45/55025/5500.045/1.20.2/3.00.1/3.00.2/3.7–15/016525/5500.025/1.40.1/3.00.2/3.70.2/4.0–10/020045/55025/5500.045/1.20.2/3.00.1/3.00.2/3.7–15/016525/5500.025/1.40.1/3.00.2/3.70.2/4.0–10/0200MHz最小/最大MHz最小/最大GHz最小/最大GHz最小/最大GHz最小/最大GHz最小/最大dBm最小/最大MHz 最大MHz最小/最大GHz最小/最大GHz最小/最大GHz最小/最大GHz最小/最大dBm最小/最大MHz 最大参见图输入电路25.使用低频率的方波输入电平= –10 dBm输入电平= –10 dBm输入电平= –10 dBm使用低频率的方波.输入电平= –5 dBm将REFIN特征将REFIN输入频率参考输入灵敏度4输入电容将REFIN将REFIN输入电流0/100–5/010±1000/100–5/010±100MHz最小/最大dBm最小/最大pF 最大µA最大交流耦合.当直流耦合:0到V DD最大(CMOS兼容)鉴相器鉴相器频率55555MHz 最大电荷泵I CP吸入/源高价值低值绝对精度R SET范围56252.52.7/1056252.52.7/10mA typµAtyp% typkΩ typ可编程:见表V随着R SET= 4.7 kΩ随着R SET= 4.7 kΩ见表VADF4110系列芯片手册4I CP3-State泄漏电流汇和源电流匹配I CP主场迎战V CPI CP与温度的关系121.52121.52nA typ% typ% typ% typ0.5 V≤V CP≤V P– 0.50.5 V≤V CP≤V P– 0.5V CP= V P/2逻辑输入V INH,输入高电压V INL,输入低电压I INH/I INL,输入电流C IN,输入电容0.8×DV DD0.2×DV DD±1100.8×DV DD0.2×DV DD±110V 最小V 最大µA最大pF 最大逻辑输出V OH,输出高电压V OL,输出低电压DV DD– 0.40.4DV DD– 0.40.4V 最小V 最大I OH= 500µAI OL= 500µA电力用品AV DDDV DDV PI DD6(AI DD+ DI DD) ADF4110ADF4111ADF4112ADF4113I P低功耗的睡眠模式2.7/5.5AV DDAV DD/6.05.55.57.5110.512.7/5.5AV DDAV DD/6.05.55.57.5110.51V分钟/视频最大V分钟/视频最大mA 最大mA 最大mA 最大mA 最大mA 最大µAtypAV DD≤V P≤6.0 V见图22和234.5 mA典型4.5 mA典型6.5 mA典型8.5 mA典型T A= 25°C噪声特性ADF4113相位噪声楼7相位噪声性能8ADF4110: 540 MHz输出9 ADF4111: 900 MHz输出10 ADF4112: 900 MHz输出10 ADF4113: 900 MHz输出10 ADF4111: 836 MHz输出11 ADF4112: 1750 MHz输出12 ADF4112: 1750 MHz输出13 ADF4112: 1960 MHz输出14 ADF4113: 1960 MHz输出14 ADF4113: 3100 MHz输出15杂散信号–171–164–91–87–90–91–78–86–66–84–85–86–171–164–91–87–90–91–78–86–66–84–85–86dBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typdBc/Hz typ@ 25千赫频率PFD@ 200千赫频率PFD@ VCO输出@ 1 kHz偏移和200千赫频率PFD@ 1 kHz偏移和200千赫频率PFD@ 1 kHz偏移和200千赫频率PFD@ 1 kHz偏移和200千赫频率PFD@ 300 Hz失调和30千赫频率PFD@ 1 kHz偏移和200千赫频率PFD@ 200 Hz失调和10千赫频率PFD@ 1 kHz偏移和200千赫频率PFD@ 1 kHz偏移和200千赫频率PFD@ 1 kHz偏移频率和1 MHz PFDADF4110系列芯片手册 5ADF4110: 540 MHz输出9 ADF4111: 900 MHz输出10 ADF4112: 900 MHz输出10 ADF4113: 900 MHz输出10 ADF4111: 836 MHz输出11 ADF4112: 1750 MHz输出12 ADF4112: 1750 MHz输出13 ADF4112: 1960 MHz输出14 ADF4113: 1960 MHz输出14 ADF4113: 3100 MHz输出15–97/–106–98/–110–91/–100–100/–110–81/–84–88/–90–65/–73–80/–84–80/–84–80/–82–97/–106–98/–110–91/–100–100/–110–81/–84–88/–90–65/–73–80/–84–80/–84–80/–82dBc typdBc typdBc typdBc typdBc typdBc typdBc typdBc typdBc typdBc typ@ 200千赫/ 400 kHz和200千赫频率PFD@ 200千赫/ 400 kHz和200千赫频率PFD@ 200千赫/ 400 kHz和200千赫频率PFD@ 200千赫/ 400 kHz和200千赫频率PFD@ 30千赫/ 60 kHz和30千赫频率PFD@ 200千赫/ 400 kHz和200千赫频率PFD@ 10千赫/ 20 kHz和10千赫频率PFD@ 200千赫/ 400 kHz和200千赫频率PFD@ 200千赫/ 400 kHz和200千赫频率PFD@ 1 MHz/2 MHz和1 MHz PFD频率附注:1工作温度范围为如下:B版:-40°C至+85°C。

美能达250_350复印机错误代码c2557解决方法

美能达250_350复印机错误代码c2557解决方法美能达复印机调整代码1:美能达1052拌载体(1080)停止---0---停止--1---1---8复印机键2:美能达2030--1054 拌载体计数器--停止00--停止--01--1--1--8--复印机3:美能达2030调暴光计数器--停止--00--停止--01----1---f---3--F---5--4: 维修模式1:暴光( F )2:技术( C)C:--4 0,不给定维修呼叫提示1,给定维修呼叫提示C--5 0.保养计数器1,可以进行2,无法进行C--7 0,可以复印( 无粉)1,禁止复印维修模式:4,保养计数器5,卡纸6,故障计数器7,零件使用期限松下:KX系列功能(菜单)--#9000--*550--启动理光5100传真机功能--61998--立刻YES--01 YES--0 YES--功能--清日板--编辑--重启动联想6212设置清零功能键开机*--2864--01--四灯同时亮--99--退出夏普7370调暴光c---00---c---46---复印---数字(0~99)1116拌载体C--插入--0--插入--25--复印1116调暴光C--插入--0--插入--46--复印--1--复印--(0~99)2030调电压A, C--插入--0--插入--44--复印--2--复印--204--CAB, C--插入--0--插入--44--复印--3----复印--(0~99)--CA美能达3170复印机维修代码检测说明F1:过纸检测,无须预热结束就可以进行,复印机计数装置不工作(按下clear/stop可停止);F2:充电高压输出调整(工厂设定),不要调整(运行30秒,或按clear/stop中断);F3:手动方式下曝光灯电压设定,按下复印键开始扫描并点亮曝光灯(运行30秒,或按clear/stop中止)F5:AE传感器基准电压设定,按下复印键开始扫描并点亮曝光灯(运行30秒,或按clear/stop中止);F6:工厂设定(扫描动作结束)F8 ·ATDC传感器调整显影装置工作,显影器搅动(运行5分钟,或按clear/stop中断)F9:工厂设定(运行30秒,或按clear/stop停止)调整方式:4-1. 调整(1)说明(光学系统的调整)A--0 设定镜头焦距(确定镜头焦距的变动值)A--1 调整镜头等倍位置(调整镜头原始与等倍位置距离)A--2 调整反射镜等被位置(调整反射镜原始位置与等倍位置距离)A--3 调整纵向倍率(通过调整扫描速度来调整)A--4 等倍纸头位置调整(在等倍方式调整纸头位置)A--5 放大图象纸头位置调整(在放大方式200%调整像的纸头)4-2. 调整(2)说明(调整黑/彩色复印的重叠宽度)B--2 调整黑色/彩色重叠部分(黑显影器)(调整彩色—>黑色重叠部分的宽度)B--3 调整黑色/彩色重叠部分(彩色显影器)(调整黑色—>彩色重叠部分的宽度)选择方式:5-1. 选择说明C--0 自动复位(选择是否自动复位功能)C--1 PC鼓干燥(开机后,选择复印机是否自动进入鼓干燥方式)C--3 尺寸显示(记录选择纸张的尺寸大小)C--4 总计数器(以复印过程计数或以纸张尺寸大小计数)C--6 消除边框(选择是否消除边框)C--7 设定ATDC控制量(设定ATDC达何种量)C--8 设定ATDC控制量(设定ATDC达何种量)C--9 -------(工厂设定)5-2.选择方式及其设定选择代码确定后,可通过如下相关值今昔功能所需要的设定:a)代码NO.C—0(自动复位)0 建立自动复位功能1 取消自动复位功能*如果设定相关值为“0”:通常,在10分钟内为装纸的情况下,1分钟内就自动复位b)代码NO.C—1(鼓干燥)0 开机后,复印机不能自动进入鼓干燥 1 开机后,复印机自动进入鼓干燥方式*如果设定相关值为“1”:复印机在预热完成之后,还要运转3分钟c)代码NO.C—3(尺寸显示)0 不能记录 1 A3 2、3 A3、A4 4 A6d)代码NO.C—4(总计数器)0 按复印过程计数(每复印1张就记录一次) 1 按复印纸尺寸计数(A3记2次,其他记1次)e)代码NO.C—6(消除边框)0 不能消除 1 图象大约3mm边框消除f)代码NO.C—7(ATDC黑色控制量)0 相当于T/C 4.5% 1 相当于T/C 5% 2 相当于T/C 5.5% 3 相当于T/C 6% 4 相当于T/C 6.5% 5 相当于T/C 7% 6 相当于T/C 7.5% 7 相当于T/C 8%f)代码NO.C—8(ATDC彩色控制量)与C—7同故障代码表:C1 负压风机失灵·负压风机应告诉运转,若连续10秒停止不动,边会被检测到C4 曝光灯失灵·曝光灯在接通时却保持断开状态10秒,或应断开时而持续接通10秒,均会检测到C5 预热故障·在主开关接通后60秒内,定影温度达不到100摄氏度·在电源开关接通120秒之内,定影温度到达100摄氏度,热辊温度达不到185摄氏度C6 光学系统失灵·在200毫秒内,SCP没能收到从CPU来的M1B信号·初始程序后11.32秒内,扫描车不在原位,而扫描车原位探测器PC4不能进入低电平·予扫描时,镜头往缩小方向移动后7.38秒,而镜头原位探测器PC5不能进入高电平;或在予扫描后,镜头移动到等倍位置7.38秒,而PC5还不能进入低电平。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

将高性能RF信号链集成至更小空间Time:2012-04-12 17:44:40 Author: Source:ADI公司空间!有待探索的最后一片疆域,将高性能RF信号链集成至更小空间的解决方案是行业需求也是未来趋势。

日趋小巧紧凑的设备在实验室里有一台Rohde & Schwarz FSIQ频谱分析仪,它的一侧贴着一个标签:“两人抬”。

如果我们让时间快进十年,可能只需要一只手就能拎起一台先进的频谱分析仪。

这虽然有点夸张,但保守地说,肯定不需要“两人抬”。

整个行业似乎都在重复这一幕,设备变得越来越小、越来越紧密,或者保持尺寸不变的同时增加更多功能。

这增大了设备设计的难度。

更严峻的问题是,冷却风扇却在设备中用得越来越少,这就带来了降低设备功耗和自热的压力。

如图1所示,包括现代通信设备在内的设备越来越小巧紧凑。

图1 小巧紧凑的设备考虑无线收发器的设计方法时,必须尽早决定是否以分立方式构建电路。

要实现蓝牙、Zigbee或GPS等常用无线电标准,采用分立方案意义不大。

同样的道理,高度集成的芯片组除了它的本来的应用外,几乎没有其他用处。

一般从空间角度考虑,高度集成的芯片组较佳,但往往灵活性不足,而且性能低于采用分立器件实现的电路。

这自然引出下面的问题:是否有一个两全其美的解决方案?也就是说,它既有一定的集成度,可以节省空间,同时能为设计人员提供适当的灵活性。

必须考虑RF信号链中典型器件的相对尺寸。

现代有源器件,例如IQ调制器、IQ 解调器和混频器等,通常采用MLF封装,典型尺寸为16mm2~36mm2。

VCO和SAW滤波器相对较大。

100mm2的VCO并不罕见,SAW滤波器的表面面积常常达到35mm2。

LO合成技术的演变基于PLL的频率合成器有两个主要器件:锁相环(PLL)和压控振荡器(VCO)。

由于分立VCO的尺寸相对较大,因此IC设计界非常希望将VCO集成到PLL中。

虽然将VCO集成到IC芯片并不是特别困难,但要集成高质量VCO并非易事。

所谓高质量,是指信号的相位噪声或频谱纯度。

较低的VCO相位噪声可以改善接收机灵敏度以及发射和接收信号的误差矢量幅度。

图2所示比较多款集成到IC中的VCO相位噪声性能。

1MHz偏移时-135dBc/Hz的相位噪声可以与分立VCO的性能相媲美。

图2 多款集成到IC中的VCO相位噪声性能ADF4350和ADF4351,这些是集成VCO的PLL系列器件。

除了相位噪声非常低以外,这些器件中的VCO库具有完整的倍频程范围。

将宽VCO频率范围与一组分频器结合,便可获得137.5 MHz~4.4 GHz的连续工作范围。

对于ADF4351,器件中还有额外的分频器,因此其最低工作频率为35 MHz。

ADF4351 PLL的闭环相位噪声性能如图3所示,VCO工作频率为4.4GHz。

闭环相位噪声由上方的深蓝色曲线表示。

随着分频器相继开启,输出频率不断降低;频率每降低一半,相位噪声性能提高6 dB。

图3 ADF4351 PLL的闭环相位噪声性能VCO库提供一个倍频程的调谐范围,利用分频器阵列实现4.4GHz~35MHz的工作范围。

器件尺寸5mm×5mm,主要外部元件包括电源去耦电容和环路滤波器。

VCO和分频器库均集成于片上,剩余的外部器件只有电源去耦电容和外部环路滤波器。

因此,集成VCO将能节省相当大的空间。

接收信号链的演变接收机架构如何演变,以及对这些电路的尺寸有何影响呢?回顾几年前,我们发现,那时的典型分集接收机已经具有一定的集成度。

但在混频器的RF侧,LNA 和可变衰减器全部是分立器件。

混频器的LO则利用外部VCO实现。

现在我们展望几年后的情况,对于大多数应用,带分立VCO的PLL可以由单个集成器件所取代。

此外,混频器RF侧的集成度更高。

后置LNA放大器与可变衰减器集成在一起。

这可以称作水平集成,即信号链中的相邻器件合并到一个封装中。

但是,可以注意到,前端LNA仍是一个独立器件。

这是因为,设计LNA的PHEMPT工艺并不是特别有利于与数字步进衰减器集成。

当我们集成分集接收机中的器件时,还有一个选项可以考虑,即所谓“垂直集成”。

如图4所示,我们选择了双通道ADC和双通道ADC驱动器,但使用两个独立的混频器。

图4 中频采样信号链的演变垂直集成时必须考虑的一个重要因素是器件之间的寄生耦合或泄漏。

比如,一个双通道混频器的输入至输入泄漏,值得注意的是泄漏水平随输入频率提高而提高。

这是非常典型的现象,因为寄生耦合路径的阻抗随频率提高而降低。

所以,混频器的RF侧通常不采用垂直集成方式。

就混频器而言,一般都会提供单通道和双通道版本,设计人员可以决定所需的集成度。

近年来,业界热衷于用直接变频或零中频接收机来取代常用的中频采样架构,如图5所示。

零中频接收机利用IQ解调器,将RF信号一步下变频至基带。

这种架构最吸引人之处在于,它无需前端镜像滤波器以及尺寸相对较大、损耗较高的IF SAW滤波器。

这种方法具有空间优势,但对频率非常敏感。

由于无需担心IF 和频率规划,因此接收机的频率范围仅受PLL、IQ解调器和前端LNA的工作范围的限制。

宽带IQ解调器和PLL的选择范围广,所以这种方法非常适合可再配置的无线电应用。

图5 直接变频接收架构采用直接变频具有潜在的空间优势。

在分集中频采样接收机和分集零中频接收机的布局中值得注意的是,空间使用率与外部无源组件密切相关,与其他方面的关系则不大。

中频采样接收机具有一个长而窄的结构,这是因为它需要两个滤波器级,一个是SAW滤波器,另一个是ADC之前的抗混叠滤波器。

因此,零中频接收机只需一个滤波器,而中频采样接收机则需要两个滤波器。

从性能和功耗两方面比较这两种架构,在ADIsimRF中,对一个典型中频采样接收机所做的信号链分析,在此增益设置下,输入IP3和噪声系数分别为27.8 dBm 和4.7 dB,功耗为2.2 W。

如果在ADIsimRF中仿真一个等效的零中频接收机,输入IP3大致相同,但噪声系数为2.1 dB,相对较低。

这主要是因为零中频架构中不存在高损耗SAW滤波器。

功耗为3.17 W,相对较高。

可以把这归因于需要两个ADC和两个基带放大器来驱动它,相比之下,中频采样接收机中只需要一个。

虽然中频采样ADC的功耗通常高于基带采样ADC,但由于需要两个基带ADC和两个ADC驱动器,因此功耗优势不复存在。

然而,这里有一个因素未被考虑,那就是中频采样接收机所需的数字下变频电路的功耗。

这一因素可能会使两种方法的功耗大致相当。

若试图去除中频采样接收机中的某些可集成器件。

这里,有源混频器集成了小数N分频PLL和窄带VCO。

除了驱动混频器以外,LO还能供外部使用。

也可以由外部LO源驱动。

零中频接收机无需IF SAW滤波器来抑制不良的带内和带外信号。

在零中频接收机中,消除所有不良信号的任务落在ADC之前的抗混叠滤波器肩上。

ADRF6561这款器件提供50dB的可变增益,以及以1dB步进变化的1MHz~30MHz可编程滤波器带宽,所有这些特性都在一个5mm×5mm LFCSP封装内实现。

发射信号链的演变零中频发射机的功能框图如图6所示。

对于500MHz~6GHz范围的无线电频率,使用IQ调制器直接跳变到RF已非常流行。

发射端采用零中频比接收端更普遍,接收端仍以使用IQ解调器的中频采样或中频到基带转换为主。

图6 零中频发射机的功能框图本例中,发射机还包括一个回送电路,它监控功率放大器的失真,并向基带中运行的数字预失真算法提供反馈。

这种配置不是真正的零中频,而是所谓的复中频,DAC输出为112 MHz。

因此,可以使用单个LO来驱动IQ调制器和回送混频器。

如果使用集成PLL和VCO的IQ调制器,可以再进一步,除了用于IQ调制器以外,还可以从芯片中引出LO信号以驱动DPD混频器。

总结首先,针对存在专用芯片组的常用无线标准,设计分立电路毫无疑问是不可取的。

采用分立器件进行设计时,我们拥有相当大的灵活性,但要付出功耗更高的代价。

使用直接变频发射机和接收机可以节省空间,但与传统收发器相比,功耗节省可能不大。

双通道器件确实可以节省空间,但须确保通道间泄漏在合理范围内。

如果一个集成VCO的PLL可提供合理水平的相位噪声,那么这将是分立RF电路设计中最能节省空间的地方之一。

问答选编问:ADI公司的RF信号链解决方案具体包括哪些内容?答:包括框架构建、各组件选型、链路参数设计等。

问: RF信号链与以往的产品差别是什么呢?答:考虑无线收发器的设计方法时,我们必须尽早决定是否以分立方式构建电路。

要实现蓝牙、Zigbee或GPS等常用无线电标准,采用分立方案意义不大。

同样的道理,高度集成的芯片组除了它的本来的应用外,几乎没有其他用处。

一般从空间角度考虑,高度集成的芯片组较佳,但往往灵活性不足,而且性能低于采用分立器件实现的电路。

这自然引出下面的问题:是否有一个两全其美的解决方案?也就是说,它既有一定的集成度,可以节省空间,同时能为设计人员提供适当的灵活性。

问:抗干扰问题怎么解决?在集成度较高的方案中,集成VCO的好处是什么?答:对于集成度较高的方案而言,很多接口都是内部实现的。

可以省去了外部接口电路,自然外围电路就少了很多,集成VCO,可以让客户的设计省去了外围的的VCO电路等。

问:在小芯片上实现高集成是否会导致各单元电路间的相互干扰?答:电路干扰是肯定存在的,但是ADI的完整的芯片集成设计技术可以更好的降低干扰,使集成IC的性能可以满足系统性能的指标要求。

问:为了节约成本和降低体积,兼容各项3G标准,有一种新的可调谐技术,ADI 公司在现有的产品是否有这方面的产品?答:ADI宽带的PLL产品ADF4350可以支持软件调整频率,ADI的宽带调制器ADL5375和DVGA ADL5240/3可以支持宽带工作,ADI的宽带调谐混频器ADL5811/2 可以支持软件调整频率和端口匹配。

问:请问高性能RF信号链的主要特性有哪些?答:主要特性为更好的动态范围,噪声性能和谐波及杂散的抑制特性,以及灵活的接口和应用性。

目前,ADI新的产品基本采用差分信号,这样很好的满足了这些需求。

问:巴伦接口是指什么?答:巴伦是BALUN的音译,其含义是指平衡——不平衡变换器。

巴伦实现的接口间转换,及单端信号转换为差分信号,或将差分信号转换为单端信号。

问:本振的性能怎样?能否满足RF信号链要求?答:是可以满足RF信号链的需求的。

ADF4360是集成VCO的整数N分频锁相环产品,ADF4350是集成VCO的宽带小数N分频锁相环产品,其频率范围从137MHz~4.4GHz。

即将推出的还有ADF4351,将拥有更好的相噪性能和更宽的频率输出范围。

问:RF解决方案在PCB设计时需要注意什么?答:主要注意传输线特征阻抗的匹配,接地,电源去耦等因素。