锁相环调频和解调实验,频率合成器实验

锁相环调频和解调实验,频率合成器实验

实验11 锁相调频与鉴频实验一、实验目的1.掌握锁相环的基本概念。

2.了解集成电路CD4046的内部结构和工作原理。

3.掌握由集成锁相环电路组成的频率调制电路/解调电路的工作原理。

二、预习要求1.复习反馈控制电路的相关知识。

2.锁相环路的工作原理。

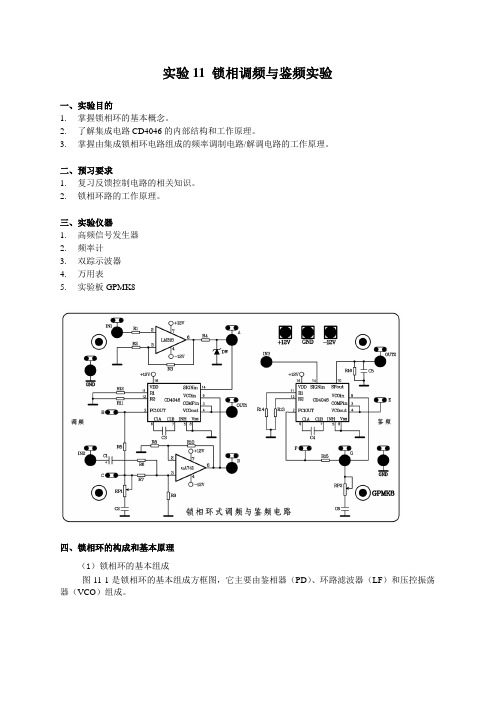

三、实验仪器1.高频信号发生器2.频率计3.双踪示波器4.万用表5.实验板GPMK8四、锁相环的构成和基本原理(1)锁相环的基本组成图11-1是锁相环的基本组成方框图,它主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)组成。

图11-1 锁相环的基本组成① 压控振荡器(VCO )VCO 是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO 上的电压。

所谓压控振荡器就是振荡频率受输入电压控制的振荡器。

② 鉴相器(PD )PD 是一个相位比较器,用来检测输出信号0V (t )与输入信号i V (t )之间的相位差θ (t),并把θ(t)转化为电压)(t V d 输出,)(t V d 称为误差电压,通常)(t V d 作为一直流分量或一低频交流量。

③ 环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在)(t V d 中产生的无用组合频率分量及干扰,产生一个只反映θ(t)大小的控制信号)(t V C 。

4046锁相环芯片包含鉴相器(相位比较器)和压控振荡器两部分,而环路滤波器由外接阻容元件构成。

(2)锁相环锁相原理锁相环是一种以消除频率误差为目的反馈控制电路,它的基本原理是利用相位误差电压去消除频率误差。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使)(t V O 与)(t V i 的相位差θ(t)发生变化,该相位差经过PD 转换成误差电压)(t V d 。

此误差电压经过LF 滤波后得到)(t V c ,由)(t V c 去改变VCO 的振荡频率,使其趋近于输入信号的频率,最后达到相等。

锁相环实验报告

锁相环实验报告锁相环实验报告一、实验目的本次实验的目的是了解锁相环(PLL)的原理和应用,掌握PLL电路的设计和调试方法,以及了解PLL在通信系统中的应用。

二、实验原理1. PLL原理锁相环是一种基于反馈控制的电路,由比例积分环节、相位检测器、低通滤波器和振荡器等组成。

其基本原理是将输入信号与参考信号进行比较,并通过反馈调整振荡频率,使得输入信号与参考信号同步。

2. PLL应用PLL广泛应用于通信系统中,如频率合成器、时钟恢复器、数字调制解调器等。

三、实验设备和材料1. 实验仪器:示波器、函数发生器等。

2. 实验元件:电阻、电容等。

四、实验步骤1. 搭建PLL电路并连接到示波器上。

2. 调节函数发生器输出正弦波作为参考信号,并将其输入到PLL电路中。

同时,在函数发生器上设置另一个正弦波作为输入信号,并将其连接到PLL电路中。

3. 调节PLL参数,包括比例积分系数和低通滤波器截止频率等,使得输入信号与参考信号同步。

4. 观察示波器上的输出波形,记录下PLL参数的取值。

五、实验结果与分析1. 实验结果通过调节PLL参数,成功实现了输入信号与参考信号的同步,并在示波器上观察到了稳定的输出波形。

记录下了PLL参数的取值,如比例积分系数和低通滤波器截止频率等。

2. 实验分析通过本次实验,我们深入了解了锁相环的原理和应用,并掌握了PLL电路的设计和调试方法。

同时,我们也了解到PLL在通信系统中的重要作用,如时钟恢复、数字调制解调等。

六、实验结论本次实验成功地实现了输入信号与参考信号的同步,并掌握了PLL电路的设计和调试方法。

同时也加深对于PLL在通信系统中应用的认识。

七、实验注意事项1. 在搭建电路时应注意接线正确性。

2. 在调节PLL参数时应注意逐步调整,避免过度调整导致系统失控。

3. 在观察示波器输出波形时应注意放大倍数和时间基准设置。

-锁相环的频率合成器课程设计报告

湘潭大学基于锁相环的频率合成器课程设计报告学院:姓名:学号:班级:指导教师:日期:2014年11月12 日同组人:朱翊目录一、设计和制作任务 (3)二、主要技术指标 (3)三、确定电路组成方案 (3)四、设计方法 (4)(一)、振荡源的设计 (4)(二)、N分频的设计 (4)(三)、1KHZ标准信号源设计(即M分频的设计) (5)五、锁相环参数设计 (6)六、调试步骤 (7)七、实验小结 (8)八、电路板制作 (8)九、心得体会 (9)附录:各芯片的管脚图 (10)锁相环CD4046设计频率合成器内容摘要:频率合成是以一个或少量的高准确度和高稳定度的标准频率作为参考频率,由此导出多个或大量的输出频率,这些输出的准确度与稳定度与参考频率是一致的。

在通信、雷达、测控、仪器表等电子系统中有广泛的应用,频率合成器有直接式频率合成器、直接数字式频率合成器及锁相频率合成器三种基本模式,前两种属于开环系统,因此是有频率转换时间短,分辨率较高等优点,而锁相频率合成器是一种闭环系统,其频率转换时间和分辨率均不如前两种好,但其结构简单,成本低。

并且输出频率的准确度不逊色与前两种,因此采用锁相频率合成。

关键词:频率合成器CD4046一、设计和制作任务1.确定电路形式,画出电路图。

2.计算电路元件参数并选取元件。

3.组装焊接电路。

4.调试并测量电路性能。

5.写出课程设计报告书二、主要技术指标1.频率步进 1kHz2.频率稳定度f ≤1KHz3.电源电压 Vcc=5V三、确定电路组成方案原理框图如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。

晶体振荡器输出的信号频率f1,经固定分频后(M分频)得到基准频率f1’,输入锁相环的相位比较器(PC)。

锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:f1/M=f1’=f2/N 故f2=Nf’1 (f’1为基准频率)当N变化时,或者N/M变化时,就可以得到一系列的输出频率f2。

锁相环与频率合成器实验讲义

锁相与频率合成技术实验讲义桂林电子科技大学通信实验中心实验一锁相环实验一、实验原理锁相环路实质是一个负反馈的相位差自动调节系统。

1、锁相环路的构成图1 锁相环基本框图1(1)鉴相器鉴相器是相位差转换成电压的变换器(θe / V变换器、相差/电压变换器),它把两个信号U2(t)和U1(t)的相位进行比较,产主对应于两个信号相位差θe的误差电Ud(t)。

图2(a) 鉴相器模型23图2(b )异或门鉴相曲线 图2(c )数字比相器的鉴频鉴相曲线4如图2(c )的数字比相器,其特性可以理解为:① 对于相位跳变信号,如f1输入已调2PSK 信号,f2输入载波信号,则鉴相器的输入输出信号为:图3 f 1 :PSK 信号图4 f 0: 载波信号图5 f 1 与f 0 的相差θe图6 鉴相器的输出电压Ud②对于频率跳变信号,如f1输入已调2FSK信号,由高低频率f H、f L组成,f2输入f L信号,则鉴相器的输入输出信号为:图7 f1:FSK信号图8 f0:FSK的f L信号图9 f1与f0 的相差θe5(2)环路滤波器环路滤波器的作用是滤除误差电压Ud(t)中的进行积分,以保证环路所要求的性能,增加系统的稳定性。

环路滤波器常用的类型有RC积分滤波器,无源比例积分滤波器,有源比例积分滤波器。

(3)压控振荡器VCO的技术指标:中心频率、频率变化范围、频率稳定度、相位噪声、压控线性度、压控灵敏度。

图11 压控振荡器控制电压/ 输出频率(Uc-ωO)特性曲线6同步带与捕获带同步带的测量方法:环路锁定之后,缓慢提高信号源的输入频率,直到输入输出频率不相等,测出Δωh H ;用同样方法测量Δωh L ,环路锁定之后,降低信号源的输入频率,直到输入输出频率不相等,测出ΔωL 。

图20 PLL同步带范围78同步带的测量方法:由于频率太低引起环路失锁之后,缓慢提高信号源的输入频率,直到输入输出频率不相等,测出Δωp H ;用同样方法测量Δωp L 。

锁相式数字频率合成器实验报告.

*******************实践教学*******************兰州理工大学计算机与通信学院2012年春季学期《通信系统基础实验》设计项目实验报告设计题目:锁相式数字频率合成器实验报告专业班级:设计小组名单:指导教师:陈昊目录一、设计实验目的 (3)二、频率合成基本原理 (4)2.1频率合成的概念 (4)2.2频率合成器的主要技术指标 (4)2.3锁相频率合成器 (5)三、锁相环技术 (6)3.1 锁相环工作原理 (6)3.2 锁相环CD4046芯片介绍 (6)四、基于锁相环技术的倍频器 (10)4.1 HS191芯片介绍 (10)4.2 基于锁相环技术的倍频器的设计 (12)4.2.1 工作原理 (12)3.2.2 Proteus软件仿真 (13)4.2.3 硬件实现 (14)4.2.4 锁相环参数设计 (15)五、总结与心得 (17)六、参考文献 (18)七、元器件清单 (19)一、设计实验目的1. 掌握VCO压控振荡器的基本工作原理。

2. 加深对基本锁相环工作原理的理解。

3. 熟悉锁相式数字频率合成器的电路组成与工作原理.。

二、频率合成基本原理2.1频率合成的概念频率合成是指由一个或多个频率稳定度和精确度很高的参考信号源通过频率域的线性运算,产生具有同样稳定度和精确度的大量离散频率的过程。

实现频率合成的电路叫频率合成器,频率合成器是现代电子系统的重要组成部分。

在通信、雷达和导航等设备中,频率合成器既是发射机频率的激励信号源,又是接收机的本地振荡器;在电子对抗设备中,它可以作为干扰信号放生器;在测试设备中,可作为标准信号源,因此频率合成器被人们称为许多电子系统的“心脏”。

早期的频率合成是用多晶体直接合成,以后发展成用一个高稳定参考源来合成多个频率。

20世纪50年代出现了间接频率合成技术。

但在使用频段上,直到50年代中期仍局限于短波范围。

60年代中期,带有可变分频的数字锁相式频率合成器问世。

锁相环频率合成实验new

频率合成实验(虚拟实验)姓名:学号:(一)锁相环频率合成器示波器1‐6波形(按系统给定的值synFq为30MHz,synSen为40MHz)分析:(1)仿真值:由上图可得各节点输出信号的幅度相同,频率分别为f1= fr/M = 1/(0.01*10-5)= 10MHz; f2 = 1/(0.005*10-5)=20MHz; f4 = f vco =1/(0.001*10-5)= 100MHz; f5 =1/(0.01*10-5)= 10MHz; f6 = fr = 3MHz;压控振荡器输入控制电压VCO=1.75V。

理论值:系统设定的振荡频率synFq=30MHz,压控灵敏度synSen=40MHz,参考信号频率synFr=30MHz,主分频比synN=10,前置分频比synM=3。

参考信号与输出信号的关系f4=f vco=synFq+synSen*VCO=30MHz+40MHz*1.75=100MHz,f1= synFr/synM =10MHz; f5 = f vco /synN= 10MHz; f6 =synFr = 30MHz.各理论值与仿真值相等(2)示波器3中的VCO的控制电压的变化曲线,其从开始阶跃到固定值间经历的时间为1.6×10﹣5 s,即为环路的锁定时间。

稳定值为1.75V。

将synSen 的初始值设为3e7(30MHz/V),示波器1‐6波形将synSen 的初始值设为5e7(50MHz/V),示波器1‐6波形分析:(将synSen的初始值为3e6与5e6分别与初始情况作比较)(1)改变压控灵敏度synSen的初始值,无论是增大还是减小,除示波器3外,其余示波器波形的周期幅度均没有变化,说明改变压控振荡器的压控灵敏度不会改变输出信号的频率。

(2)synSen的初始值为3e7,即相对4e7减小,示波器3中的电压最大值增大,稳定值也增大,环路锁定时间增大。

synSen的初始值为5e7,即相对4e7增大,示波器3中的电压最大值减小,稳定值也减小,环路锁定时间1.6×10﹣4 s,与初始情况相差不大。

简易频率合成器实验报告

竭诚为您提供优质文档/双击可除简易频率合成器实验报告篇一:简易频率合成器图滨江学院课程报告课程院系电子工程专业班级电科(2)任课教师赵静姓名凌超简易频率合成器一、技术指标1、输出信号的频率范围:1khz-99khz2、步进频率:1Khz3、输出电平为方波二、设计原理总体设计原理的框图与描述1、cD4046锁相环电路设计(1)、锁相环基本组成锁相环主要由相位比较Ⅰ、Ⅱ、压控振荡器(Vco)、线性放大器、源跟随器、整形电路等部分构成。

(2)、鉴相器(pD)鉴相器主要由放大整形电路和相位比较器组成。

比较器Ⅰ采用异或门结构,当两个输人端信号ui、uo的电平状态相异时,输出端信号uΨ为高电平;反之,ui、uo电平状态相同时,uΨ输出为低电平。

当ui、uo的相位差Δφ在0°-180°范围内变化时,uΨ的脉冲宽度m亦随之改变,即占空比亦在改变。

对相位比较器Ⅰ,它要求ui、uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

相位比较器Ⅱ对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。

它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。

(3)、压控振荡器(Vco)cD4046锁相环采用的是Rc型压控振荡器,须外接电容c1和电阻R1作为充放电元件。

当pLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。

由于Vco是一个电流控制振荡器,对定时电容c1的充电电流与从9脚输入的控制电压成正比,使Vco的振荡频率亦正比于该控制电压。

当Vco控制电压为0时,其输出频率最低;当输入控制电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率。

Vco振荡频率的范围由R1、R2和c1决定。

由于它的充电和放电都由同一个电容c1完成,故它的输出波形是对称方波(4)、低通滤波器cD4046的滤波器是需要外接来完成的,使用Rc型滤波器,Rc时间常数要选择合适的。

实验十 集成电路(锁相环)构成的频率解调器

实验十 集成电路(锁相环)构成的频率解调器一、实验目的1.了解用锁相环构成调频波的解调原理。

2.学习掌握集成电路频率调制器/解调器系统的工作原理。

二、预习要求1.查阅有关锁相环内部结构及工作原理。

2.弄清锁相环集成电路与外部元器件之间的关系。

三、实验仪器1.双踪示波器2.频率计3.万用表4.实验板G5四、实验电路说明图10-1为565(PLL 单片集成电路)的框图及管脚排列,锁相环内部电路由相位鉴别器、压控振荡器、放大器三部分构成,相位鉴别器由模拟乘法器构成,它有二组输入信号,一组为外部管脚②、③输入信号e 1,其频率为f1;另一组为内部压控振荡器产生信号e 2,经④脚输出,接至⑤送到相位鉴别器,其频率为f2,当f1和f2差别很小时,可用频率差代表两信 号之间的相位差,即f1- f2的值使相位鉴别器输出一直流电压,该 图10-1 565(PLL )的框图及管脚排列 电压经⑦脚送至VCO 的输入端,控制VCO ,使其输出信号频率发生变化f2发生变化,这一过程不断进行,直至f2= f1为止,这时称为锁相环锁定。

输入输入VCO 输出频率F2相位鉴别器VCO 输入参考电压输出VCO 控制电压时基电阻时基电容+VCC五、实验内容实验电路见图10-2图10-2 565(PLL)构成的频率解调器正弦波解调器调R P使其中VCO的输出频率f0(A点:即④⑤脚)为50KHz。

先按实验九的实验内容2(2)a的要求获得调频方波输出信号(③脚),要求输入的正弦调制信号e m为:V P-P=0.8V,f=1KHz,然后将其接至565锁相环的IN 输入端,调节566的R P1(逆时针旋转)使R最小,用双踪示波器观察并记录566的输入调制信号e m和565“B”点的解调输出信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验11 锁相调频与鉴频实验一、实验目的1.掌握锁相环的基本概念。

2.了解集成电路CD4046的内部结构和工作原理。

3.掌握由集成锁相环电路组成的频率调制电路/解调电路的工作原理。

二、预习要求1.复习反馈控制电路的相关知识。

2.锁相环路的工作原理。

三、实验仪器1.高频信号发生器2.频率计3.双踪示波器4.万用表5.实验板GPMK8四、锁相环的构成和基本原理(1)锁相环的基本组成图11-1是锁相环的基本组成方框图,它主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)组成。

图11-1 锁相环的基本组成①压控振荡器(VCO)VCO是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO上的电压。

所谓压控振荡器就是振荡频率受输入电压控制的振荡器。

② 鉴相器(PD )PD 是一个相位比较器,用来检测输出信号0V (t )与输入信号i V (t )之间的相位差θ (t),并把θ(t)转化为电压)(t V d 输出,)(t V d 称为误差电压,通常)(t V d 作为一直流分量或一低频交流量。

③ 环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在)(t V d 中产生的无用组合频率分量及干扰,产生一个只反映θ(t)大小的控制信号)(t V C 。

4046锁相环芯片包含鉴相器(相位比较器)和压控振荡器两部分,而环路滤波器由外接阻容元件构成。

(2)锁相环锁相原理锁相环是一种以消除频率误差为目的反馈控制电路,它的基本原理是利用相位误差电压去消除频率误差。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使)(t V O 与)(t V i 的相位差θ(t)发生变化,该相位差经过PD 转换成误差电压)(t V d 。

此误差电压经过LF 滤波后得到)(t V c ,由)(t V c 去改变VCO 的振荡频率,使其趋近于输入信号的频率,最后达到相等。

环路达到最后的这种状态就称为锁定状态。

当然由于控制信号正比于相位差,即)(t V d 正比于θ(t ),因此在锁定状态,θ(t )不可能为零,换言之,在锁定状态)(t V O 与)(t V i 仍存在相位差。

虽然有剩余相位误差存大,但频率误差可以降低到零,因此环路锁定时,压控振荡器输出频率O F 与外加基准频率(输入信号频率)i F 相等,即压控振荡器的频率被锁定在外来参考频率上。

(3)同频带与捕捉带同步带是指从环路锁定开始,改变输入信号的频率i f (向高或向低两个方向变化),直到环路失锁( 由锁定到失锁),这段频率范围称为同步带。

捕捉带是指锁相环处于一个固有的自由振荡频率V f ,即处于失锁状态,当从高端慢慢减小外加输入信号频率i f (初始频率设置较高),直到环路锁定,此时外加输入信号频率max i f 就是同步带的最高频率。

当从低端慢慢增加外加输入信号频率(初始频率设置较低),直到环路锁定,此时外加输入信号频率min i f 就是捕捉带的最低频率。

捕捉带为max i f -min i f 。

五、实验电路说明调频是用调制信号直接线性地改变载波振荡的瞬时频率,既使载波振荡频率随调制信号的失真变化而变化。

其逆过程为频率解调(也称频率检波或鉴频)。

本实验是用CD4046数字集成锁相环(PLL )来实现调频/解调(鉴频)的。

有关数字集成锁相环CD4046的内部构成和工作原理请参阅相关内容的书籍。

锁相环(4046)的结构框图及引出端功能图如下图所示。

CD404612345678910111213141516PCPout PC1outCOMPin VCOout INH C1AC1B VssVCOinSFout R1R2PC2outSINGin ZENER V DD1. 用锁相环(集成)构成的调频/解调(鉴频)电路 (1).锁相环调频原理鉴相器PID 压控振荡器VCO 高频信号放大器LM318低通滤波器R5C2加法器uA741载波调制信号调频波输出CD4046(3)(4)(14)(2)(9)锁相环调频电路原理框图注:由于载波信号频率相对于调制信号频率高的多,故载波信号频率称为所谓的高频(只是相对而言),而调制信号频率则相对应的称为低频。

将调制信号加到压控振荡器(VCO )的控制端,使压控振荡器的输出频率(在自振频率(中心频率)f 0上下)随调制信号的变化而变化,于是生成了调频波。

当载波频率与压控振荡频率相近时,载波频率与压控振荡器的振荡频率锁定。

低通滤波器只保证压控振荡器中心振荡频率与载波频率锁定时所产生的相位误差电压通过,该电压与调制信号同经加法器,用以控制压控振荡器的频率,从而获得与载波频率具有同样频率稳定度的调频波。

(2).锁相环解调原理鉴相器PID 压控振荡器VCO高频信号放大器LM318低通滤波器R15C6载波解调输出CD4046(3)(4)(14)(2)(9)锁相环解调电路原理框图跟随器调频波(经过放大器放大后)与压控振荡器的输出被送入鉴频器,经鉴相获得变化着的相位误差电压,该误差电压通过低通滤波器被滤掉其高频成份,继而获得随调制信号频率变化而变化的信号,经跟随器得到解调信号,从而实现了解调(鉴频)过程。

2.锁相环振荡频率f0、同步带与捕捉带的测量方法。

(1).自振频率f0的测量用示波器观测⑷脚的输出波形(方波),用频率计测量自振频率f0。

(2).锁定的判断⒁脚(SIGNin)输入方波信号,用示波器观察⑵脚(PC1out)的波形,如锁定,可得到一个稳定的矩形脉冲;若⒁脚输入信号频率与压控振荡器的振荡频率相等,则⑵脚输出为稳定地两倍频方波信号。

(3).同步带宽(锁定范围)和捕捉带宽(捕捉范围)的测量⒁脚输入一个方波信号(最好用频率计检测),其频率与f0(VCO自振频率)相同。

改变⒁脚输入信号频率,使频率逐渐降低,直至⑷脚(或⑵脚)输出方波刚好不稳定时,环路进入失锁状态,该点频率定义为同步带的下限频率“f1”。

改变⒁脚输入信号频率,由f1开始频率逐渐增加,直至⑷脚输出方波刚好再次稳定时,环路进入锁定状态,该点频率定义为捕捉带的下限频率“f2”。

f 0f 1234f f f 同步带捕捉带改变⒁脚输入信号频率,由f 2开始频率逐渐增加,直至⑷脚输出方波刚好再次不稳定时,环路进入失锁状态,该点频率定义为同步带的上限频率“f 4”。

改变⒁脚输入信号频率,由f 4开始频率逐渐降低,直至⑷脚输出方波刚好稳定时,环路进入锁定状态,该点频率定义为捕捉带的上限频率“f 3”。

由以上可计算出:同步带宽为:f 4-f 1 捕捉带宽为:f 3-f 23. 实验电路说明相关概念前面已分析清楚。

这里需要说明的是当要测量压控振荡器的自振频率时,必须先将IN1短路,当要测量压控振荡器的同步带和捕捉带时,必须将IN2短路。

由于电路是环路锁相,改变滤波器参数既可改变VCO 的自振频率,因此调节RP1或RP2可改变VCO 的自振频率。

当改变C3、C4、R11、R12、R13、R14也可在较大范围内改变VCO 的输出频率。

六、实验内容与步骤 1. 调频锁相环部分的测试 (1).锁相环自振频率f 0的测量将IN1、IN2分别对地短路,调节电位器RP1至适中位置,测量D 端直流电压(近似电源电压的1/2),用示波器观察锁相环输出OUT1端的波形。

记录波形特性、频率、幅度,填入下表。

观察相位比较器(鉴相器)B端的波形,将测量结果填入下表。

观察鉴相器输出C端的预积分波形,将测量结果填入下表。

观察压控振荡器输入D端的波形,将测量结果填入下表。

(2).锁定的判断将信号发生器输出的方波信号(幅度3.5V P-P,频率为自振频率f0)加到载波输入IN1端,用双踪示波器同时观测锁相环OUT1端和A端的波形(即锁相环的⑷脚和⒁脚)。

如波形稳定表示频率被锁定。

改变信号发生器的输出信号频率,可发现在较大范围内锁相环均能锁定。

记录测量结果。

思考:当频率锁定时,观测OUT1端和B端出现什么现象?如何解释?(3).测量同步带宽(锁定范围)和捕捉带宽(捕捉范围)观测A端和OUT1端,改变信号发生器的输出频率(即载波频率)调节载波信号频率(输入IN1),由自振频率f0开始逐渐缓慢降低,直至(VCOout端)波形抖动(即:失锁),记录此时的载波输入信号频率f1(下限失锁频点)。

调节载波信号频率,由f1开始逐渐缓慢增加,直至(VCOout端)波形不抖动(即:锁定),记录此时的载波输入信号频率f2(下限锁定频点)。

调节载波信号频率,由f2开始逐渐缓慢增加,直至(VCOout端)波形抖动(即:失锁),记录此时的载波输入信号频率f4(上限失锁频点)。

同步带宽(锁定范围)=f4-f1调节载波信号频率,由f4开始逐渐缓慢降低,直至(VCOout端)波形不抖动(即:锁定),记录此时的载波输入信号频率f3(上限锁定频点)。

捕捉带宽(捕捉范围)=f3-f22.解调部分的测试(1).锁相环自振频率的测量调节电位器RP2至适中位置,测量G端直流电压,用示波器观察锁相环输出E端的波形。

记录波形特性、频率、幅度,填入下表。

观察相位比较器(鉴相器)F端的波形,将测量结果填入下表。

(2).锁定的判断将信号发生器输出的方波信号(幅度3.5V P-P,频率为自振频率f0)加到载波输入IN1端,连接A端和IN3端,用双踪示波器同时观测锁相环E端和A端的波形。

如波形稳定表示频率被锁定。

改变信号发生器的输出信号频率,可发现在较大范围内锁相环均能锁定。

记录测量结果。

思考:锁定时观测A端和F端的波形,有何结论,如何分析?(3).测量同步带宽(锁定范围)和捕捉带宽(捕捉范围)观测A端和E端,改变信号发生器的输出频率(即载波频率)调节载波信号频率(输入IN1),由自振频率f0开始逐渐缓慢降低,直至(E端)波形抖动(即:失锁),记录此时的载波输入信号频率f1(下限失锁频点)。

调节载波信号频率,由f1开始逐渐缓慢增加,直至(E端)波形不抖动(即:锁定),记录此时的载波输入信号频率f2(下限锁定频点)。

调节载波信号频率,由f2开始逐渐缓慢增加,直至(E端)波形抖动(即:失锁),记录此时的载波输入信号频率f4(上限失锁频点)。

同步带宽(锁定范围)=f4-f1调节载波信号频率,由f4开始逐渐缓慢降低,直至(E端)波形不抖动(即:锁定),记录此时的载波输入信号频率f3(上限锁定频点)。

捕捉带宽(捕捉范围)=f3-f23.观测系统的调频情况IN1端输入幅值为3.5V P-P,频率与自振频率相同的方波信号(定义为载波)。

IN2端输入幅值为0.4V P-P,频率1KHz的正弦波信号(定义为调制波)。

用双踪示波器仔细观测OUT1和IN2端,为了可清楚地观看到调频波的疏密变化,可微调调制信号的频率。