计算机组成原理第四章习题

计算机组成原理第四章单元测试(二)(含答案)

计算机组成原理第四章单元测试(二)(含答案)第四章存储系统(二)测试1、32位处理器的最大虚拟地址空间为A、2GB、4GC、8GD、16G2、在虚存、内存之间进行地址变换时,功能部件()将地址从虚拟(逻辑)地址空间映射到物理地址空间A、TLBB、MMUC、CacheD、DMA3、在程序执行过程中,Cache与主存的地址映象是由A、用户编写程序完成B、操作系统完成C、编译系统完成D、硬件自动完成4、某计算机的存储系统由cache和主存组成。

某程序执行过程共访存2000次,其中访问cache缺失(未命中)100次,则该程序执行过程中Cache的命中率为A、80%B、85%C、90%D、95%5、在Cache的地址映射中,若主存中的任意一块均可映射到Cache内任意一行的位置上,则这种映射方法称为A、全相联映射B、直接映射C、2-路组相联映射D、混合映射6、采用虚拟存储器的主要目的是A、提高主存储器的存取速度B、扩大主存储器的存储空间,且能进行自动管理和调度C、提高外存储器的存取速度D、扩大外存储器的存储空间7、虚拟存储器中,程序执行过程中实现虚拟地址到物理地址映射部件(系统)是A、应用程序完成B、操作系统和MMU配合完成C、编译器完成D、MMU完成8、相联存储器是按( )进行寻址访问的存储器A、地址B、内容C、堆栈D、队列9、以下哪种情况能更好地发挥Cache的作用A、程序中存在较多的函数调用B、程序的大小不超过内存容量C、程序具有较好的时间和空间局部性D、递归子程序10、以下关于虚拟存储管理地址转换的叙述中错误的是()A、地址转换是指把逻辑地址转换为物理地址B、一般来说,逻辑地址比物理地址的位数少C、地址转换过程中可能会发生“缺页”D、MMU在地址转换过程中要访问页表项11、假定主存按字节编址,cache共有64行,采用4路组相联映射方式,主存块大小为32字节,所有编号都从0开始。

问主存第3000号单元所在主存块对应的cache组号是A、1B、5C、13D、2912、下列关于MMU的叙述中,错误的是()A、MMU是存储管理部件B、MMU负责主存地址到Cache地址的映射C、MMU参与虚拟地址到物理地址的转换D、MMU配合使用TLB 地址转换速度更快13、下列关于主存与cache地址映射方式的叙述中正确的是()A、全相联映射方式比较适用于大容量CacheB、直接映射是一对一的映射关系,组相联映射是多对一的映射关系C、在Cache容量相等条件下,直接映射方式的命中率比组相联方式有更高的命中率D、在Cache容量相等条件下,组相联方式的命中率比直接映射方式有更高的命中率14、下列关于CaChe的说法中,错误的是()A、CaChe对程序员透明B、CaChe行大小与主存块大小一致C、分离CaChe(也称哈佛结构)是指存放指令的CaChe与存放数据CaChe分开设置D、读操作也要考虑CaChe与主存的一致性问题15、下列关于CaChe的论述中,正确的是A、采用直接映射时,CaChe无需使用替换算法B、采用最优替换算法,CaChe的命中率可达到100%C、加快CaChe本身速度,比提高CaChe命中率更能提升存储系统的等效访问速度D、CaChe的容量与主存的容量差距越大越能提升存储系统的等效访问速度16、某计算机系统中,CaChe容量为512 KB,主存容量为256 MB,则CaChe 一主存层次的等效容量为A、512 KBB、256 MBC、256 MB+512 KBD、256 MB - 512 KB17、下列关于Cache的描述中正确的是( )A、Cache存储器是内存中的一个特定区域B、Cache存储器的存取速度介于内存和磁盘之间C、Cache存储器中存放的内容是内存的副本D、Cache中存放正在处理的部分指令和数据18、关于TLB和Cache,下面哪些说法中正确的是( )A、TLB和Cache中存的数据不同B、TLB 访问缺失(miss)后,可能在Cache中直接找到页表内容C、TLB miss会造成程序执行出错,但是Cache miss不会D、TLB和Cache都采用虚拟地址访问19、在下列因素中,与Cache的命中率有关的是( )A、Cache块大小B、Cache的总容量C、主存的存取时间D、替换算法20、下面有关Cache的说法中正确的是( )A、设置Cache的目的,是解决CPU和主存之间的速度匹配问题B、设置Cache的理论基础,是程序访问的局部性原理C、Cache与主存统一编址,Cache地址空间是主存的一部分D、Cache功能均由硬件实现,对程序员透明21、下列关于存储系统的描述中正确的是( )A、每个程序的虚地址空间可以远大于实地址空间,也可以远小于实地址空间B、多级存储体系由cache、主存和虚拟存储器构成C、Cache和虚拟存储器这两种存储器管理策略都利用了程序的局部性原理D、当Cache未命中时,CPU以直接访问主存,而外存与CPU之间则没有直接通路22、下列关于TLB、cache和虚存页(Page)命中组合情况中,一次访存过程中可能发生的是( )A、TLB命中、cache命中、Page命中B、TLB未命中、cache命中、Page命中C、TLB未命中、cache未命中、Page命中D、TLB未命中、cache命中、Page未命中23、下列RAID组中需要的最小硬盘数为3个的是()A、RAID 1B、RAID 3C、RAID 5D、RAID 1024、下列RAID技术中采用奇偶校验方式来提供数据保护的是()A、RAID 1B、RAID 3C、RAID 5D、RAID 1025、在请求分页存储管理方案中,若某用户空间为16个页面,页长1 K B,虚页号0、1、2、3、4对应的物理页号分别为1、5、3、7、2。

计算机组成原理第四章课后题参考答案

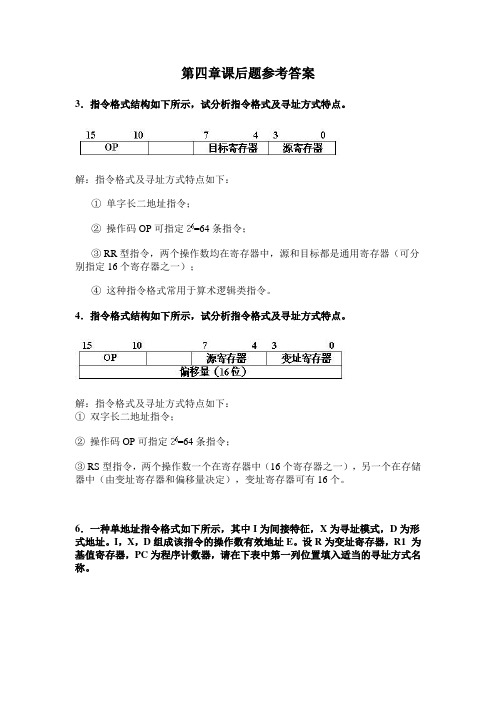

第四章课后题参考答案3.指令格式结构如下所示,试分析指令格式及寻址方式特点。

解:指令格式及寻址方式特点如下:①单字长二地址指令;②操作码OP可指定=64条指令;③ RR型指令,两个操作数均在寄存器中,源和目标都是通用寄存器(可分别指定16个寄存器之一);④这种指令格式常用于算术逻辑类指令。

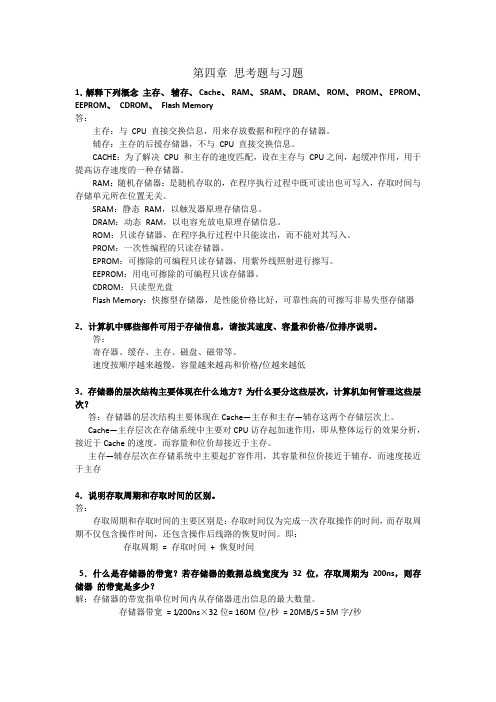

4.指令格式结构如下所示,试分析指令格式及寻址方式特点。

解:指令格式及寻址方式特点如下:①双字长二地址指令;②操作码OP可指定=64条指令;③ RS型指令,两个操作数一个在寄存器中(16个寄存器之一),另一个在存储器中(由变址寄存器和偏移量决定),变址寄存器可有16个。

6.一种单地址指令格式如下所示,其中I为间接特征,X为寻址模式,D为形式地址。

I,X,D组成该指令的操作数有效地址E。

设R为变址寄存器,R1 为基值寄存器,PC为程序计数器,请在下表中第一列位置填入适当的寻址方式名称。

解:①直接寻址②相对寻址③变址寻址④基址寻址⑤间接寻址⑥基址间址寻址12. 根据操作数所在位置,指出其寻址方式(填空):(1)操作数在寄存器中,为(A)寻址方式。

(2)操作数地址在寄存器,为(B)寻址方式。

(3)操作数在指令中,为(C)寻址方式。

(4)操作数地址(主存)在指令中,为(D)寻址方式(5)操作数的地址,为某一寄存器内容与位移量之和可以是(E,F,G)寻址方式。

解:A:寄存器直接(或寄存器);B:寄存器间接;C:立即;D:直接;E:相对;F:基址;G:变址补充一下,间接寻址可以表述为:操作数地址(主存)在内存中或者操作数地址的地址(主存)在指令中。

计算机组成原理课后答案第四章_庞海波

设DRAM的刷新最大间隔时间为2ms,

则异步刷新的刷新间隔=2ms/256行=0.0078125ms =7.8125µs

即:每7.8125µs刷新一行。

集中刷新时,死时间为256*0.1us=25.6us。

分散刷新,刷新间隔0.2us,死时间为0.1us,读写周期0.2us

异步刷新,死时间0.1us,刷新间隔7.8125us。

第四章思考题与习题

1.解释下列概念主存、辅存、Cache、RAM、SRAM、DRAM、ROM、PROM、EPROM、EEPROM、CDROM、Flash Memory

答:

主存:与CPU直接交换信息,用来存放数据和程序的存储器。

辅存:主存的后援存储器,不与CPU直接交换信息。

CACHE:为了解决CPU和主存的速度匹配,设在主存与CPU之间,起缓冲作用,用于提高访存速度的一种存储器。

3.存储器的层次结构主要体现在什么地方?为什么要分这些层次,计算机如何管理这些层次?

答:存储器的层次结构主要体现在Cache—主存和主存—辅存这两个存储层次上。

Cache—主存层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,接近于Cache的速度,而容量和位价却接近于主存。

主存—辅存层次在存储系统中主要起扩容作用,其容量和位价接近于辅存,而速度接近于主存

页面容量=总容量/页面数= 64K×8 / 4 = 16K×8位,4片16K×8字串联成64K×8位

组容量=页面容量/组数= 16K×8位/ 16 = 1K×8位,16片1K×8位字串联成16K×8位

组内片数=组容量/片容量= 1K×8位/ 1K×4位= 2片,两片1K×4位芯片位并联成1K×8位

存储器逻辑框图:

计算机组成原理第五版 白中英(详细)第4章习题参考答案

第4章习题参考答案1.ASCII码是7位,如果设计主存单元字长为32位,指令字长为12位,是否合理?为什么?答:不合理。

指令最好半字长或单字长,设16位比较合适。

一个字符的ASCII 是7位,如果设计主存单元字长为32位,则一个单元可以放四个字符,这也是可以的,只是在存取单个字符时,要多花些时间而已,不过,一条指令至少占一个单元,但只占一个单元的12位,而另20位就浪费了,这样看来就不合理,因为通常单字长指令很多,浪费也就很大了。

2.假设某计算机指令长度为32位,具有双操作数、单操作数、无操作数三类指令形式,指令系统共有70条指令,请设计满足要求的指令格式。

答:字长32位,指令系统共有70条指令,所以其操作码至少需要7位。

双操作数指令单操作数指令无操作数指令3.指令格式结构如下所示,试分析指令格式及寻址方式特点。

答:该指令格式及寻址方式特点如下:(1) 单字长二地址指令。

(2) 操作码字段OP可以指定26=64种操作。

(3) 源和目标都是通用寄存器(可分指向16个寄存器)所以是RR型指令,即两个操作数均在寄存器中。

(4) 这种指令结构常用于RR之间的数据传送及算术逻辑运算类指令。

4.指令格式结构如下所示,试分析指令格式及寻址方式特点。

15 10 9 8 7 4 3 0答:该指令格式及寻址方式特点如下:(1)双字长二地址指令,用于访问存储器。

(2)操作码字段OP可以指定26=64种操作。

(3)RS型指令,一个操作数在通用寄存器(选择16个之一),另一个操作数在主存中。

有效地址可通过变址寻址求得,即有效地址等于变址寄存器(选择16个之一)内容加上位移量。

5.指令格式结构如下所示,试分析指令格式及寻址方式特点。

答:该指令格式及寻址方式特点如下:(1)该指令为单字长双操作数指令,源操作数和目的操作数均由寻址方式和寄存器构成,寄存器均有8个,寻址方式均有8种。

根据寻址方式的不同,指令可以是RR型、RS型、也可以是SS型;(2)因为OP为4位,所以最多可以有16种操作。

计算机组成原理第4章习题参考答案

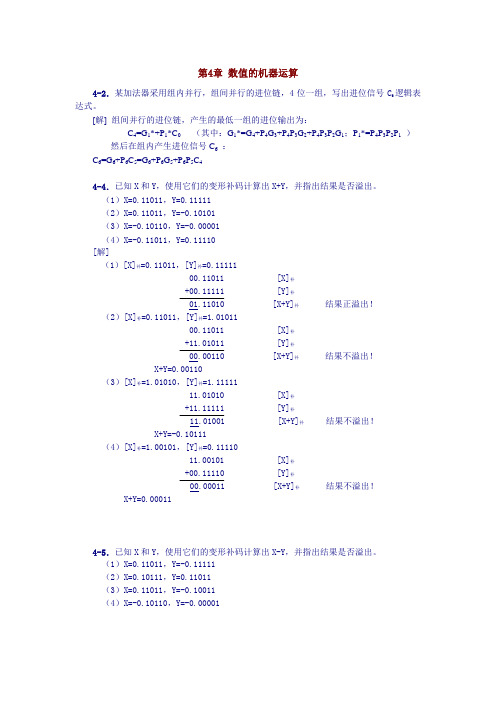

第4章 数值的机器运算4-2.某加法器采用组内并行,组间并行的进位链,4位一组,写出进位信号C6逻辑表达式。

[解] 组间并行的进位链,产生的最低一组的进位输出为:C4=G1*+P1*C0 (其中:G1*=G4+P4G3+P4P3G2+P4P3P2G1;P1*=P4P3P2P1)然后在组内产生进位信号C6:C6=G6+P6C5=G6+P6G5+P6P5C44-4.已知X和Y,使用它们的变形补码计算出X+Y,并指出结果是否溢出。

(1)X=0.11011,Y=0.11111(2)X=0.11011,Y=-0.10101(3)X=-0.10110,Y=-0.00001(4)X=-0.11011,Y=0.11110[解](1)[X]补=0.11011,[Y]补=0.1111100.11011 [X]补+00.11111 [Y]补01.11010 [X+Y]补 结果正溢出!(2)[X]补=0.11011,[Y]补=1.0101100.11011 [X]补+11.01011 [Y]补00.00110 [X+Y]补 结果不溢出!X+Y=0.00110(3)[X]补=1.01010,[Y]补=1.1111111.01010 [X]补+11.11111 [Y]补11.01001 [X+Y]补 结果不溢出!X+Y=-0.10111(4)[X]补=1.00101,[Y]补=0.1111011.00101 [X]补+00.11110 [Y]补00.00011 [X+Y]补 结果不溢出!X+Y=0.000114-5.已知X和Y,使用它们的变形补码计算出X-Y,并指出结果是否溢出。

(1)X=0.11011,Y=-0.11111(2)X=0.10111,Y=0.11011(3)X=0.11011,Y=-0.10011(4)X=-0.10110,Y=-0.00001[解](1)[X]补=0.11011,[Y]补=1.00001, [-Y]补=0.1111100.11011 [X]补+00.11111 [-Y]补01.11010 [X-Y]补 结果正溢出!(2)[X]补=0.10111,[Y]补=0.11011, [-Y]补=1.0010100.10111 [X]补+11.00101 [-Y]补11.11100 [X-Y]补 结果不溢出!X-Y=11.11100(3)[X]补=0.11011,[Y]补=1.01101, [-Y]补=0.1001100.11011 [X]补+00.10011 [-Y]补01.01110 [X-Y]补 结果正溢出!(4)[X]补=1.01010,[Y]补=1.11111,[-Y]补=0.0000111.01010 [X]补+00.00001 [-Y]补11.01011 [X-Y]补 结果不溢出!X-Y=-0.101014-6.已知:X=0.1011,Y=-0.0101求:[X/2]补 ,[X/4]补 ,[-X]补 ,[Y/2]补 ,[Y/4]补 ,[-Y]补,[2Y]补[解] 由[X]补=0.1011,[Y]补=1.1011 得:[X/2]补=0.0101,[X/4]补=0.0010,[-X]补=1.0101[Y/2]补=1.1101,[Y/4]补=1.1110,[-Y]补=0.0101,[2Y]补=1.01104-7. 设下列数据长8位,包括一位符号位,采用补码表示,分别写出每个数右移或左移两位之后的结果(1)0.1100100 (2) 1.0011001 (3) 1.1100110 (4)1.0000111[解] (1)右移两位后为 0.0011001 左移两位后为1.0010000(溢出)或0.0010000 (2)右移两位后为 1.1100110 左移两位后为0.1100100(溢出)或1.1100100(3)右移两位后为1.1111001 左移两位后为 1.0011000(4)右移两位后为 1.11000001 左移两位后为0.0011100(溢出)或1.00111004-8.分别用原码乘法和补码乘法计算X×Y.(1) X=0.11011,Y=-0.11111(2) X=-0.11010,Y=-0.01110[解]原码乘法:(1)|X|=0.11011 → B, |Y|=0.11111 →C,0→A5=1,+ |X|00.1101100.01101 1 0 1 1 1 1 部分积右移1位5=1,+ |X|01.0100000.10100 0 1 0 1 1 1 部分积右移1位5=1,+ |X|01.0111100.10111 1 0 1 0 1 1 部分积右移1位5=1,+ |X|01.1001000.11001 0 1 0 1 0 1 部分积右移1位5=1,+ |X|01.1010000.11010 0 0 1 0 1 0 部分积右移1位所以, |X×Y|=0.1101000101X×Y=-0.1101000101(2) |X|=0.11010 → B, |Y|=0.01110 → C, 0→A5=0,+ 000.0000000.00000 0 0 0 1 1 1 部分积右移1位5=1,+ |X|00.1101000.01101 0 0 0 0 1 1 部分积右移1位5=1,+ |X|01.0011100.10011 1 0 0 0 0 1 部分积右移1位5=1,+ |X|01.0110100.10110 1 1 0 0 0 0 部分积右移1位5=0,+ 000.1011000.01011 0 1 1 0 0 0 部分积右移1位所以, |X×Y|=0.010*******X×Y=+0.010*******补码乘法:(1)[X]补=0.11011 → B, [Y]补=1.00001 → C, 0 → A[-X]补说明 + [-X]补5C 6=10,+ [-X]补11.0010111.10010 1 1 0 0 0 0 1 部分积右移1位+ [X]补5C 6=01,+ [X]补00.0110100.00110 1 1 1 0 0 0 0 部分积右移1位5C 6=00,+ 000.0011000.00011 0 1 1 1 0 0 0 部分积右移1位5C 6=00,+ 000.0001100.00001 1 0 1 1 1 0 0 部分积右移1位5C 6=00,+ 000.0000100.00000 1 1 0 1 1 1 0 部分积右移1位+ [-X]补 5C 6=10,+ [-X]补所以, [X×Y]补=1.0010111011X×Y =-0.1101000101(2)[X]补=1.00110 → B, [Y]补=1.10010 → C, 0→A[-X]补说明5C 6=00,+ 01位+ [-X]补 00.11010 C 5C 6=10,+ [-X]补00.1101000.01101 0 0 1 1 0 0 1 部分积右移1位+ [X]补 11.00110 C 5C 6=01,+ [X]补11.1001111.11001 1 0 0 1 1 0 0 部分积右移1位+ 0 00.00000 C 5C 6=00,+ 011.1100111.11100 1 1 0 0 1 1 0 部分积右移1位+ [-X]补 00.11010 C 5C 6=10,+[-X]补00.1011000.01011 0 1 1 0 0 1 1 部分积右移1位+ 0 5C 6=11,+ 000.01011所以, [X×Y]补=0.010*******X×Y = 0.010*******4-10.分别用原码和补码加减交替法计算X/Y 。

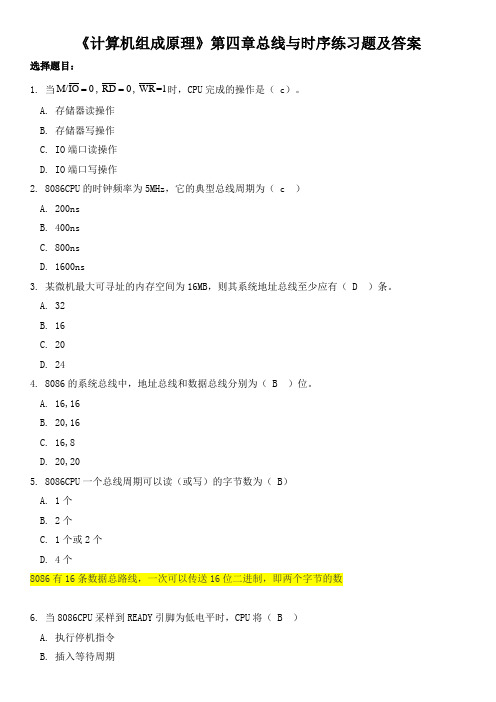

《计算机组成原理》第四章总线与时序练习题及答案

《计算机组成原理》第四章总线与时序练习题及答案选择题目:1. 当M/IO 0=,RD 0=,WR=1时,CPU 完成的操作是( c )。

A. 存储器读操作B. 存储器写操作C. IO 端口读操作D. IO 端口写操作2. 8086CPU 的时钟频率为5MHz ,它的典型总线周期为( c )A. 200nsB. 400nsC. 800nsD. 1600ns3. 某微机最大可寻址的内存空间为16MB ,则其系统地址总线至少应有( D)条。

A. 32B. 16C. 20D. 244. 8086的系统总线中,地址总线和数据总线分别为( B )位。

A. 16,16B. 20,16C. 16,8D. 20,205. 8086CPU 一个总线周期可以读(或写)的字节数为( B )A. 1个B. 2个C. 1个或2个D. 4个8086有16条数据总路线,一次可以传送16位二进制,即两个字节的数6. 当8086CPU 采样到READY 引脚为低电平时,CPU 将( B )A. 执行停机指令B. 插入等待周期C. 执行空操作D. 重新发送地址7. 当8086CPU读写内存的一个对准存放的字时,BHE和A0的状态为( A )。

A. 00B. 01C. 10D. 118. 当8086CPU采样到READY引脚为低电平时,CPU将( B )A. 执行停机指令B. 插入等待周期C. 执行空操作D. 重新发送地址9. 8086CPU的字数据可以存放在偶地址,也可以存放在奇地址。

下列说法正确的是( A )A. 堆栈指针最好指向偶地址B. 堆栈指针最好指向奇地址C. 堆栈指针只能指向偶地址D. 堆栈指针只能指向奇地址10. 8086CPU在进行对外设输出操作时,控制信号M/IO和DT/R状态必须是(D )A. 0,0B. 0,1C. 1,0D. 1,111. 8086CPU复位时,各内部寄存器复位成初值。

复位后重新启动时,计算机将从内存的( c )处开始执行指令。

计算机组成原理第四章课下练习题答案

CH4 作业答案一、判断题1.√2. √3.×4. √5. √6. ×7. ×8. √9. √10. ×二、选择题1.D2.A3.A4.B5.C6.D7.C8.C9.A10.A 11.D 12.B 13.A 14.C 15.D 16.C 17.D 18.D19.A 20.D 21.C三、填空题1.答:程序和数据;存储位置2.答:无关;随机访问3.答:存储体;读写电路4.答:随机存储器( R A M )5.答 : 行选通列选通6.答 : 647.答 : 双稳态电路刷新 ( 或恢复 )8.答 : 两行选通列选通9.答 :刷新10.答 : 地址线控制11.答 : 地址片选12.答 : 8 413.答 : 20 1614.答 : 可多次擦写紫外线照射15.答 : 一次性写入的可编程芯片16.答 : 容量小速度快17.答 : 快速度18.答 : 虚拟存储器19.答 : 主存-辅存主存容量不足20.答 : 虚拟地址( 逻辑地址) 实际地址( 物理地址)21.答 : Ca c h e 的访问命中率22.答 : 一快块冲突23.答 : 8 1324.答 : 1024 6425.答 : 寄存器 Cache 主存辅存26.答 : 掩膜 R O M27.答:3FFFFH28.答 : 存储容量;存取周期29.答:ROM RAM 顺序存储器直接存储器30.答:地址寄存器地址译码器31.答:1024 6432.答:程序访问内存的局限性33.答:静态RAM 动态RAM34.答 : 19 1635.答 : 全相联直接36.答 : 存储介质37.答 : 半导体存储器、磁存储器光存储器38.答 : 非易失性存储器易失性存储器39.答 : 普通 R O M 可编程 R O M 可擦写可编程 R O M 电可擦可编程 R O M40.答 : c ach e 主存磁盘光盘41.答 : 6442.答 : 主存辅存逻辑物理地址映射43.答 : 掩膜 R O M44.答 : 1024 1024 845.答 : 存储体地址寄存器读写电路46.答 : 读/ 写时间47.答 : 电容是否充电定时刷新48.答:静态RAM。

(完整版)计算机组成原理第4章作业参考答案

第4章部分习题参考答案【4-4】已知X和Y,试用它们的变形补码计算出X + Y,并指出结果是否溢出(3)X = -0.10110,Y = -0.00001解:[X]补= 1.01010 [Y]补= 1.111111 1 . 0 1 0 1 0+ 1 1 . 1 1 1 1 11 1 . 0 1 0 0 1无溢出,X+Y = -0.10111【4-5】已知X和Y,试用它们的变形补码计算出X - Y,并指出结果是否溢出(3)X = 0.11011,Y = -0.10011解:[X]补= 0.11011 [-Y]补= 0.100110 0 . 1 1 0 1 1+ 0 0 . 1 0 0 1 10 1 . 0 1 1 1 0结果正溢【4-8】分别用原码乘法和补码乘法计算X * Y(1)X = 0.11011,Y = -0.11111法一:原码一位乘算法解:|X| = 0.11011→B |Y| = 0.11111→C 0→AA C 说明1 1 1 1 1C5 = 1, +|X|1 1 1 1 1 部分积右移一位→C5 = 1, +|X|0 1 1 1 1 部分积右移一位→C5 = 1, +|X|1 0 1 1 1 部分积右移一位→C5 = 1, +|X|0 1 0 1 1 部分积右移一位→C5 = 1, +|X|0 0 1 0 1 部分积右移一位→|X * Y| = 0.1101000101Ps = Xs ⊕ Ys = 0 ⊕ 1 = 1X*Y = -0.1101000101法二:补码一位乘算法解:[X]补= 0.11011→B [Y]补= 1.00001→C [-X]补= 1.00101 0→AA C 附加说明0 0. 0 0 0 0 0 1 0 0 0 0 1 0+1 1. 0 0 1 0 1 C4C5 = 10 -|X|1 1. 0 0 1 0 11 1. 1 0 0 1 0 1 1 0 0 0 0 1 部分积右移一位→+0 0. 1 1 0 1 1 C4C5 = 01 +|X|0 0. 0 1 1 0 10 0. 0 0 1 1 0 1 1 1 0 0 0 0 部分积右移一位→+0 0. 0 0 0 0 0 C4C5 = 00 +00 0. 0 0 1 1 00 0. 0 0 0 1 1 0 1 1 1 0 0 0 部分积右移一位→+0 0. 0 0 0 0 0 C4C5 = 00 +00 0. 0 0 0 1 10 0. 0 0 0 0 1 1 0 1 1 1 0 0 部分积右移一位→+0 0. 0 0 0 0 0 C4C5 = 00 +00 0. 0 0 0 0 10 0. 0 0 0 0 0 1 1 0 1 1 1 0 部分积右移一位→+1 1. 0 0 1 0 1 C4C5 = 10 -|X|1 1. 0 0 1 0 1[X*Y]补= 11.0010111011X*Y = -0.1101000101【4-10】计算X/Y(2)X = -0.10101,Y = 0.11011原码恢复余数法:解:|X| = -0.101010→A |Y| = 0.110110→B [-|Y|]补= 1.00101 0→C0 0. 1 0 1 0 1 0 0 0 0 0 0+1 1. 0 0 1 0 1 -|Y|1 1. 1 1 0 1 0 <0+0 0. 1 1 0 1 1 +|Y|0 0. 1 0 1 0 1 0 0 0 0 0 0 商00 1. 0 1 0 1 0 0 0 0 0 0 0 左移←+1 1. 1 1 0 0 1 -|Y|0 0. 0 1 1 1 1 0 0 0 0 0 1 >0,商10 0. 1 1 1 1 0 0 0 0 0 1 0 左移←+1 1. 0 0 1 0 1 -|Y|0 0. 0 0 0 1 1 0 0 0 0 1 1 >0,商10 0. 0 0 1 1 0 0 0 0 1 1 0 左移←+1 1. 0 0 1 0 1 -|Y|1 1. 0 1 0 1 1 <0+0 0. 1 1 0 1 1 +|Y|0 0. 0 0 1 1 0 0 0 0 1 1 0 商00 0. 0 1 1 0 0 0 0 1 1 0 0 左移←+1 1. 0 0 1 0 1 -|Y|1 1.1 0 0 0 1 <0+0 0. 1 1 0 1 1 +|Y|0 0. 0 1 1 0 0 0 0 1 1 0 0 商00 0. 1 1 0 0 0 0 1 1 0 0 0 左移←+1 1. 0 0 1 0 1 -|Y|1 1. 1 1 1 0 1 <0+0 0. 1 1 0 1 1 +|Y|0 0. 1 1 0 0 0 0 1 1 0 0 0 商0Qs = Xs⊕Ys = 0⊕1 = 1Q = -0.11000,R = 0.11000*2-5【4-11】设浮点数的阶码和尾数部分均用补码表示,按照浮点数的运算规则,计算下列各题(2)X = 2-101*0.101100,Y = 2-100*(-0.101000)解:[X]补= 1011;0.101100[Y]补= 1100;1.011000对阶:△E = Ex – Ey = -5 -(-4)= -1Ex < Ey,将Mx右移一位,Ex+1→Ex[X]’补=1011;0.010110尾数求和:0 0. 0 1 0 1 1 0+1 1. 0 1 1 0 0 01 1. 1 0 1 1 1 0尾数结果规格化:尾数左移1位,阶码减1[X+Y]补=1011;1.011100X+Y = (-0.100100)*2-101减法算法过程略,X-Y = 0.111110 * 2-100【4-13】用流程图描述浮点除法运算的算法步骤设:被除数X = Mx * 2Ex; 除数Y = My * 2 Ey。

计算机组成原理第四章要求作业参考答案

习题4 4.1设X=0.1101,Y= -0.0110,求:(1)[X]补(2)[-X]补(3)[2X]补(4)[-2X]补(5)[X/2]补(6)[-X/2]补(7)[Y]补(8)[-Y]补(9)[2Y]补(10)[-2Y]补(11)[Y/2]补(12)[-Y/2]补(13)[-Y/4]补1. (1) [X]补= 0.1101(2) [-X]补= 1.0011(3) [2X]补= 0.1010 溢出(4) [-2X]补= 1.0110 溢出(5)[X/2]补= 0.0110注意:参见P109中的补码算术移位规则,以及P110的例4.4(6)[-X/2]补= 1.1001(7)[Y]补= 1.1010(8) [-Y]补= 0.0110(9) [2Y]补=1.0100(10)[-2Y]补=0.1100(11)[Y/2]补=1.1101(12)[-Y/2]补= 0.0010(13) [-Y/4]补= 0.00014.2 已知X和Y,用变形补码计算X+Y和X-Y,并指出运算结果是否溢出:(1) X=0.11011,Y=0.11111(2) X=-0.1101,Y=0.0110答:.(1)[X]补=00.11011 [Y]补=00.11111 [-Y]补=11.00001[X]补 00.11011+ [Y]补 00.11111 [X+ Y]补 01.11010 [X]补 00.11011 + [-Y]补 11.00001 [X-Y]补 11.11100 S f1与S f2不同,溢出S f1与S f2相同,无溢出所以:[X+Y]补:发生溢出[X-Y]补= 1.11100注意:参见P107中的双符号位判溢方法原理。

(2) [X+Y]补=1.1001[X-Y]补:溢出4.4 使用原码一位乘法计算X*Y : (1) X=0.11101,Y=0.01111 (2) X=-0.10011,Y=0.11010答: (1)[X]原=0.11101 [Y]原=0.01111000s s s P X Y =⊕=⊕=部分积0.00000乘数|Y|操作说明Y 5=1,+|X |0.11101+0.11101右移一位0.011100.11101+1.01011右移一位0.10101Y 2=1,+|X |0.11101+1.10010右移一位0.11001Y 1=0,+00.11101+1.10110右移一位0.11011+0.110110.00000 0011 01 0111011 0111 01101111右移一位Y 4=1,+|X |Y 3=1,+|X |100110.01101[]0.01101100110.0110110011P X Y ∴=∴⨯=+原4.5 使用补码Booth 乘法计算X*Y : (1) X=0.01111,Y=-0.11101 (2) X=-0.10011,Y=-0.11010答:(1)[X ]补=00.01111 [Y ]补=11.00011 [-X ]补=11.10001部分积00.00000乘数Y(Y n Y n+1)操作说明11.10001+11.1000111.1100000.00000+11.1100011.1110000.01111+00.01011右移一位00.0010100.00000+00.00101右移一位00.0001000.00000+00.0001000.0000111.1000111.10010+1.0001101 1.000110 1 1.00011 0 1 1.0001101 1.00Y 5Y 6=10,+[-X ]补右移一位Y 4Y 5=11,+0右移一位Y 0Y 1=10,+[-X ]补Y 1Y 2=00,+001101 1.001101右移一位Y 3Y 4=01,+[X ]补Y 2Y 3=00,+0所以:[X*Y ]补=1.1001001101X*Y =-0.01101100114.6 分别使用原码恢复余数除法和原码加减交替除法计算X/Y : (1) X=0.0111,Y=0.1101 (2) X=0.1011,Y=-0.1110 答:(1)原码恢复余数除法注意:参见P124中例4.9。

计算机组成原理第四章课后习题及答案唐朔飞完整版

第4章存储器1. 解释概念:主存、辅存、Cache、RAM、SRAM、DRAM、ROM、PROM、EPROM、EEPROM、CDROM、Flash Memory。

答:主存:主存储器,用于存放正在执行的程序和数据。

CPU可以直接进行随机读写,访问速度较高。

辅存:辅助存储器,用于存放当前暂不执行的程序和数据,以及一些需要永久保存的信息。

Cache:高速缓冲存储器,介于CPU和主存之间,用于解决CPU和主存之间速度不匹配问题。

RAM:半导体随机存取存储器,主要用作计算机中的主存。

SRAM:静态半导体随机存取存储器。

DRAM:动态半导体随机存取存储器。

ROM:掩膜式半导体只读存储器。

由芯片制造商在制造时写入内容,以后只能读出而不能写入。

PROM:可编程只读存储器,由用户根据需要确定写入内容,只能写入一次。

EPROM:紫外线擦写可编程只读存储器。

需要修改内容时,现将其全部内容擦除,然后再编程。

擦除依靠紫外线使浮动栅极上的电荷泄露而实现。

EEPROM:电擦写可编程只读存储器。

CDROM:只读型光盘。

Flash Memory:闪速存储器。

或称快擦型存储器。

2. 计算机中哪些部件可以用于存储信息?按速度、容量和价格/位排序说明。

答:计算机中寄存器、Cache、主存、硬盘可以用于存储信息。

按速度由高至低排序为:寄存器、Cache、主存、硬盘;按容量由小至大排序为:寄存器、Cache、主存、硬盘;按价格/位由高至低排序为:寄存器、Cache、主存、硬盘。

3. 存储器的层次结构主要体现在什么地方?为什么要分这些层次?计算机如何管理这些层次?答:存储器的层次结构主要体现在Cache-主存和主存-辅存这两个存储层次上。

Cache-主存层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于Cache的速度,而寻址空间和位价却接近于主存。

主存-辅存层次在存储系统中主要起扩容作用,即从程序员的角度看,他所使用的存储器其容量和位价接近于辅存,而速度接近于主存。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)计算X+Y A:求阶差:|△E|=|1011-0110|=0101 B:对阶:Y变为 1 011 0 00000 1101101 C:尾数相加:00 0110011 00000+ 00 00000 1101101=00 0110110 01101 D:规格化:左规:尾数为0 1101100 1101,阶码为1010 F:舍入处理:采用0舍1入法处理,则有00 1101100+1=00 1101101 E:不溢出 所以,X+Y最终浮点数格式的结果: 1 010 0 1101101,即 0.1101101*210

参考答案:在教学计算机中, 为控制运算器完成指定的数据运算、 传送功能,必须给出要用的数据组合、ALU要完成的运算功能、和 对运算结果的保存及送出办法; 选择送到ALU最低位的进位信号的状态,如何处理最高、最低位的 移位信号的状态,是否保存运算结果的特征位信号等问题,都要依 据指令执行的实际需求来处理,不是运算器内部功能所能包含的, 故只能到Am2901芯片之外来解决。

4.5 在运算器部件中,为什么要设置一个乘商寄存器?它 在运算器部件中,为什么要设置一个乘商寄存器? 与运算器部件中的累加器有哪些不同之处? 与运算器部件中的累加器有哪些不同之处?

为了用硬件线路完成乘除指令运算,运算器内一般还有 一个能自行左右移位的专用寄存器,通称乘商寄存器。 运算器内的通用寄存器与乘商寄存器的差异表现在:通 用寄存器是暂存将参加运算的数据和中间结果,这些寄 存器可被汇编程度员直接访问与使用;乘商寄存器由计 算机内部设置,不能为汇编程序员访问。

4.8.以教学计算机为例,说明应如何控制与操作运算器完成指定的数据运算、 以教学计算机为例,说明应如何控制与操作运算器完成指定的数据运算、 以教学计算机为例 传送功能,为什么必须在Am2901芯片之外解决向运算器提供最低位的进位信 传送功能,为什么必须在 芯片之外解决向运算器提供最低位的进位信 最低、最高位的移位输入信号,以及状态位的接受与记忆问题。 号,最低、最高位的移位输入信号,以及状态位的接受与记忆问题。设计完 成如下操作功能的操作步骤和必须提供的信号: 送入R0, 的内容送入 成如下操作功能的操作步骤和必须提供的信号:把100送入 ,R0的内容送入 送入 R1,完成 并存入R0, 的内容减 的内容减1, 的内容送入 的内容送入Q, 和 与 联合 ,完成R0-R1并存入 ,R1的内容减 ,R1的内容送入 ,R1和Q与C联合 并存入 右移一位。 右移一位。

4.13.假定 假定X=0.0110011*211,Y=0.1101101*2-10(此处的数均为二进制 。 此处的数均为二进制)。 假定 此处的数均为二进制 浮点数阶码用4位移码、尾数用8位原码表示(含符号位), ),写出 (1)浮点数阶码用4位移码、尾数用8位原码表示(含符号位),写出 该浮点数能表示的绝对值最大、最小的(正数和负数)数值; 该浮点数能表示的绝对值最大、最小的(正数和负数)数值; 写出X 正确的浮点数表示(注意,此处预设了个小陷阱); (2)写出X、Y正确的浮点数表示(注意,此处预设了个小陷阱); 计算X+Y X+Y; (3)计算X+Y; 计算X*Y X*Y。 (4)计算X*Y。

4.6 运算器内的乘商寄存器的为什么会是这样? 位操作之间应有什么样的关联关系吗?为什么会是这样?

乘除寄存器的移位操作与通用寄存器的移位操作是联合 移位,没有乘除寄存器单独移位功能。当通用寄存器本 身移位时,乘除寄存器不受影响。

4.8.以教学计算机为例,说明应如何控制与操作运算器完成指定的数据运算、 以教学计算机为例,说明应如何控制与操作运算器完成指定的数据运算、 以教学计算机为例 传送功能,为什么必须在Am2901芯片之外解决向运算器提供最低位的进位信 传送功能,为什么必须在 芯片之外解决向运算器提供最低位的进位信 最低、最高位的移位输入信号,以及状态位的接受与记忆问题。 号,最低、最高位的移位输入信号,以及状态位的接受与记忆问题。设计完 成如下操作功能的操作步骤和必须提供的信号: 送入R0, 的内容送入 成如下操作功能的操作步骤和必须提供的信号:把100送入 ,R0的内容送入 送入 R1,完成 并存入R0, 的内容减 的内容减1, 的内容送入 的内容送入Q, 和 与 联合 ,完成R0-R1并存入 ,R1的内容减 ,R1的内容送入 ,R1和Q与C联合 并存入 右移一位。 右移一位。

4.1解释定点运算器的功能和组成部件?以Am2901芯片为 4.1解释定点运算器的功能和组成部件? Am2901芯片为 解释定点运算器的功能和组成部件 实例,来介绍定点运算器的有关知识,你的认知程度如何? 实例,来介绍定点运算器的有关知识,你的认知程度如何?

例如,Am2901芯片,其组成部分包括一个算术逻 辑运算部件,完成对数据的算术运算和逻辑运算; 一个由16个通用寄存器组成的寄存器组,以暂存 参加运算的数据和中间结果;一个Q寄存器,实 现硬件乘除运算;有5组二选一或三选一器件, 以选择数据的输入和送出运算结果;有9个控制 信号:其中I5~I3选择运算功能,I2~I0选择数 据来源,I8~I6控制数据处理方式,从而实现与 计算机其它部件协调工作。

4.13.假定 假定X=0.0110011*211,Y=0.1101101*2-10(此处的数均为二进制 。 此处的数均为二进制)。 假定 此处的数均为二进制 浮点数阶码用4位移码、尾数用8位原码表示(含符号位), ),写出 (1)浮点数阶码用4位移码、尾数用8位原码表示(含符号位),写出 该浮点数能表示的绝对值最大、最小的(正数和负数)数值; 该浮点数能表示的绝对值最大、最小的(正数和负数)数值; 写出X 正确的浮点数表示(注意,此处预设了个小陷阱); (2)写出X、Y正确的浮点数表示(注意,此处预设了个小陷阱); (3)计算X+Y; 计算X+Y; X+Y 计算X*Y X*Y。 (4)计算X*Y。 4)计算X*Y A:阶码相加:[X+Y]移=[X]移+[Y]补=01 011+11 110=01 001 (符号位10第1位为0,不溢出;00时上溢,01时下溢) B:尾数相乘结果:0 1010110 110111 C:已满足规格化要求,不需左规,尾数不变,阶码仍为001 D:舍入处理:按0舍1入规则,尾数之后的6位110111舍去,尾数 +1=0 1010111 所以,X*Y最终浮点数格式的结果: 1 001 0 1010111,即 0.1010111*21

注意:最后一项操作中,移入通用寄存起R1最高位的不是状态触发器C的值,而是 ALU运算的符号位Cy的值,通用寄存器和Q联合右移时,不能支持与C的循环移位。

4.10 在浮点数中为什么采用隐藏位?在什么时刻处理隐藏 在浮点数中为什么采用隐藏位? 位?

原码尾数中使用隐藏位技术,是指把非“0”值的 规格化浮点数的尾数最高位上的1强行去掉(隐 藏起来),这是通过左移原来的尾数实现的,最 高位上的1看不见了,却可以使结果的表示精度 多出了一个二进制位,考虑到隐藏位和剩余尾数, 则此时它所代表的实际值在1~2之间。

计算机组成原理第四章习题

4.1解释定点运算器的功能和组成部件?以Am2901芯片为 4.1解释定点运算器的功能和组成部件? Am2901芯片为 解释定点运算器的功能和组成部件 实例,来介绍定点运算器的有关知识,你的认知程度如何? 实例,来介绍定点运算器的有关知识,你的认知程度如何?

答:定点运算器的功能与组成 ⑴ 对数据进行算术运算和逻辑运算,给出结果某些特征; ⑵ 暂存参加运算的数据和中间结果; ⑶可用硬件完成乘除运算; ⑷ 接受外部数据的输入,送出运算结果; ⑸与计算机其他部件协同工作运算器的组成:①算术与 逻辑运算部件;②通用寄存器;③乘商寄存器;④多路 选择器;⑤输入/输出逻辑电路。

解答:(1)绝对值最大: 1 111 0 1111111、1 111 1 1111111; 绝对值最小: 0 001 0 0000000、0 001 1 0000000 (2)X: 1 011 0 0110011、Y: 0 110 0 1101101

4.13.假定 假定X=0.0110011*211,Y=0.1101101*2-10(此处的数均为二进制 。 此处的数均为二进制)。 假定 此处的数均为二进制 浮点数阶码用4位移码、尾数用8位原码表示(含符号位), ),写出 (1)浮点数阶码用4位移码、尾数用8位原码表示(含符号位),写出 该浮点数能表示的绝对值最大、最小的(正数和负数)数值; 该浮点数能表示的绝对值最大、最小的(正数和负数)数值; 写出X 正确的浮点数表示(注意,此处预设了个小陷阱); (2)写出X、Y正确的浮点数表示(注意,此处预设了个小陷阱); 计算X+Y X+Y; (3)计算X+Y; 计算X*Y X*Y。 (4)计算X*Y。