杭电计组实验考试

杭电计组实验四

0000_0003

$00011

7FFF_FFFF

7FFF_FFFF

$00111

7FFF_FFFF

7FFF_FFFF

$01111

0000_0000

0000_0000

$11111

000ቤተ መጻሕፍቲ ባይዱ_0003

0000_0003

$10000

7FFF_FFFF

7FFF_FFFF

$11000

7FFF_FFFF

input [4:0] W_Addr;

input [31:0] W_Data;

input Write_Reg;

input Clk;

input Reset;

output [31:0] R_Data_A;

output [31:0] R_Data_B;

integer i;

reg[31:0] REG_Files[31:0];//定义寄存器

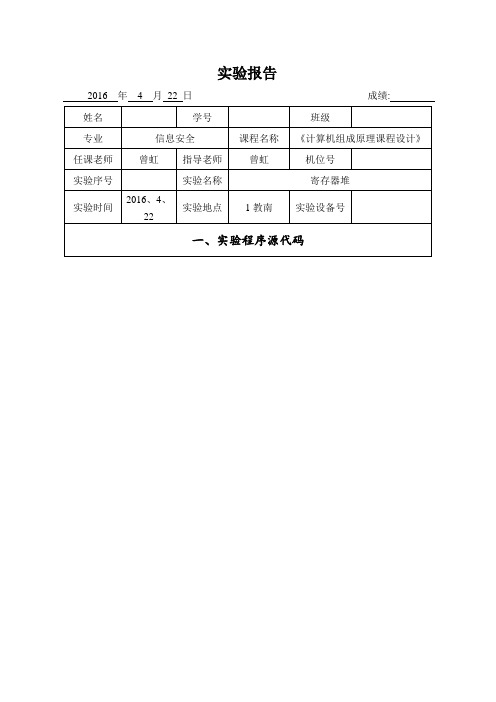

实验报告

2016年4月22日成绩:

姓名

学号

班级

专业

信息安全

课程名称

《计算机组成原理课程设计》

任课老师

曾虹

指导老师

曾虹

机位号

实验序号

实验名称

寄存器堆

实验时间

2016、4、22

实验地点

1教南

实验设备号

一、实验程序源代码

module Reg(LED,RW_SW,AB,Reg_Addr_A,Reg_Addr_B,Write_Reg,clk,rst);

NET "Add[3]" LOC = "V8";

NET "Add[2]" LOC = "U8";

杭电计组实验5-存储器设计实验

5’b000007 32’b0000000732’b0000000732'h0055_752332'h0055_7523

(2)答:这些单元的数据已经被改写了。读出数据与写入数据一致。

RAM_B uut (

.clka(clka),

.wea(wea),

.addra(addra),

.dina(dina),

.douta(douta)

);

initial begin

// Initialize Inputs

clka = 0;

wea = 0;

addra = 0;

dina = 0;

// Wait 100 ns for global reset to finish

NET "Clk" LOC = C9;

NET "LED[4]" LOC = M11;

NET "LED[3]" LOC = V15;

NET "LED[2]" LOC = U15;

NET "LED[1]" LOC = V16;

NET "LED[0]" LOC = U16;

NET "Mem_Addr[7]" LOC = U8;

output reg [7:0]LED;

wire [31:0]M_R_Data;//存在存储器里的32位读出数据

reg [31:0]M_W_Data;//寄存在暂存器的32位写入数据

RAM_B test_ram (

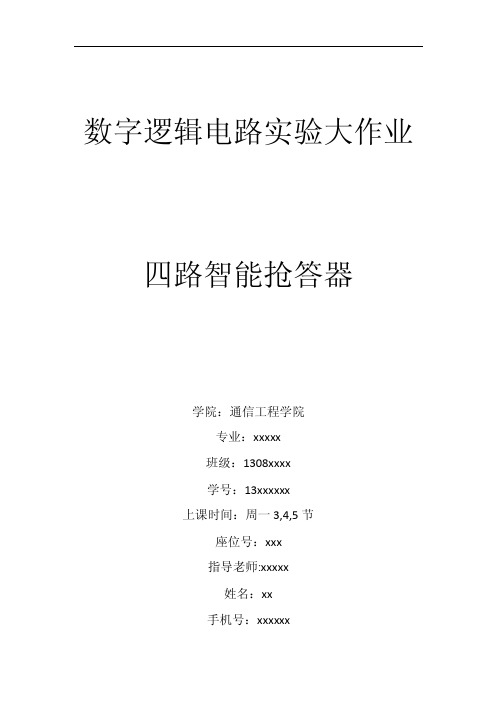

杭电-数字逻辑电路实验大作业-四路智能抢答器

数字逻辑电路实验大作业四路智能抢答器学院:通信工程学院专业:xxxxx班级:1308xxxx学号:13xxxxxx上课时间:周一3,4,5节座位号:xxx指导老师:xxxxx姓名:xx手机号:xxxxxx一、 项目概况在主持人发出抢答命令之后,四只队伍可以同时抢答,如果有一支队伍抢答成功,立马封锁输入端口以禁止其他队伍抢答,并且抢到机会的队伍共阴极显示器显示其队伍号码。

即,做一个四路智能抢答器。

1 2四路智能抢答器大概框图1、 系统简介:通过优先编码器,寄存器和译码器实现一个4路智能选择器。

2、 系统框图,如下图四路智能抢答器详细框图3、各模块具体设计:①优先编码电路模块(74148芯片):1,2,3,4分别代表队伍1,队伍2,队伍3,队伍4。

假如队伍1抢答,则1234输入序列为0111,假如是队伍2抢答则输入1011,假如是队伍3抢答,则输入1101,假如是队伍4抢答,则对应输入1110。

②锁存器模块(74279芯片)AO,A1,A2为优先编码器的三个输出,根据锁存器真值表可以如上图去连接。

③译码器模块(7448芯片)7448为译码器,其输入A,B,C,D分别对应锁存器的输出Q2,Q3,和地,根据真值表,译码器可以将锁存器传输进来的序列翻译成相应的序列。

总体实验电路图:4、仿真波形:例如:队伍1抢答,输入序列0111,输出序列0110000,根据7448真值表可知,0110000对应的十进制数为1,仿真成功!例如:队伍3抢答,输入序列1101,输出序列1111001,根据7448真值表可知,1111001对应的十进制数为3,仿真成功!三、参考资料:1.74148中文资料:2、74279中文资料:3、7448芯片中文资料:真值表:4、数字电子技术基础(第二版)科学出版社四、实验过程遇到的问题及解决方案:这次试验在电路设计方面问题不是很大,但是在软件使用上出现了一些问题,先是把工具栏关掉导致无法快速的绘制实验电路图,然后后来绘制仿真波形的时候又不慎把输入信号序列快捷方式关闭,导致后面的实验进程比较缓慢。

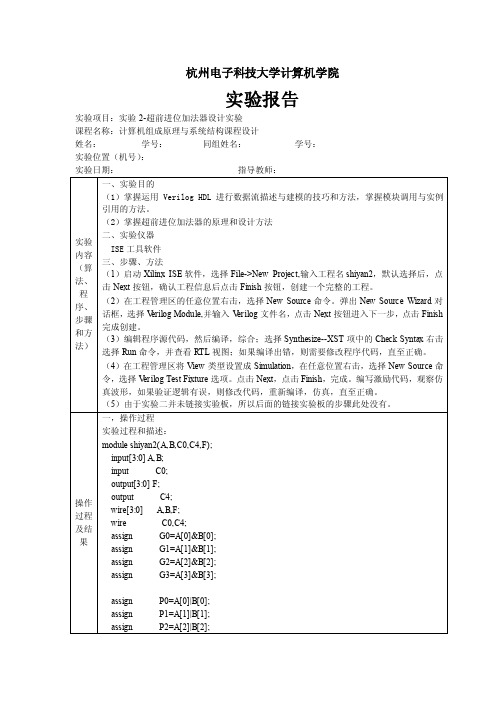

杭电计组实验2-超前进位加法器设计实验

杭州电子科技大学计算机学院

实验报告

实验项目:实验2-超前进位加法器设计实验

课程名称:计算机组成原理与系统结构课程设计

姓名:学号:同组姓名:学号:

实验位置(机号):

实验日期:指导教师:

二、结果

思考题:

(1)综合得到的电路图,它和想要设计的电路在引脚的输入输出方面是完全相同的,但是相比较内部的RTL图,实验实现的结果是相同的,但是我编写的实验代码并没有调用实验一的全加器设计。

(2)尝试编写8位超前进位加法器设计实验

module add_8 ( input [7:0]a, input [7:0]b, input cin, output [7:0] s, output co );

wire [7:0]c_tmp;

wire [7:0]g;

wire [7:0]p;。

杭电计算机组成原理A卷

1、在CPU执行的一段时间内,Cache完成存取的次数为3900次,主存完成的存取次数为100次,已知Cache的存储周期为15ns,主存的存储周期为75ns。则Cache的命中率为(1),Cache/主存系统的平均访问时间为(2)ns,Cache/主存系统的效率为(3)。

RD(2位)

ADDR/ DATA / DISP

其中,RD为源/目的寄存器号,MOD为寻址方式码字段,指令第二字为地址、数据或偏移量;源操作数由MOD字段和指令第二字共同确定。除了HALT指令为单字指令外,其他指令均为双字指令;操作码字段解释见表1-1,MOD字段解释见表1-2,RD字段解释见表1-3。

表1-1

指令助记符

操作码

指令助记符

操作码

MOV

0000

SBB

0100

ADD

0001

JMP

1000

SUB

0010

……

……

AND

0011

HALT

1111

表1-2表1-3

MOD

寻址方式

RD

寄存器

00

立即寻址

00

R0

01

直接寻址

01

R1

10

变址寻址(SI)

10

R2

11

间接寻址

11

R3

1指令ADDR1,((40H))的功能:R1 = ((40H))+R1;指令使用间接寻址,则该指令机器码第一字节为(9)H,第二字节为(10)H。

杭州电子科技大学学生考试卷(A)卷

考试课程

计算机组成原理(甲)

考试日期

成 绩

课程号

教师号

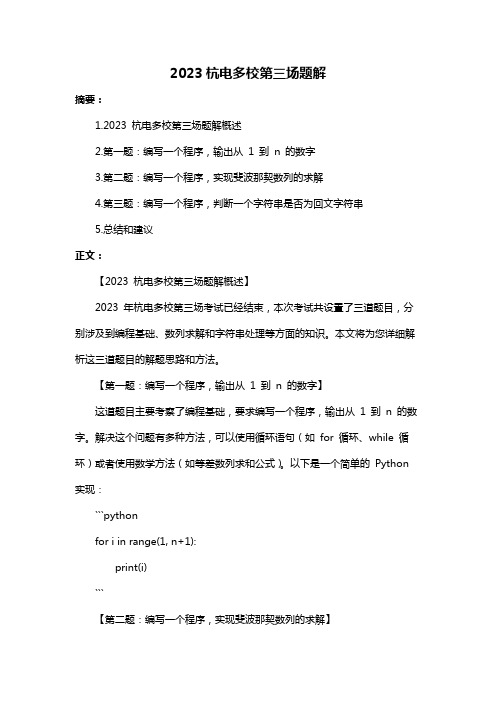

2023杭电多校第三场题解

2023杭电多校第三场题解摘要:1.2023 杭电多校第三场题解概述2.第一题:编写一个程序,输出从1 到n 的数字3.第二题:编写一个程序,实现斐波那契数列的求解4.第三题:编写一个程序,判断一个字符串是否为回文字符串5.总结和建议正文:【2023 杭电多校第三场题解概述】2023 年杭电多校第三场考试已经结束,本次考试共设置了三道题目,分别涉及到编程基础、数列求解和字符串处理等方面的知识。

本文将为您详细解析这三道题目的解题思路和方法。

【第一题:编写一个程序,输出从1 到n 的数字】这道题目主要考察了编程基础,要求编写一个程序,输出从1 到n 的数字。

解决这个问题有多种方法,可以使用循环语句(如for 循环、while 循环)或者使用数学方法(如等差数列求和公式)。

以下是一个简单的Python 实现:```pythonfor i in range(1, n+1):print(i)```【第二题:编写一个程序,实现斐波那契数列的求解】斐波那契数列是一个经典的数列问题,要求编写一个程序,实现斐波那契数列的求解。

斐波那契数列的定义为:F(0)=0,F(1)=1,F(n)=F(n-1)+F(n-2)。

解决这个问题有多种方法,可以使用递归、循环或者矩阵求幂等方法。

以下是一个简单的Python 实现:```pythondef fibonacci(n):if n == 0:return 0elif n == 1:return 1else:return fibonacci(n-1) + fibonacci(n-2)print(fibonacci(n))```【第三题:编写一个程序,判断一个字符串是否为回文字符串】回文字符串是指正序和倒序都相同的字符串,如“abcdcba”。

这道题目要求编写一个程序,判断一个字符串是否为回文字符串。

解决这个问题有多种方法,可以使用双指针法、哈希表或者直接比较字符串等方法。

以下是一个简单的Python 实现:```pythondef is_palindrome(s):s = s.lower()left, right = 0, len(s) - 1while left < right:if s[left]!= s[right]:return Falseleft += 1right -= 1return Trueprint(is_palindrome("abcdcba"))```【总结和建议】本次考试的三道题目涉及到了编程基础、数列求解和字符串处理等方面的知识。

杭电计组实验10-实现R-I-J型指令的CPU设计实验精编版

4'b0111:LED=M_R_Data[31:24];

4'b1000:begin LED[7:2]=0;LED[1]=OF;LED[0]=ZF;end

4'b1100:LED=PC[7:0];

4'b1101:LED=PC[15:8];

4'b1110:LED=PC[23:16];

.clka(clk),

.addra(PC[7:2]),

.douta(Inst_)

);

assign PC_new=PC+4;

always@(negedge clk or posedge rst)

begin

if(rst)

PC<=32'h00000000;

else

begin

case(PC_s)

2'b00:PC<=PC_new;

wire [31:0] PC;

// Instantiate the Unit Under Test (UUT)

TOP_RIJ_CPU uut (

.rst(rst),

.clk_100MHz(clk_100MHz),

.clk(clk),

.ZF(ZF),

.OF(OF),

.F(F),

.M_R_Data(M_R_Data),

rt_imm_s,Mem_Write,address,w_r_s,wr_data_s,PC_s,ZF);

assign W_Addr=(w_r_s[1])?5'b11111:((w_r_s[0])?rt:rd);

assign imm_data=(imm_s)?{{16{imm[15]}},imm}:{{16{1'b0}},imm};

操作系统实验 带答案版

if(strcmp(sender,tcb[i].name)==0){

id=i;

break;

}

}

if(id==-1) {

enable();

return(0);

}

p(&tcb[current].sm);

p(&tcb[current].mutex);

buff=remov(&(tcb[current].mq),id);

if(current==NTCB) current=1;

}

if(tcb[current].state!=READY) current=0;

_SS=(4)tcb[current].ss;

_SP=(5)tcb[current].sp;

tcb[current].state=RUNNING;

timecount=0;

insert(&freebuf,buff);

v(&mutexfb);

v(&sfb);

enable();

return(size);

}

八.请问应如何让new_int8()发挥作用?并说明系统是如何转去执行new_int8()的?

编写new_int8有两种方法,一种是研究原有的时钟中断程序INT 08H,修改它的代码;另一种是利用getvect()函数获取系统原来的INT 08 H的入口地址,用我们新编写的new_int8()函数去调用它,利用setvect()函数将new_int8()函数装入。如果时间片到,DOS不忙,则执行new_int8()。

v(&tcb[current].mutex);

if(buff==NULL){

杭电2018计组期末Test chapter 7 CPU Controller

wr_data_s

ALU_OP

Write_Reg Mem_Write

PC_s

实现R型指令的处理器结构

2.srav 是对(有符号)数据的算术右移指令,考虑如何实现? 讨论课前思考题 1:寄存器堆、PC和标志寄存器的打入脉冲是怎么得到的?

b[31:26](OP)

4 PC_ new

ADD

指

b[5:0](func)

Test 2

设label1指令的地址为40000,下表为label1开始的各指 令的机器代码,则表5中rs、rt、offset和address分别等 ________,数组A中每个元素 位。

地址 6位 5位 5位 5位 5位 6位

40000

40004 40008 4000C

0

0 35 5

0

11 rs 9

9

0

0 offset 1

32

address ……

Test 1

简答

MIPS的编址单位是多少?数组save的每个元素占几个 字节? 该循环指令序列中哪些是R型指令?哪些是I型指令? $t1和$s5的编号各是多少? 标号exit的值是多少?如何根据指令计算得到? 标号loop的值是多少?如何根据指令计算得到?

写出表中各指令的数据通路对应的控制信号之值。若 某信号无论取何值都不影响指令的功能,则该信号填 “-”。

指令 addi w_r_s imm_s rt_imm_ s wr_data_s ALU_OP Write_Reg Mem_Write PC_s

lw

bne

某高级语言源程序中的语句:

while ( A[i] == k ) i+ = 1

add $s0,$zero,$zero label1: sll $t3,$s0,2 add $t3,$t3,$t0 lw $t1,0($t3) bne $t1,$s1,label2 addi $s0,$s0,1 j label1 label2: …

杭电2018计组期末Test chapter 7 CPU Controller

Test 1

某高级语言源程序中的语句:

while ( A[i] == k ) i+ = 1

若对其编译时,编译器将i和k分别分配在寄存器$s3和 $s5中,数组A的基址存放在$s6中,则生成的MIPS汇 编代码段如下:

add $s3, $zero, $zero loop: sll $t1, $s3, 2 add $t1, $t1, $s6 lw $t0, 0($t1) bne $t0, $s5, exit addi $s3, $s3, 1 j loop exit: … #左移: R[$t1]=R[$s3]<<2, 即R[$t1]=i×4 #算术加:R[$t1]=R[$t1]+ R[$s6],即R[$t1]=address of A[i] #取数: R[$t0]=M[R[$t1]+ 0], 即R[$t0]=A[i] #不相等转移:R[$t0]≠R[$s5] then goto exit #算术加: R[$s3]=R[$s3]+ 1,即i=i+1 #无条件转移:goto loop

译码及 控制单元

Write_Reg R_Addr_A R_Addr_B W_Addr

32 ALU_OP

令 b[25:21](rs)

PC rst

Inst_addr Inst_code 指令存储器

机 b[20:16](rt) 器

R_Data_A 寄存器堆

rt_imm_s

A

指 码 b[15:11](rd) 令 机 器 码

ALU

0 1

B

clk rst

32

imm offset

16

符号 扩展

wr_data_s 0 1 2 3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

input Clk,Reset;

input wire Write_Reg;

input wire[4:0] R_Addr_A;

input wire[4:0] W_Addr;

input wire[4:0] R_Addr_B;

input wire[31:0] W_Data;

reg[31:0] // input [31 : 0] dina

.douta(douta) // output [31 : 0] douta

);

always@(posedge rst or posedge clka)

begin

if(rst)

PC<=32'h00000000;

else

PC<=PC_new;

,ALU_B,rt_imm_s,Mem_Write,M_R_Data,ALU_Data,alu_mem_s);

input wire clk;

input reset;

output [2:0] ALU_OP;//操作符

output [31:0] inst;//指令存放

output [4:0] rs;//rs地址

rt=inst[20:16];//rt

rs=inst[25:21];//rs

Mem_Write=0;//是否写入数据存储器

rd_rt_s=1;//rt作为目的存储器

rt_imm_s=1;//imm作为源操作数

alu_mem_s=0;//以alu结果输出

Write_Reg=1;

//判断属于那条指令

case(inst[31:26])

.W_Addr(W_Addr),

.W_Data(W_Data),

.R_Data_A(rs_data),

.R_Data_B(rt_data),

.Reset(reset),

.Write_Reg(Write_Reg) //不写入

);

assign ALU_B=(rt_imm_s)?imm_data:rt_data;

REG_Files[i]<=32'h00000000;

end

else

begin

if(Write_Reg)

REG_Files[W_Addr]<=W_Data;

end

end

assign R_Data_A=REG_Files[R_Addr_A];

assign R_Data_B=REG_Files[R_Addr_B];

output reg [4:0] rs;

output reg [4:0] rt;

output reg [4:0] rd;

output reg Write_Reg;

output reg [15:0] imm;

output reg rd_rt_s;

output reg imm_s;

output reg rt_imm_s;

output [4:0] rt;//rt地址

output [4:0] rd;//rd地址

output [31:0] rs_data;//rs数据

output [31:0] rt_data;//rt数据

output [31:0] rd_data;//rd数据

output [31:0] PC;

output [31:0] PC_new;

output ZF;

output OF;

output Write_Reg;//是否写入

output [31:0] W_Data;

output rd_rt_s; //控制那个作为目的寄存器

output [4:0]W_Addr;//目的操作数地址

output [15:0] imm; //立即数

output [31:0] imm_data;//被扩展的立即数

6'b001000: begin imm_s=1; ALU_OP=3'B100;end

6'b001100: begin imm_s=0; ALU_OP=3'B000;end

6'b001110: begin imm_s=0; ALU_OP=3'B010;end

6'b001011: begin imm_s=0; ALU_OP=3'B110;end

rt=inst[20:16];//rt

rs=inst[25:21];//rs

alu_mem_s=0;//以alu结果输出

Mem_Write=0;//是否写入数据存储器

rd_rt_s=0;//rd作为目的存储器

rt_imm_s=0;//rt作为源操作数

Write_Reg=(inst[5:0]==0)?1'b0:1'b1;

endmodule

ALU模块:

module ex3(ALU_OP,A,B,F,ZF,OF

);

input[2:0] ALU_OP;

input[31:0] A,B;

output reg [31:0] F;

output reg ZF,OF;

endcase

end

//----------------处理I型取数/存数指令------------------

if(inst[31:30]==2'b10&&inst[28:26]==3'b011)

begin

imm=inst[15:0];

rt=inst[20:16];//rt

rs=inst[25:21];//rs

reg [0:0] wea;

assign PC_new=PC+4;

initial

begin

PC=32'h00000000;

wea=0;

end

ex77 regrom (

.clka(clka), // input clka

.wea(wea), // input [0 : 0] wea

.addra(PC[7:2]), // input [5 : 0] addra

.rs(rs),

.rt(rt),

.rd(rd),

.Write_Reg(Write_Reg),

.imm(imm),

.rd_rt_s(rd_rt_s),

.imm_s(imm_s),

.rt_imm_s(rt_imm_s),

.Mem_Write(Mem_Write),

.alu_mem_s(alu_mem_s)

case(inst[5:0])//映射对应的ALU

6'b100000:ALU_OP=3'B100;

6'b100010:ALU_OP=3'B101;

6'b100100:ALU_OP=3'B000;

6'b100101:ALU_OP=3'B001;

6'b100110:ALU_OP=3'B010;

6'b100111:ALU_OP=3'B011;

endmodule

pc模块:

module ex7(clka,douta,rst,PC,PC_new

);

input rst;

input clka;

output wire[31:0] douta;

output reg[31:0] PC;

output [31:0] PC_new;

wire [31:0]dina;

6'b101011: begin Mem_Write=1;Write_Reg=0;ALU_OP=3'B100;end

endcase

end

end

endmodule

Reg模块

module reg1(R_Addr_A,R_Addr_B,Clk,W_Addr,W_Data,R_Data_A,R_Data_B,Reset,Write_Reg

output imm_s;//是否需要扩展

output rt_imm_s;//B端选择rt或者是imm

output [31:0] ALU_B;//ALU_B端口数据

output Mem_Write;//是否写入数据rom

output [31:0]M_R_Data;//从数据rom读出来的数据

output [31:0]ALU_Data;//ALU运算出来的结果,根据alu_mem_s选择由M_W_Data或者W_Data来赋值

6'b101011:ALU_OP=3'B110;

6'b000100:ALU_OP=3'B111;

endcase

end

//------------------处理I型立即寻址指令------------------------

if(inst[31:29]==3'b001)

begin

imm=inst[15:0];

);

//读取源操作数的值:

assign W_Addr = (rd_rt_s)?rt:rd;

assign imm_data = (imm_s)?{{16{imm[15]}},imm}:{{16{1'b0}},imm};

reg1 Reg(

.R_Addr_A(rs),

.R_Addr_B(rt),

.Clk(clk),

.addra(ALU_Data[5:0]), // input [5 : 0] addra

.dina(rt_data), // input [31 : 0] dina

.douta(M_R_Data) // output [31 : 0] douta

);

assign W_Data = alu_mem_s?M_R_Data:ALU_Data;