MPSK调制与解调VHDL程序与仿真

PSK原理及调制解调仿真

2PSK 信号的功率谱密度

若二进制基带信号s(t)的功率谱密度Ps( f ) 为 二进制相移键控信号的功率谱密度为

第9页/共17页

2PSK调制与解调simulink仿真图

载波1 载波2(二者幅度相反)基带信号发生器 高斯噪声源 码型变换器 键控开关 调制部分示波器 加法器 乘法器 带通滤波器 低通滤波器 误码表 抽样判决器 解调部分示波器

参考文献通信原理(国防工业出版社 第六版)基于MATLA贵资料原理整理:张凯强 尹强PPT制作:沐辰梓

第1页/共17页

通信系统就是传递信息所需要的一切技术设备和传输媒质的总和,包括信息源、发送设备、信道、接收设备和信宿(受信者)

第12页/共17页

加入高斯噪声后波形

第一路为加入了高斯噪声的2PSK信号波形第二路为加入的同频同相的载波波形第三路是2PSK信号与载波相乘的波形,由于调制波形通过了调制信道,叠加了噪声,并且通过恢复载波,最后的波形就变成了下面的图形。这是因为经过了恢复载波乘法器之后,2PSK叠加噪声之后的波形与恢复载波相乘,正正得正,正负得负,所以才形成了上下不一的图形。第四路是低通滤波后的波形,通过低通滤波器之后相当于载波提取后的波形与低通滤波器的波形相互卷积,并且下图的大概包络与载波提取后的波形包络大概相同,而且还有噪声的滤波器的一些不理想因素造成了滤波后的波形出现了波纹幅度;第五路为抽样判决的波形第六路为经过极性变换后的波形通过波形对比分析可知2PSK信号解调由于噪声的影响解调基本成功

第13页/共17页

第14页/共17页

结论:信号经过低通滤波器后,去除高频成分,得到包含基带信号的低频信号,加入方差越小的波形滤波后得到的信号与基带信号更相似

第15页/共17页

MPSK调制与解调VHDL程序与仿真

课程设计任务书学生姓名:专业班级:指导教师:工作单位:题目:MPSK调制与解调VHDL程序与仿真初始条件:选择的FPGA芯片不限,选用的仿真工具不限要求完成的主要任务:完成MPSK调制与解调FPGA实现过程,能熟练使用VHDL语言对其调制与解调程序的描述,以及对仿真结果的分析。

时间安排:1、2014年5月30日,布置课设具体实施计划与课程设计报告格式的要求说明。

2、2014年5月31日至2014年6月15日,设计说明书撰写。

3、2014年6月18日,上交课程设计成果及报告,同时进行答辩。

指导教师签名:2014年月日系主任(或责任教师)签名:2014年月日摘要本论文是为了设计在FPGA(Field-Programmable Gate Array,现场可编程门阵列)上实现MPSK(多进制相移键控)调制解调的功能。

在Quartus Ⅱ平台上,运用VHDL硬件描述语言进行编程,对整个MPSK 系统进行仿真,得到仿真时序图,对程序代码进行XST综合,得到RTL 视图。

仿真结果表明该设计的正确性以及可行性,更清晰直观的了解到MPSK调制解调的原理。

关键词:MPSK;Quartus Ⅱ;VHDL语言AbstractThis paper is designed to achieve MPSK (M-ary Phase Shift Keying) modulation and demodulation functions in FPGA (Field-Programmable Gate Array, a field programmable gate array) on. On the Quartus Ⅱplatform, the use of VHDL hardware description language programming for the entire MPSK system simulation, simulation timing diagram of the program code XST synthesis, get RTL view. Simulation results show the correctness and feasibility of the design, intuitive to understand more clearly the principle of MPSK modulation and demodulation.Keywords: MPSK; Quartus Ⅱ; VHDL language摘要 (I)Abstract (II)目录 (1)引言 (2)1 MPSK调制解调的原理 (3)2 QPSK调制实现方法 (3)2.1相乘电路 (3)2.2选择法 (4)3 QPSK解调实现方法 (4)4 QPSK调制解调电路的FPGA实现过程 (5)4.1 QPSK调制解调实现依据 (5)4.2 QPSK调制及仿真结果 (5)4.3 QPSK解调及仿真结果 (7)5总结 (9)6参考文献 (10)附录ⅠQPSK调制程序 (11)附录Ⅱ:QPSK解调程序 (12)作为数字通信技术中重要组成部分的调制解调技术一直是通信领域的热点课题。

基于VHDL语言的QPSK调制与解调的实现解读

毕业设计(论文)题目:基于VHDL语言的QPSK调制与解调的实现年月日毕业设计(论文)原创性声明本人郑重声明:所提交的毕业设计(论文),是本人在导师指导下,独立进行研究工作所取得的成果。

除文中已注明引用的内容外,本毕业设计(论文)不包含任何其他个人或集体已经发表或撰写过的作品成果。

对本研究做出过重要贡献的个人和集体,均已在文中以明确方式标明并表示了谢意。

论文作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保障、使用学位论文的规定,同意学校保留并向有关学位论文管理部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权省级优秀学士学位论文评选机构将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

本学位论文属于1、保密□,在_____年解密后适用本授权书。

2、不保密□。

(请在以上相应方框内打“√”)论文作者签名:日期:年月日导师签名:日期:年月日目录摘要 (I)Abstract.................................................. I I 1 绪论.. (1)1.1 数字调制解调技术 (1)1.2 研究内容及意义 (1)2 MPSK的调制原理 (2)2.1 二进制移相键控(BPSK) (2)2.2 MPSK调制与解调的原理 (2)2.3 QPSK调制原理 (3)3 系统设计 (5)3.1 QPSK调制系统 (5)3.1.1 成型滤波器 (5)3.1.2 QPSK信号的载波调制 (5)3.1.3 QPSK的星座图 (5)3.2 调制解调设计 (6)3.2.1 QPSK调制原理 (6)3.2.2 QPSK调制电路框图 (6)3.2.3 QPSK解调原理 (7)3.2.4 QPSK解调电路框图 (8)4 系统实现 (9)4.1 硬件描述性语言 (9)4.2 软件开发工具 (10)4.3 调制模块 (10)4.2 解调模块 (10)5 程序实现与仿真 (12)5.1 工程的建立 (12)5.2 调制程序仿真 (13)5.3 解调程序仿真 (15)结论 (18)参考文献 (19)附录 (22)基于VHDL语言的QPSK调制与解调的实现摘要:随着当今世界信息化的飞速发展,各国对通信行业都加大了支持。

完整版PSK原理及MATLAB仿真

S(t)

相对

码元1 0 1 10 0

调相

t

图4 相对移相的波形示意图

一般情况下,相对移相可通过对信码进行变换 和绝对移相来实现。将信码经过差分编码变换成新 的码组 ——相对码,再利用相对码对载波进行绝对 移相,使输出的已调载波相位满足相对移相的相位 关系。

3. 2PSK的调制原理

? 数字调相:如果两个频率相同的载波同时开始 振荡,这两个频率同时达到正最大值,同时达 到零值,同时达到负最大值,它们应处于“同 相”状态;如果其中一个开始得迟了一点,就 可能不相同了。如果一个达到正最大值时,另 一个达到负最大值,则称为“反相”。

PSK 原理及MATLAB 仿真

前言

? 移动通信的迅速发展,离不开很多关键技术的支

持与应用 ,数字调制在通信领域中就发挥着重大

的作用

? 为了使数字信号在带通信道中传输,必须使用数 字基带信号对载波进行调制,以使信号与信道的 特性匹配

? 由于PSK在生活中有着广泛的应用,本课题主要 介绍了 PSK 波形的产生和仿真过程

形');

所得波形图如下:

for i=1:7 if a(i)==0 for j=1:50 out(j+50*(i-1))=f(j); end else for j=1:50 out(j+50*(i-1))=-f(j); end end

end for i=1:7

for j=1:50 m=0;n=0; if out(j+50*(i-1))-f(j)==0 m=m+1; end if out(j+50*(i-1))+f(j)==0 n=n+1; end

码元定时与载波的关系可以是同步的,以 便清晰观察码元变化时对应调制载波的相应 变化;也可以是异步的,因为实际的系统都 是异步的,码元速率约为1Mbt/s。

PSK的调制与解调仿真

1 EWB仿真软件简介EWB软件,全称为ELECTRONICS WORKBENCH EDA,是交互图像技术有限公司在九十年代初推出的EDA软件,用于模拟电路和数字电路的仿真,利用它直接从屏幕上看到电路的输出波形。

EWB是一款小巧,但是十分强大。

EWB软件由INTERACTIVE IMAGE TECHNOLOGIES Ltd(交互图像技术有限公司)推出,近几年开始在国内使用。

现在普遍使用的是在WIN95环境下工作的EWB5.0(在国内曾见过6.0的演示版,注:EWB5.0也可以在WINDOWS3.1环境下使用,但需安装WING32工具)。

相对其它EDA软件而言,它是个较小巧的软件,只有16M,功能也比较单一,就是进行模拟电路和数字电路的混合仿真,但你绝对不可小瞧它,它的仿真功能十分强大,可以几乎100%地仿真出真实电路的结果,而且它在桌面上提供了万用表、示波器、信号发生器、扫频仪、逻辑分析仪、数字信号发生器、逻辑转换器等工具,它的器件库中则包含了许多大公司的晶体管元器件、集成电路和数字门电路芯片,器件库中没有的元器件,还可以由外部模块导入,在众多的电路仿真软件中,EWB是最容易上手的,它的工作界面非常直观,原理图和各种工具都在同一个窗口内,未接触过它的人稍加学习就可以很熟练地使用该软件,对于电子设计工作者来说,它是个极好的EDA工具,许多电路你无需动用烙铁就可得知它的结果,而且若想更换元器件或改变元器件参数,只需点点鼠标即可,它也可以作为电学知识的辅助2方案分析与方案确定2.1数字基带信号的传输本次课设中涉及到的通信技术为信息传输技术中“数字调制与解调。

通过数字调制与解调,可以把信号变成适合在信道中传输的信号。

调制与解调技术可以提高信号传输的可靠性和有效性,增强信号的抗干扰能力,减小发射天线的尺寸,削减传输成本。

基于以上特点,数字信号的调制与借条在通信领域有广泛的应用。

调制一般可分为两种类型:(1) 利用模拟方法去实现数字调制,即把数字基带信号当作模拟信号的特殊情况来处理;(2) 利用数字信号的离散取值特点键控载波,从而实现数字调制——键控法。

基于VHDL的基带信号的MFSK调制

--多进制数字频率调制(MFSK)系统 VHDL 程序 --文件名:MFSK --功能:基于 VHDL 硬件描述语言,完成对基带信号的 MFSK 调制 --说明:这里 MFSK 的 M 为 4 --最后修改日期:2004.2.13 library ieee; use ieee.std_logic_aricess(clk,yy) --此进程完成对输入基带信号 x 的 MFSK 调制 begin if clk'event and clk='1' then if start='0' then y elsif yy=00 then y elsif yy=01 then y elsif yy=10 then y else y end if; end if; end process;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; enTIty MFSK is port(clk :in std_logic; --系统时钟 start :in std_logic; --开始调制信号 x :in std_logic; --基带信号 y :out std_logic); --调制信号 end MFSK; architecture behav of MFSK is

end behav; --对输入的基带信号 x 进行串/并转换,得到 2 位并行信号的 yy begin if clk'event and clk='1' then if start='0' then q elsif q=0 then q elsif q=8 then q else q end if; end if; end process;

基于MATLAB的PSK调制与解调的仿真

基于MATLAB的PSK调制与解调的仿真一、课题说明现代社会发展要求通信系统功能越来越强,性能越来越高,构成越来越复杂;另一方面,要求通信系统技术研究和产品开发缩短周期,降低成本,提高水平。

这样尖锐对立的两个方面的要求,只有通过使用强大的计算机辅助分析设计技术和工具才能实现。

通信系统仿真贯穿通信系统工程设计的全过程,对通信系统的发展起着举足轻重的作用。

本报告针对通信系统仿真的探讨主要做了以下的工作:(1)介绍了通信系统仿真的相关内容,包括通信系统仿真的一般步骤。

(2)对通信系统中的主要环节,如模拟信号的数字传输系统进行了详细的阐述。

(3)在理解通信系统理论的基础上,利用Simulink强大的仿真功能,对PSK通信系统进行了模型构建、系统设计、仿真演示、结果显示,并且给出了具体的分析。

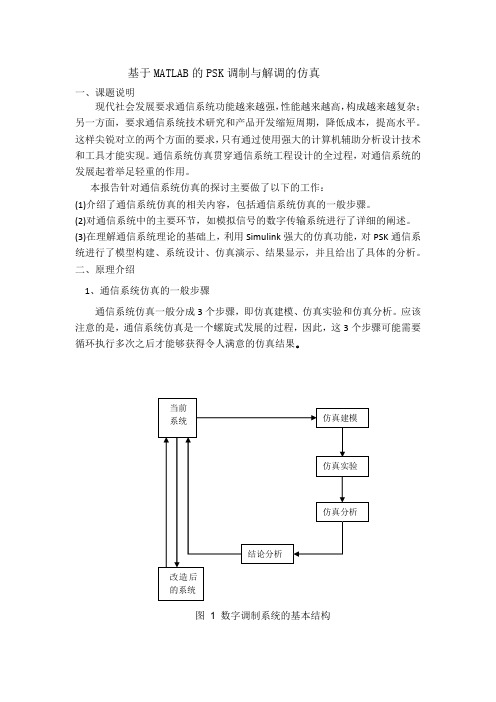

二、原理介绍1、通信系统仿真的一般步骤通信系统仿真一般分成3个步骤,即仿真建模、仿真实验和仿真分析。

应该注意的是,通信系统仿真是一个螺旋式发展的过程,因此,这3个步骤可能需要循环执行多次之后才能够获得令人满意的仿真结果。

图1 数字调制系统的基本结构2、数字频带传输系统在数字基带传输系统中,为了使数字基带信号能够在信道中传输,要求信道应具有低通形式的传输特性。

然而,在实际信道中,大多数信道具有带通传输特性,数字基带信号不能直接在这种带通传输特性的信道中传输。

必须用数字基带信号对载波进行调制,产生各种已调数字信号。

图2 数字调制系统的基本结构3、PSK调制系统3.1 2PSK数字调制原理在二进制数字调制中,当正弦载波的相位随二进制数字基带信号离散变化时,则产生二进制移相键控(2PSK)信号. 通常用已调信号载波的0°和180°分别表示二进制数字基带信号的 1 和0.3.2 2PSK原理图图32PSK信号的调制原理图图42PSK信号的解调原理图三、数字通信2PSK系统建模1、建模基本步骤通信系统仿真的基本步骤如下:(1)建立数学模型:根据通信系统的基本原理,确定总的系统功能,并将各部分功能模块化,找出各部分之间的关系。

PSK调制与解调系统的仿真

科类理工科编号(学号)本科生毕业论文(设计)PSK调制与解调系统的仿真The simulation of PSK modulation and demodulation system秦安东指导教师:赵红伟(讲师)云南农业大学昆明黑龙潭650201学院:基础与信息工程学院专业:电子信息工程年级:论文(设计)提交日期:答辩日期:答辩委员会主任:云南农业大学年月目录摘要 ................................................................................................................ 错误!未定义书签。

ABSTRACT.. (5)1.前言 (5)2.设计原理 (5)2.1 2PSK信号的调制与解调 (5)2.1.1 2PSK信号的调制原理 (5)2.1.2 2PSK信号的解调原理 (7)2.2 4PSK信号的调制与解调 (5)2.2.1 4PSK信号的调制原理 (5)2.2.2 4PSK信号的解调原理 (7)2.3 8PSK信号的调制与解调 (5)2.3.1 8PSK信号的调制原理 (5)2.3.2 8PSK信号的解调原理 (7)3仿真结果 (11)4.1 2PSK信号的仿真结果如下图所示......................................... 错误!未定义书签。

4.2 4PSK信号的仿真结果如下图所示 (7)4.3 8PSK信号的仿真结果如下图所示......................................... 错误!未定义书签。

5.心得体会 (12)参考文献 (13)致谢··················································································································错误!未定义书签。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8.14 MPSK调制与解调VHDL程序与仿真

2. MPSK调制程序及注释

--文件名:PL_MPSK

--功能:基于VHDL硬件描述语言,对基带信号进行MPSK调制(这里M=4)--说明:调制信号说明如表8.14.2所示。

表8.14.2 调制信号说明

--最后修改日期:2004.2.14

library ieee;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity PL_MPSK is

port(clk :in std_logic; --系统时钟

start :in std_logic; --开始调制信号

x :in std_logic; --基带信号

y :out std_logic); --调制信号

end PL_MPSK;

architecture behav of PL_MPSK is

signal q:integer range 0 to 7; --计数器

signal xx:std_logic_vector(1 downto 0); --中间寄存器

signal yy:std_logic_vector(1 downto 0); --2位并行码寄存器

signal f:std_logic_vector(3 downto 0); --载波f

begin

process(clk) --通过对clk分频,得到4种相位;并完成基带信号的串并转换begin

if clk'event and clk='1' then

if start='0' then q<=0;

elsif q=0 then q<=1;f(3)<='1'; f(1)<='0'; xx(1)<=x;yy<=xx;

elsif q=2 then q<=3;f(2)<='0'; f(0)<='1';

elsif q=4 then q<=5;f(3)<='0'; f(1)<='1'; xx(0)<=x;

elsif q=6 then q<=7;f(2)<='1'; f(0)<='0';

else q<=q+1;

end if;

end if;

end process;

y<=f(0) when yy="11" else

f(1) when yy="10" else

f(2) when yy="01" else

f(3); --根据yy寄存器数据,输出对应的载波end behav;

3. MPSK调制程序仿真及注释

MPSK调制程序仿真及注释如图8.14.6所示。

(a)MPSK调制VHDL程序仿真全图

(b)MPSK调制VHDL程序仿真局部放大图1

(c)MPSK调制VHDL程序仿真局部放大图2

图8.14.6 MPSK调制VHDL程序仿真及注释

2. MPSK解调VHDL程序及注释

--文件名:PL_MPSK2。

--功能:基于VHDL硬件描述语言,完成对MPSK调制信号的解调(这里M=4)。

--说明:解调信号说明如表8.14.3所示。

将一个信号周期分成4份,高电平权值分别为0、0、0、0,低电平权值分别为1、1、2、3。

表8.14.3 解调信号说明

--最后修改日期:2004.2.14。

library ieee;

use ieee.std_logic_arith.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity PL_MPSK2 is

port(clk :in std_logic; --系统时钟

start :in std_logic; --同步信号

x :in std_logic; --调制信号

y :out std_logic); --基带信号

end PL_MPSK2;

architecture behav of PL_MPSK2 is

signal q:integer range 0 to 7; --计数器

signal xx:std_logic_vector(2 downto 0); --加法器

signal yyy:std_logic_vector(1 downto 0); --2位并行基代信号寄存器

signal yy:std_logic_vector(2 downto 0); --寄存xx数据

begin

process(clk)

begin

if clk'event and clk='1' then

if start='0' then q<=0;

elsif q=0 then q<=1;yy<=xx; y<=yyy(0); --把加法计数器的数据送入yy寄存器if x='0' then xx<="001"; --调制信号x为低电平时,送入加法器的数据“001”

else xx<="000";

end if;

elsif q=2 then q<=3;

if x='0' then xx<=xx+"001"; --调制信号x为低电平时,送入加法器的数据“001”

end if;

elsif q=4 then q<=5; y<=yyy(1);

if x='0' then xx<=xx+"010"; --调制信号x为低电平时,送入加法器的数据“010”

end if;

elsif q=6 then q<=7;

if x='0' then xx<=xx+"011"; --调制信号x为低电平时,送入加法器的数据“011”

end if;

else q<=q+1;

end if;

end if;

end process;

process(yy) --此进程根据yy寄存器里的数据进行译码

begin

if clk='1' and clk'event then

if yy="101" then yyy<="00"; --yy寄存器“101”对应基带码“00”

elsif yy="011" then yyy<="01"; --yy寄存器“011”对应基带码“01”

elsif yy="010" then yyy<="10"; --yy寄存器“010”对应基带码“10”

elsif yy="100" then yyy<="11"; --yy寄存器“100”对应基带码“11”

else yyy<="00";

end if;

end if;

end process;

end behav;

3. MPSK解调程序仿真图及注释

MPSK解调程序仿真图及注释如图8.14.9所示。

(a)MPSK解调VHDL程序仿真全图

注:中间信号yy 与yyy的关系为:5对应“00”;3对应“01”;2对应“10”;4对应“11”。

(b)MPSK解调VHDL程序仿真局部放大图1

(c)MPSK解调VHDL程序仿真局部放大图2

图8.14.9 MPSK解调VHDL程序仿真图及注释。