触发器和时序逻辑电路习题答案

时序逻辑电路习题与答案

第12章时序逻辑电路自测题一、填空题1.时序逻辑电路按状态转换情况可分为时序电路和时序电路两大类。

2.按计数进制的不同,可将计数器分为、和N进制计数器等类型。

3.用来累计和寄存输入脉冲个数的电路称为。

4.时序逻辑电路在结构方面的特点是:由具有控制作用的电路和具记忆作用电路组成。

、5.、寄存器的作用是用于、、数码指令等信息。

6.按计数过程中数值的增减来分,可将计数器分为为、和三种。

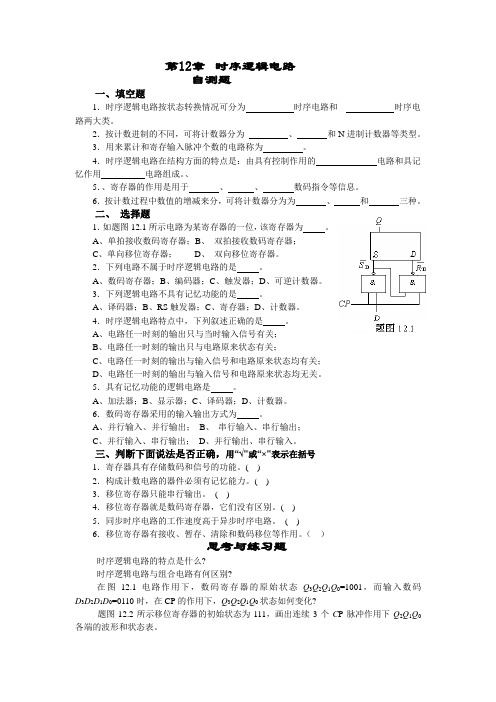

二、选择题1.如题图12.1所示电路为某寄存器的一位,该寄存器为。

A、单拍接收数码寄存器;B、双拍接收数码寄存器;C、单向移位寄存器;D、双向移位寄存器。

2.下列电路不属于时序逻辑电路的是。

A、数码寄存器;B、编码器;C、触发器;D、可逆计数器。

3.下列逻辑电路不具有记忆功能的是。

A、译码器;B、RS触发器;C、寄存器;D、计数器。

4.时序逻辑电路特点中,下列叙述正确的是。

A、电路任一时刻的输出只与当时输入信号有关;B、电路任一时刻的输出只与电路原来状态有关;C、电路任一时刻的输出与输入信号和电路原来状态均有关;D、电路任一时刻的输出与输入信号和电路原来状态均无关。

5.具有记忆功能的逻辑电路是。

A、加法器;B、显示器;C、译码器;D、计数器。

6.数码寄存器采用的输入输出方式为。

A、并行输入、并行输出;B、串行输入、串行输出;C、并行输入、串行输出;D、并行输出、串行输入。

三、判断下面说法是否正确,用“√"或“×"表示在括号1.寄存器具有存储数码和信号的功能。

( )2.构成计数电路的器件必须有记忆能力。

( )3.移位寄存器只能串行输出。

( )4.移位寄存器就是数码寄存器,它们没有区别。

( )5.同步时序电路的工作速度高于异步时序电路。

( )6.移位寄存器有接收、暂存、清除和数码移位等作用。

()思考与练习题时序逻辑电路的特点是什么?时序逻辑电路与组合电路有何区别?在图12.1电路作用下,数码寄存器的原始状态Q3Q2Q1Q0=1001,而输入数码D3D2D1D0=0110时,在CP的作用下,Q3Q2Q1Q0状态如何变化?题图12.2所示移位寄存器的初始状态为111,画出连续3个C P脉冲作用下Q2Q1Q0各端的波形和状态表。

哈工大数字电子技术基础习题册2010-答案6-7章

哈工大数字电子技术基础习题册2010-答案6-7章第6章触发器【6-1】已知由与非门构成的基本RS触发器的直接置“0”端和直接置“1”端的输入波形如图6.1所示,试画出触发器Q端和Q端的波形。

R d SdQQ图 6.1解:基本RS触发器Q端和Q端的波形可按真值表确定,要注意的是,当dR和d S同时为“0”时,Q端和Q端都等于“1”。

d R和d S同时撤消,即同时变为“1”时,Q端和Q端的状态不定。

见图6.1(b)所示,图中Q端和Q端的最右侧的虚线表示状态不定。

R dS dQQ不定状态图6.1(b)题6-1答案的波形图【6-2】触发器电路如图6.2(a)所示,在图(b)中画出电路的输出端波形,设触发器初态为“0”。

QdS dQQR(a) (b)图6.2解:此题是由或非门构成的RS 触发器,工作原理与由与非门构成的基本RS 触发器一样,只不过此电路对输入触发信号是高电平有效。

参照题6-1的求解方法,即可画出输出端的波形,见图6.2(c)。

d S dQR 不定状态图6.2(c)【6-3】试画出图6.3所示的电路,在给定输入时钟作用下的输出波形,设触发器的初态为“0”。

“CPYZCP图 6.3解:见图6.3(b)所示,此电路可获得双相时钟。

Q Q CP Y Z图6.3(b)【6-4】分析图6.4所示电路,列出真值表,写出特性方程,说明其逻辑功能。

Q图6.4解:1.真值表(CP =0时,保持;CP =1时,如下表)D n Q n Q n+1 0 0 0 0 1 0 1 0 1 1 1 12.特性方程Q n+1=D n3.该电路为锁存器(时钟型D 触发器)。

CP =0时,不接收D 的数据;CP =1时,把数据锁存,但该电路有空翻。

【6-5】试画出在图6.5所示输入波形的作用下,上升和下降边沿JK 触发器的输出波形。

设触发器的初态为“0”。

CP J K图 6.5解:见图6.5(b)所示。

CP J KJ K QQ图6.5(b)【6-6】试画出图P6.6(a)所示电路,在图6.6(b)给定输入下的Q 端波形,设触发器初态为“0”。

(完整版)触发器时序逻辑电路习题答案

第4章 触发器4.3 若在图4.5电路中的CP 、S 、R 输入端,加入如图4.27所示波形的信号,试画出其Q 和Q 端波形,设初态Q =0。

SRCP图4.27 题4.3图解:图4.5电路为同步RS 触发器,分析作图如下:S RQ4.5 设图4.28中各触发器的初始状态皆为Q =0,画出在CP 脉冲连续作用下个各触发器输出端的波形图。

Q 11CPQ 3CPCPQ 2Q 6Q 4Q 5CP图4.28 题4.5图解:Q Q nn 111=+ Q Q n n 212=+ Q Q nn 313=+Q Q n n 414=+ Q Q n n 515=+ Q Q nn 616=+Q 1CP Q 2Q 3Q 4Q 5Q64.6 试写出 图4.29(a)中各触发器的次态函数(即Q 1 n+1 、 Q 2 n+1与现态和输入变量之间的函数式),并画出在图4.29(b )给定信号的作用下Q 1 、Q 2的波形。

假定各触发器的初始状态均为Q =0。

1A BCP>1D C1=1A BQ 1Q 2Q 2(a)BA(b)图4.29题4.6图解:由图可见:Q B A AB Q n n 111)(++=+ B A Q n ⊕=+12B A Q 2Q 14.7 图4.30(a )、(b )分别示出了触发器和逻辑门构成的脉冲分频电路,CP 脉冲如图4.30(c )所示,设各触发器的初始状态均为0。

(1)试画出图(a )中的Q 1、Q 2和F 的波形。

(2)试画出图(b )中的Q 3、Q 4和Y 的波形。

Y(b )(c )CPQ 1Q 2(a )图4.30 题4.7图解: (a )Q Q nn 211=+ QQ nn 112=+ Q F 1CP ⊕= R 2 = Q 1 低电平有效CPQ 1Q 2F(b )Q Q Q n n n 4313=+ Q Q Q n n n 4314=+ Q Q Y nn43=CP 3= CP 上降沿触发 CP 4= CP 下降沿触发CPQ 3Q 4Y4.8 电路如图4.31所示,设各触发器的初始状态均为0。

电工与电子技术习题参考答案第9章

第9章时序逻辑电路习题解答9.1 d R端和d S端的输入信号如题9.1图所示,设基本RS触发器的初始状态分别为1和0两种情况,试画出Q端的输出波形。

题9.1图解:9.2 同步RS触发器的CP、R、S端的状态波形如题9.2图所示。

设初始状态为0和1两种情况,试画出Q端的状态波形。

题9.2图解:9.3 设主从型JK触发器的初始状态为0,J、K、CP端的输入波形如题9.3图所示。

试画出Q端的输出波形(下降沿触发翻转)。

解:如题9.3图所示红色为其输出波形。

第9章时序逻辑电路225题9.3图9.4 设主从型JK触发器的初始状态为0,J、K、CP端输入波形如题9.4图所示。

试画出Q端的输出波形(下降沿触发翻转)。

如初始状态为1态,Q端的波形又如何?解:如题9.4图所示红色为其输出波形。

题9.4图9.5 设维持阻塞型D触发器的初始状态为0,D端和CP端的输入波形如题9.5图所示,试画出Q端的输出波形(上升沿触发翻转)。

如初始状态为1态,Q端的波形又如何?解:如题9.5图所示红色为其输出波形。

第9章时序逻辑电路226题9.5图9.6 根据CP时钟脉冲,画出题9.6图所示各触发器Q端的波形。

(1)设初始状态为0;(2)设初始状态为1。

(各输入端悬空时相当于“1”)题9.6图解:第9章时序逻辑电路2279.7 题9.7图所示的逻辑电路中,有J和K两个输入端,试分析其逻辑功能,并说明它是何种触发器。

题9.7图=⋅⋅⋅=⋅+⋅解:由图得D Q F J Q Q F J QJ K Q n D Q n+10 0 0 0 00 0 1 1 10 1 0 0 00 1 1 0 01 0 0 1 11 0 1 1 11 1 0 1 11 1 1 0 0此电路为D触发器和与非门组成的上升沿触发的JK触发器。

9.8 根据题9.8图所示的逻辑图和相应的CP、d R、D的波形,试画出Q1和Q2端的输出波形。

设初始状态Q1=Q2=0。

题9.8图解:第9章时序逻辑电路2289.9 试用4个D触发器组成一个四位右移移位寄存器。

第14章触发器和时序逻辑电路-习题

第14章 触发器和时序逻辑电路A 选择题14.1.1 触发器如图14.01所示,设初始状态为0,则输出Q的波形为图14.02中的( )。

图14.01 习题14.1.1的图 图14.02 习题14.1.1的图14.1.2 触发器如图14.03所示,设初始状态为0,则输出Q的波形为图14.04中的( )。

图14.03 习题14.1.2的图 图14.04 习题14.1.2的图14.1.3 图14.05所示的触发器具有( )功能。

(1)保持 (2)计数 (3)置1图14.05 习题14.1.3的图14.1.4 在图14.06所示的电路中,触发器的原状态Q1Q0=01,则在下一个CP作用下,Q1Q0为( )。

(1)00 (2)01 (3)10图14.06 习题14.1.4的图 图14.07 习题14.1.5的图14.1.5在图14.07所示的电路中,触发器的原状态Q1Q0=00,则在下一个CP作用下,Q1Q0为( )。

(1)00 (2)01 (3)1014.3.1 图14.08所示的是( )计数器。

(1)七进制 (2)八进制 (3)九进制图14.08 习题14.3.1的图14.4.1 由555定时器组成的单稳态触发器如图14.4.2(a)所示,若加大电容C的电容值,则( )。

(1)增大输出脉冲u0的幅度(2)增大输出脉冲u0的宽度(3)对输出脉冲u0无影响14.4.2 由555定时器组成的多谐振荡器如图14.4.3(a)所示,欲使振荡频率增高,则可( )。

(1)减小C (2)增大R1,R2 (3)增大U CCB基本题14.1.6 当基本RS触发器D R和D S端加上图14.09所示的波形时,试画出Q端的输出波形。

设初始状态为0和1两种情况。

14.1.7 当可控RS触发器CP,S和R端加上图14.10所示的波形时,使画出Q端的输出波形。

设初始状态为0和1两种情况。

图14.09 习题14.1.6的图 图14.10 习题14.1.7的图14.1.8 当主从型JK触发器的CP,J、K端分别加上图14.11所示的波形时,试画出Q端的输出波形。

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

电子技术习题解答第章触发器和时序逻辑电路及其应用习题解答

第8章 触发器和时序逻辑电路及其应用习题解答8.1 已知基本RS 触发器的两输入端D S 和D R 的波形如图8-33所示,试画出当基本RS 触发器初始状态分别为0和1两种情况下,输出端Q的波形图。

图8-33 习题8.1图解:根据基本RS 触发器的真值表可得:初始状态为0和1两种情况下,Q的输出波形分别如下图所示:习题8.1输出端Q的波形图8.2 已知同步RS 触发器的初态为0,当S 、R 和CP 的波形如图8-34所示时,试画出输出端Q的波形图。

图8-34 题8.2图解:根据同步RS 触发器的真值表可得:初始状态为0时,Q的输出波形分别如下图所示:习题8.2输出端Q的波形图8.3 已知主从JK触发器的输入端CP、J和K的波形如图8-35所示,试画出触发器初始状态分别为0时,输出端Q的波形图。

图8-35 习题8.3图解:根据主从JK触发器的真值表可得:初始状态为0情况下,Q的输出波形分别如下图所示:习题8.3输出端Q的波形图8.4 已知各触发器和它的输入脉冲CP的波形如图8-36所示,当各触发器初始状态均为1时,试画出各触发器输出Q端和Q端的波形。

图8-36 习题8.4图解:根据逻辑图及触发器的真值表或特性方程,且将驱动方程代入特性方程可得状态方程。

即:(a )J =K =1;Qn +1=n Q,上升沿触发 (b)J =K =1;Qn +1=n Q, 下降沿触发 (c)K =0,J =1;Qn +1=J n Q+K Qn =1,上升沿触发 (d)K =1,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0·Qn =n Q,上升沿触发 (e)K =Qn ,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0=n Q,上升沿触发 (f)K =Qn ,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0=n Q,下降沿触发, 再根据边沿触发器的触发翻转时刻,可得当初始状态为1时,各个电路输出端Q的波形分别如图(a )、(b )、(c )、(d )、(e )和(f )所示,其中具有计数功能的是:(a )、(b )、(d )、(e )和(f )。

第9章时序逻辑电路习题解答

第九章习题参考答案9-1对应于图9-la 逻辑图,若输入波形如图9-54所示,试分别画出原态为0和原 态为1对应时刻得Q 和◎波形。

3D 八图9-54逆9-1图解得到的波形如题9-1解图所示。

9-2逻辑图如图9-55所示,试分析它们的逻辑功能,分别画出逻辑符号,列出逻辑 真值表,说明它们是什么类型的触发器。

解 对于(a ):由图可写出该触发器的输出与输入的逻辑关系式为:(9-1)原态为•丿京态为a) b)图9-55题9-2图下面按输入的不同组合,分析该触发器的逻辑功能。

(1) R n =1、S D =0若触发器原状态为0,由式(9-1)可得Q=0、Q =1 ;若触发器原状态为1,由式(9-1) 同样可得Q =0、Q = 1。

即不论触发器原状态如何,只要R D =1、S° =0,触发器将置成0态。

(2) R D=0、S°=l用同样分析可得知,无论触发器原状态是什么 > 新状态总为:Q =1・Q=0,即触发器被置成1态。

(3) R[)=Sj)=0按类似分析可知,触发器将保持原状态不变。

⑷= s° = 1两个“与非”门的输出端Q和Q全为0,这破坏了触发器的逻辑关系,在两个输入信号同时消失后,由于“或非”门延迟时间不可能完全相等,故不能确定触发器处于何种状态。

因此这种情况是不允许出现的。

逻辑真值表如表9-1所示,这是一类用或非门实现的基本RS触发器,逻辑符号如題9-2(a) 的逻辑符号所示。

对于(b):此图与(a)图相比,只是多加了一个时钟脉冲信号,所以该逻辑电路在CP =1时的功能与(a)相同,真值表与表9-1相同;而在CP=0时相当于(a)中(3)的情况,触发器保持原状态不变。

逻辑符号见趣9-2 (b)逻辑符号。

这是一类同步RS触发器。

Q1000]表9」題9・2 (a)真值表00不变1 1 不定题9・2 (a)的逻辑符号9-3同步RS 触发器的原状态为1,R 、S 和CP 端的输入波形如图9-56所示,试画出 对应的Q 和。

时序逻辑电路习题解答

5-1 分析图所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

CLKZ图 题 5-1图解:从给定的电路图写出驱动方程为:00121021()n n nn n D Q Q Q D Q D Q ⎧=⎪⎪=⎨⎪=⎪⎩将驱动方程代入D 触发器的特征方程D Qn =+1,得到状态方程为:10012110121()n n n n n n n n Q Q Q Q Q Q Q Q +++⎧=⎪⎪=⎨⎪=⎪⎩由电路图可知,输出方程为2nZ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-1(a )所示,时序图如图题解5-1(b )所示。

题解5-1(a )状态转换图1Q 2/Q ZQ题解5-1(b )时序图综上分析可知,该电路是一个四进制计数器。

5-2 分析图所示电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入变量。

YA图 题 5-2图解:首先从电路图写出驱动方程为:()0110101()n n n n nD AQ D A Q Q A Q Q ⎧=⎪⎨==+⎪⎩将上式代入触发器的特征方程后得到状态方程()101110101()n n n n n n nQ AQ Q A Q Q A Q Q ++⎧=⎪⎨==+⎪⎩电路的输出方程为:01n nY AQ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-2所示YA题解5-2 状态转换图综上分析可知该电路的逻辑功能为:当输入为0时,无论电路初态为何,次态均为状态“00”,即均复位;当输入为1时,无论电路初态为何,在若干CLK 的作用下,电路最终回到状态“10”。

5-3 已知同步时序电路如图(a)所示,其输入波形如图 (b)所示。

试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图,并说明该电路的功能。

X(a) 电路图1234CLK5678X(b)输入波形 图 题 5-3图解:电路的驱动方程、状态方程和输出方程分别为:00101100011011011, ,n n n n n n n n n nJ X K X J XQ K XQ X Q XQ XQ XQ Q XQ XQ XQ Y XQ ++⎧==⎪⎨==⎪⎩⎧=+=⎪⎨⎪=+=+⎩= 根据状态方程和输出方程,可分别做出1110,n n Q Q ++和Y 的卡诺图,如表5-1所示。

21章 题库——时序逻辑电路+答案

第21章 触发器和时序逻辑电路一、填空题1、JK 触发器的特性方程为:=+1n Q ________________________。

2、时钟触发器按照结构和触发方式不同可分为:_________、__________、_________和主从式触发器四种。

3、T 触发器的特性方程为=+1n Q _________________。

4、4个触发器组成的寄存器可以存储__________位二进制数。

5、将JK 触发器的J 端连在Q 端上,K 端接高电平。

假设)(t Q =0,则经过50个CP 脉冲作用后,它的状态)50(+t Q =_____。

6、对于时钟RS 触发器,若要求其输出“0”状态保持不变,则输入的RS 信号应为________。

7、组成计数器的各个触发器的状态能在时钟信号到达时同时翻转,它属于__________ 计数器。

(填“同步”或“异步”)8、当JK 触发器的输入J=1,K=0时,触发器的次态Q n+1=____________。

9、若要构成十二进制计数器,最少要用__________个触发器。

10、构成一个模6的同步计数器最少要________个触发器。

11、一个 JK 触发器有____个稳态,它可存储____位二进制数。

二、选择题1、下列触发器中有空翻现象的是_________。

A 、同步式触发器B 、维持阻塞式触发器C 、主从式触发器D 、边沿式触发器 2、在以下各种电路中,属于时序电路的有__________。

A 、译码器B 、计数器C 、数据选择器D 、编码器 3、JK 触发器当J=K=1时,Q n+1=__________。

A 、0B 、1C 、Q nD 、 Q n4、下列触发器中逻辑功能最多是_______。

A 、J-K 触发器B 、D 触发器C 、T 触发器D 、T ′触发器 5、在CP 有效的情况下,当输入端D=0时,则D 触发器的输出端=+1n Q ________。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第21章 触发器和时序逻辑电路

191、触发器按其工作状态是否稳定可分为( b )。

(a)RS 触发器,JK 触发器,D 触发器,T 触发器;

(b)双稳态触发器,单稳态触发器,无稳态触发器;

(c)主从型触发器,维持阻塞型触发器。

192、逻辑电路如图所示,当A=“1”时,基本RS 触发器( c )。

(a)置“1”; (b)置“0”; (c)保持原状态。

≥1A ""1R D Q Q

S D

193、 逻辑电路如图所示,分析C ,S ,R 的波形,当初始状态为“0”时,输出Q 是“0”的瞬间为( c )。

(a)1t ; (b)2t ; (c)3t 。

C S R

t 1t 2t 3S

C

R D R

S D

Q Q

194、 某主从型JK 触发器,当J=K=“1”时,C 端的频率f=200Hz ,则Q 的频率为( c )。

(a)200Hz ; (b)400Hz ; (c)100Hz 。

195、逻辑电路如图所示,当A=“1”时,C 脉冲来到后JK 触发器( a )。

(a)具有计数功能; (b)置“0”; (c)置“1”。

≥1

A J

C

R D K

S D Q Q ""

1""1

196、 逻辑电路如图所示,A=“0”时,C 脉冲来到后D 触发器( b )。

(a)具有计数器功能; (b)置“0”; (c)置“1”。

D

C Q Q

&

A 197、逻辑电路如图所示,分析C 的波形,当初始状态为“0”时,输出Q

是“0”的瞬间为( a )。

(a) 1t ; (b)2t ; (c)3t 。

D

C Q Q C t 1t 2t 3

198、逻辑电路如图所示,它具有( a )。

(a)D 触发器功能; (b)T 触发器功能; (c)T'触发器功能。

J C

R D K

S D

Q

Q 1

199、逻辑电路如图所示,它具有( b )。

(a)D 触发器功能; (b)T 触发器功能; (c)T'触发器功能。

J C

R D K

S D

Q

Q

200、时序逻辑电路与组合逻辑电路的主要区别是( c )。

(a)时序电路只能计数,而组合电路只能寄存;

(b)时序电路没有记忆功能,组合电路则有;

(c)时序电路具有记忆功能,组合电路则没有。

201、寄存器与计数器的主要区别是( b )。

(a)寄存器具有记忆功能,而计数器没有;

(b)寄存器只能存数,不能计数,计数器不仅能连续计数,也能存数;

(c)寄存器只能存数,计数器只能计数,不能存数。

202、移位寄存器与数码寄存器的区别是( a )。

(a)前者具有移位功能,后者则没有;

(b)前者不具有移位功能,后者则有;

(c)两者都具有移位功能和计数功能。

203、某时序逻辑电路的波形如图所示,由此判定该电路是(c)。

(a)二进制计数器;(b)十进制计数器;(c)移位寄存器。

C

Q

1

Q

2

Q

3

Q

4

204、分析某时序逻辑电路的状态表,判定它是(a)。

(c)十进制计数器。

C Q2Q1Q0

0 0 0 0

0 1

1

2 0 1 1

3 1 1 1

4 1 1 0

5 1 0 0

6 0 0 0

(a )。

(a)n;(b)n+1;(c)n-1。

206、某计数器最大输入脉冲数为15,组成该计数器所需最少的触发器个数为(c)。

(a)2;(b)3;(c)4。

207、同步计数器和异步计数器的不同点是(a)。

(a)前者各触发器是同步进位的,后者则不同步;

(b)前者由JK端接受计数信号,后者则由时钟脉冲端接受计数信号;

(c)前者计数慢,后者计数快。

208、计数器是一种(b)。

(a)组合逻辑电路;(b)时序逻辑电路;(c)脉冲整形电路。

209、一位十进制计数器由(c)位二进制计数器组成。

(a)2;(b)3;(c)4。