详细设计方案_DDS

DDS信号发生器的设计

第9卷第1期2010年2月 无锡职业技术学院学报JOU RNAL O F W U X I I NS TITU TE O F TECHNOLO G Y V ol 19N o 11Feb 12010DDS 信号发生器的设计陈 慧1,2,云乃彰1(1.南京航空航天大学,江苏 南京 210016;2.无锡职业技术学院电子信息技术学院,江苏 无锡 214121)收稿日期:2009-12-13作者简介:陈 慧(1980— ),女,江苏丹阳人,硕士研究生,无锡职业技术学院讲师。

摘 要:利用现场可编程逻辑门阵列(FPGA )实现直接数字频率合成(DDS )原理以及以DD S 为核心的信号发生器的设计,并给出了以单片机80C 51为内核的FPGA 的设计方案及信号发生器产生的仿真波形。

关键词:直接数字频率合成技术(DD S );现场可编程逻辑门阵列(FPGA )中图分类号:TN 911 文献标识码:A 文章编号:1671-7880(2010)01-0028-04D e s i gn o f DD S S i gna l Gene ra t o rCH EN H u i 1,2,Y UN N a i 2zhang1(1.N anjing U niversity of A eronautics and A stronautics,N anjing 210016,C hina;2.E lectrical Info r m ation Institute,W uxi Institute of Technology,W uxi 214121,C hina )Abstract:The use of field p rogramm able gate arrays fo r direct digital frequency syn thesis p rinci p le andw ith DD S as the core of the signal generator .D esign on 80C 51single 2chi p m icrocom pu ter as the co re of the FPGA and p resent the si m ulation w ave for m from the signal generator .Key words:direct d igital frequency synthesis;field p rog ramm able gate array 作为电子系统必不可少的信号源,在很大程度上决定了系统的性能,因而常称之为电子系统的“心脏”。

dds方案

DDS方案概述DDS(Data Distribution Service)是一种实时数据分发中间件标准,旨在提供高性能、可靠的数据交换服务。

它广泛应用于工业自动化、网络通信、航空航天等领域,可满足高并发、低延迟、可扩展等需求。

本文将介绍DDS方案的基本原理、主要特点以及适用场景,并提供一些实际案例以供参考。

基本原理DDS方案的基本原理是发布-订阅模式,即数据的发布者(Publisher)将数据发布到特定的主题(Topic)上,而订阅者(Subscriber)则通过订阅相应的主题来接收数据。

DDS采用了一种分布式的架构,其中包含了各种组件,如发布者、订阅者、中间代理(Middleware)等。

发布者和订阅者通过中间代理来交换数据,中间代理负责数据的可靠分发、数据的过滤和转换等功能。

主要特点高性能DDS方案的核心目标之一是提供高性能的数据交换服务。

为此,DDS采用了一系列优化措施,如数据压缩、批处理、异步传输等。

这些措施可以显著提升数据传输的效率,降低系统的延迟。

此外,DDS还支持多种传输协议,如TCP/IP、UDP等,并可以根据实际需求选择最适合的协议进行数据传输。

可靠性DDS方案通过使用可靠的传输协议和机制来保证数据的可靠性。

它提供了丰富的错误处理机制,可以在数据传输过程中及时检测和处理错误,从而确保数据的完整性和可用性。

DDS还支持数据的持久化存储,可以将数据保存到本地磁盘或数据库中,以便在需要时进行回放和分析。

可扩展性DDS方案具有良好的可扩展性,可以根据实际需求灵活地扩展系统的规模和性能。

它支持集群部署,可以通过增加节点来提升系统的并发能力和容错性。

此外,DDS还提供了灵活的数据模型和接口,可以根据业务需求定制数据的格式和结构。

实时性DDS方案的设计目标之一是提供实时的数据交换服务。

它通过优化数据传输和处理的机制,可以在毫秒级别的延迟下实现数据的实时传输和响应。

DDS还支持数据的优先级处理,可以根据需求对数据进行优先级排序和处理,确保关键数据的实时性和可靠性。

dds课程设计

dds课程设计一、教学目标本课程的教学目标是使学生掌握XX学科的基本概念、原理和方法,能够运用所学知识解决实际问题;提高学生的科学思维能力和创新能力;培养学生对XX学科的兴趣和热情,树立正确的科学态度和价值观。

具体来说,知识目标包括:1.掌握XX学科的基本概念、原理和方法;2.了解XX学科的发展趋势和应用领域;3.学会使用XX学科的相关工具和仪器。

技能目标包括:1.能够运用所学知识解决实际问题;2.具备科学实验的基本技能,能够进行实验操作和数据分析;3.能够运用科学思维方法进行创新性研究。

情感态度价值观目标包括:1.培养学生对XX学科的兴趣和热情;2.树立正确的科学态度,注重科学方法和实证精神;3.培养学生的团队协作能力和交流表达能力。

二、教学内容本课程的教学内容主要包括XX学科的基本概念、原理和方法,以及实际应用案例。

具体安排如下:1.第一章:XX学科的基本概念和原理2.第二章:XX学科的方法和技术3.第三章:XX学科的应用案例每章内容包括若干个小节,每个小节结束后安排一次课堂讨论或实验操作,以便巩固所学知识。

三、教学方法为了提高教学效果,我们将采用多种教学方法,包括:1.讲授法:用于传授基本概念、原理和方法;2.讨论法:通过小组讨论,培养学生的思考能力和团队协作精神;3.案例分析法:通过分析实际案例,使学生了解XX学科在现实生活中的应用;4.实验法:安排实验课程,培养学生的实验技能和科学思维方法。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:选用国内权威出版的XX学科教材;2.参考书:推荐学生阅读相关领域的经典著作和最新研究论文;3.多媒体资料:制作课件、教学视频等,以丰富教学手段;4.实验设备:配备必要的实验仪器和设备,保障实验教学的顺利进行。

五、教学评估本课程的评估方式包括平时表现、作业、考试等,以全面客观地反映学生的学习成果。

1.平时表现:通过课堂参与、提问、讨论等环节,评估学生的学习态度和思考能力;2.作业:布置适量作业,评估学生对所学知识的掌握和应用能力;3.考试:安排期中考试和期末考试,评估学生的综合运用能力和知识水平。

dds设计标准

dds设计标准

DDS(分布式数据系统)设计标准主要包括以下几个方面:

数据模型设计:根据业务需求,设计系统的数据模型。

这包括定义实体类型、属性、关系以及数据规范等。

确保数据模型能够满足业务需求,并且具有良好的扩展性和可维护性。

分布式架构设计:根据系统的规模和性能要求,设计合理的分布式架构。

这包括节点间的通信机制、数据同步机制、负载均衡以及容错处理等。

确保系统具有高性能、高可用性和可扩展性。

数据存储设计:根据数据模型的特性,选择合适的存储方式。

这包括关系型数据库、NoSQL数据库、分布式文件系统等。

确保存储方式能够满足数据存储的需求,并且具有良好的读写性能和数据一致性。

数据访问设计:根据业务需求,设计数据的访问方式。

这包括定义API接口、查询语句以及数据流等。

确保数据能够被正确地访问和操作,并且具有良好的安全性和可维护性。

数据安全设计:根据业务需求和安全要求,设计数据的安全机制。

这包括用户认证、权限控制、加密传输和存储等。

确保数据的安全性和隐私保护。

测试和部署:进行充分的测试和部署,确保系统稳定运行,满足业务需求和性能要求。

综上所述,DDS设计标准是一个综合性的标准,涉及到多个方面。

在实际应用中,需要根据具体业务需求和技术环境进行设计和实现。

dds信号源课程设计

dds信号源课程设计一、课程目标知识目标:1. 学生能理解DDS(直接数字频率合成器)信号源的基本原理,掌握其工作流程。

2. 学生能掌握DDS信号源的关键参数,如频率、相位、幅度等,并了解它们之间的关系。

3. 学生能解释DDS信号源在电子技术中的应用,如信号发生、通信系统等。

技能目标:1. 学生能够操作DDS信号源硬件,进行基本的信号生成与调制。

2. 学生能够利用相关软件对DDS信号源进行编程控制,实现特定信号的输出。

3. 学生能够通过实验,分析DDS信号源的性能,提出优化方案。

情感态度价值观目标:1. 学生对电子技术产生兴趣,培养探索精神和创新意识。

2. 学生在实验和讨论过程中,培养团队合作精神和沟通能力。

3. 学生认识到DDS信号源在科技发展中的重要作用,增强社会责任感和使命感。

课程性质:本课程为电子技术实践课程,结合理论讲解和实验操作,提高学生对DDS信号源的理解和应用。

学生特点:学生为高中年级,具备一定的电子技术基础,对实验操作感兴趣,但需引导深入理解理论知识。

教学要求:注重理论与实践相结合,鼓励学生动手实践,培养解决实际问题的能力。

在教学过程中,关注学生个体差异,提供针对性的指导。

通过课程学习,使学生能够将所学知识应用于实际电子技术领域。

二、教学内容1. DDS信号源原理介绍:- 数字频率合成技术背景- DDS信号源基本工作原理- 频率、相位、幅度控制原理2. DDS信号源硬件结构:- 主要组成部分及其功能- 常见DDS芯片介绍- 硬件连接与操作方法3. DDS信号源编程控制:- 编程接口与协议- 常用编程语言及工具- 实例演示:信号生成与调制4. DDS信号源应用案例分析:- 信号发生器- 通信系统- 频率合成器5. 实验教学:- 实验一:DDS信号源基本操作- 实验二:信号生成与调制- 实验三:性能分析与优化6. 教学进度安排:- 第一周:原理介绍与硬件结构学习- 第二周:编程控制与实例演示- 第三周:应用案例分析- 第四周:实验教学与实践教学内容关联教材章节:- 第一章:电子技术基础- 第二章:数字频率合成技术- 第三章:DDS信号源硬件与编程- 第四章:实验与实践三、教学方法本课程采用以下多样化的教学方法,以激发学生的学习兴趣和主动性,提高教学效果:1. 讲授法:- 对于DDS信号源的基本原理、硬件结构、编程控制等理论知识,采用讲授法进行系统讲解,使学生掌握必要的基础知识。

DDS信号发生器设计

目录绪论 (1)1 系统设计 (2)1.1方案论证 (2)1.1.1 信号模块 (2)1.1.2 控制模块 (3)1.1.3 显示模块 (4)1.1.4 键盘输入模块 (4)1.1.5 系统各模块的最终方案 (4)1.2理论分析与计算 (5)1.2.1 频率精度计算 (5)1.2.2 DDS的理论分析 (5)1.2.3 DDS的参数计算 (6)2 硬件系统设计 (7)2.1硬件元器件的选用 (7)2.1.1 C8051F020控制芯片简介 (7)2.1.2 AD9954简介 (9)2.2单元硬件电路设计 (13)2.2.1 矩阵(4×4)键盘电路 (13)2.2.2 电源电路 (14)2.2.3 电压调幅电路 (14)2.2.4 方波电路 (14)2.2.5 三角波电路 (15)3 软件系统设计 (16)3.1程序流程图 (16)4 系统测试 (19)4.1仿真测试 (19)4.2指标测试 (19)4.3测试方法 (20)5 结束语 (22)致谢 (23)参考文献 (24)附录一对AD9954编程的主要源程序清单 (25)附录二LCD显示子程序 (35)摘要:随着数字集成电路、微电子技术和EDA技术的深入研究,DDS技术以其有别于其它频率合成技术的优越性能和特点,成为现代频率合成技术中的佼佼者。

根据题目要求,我们以单片机C8051F020芯片和AD9954芯片为核心,辅以必要的模拟电路,设计一台信号发生器,使之能产生正弦波、方波和三角波。

该系统主要由控制模块、信号模块、显示模块、键盘输入模块构成。

仅用单片AD9954就实现了直接数字频率合成技术(DDS),产生稳幅正弦波。

输出的正弦波经过比较电路来实现方波的输出,而三角波则是在方波的基础上通过接入积分电路来实现的。

单片机对内部寄存器控制,AD9954就可以产生一个频谱纯净、频率和相位都可编程控制且稳定性很好的模拟波形,整个系统结构紧凑,电路简单,功能强大,可扩展性强。

基于VHDL的DDS设计

信息与通信工程学院VHDL课程设计2013年5月基于VHDL语言的DDS的设计1.设计内容DDS即直接数字频率合成,是近年来发展起来的一种新的频率合成技术,其主要优点是相对带宽很大,频率转换时间极短(可小于20 ns),频率分辨率很高,全数字化结构便于集成,输出相位连续可调,且频率、相位和幅度均可实现程控。

DDS 能够与计算机技术紧密结合在一起,克服了模拟频率合成和锁相频率合成等传统频率合成技术电路复杂、设备体积较大、成本较高的不足,因此它是一种很有发展前途的频率合成技术。

DDS 技术现已在接收机本振、信号发生器、通信系统、雷达系统等方面得到广泛应用。

数字频率合成器作为一种信号产生装置己经越来越受到人们的重视,它可以根据用户的要求产生相应的波形,具有重复性好、实时性强等优点,己经逐步取代了传统的函数发生器。

我们组本次课程设计的目的是设计基于所学课程VHDL硬件描述语言开发出一个能产生正弦波、方波、三角波、锯齿波等波形的信号源。

2.实现方案2.1 DDS原理直接数字频率合成是采用数字化技术,通过控制相位的变化速度,直接产生各种不同频率、不同波形信号的一种频率合成方法。

DDS 的基本结构如图1 所示,它主要由相位累加器、正弦ROM 表、D/A 转换器和低通滤波器构成。

图1 DDS工作原理图DDS 工作时,在时钟脉冲fc的控制下对频率控制字K 用累加器进行处理以得到相应的相位码,然后由相位码寻址波形存储器进行相位码―幅度编码变换,再经过D/A 数模变换器得到相应的阶梯波,最后经过低通滤波器对阶梯波进行平滑处理即可得到由频率控制字K 决定的频率可调的输出波形。

参考频率源一般是高稳定的晶体振荡器,用于DDS 中各部件的同步工作,因此DDS 输出的合成信号频率稳定度与晶体振荡器是相同的。

在标准频率参考源的控制下,频率控制字K可决定相应的相位增量,相位累加器则以步长K进行线性累加,相位累加器积满时就会产生一次溢出,从而完成一个周期性动作,这个动作周期即是DDS合成信号的一个周期。

以FPGA为基础的DDS控制电路设计方案详解

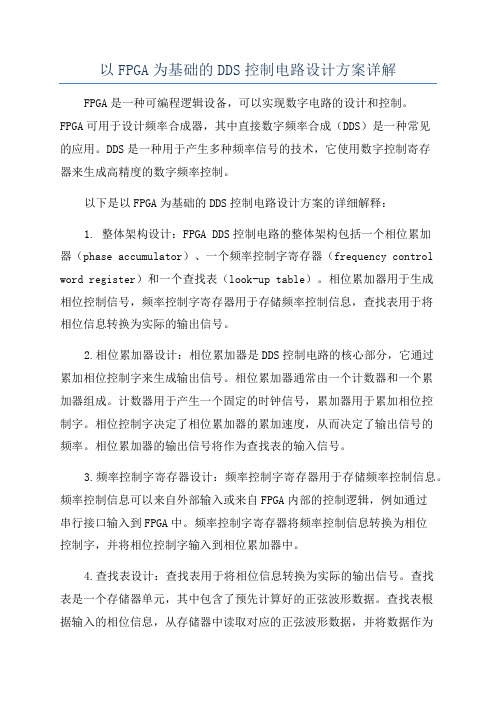

以FPGA为基础的DDS控制电路设计方案详解FPGA是一种可编程逻辑设备,可以实现数字电路的设计和控制。

FPGA可用于设计频率合成器,其中直接数字频率合成(DDS)是一种常见的应用。

DDS是一种用于产生多种频率信号的技术,它使用数字控制寄存器来生成高精度的数字频率控制。

以下是以FPGA为基础的DDS控制电路设计方案的详细解释:1. 整体架构设计:FPGA DDS控制电路的整体架构包括一个相位累加器(phase accumulator)、一个频率控制字寄存器(frequency control word register)和一个查找表(look-up table)。

相位累加器用于生成相位控制信号,频率控制字寄存器用于存储频率控制信息,查找表用于将相位信息转换为实际的输出信号。

2.相位累加器设计:相位累加器是DDS控制电路的核心部分,它通过累加相位控制字来生成输出信号。

相位累加器通常由一个计数器和一个累加器组成。

计数器用于产生一个固定的时钟信号,累加器用于累加相位控制字。

相位控制字决定了相位累加器的累加速度,从而决定了输出信号的频率。

相位累加器的输出信号将作为查找表的输入信号。

3.频率控制字寄存器设计:频率控制字寄存器用于存储频率控制信息。

频率控制信息可以来自外部输入或来自FPGA内部的控制逻辑,例如通过串行接口输入到FPGA中。

频率控制字寄存器将频率控制信息转换为相位控制字,并将相位控制字输入到相位累加器中。

4.查找表设计:查找表用于将相位信息转换为实际的输出信号。

查找表是一个存储器单元,其中包含了预先计算好的正弦波形数据。

查找表根据输入的相位信息,从存储器中读取对应的正弦波形数据,并将数据作为输出信号输出。

查找表的大小取决于输出信号的需求精度,较大的查找表会提供更高的输出精度。

5.时钟和状态控制:DDS控制电路通常需要一个高精度的时钟信号来驱动相位累加器和频率控制字寄存器。

时钟信号的频率和相位可以通过FPGA内部的时钟控制器进行调整。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DDS详细设计方案

1.DDS简介:

DDS同DSP(数字信号处理)一样,是一项关键的数字化技术。

DDS 是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

一块DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分(如Q2220)。

频率控制寄存器可以串行或并行的方式装载并寄存用户输入的频率控制码;而相位累加器根据频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对该相位值计算数字化正弦波幅度(芯片一般通过查表得到)。

DDS芯片输出的一般是数字化的正弦波,因此还需经过高速D/A转换器和低通滤波器才能得到一个可用的模拟频率信号。

2.DDS规格:

Xxx

3.实现原理

DDS的核心部分是相位累加器,相位累加器有一个累加器和相位寄存器组成,它的作用是再基准时钟源的作用下进行线性累加,当产生溢出时便完成一个周期,即DDS的一个频率周期。

其中频率字的位宽为K位,作为累加器的一个输入,累加器的另一个输入端位宽为N位(N>K),每来一个时钟,频率字与累加器的另一个输入相加的结果存入相位寄存器,再反馈给累加器,这相当于每来一个时钟,相位寄存器的输出就累加一次,累加的时间间隔为频率字的时间,输入加法器的位宽为(N-K)位,它与同样宽度的相位控制字相加形成新的相位,并以此作为查找表的地址。

每当累加器的值溢出一次,输入加法器的值就加一,相应的,作为查找表的地址就加一,而查找表的地址中保存波形的幅度值,这些离散的幅度值经DAC和PLF便课还原为模拟波形。

4.Verilog HDL源代码

Verilog HDL代码为:

module DDS (

//input

sys_clk,

sys_rst_n,

fword,

pword,

//output

da_clk,

da_data

);

//input ports

input sys_clk ; //system clock;

input sys_rst_n ; //system reset, low is active; input [WIDTH1-1:0] fword ; //输入频率字

input [WIDTH2-1:0] pword ; //输入相位字

//output ports

output [SIZE-1:0] da_data ; //DA 数据

output da_clk ; //DA 时钟

//reg define

reg [WIDTH1-1:0] fword_r ;

reg [WIDTH2-1:0] pword_r ;

reg [WIDTH1-1:0] freq_count ;

reg [WIDTH2-1:0] rom_addr ;

//wire define

//parameter define

parameter WIDTH1 = 32;

parameter WIDTH2 = 12;

parameter SIZE = 10;

/******************************************************************** ***********************************

** Main Program

**

********************************************************************* ***********************************/

assign da_clk = sys_clk ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0) begin

fword_r <= 32'h0000;

end

else

fword_r <= fword;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0) begin

pword_r <= 12'h0000;

end

else

pword_r <= pword;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0) begin

freq_count <= 32'h0000;

end

else

freq_count <= freq_count + fword_r; //频率控制器end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n ==1'b0) begin

rom_addr <= 32'h0000;

end

else

rom_addr <= freq_count[31:20] + pword_r; //相位控制器end

ROM DDS_ROM_U0 (

.address (rom_addr) ,

.clock (sys_clk) ,

.q (da_data)

);

endmodule

//end of RTL code

5.日积月累

Xxx

6.综合出的电路

DDS代码综合出的电路如下:

注意:波形文件存在Project\DDS\wave_file下面。

2009-10-25 (C) DongDong Stduio。