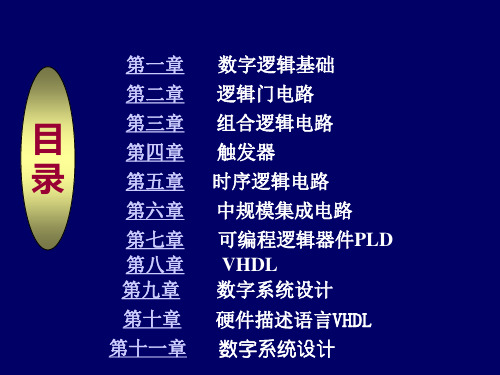

数字电子技术基础全套

合集下载

数字电子技术基础简明教程(第三版)全

三、二进制代码 编码: 用二进制数表示文字、符号等信息的过程。 二进制代码: 编码后的二进制数。

二-十进制代码:用二进制代码表示十个数字符号 0 ~ 9,又称为 BCD 码(Binary Coded Decimal )。 8421码 2421码 5211码

几种常见的BCD代码: 余 3 码 余 3 循环码

Y2 1 0 1 0 11 0 0

& ≥1

Y3

(真值表略)

(4) 异或运算 A

=1

(Exclusive—OR) B

Y4 = A ⊕ B = AB + AB

(5) 同或运算 (异或非)

(Exclusive—NOR)

Y5 = A ⊕ B A =1 B

= AB + AB A=

= A⊙B B

Y4

A B Y4 00 0

10 1 11 1

(3)非运算:

真

A

Y

值

0

1

表

1

0

逻辑函数式 Y = A + B 逻辑符号

A B

≥1 Y 或门(OR gate)

逻辑函数式 逻辑符号

Y= A

A1

Y 非门(NOT gate)

二、逻辑变量与逻辑函数及常用复合逻辑运算

1. 逻辑变量与逻辑函数 逻辑变量:在逻辑代数中,用英文字母表示的变量称

¾ 1.3.1 几种表示逻辑函数的方法 ¾ 1.3.2 几种表示方法之间的转换

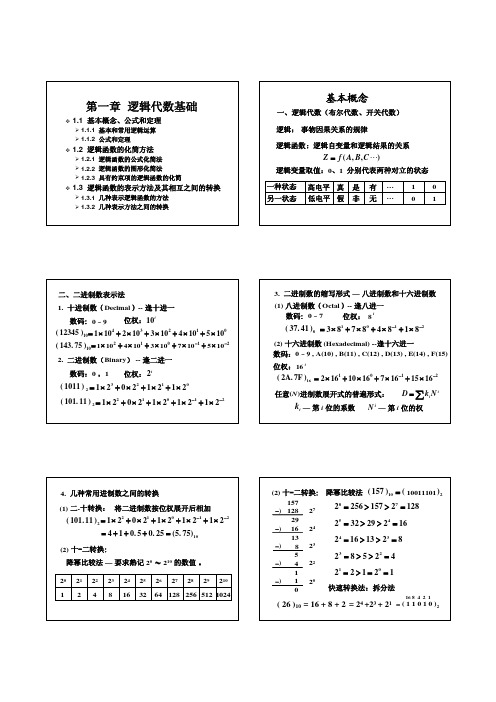

基本概念

一、逻辑代数(布尔代数、开关代数)

逻辑: 事物因果关系的规律

逻辑函数: 逻辑自变量和逻辑结果的关系 Z = f ( A, B, C L)

逻辑变量取值:0、1 分别代表两种对立的状态

数字电子技术基础全套ppt课件

输出方程

Y ( A Q ( 1 Q 2 ) ( A Q 1 Q 2 ) ) A Q 1 Q 2 A Q 1 Q 2

③计算、 列状态转

换表

Y 输A 入Q 1 Q 2 现A Q 态1 Q 2

A Q2 Q1

次

Q2*

态

Q1*

00 0

01

00 1

10

01 0

11

QQ102*1*AQ01 1 Q1

双向移位寄存器

2片74LS194A接成8位双向移位寄存器

用双向移位寄存器74LS194组成节日彩灯控制电路

1k

LED 发光 二极管

Q=0时 LED亮

+5V

RD Q0 DIR D0

Q1

Q2

Q3 S1

74LS194

S0

D1 D2 D3 DIL CLK +5V

RD Q0 DIR D0

Q1

Q2

Q3 S1

二.一般掌握的内容:

(1)同步、异步的概念,电路现态、次态、有效 状态、无效状态、有效循环、无效循环、自启动的 概念,寄存的概念;

(2)同步时序逻辑电路设计方法。

6.1 概述

一、组合电路与时序电路的区别

1. 组合电路: 电路的输出只与电路的输入有关, 与电路的前一时刻的状态无关。

2. 时序电路:

电路在某一给定时刻的输出

1 0 Q2

0 1

0 1

10 1

00

11 0

01

11 1

10

输出

Y

0 0 0 1 1 0 0 0

Q Q2*1*D D21A Q1 Q1 Q2

YA Q 1 Q 2A Q 1 Q 2

转换条件

Y ( A Q ( 1 Q 2 ) ( A Q 1 Q 2 ) ) A Q 1 Q 2 A Q 1 Q 2

③计算、 列状态转

换表

Y 输A 入Q 1 Q 2 现A Q 态1 Q 2

A Q2 Q1

次

Q2*

态

Q1*

00 0

01

00 1

10

01 0

11

QQ102*1*AQ01 1 Q1

双向移位寄存器

2片74LS194A接成8位双向移位寄存器

用双向移位寄存器74LS194组成节日彩灯控制电路

1k

LED 发光 二极管

Q=0时 LED亮

+5V

RD Q0 DIR D0

Q1

Q2

Q3 S1

74LS194

S0

D1 D2 D3 DIL CLK +5V

RD Q0 DIR D0

Q1

Q2

Q3 S1

二.一般掌握的内容:

(1)同步、异步的概念,电路现态、次态、有效 状态、无效状态、有效循环、无效循环、自启动的 概念,寄存的概念;

(2)同步时序逻辑电路设计方法。

6.1 概述

一、组合电路与时序电路的区别

1. 组合电路: 电路的输出只与电路的输入有关, 与电路的前一时刻的状态无关。

2. 时序电路:

电路在某一给定时刻的输出

1 0 Q2

0 1

0 1

10 1

00

11 0

01

11 1

10

输出

Y

0 0 0 1 1 0 0 0

Q Q2*1*D D21A Q1 Q1 Q2

YA Q 1 Q 2A Q 1 Q 2

转换条件

数字电子技术基础(侯建军)

§1-2 逻辑代数基础

逻辑变量及基本逻辑运算 逻辑函数及其表示方法

逻辑代数的运算公式和规则

逻辑变量及基本逻辑运算

一、逻辑变量

取值:逻辑 0 、逻辑 1 。逻辑 0 和逻辑 1 不代 表数值大小,仅表示相互矛盾、相互对立 的两种逻辑状态

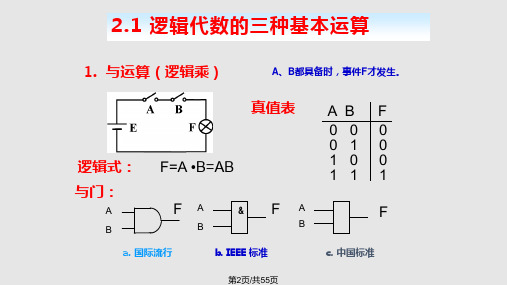

二、基本逻辑运算 与运算 或运算 非运算

返 回

与逻辑

只有决定某一事件的所有条件全部具备, 这一事件才能发生

乘基取整法 :小数乘以目标数制的基数( R=2 ),第 1一次相乘结果的整数部分为目的数的最高位 0 1 K0 0 -1,将其小 数部分再乘基数依次记下整数部分,反复进行下去, 直 K-1 K-2 K-3 K-4 K-5

由此得:(0.65)10=(0.10100)2 综合得:(81.65)10=(1010001.10100)2

逻辑表达式

―-‖非逻辑运算符

F= A

逻辑符号 1 A

F

三、复合逻辑运算 与非逻辑运算 或非逻辑运算 与或非逻辑运算

或逻辑真值表

A 0 0 1 1 B 0 1 0 1 F 0 1 1 1 逻辑符号 A 1 B

F

或逻辑运算符,也有 N个输入: 用“∨”、“∪”表 逻辑表达式 示 F= A + B+ ...+

F= A + B

N

返 回

非逻辑

当决定某一事件的条件满足时,事件不发 返 回 生;反之事件发生,

非逻辑真值表 A F 0 1 1 0

§1-1 数制与编码

进位计数制 数制转换

数值数据的表示

常用的编码

§1-2 逻辑代数基础

逻辑变量及基本逻辑运算 逻辑函数及其表示方法

逻辑代数的运算公式和规则

数字电子技术基础(侯建军)

按权展开式 位置计数法 1、十进制 (333.33)10 =3 102 + 3 101+ 3 100+ 3 10-1 +3 10-2

权 权 权 权 权

进位计数制

特点:1)基数10,逢十进一,即9+1=10

表示相对小数点 的位置 2)有0-9十个数字符号和小数点,数码K i从0-9

3)不同数位上的数具有不同的权值10i。 4)任意一个十进制数,都可按其权位数基 展成多项式的形式 (N)10=(Kn-1 K1 K0. K-1 K-m)10 =Kn-1 10n-1++K1101+K0100+K-1 10-1++K-m 10-m n 1 K 10 i i 返 回 i m

原码的性质:

返 回

一、真值与机器数

(数值的绝对值) 最高位: ―1‖表示“-‖

―0‖有两种表示形式 正数:尾数部分与真值形式相同 …0] = 000…0 而 [-00…0] = 111…1 [+00 反 反 负数:尾数为真值数值部分按位取反 数值范围: +(2n –1-1)≤[X]反≤-(2n-1-1) 如n = 反码[X]反: 符号位 + 尾数部分 2. 8,反码范围01111111~10000000,数值范围 为+127~-127 [X1]反 = 00000100 X1 = +4 符号位后的尾数是否为真值取决于符号位 [X2]反 = 11111011 X2 = -4

常用编码

常用的编码:

用一组二进制码按一定规则排列起 来以表示数字、符号等特定信息。

(一)自然二进制码及格雷码 按自然数顺序 排列的二进 常用四位自然二进制码,表示十进 制 码 制数0--15,各位的权值依次为23、 22、21、20。 格雷码 1.任意两组相邻码之间只有一位不同。 注:首尾两个数码即最小数0000和最大 数1000之间也符合此特点,故它可称为 循环码 2.编码还具有反射性,因此又可称其 为反射码。 返 回 自然二进制码

《数字电子技术基础》(第四版)

CPLD结构特点

CPLD(复杂可编程逻辑器件)是一种基于乘积项的可编程逻辑器件,具有简单的结构和较快 的处理速度。它采用与或阵列(AND-OR Array)来实现逻辑功能,适用于中小规模的数字 电路设计。

FPGA与CPLD比较

FPGA和CPLD在结构、性能和适用场景上有所不同。FPGA具有更高的逻辑密度和更灵活 的可编程性,适用于大规模的数字电路设计和复杂的算法实现;而CPLD则具有更简单的 结构和更快的处理速度,适用于中小规模的数字电路设计和控制应用。

容量和提高存取速度

应用实例

如计算机的内存条就是采用RAM 存储器进行扩展的;而一些嵌入 式系统中则采用ROM存储器来

存储固件和程序代码等

发展趋势

随着科技的不断发展,存储器的 容量不断增大,存取速度不断提 高,功耗不断降低,未来存储器 将更加智能化、高效化和绿色化

05 可编程逻辑器件与EDA技 术

PLD可编程逻辑器件概述

要点一

PLD定义与分类

可编程逻辑器件(PLD)是一种通用集 成电路,用户可以通过编程来配置其逻 辑功能。根据结构和功能的不同,PLD 可分为PAL、GAL、CPLD、FPGA等类 型。

要点二

PLD基本结构

PLD的基本结构包括可编程逻辑单元 、可编程互连资源和可编程I/O单元 等。其中,可编程逻辑单元是实现逻 辑功能的基本单元,可编程互连资源 用于实现逻辑单元之间的连接,可编 程I/O单元则负责与外部电路的连接 。

逻辑代数法

利用逻辑代数化简和变换电路 表达式

图形化简法

利用卡诺图化简电路

பைடு நூலகம்

状态转换表

列出电路的状态转换过程,便 于分析和理解电路功能

状态转换图

以图形方式表示电路的状态转 换过程,直观易懂

CPLD(复杂可编程逻辑器件)是一种基于乘积项的可编程逻辑器件,具有简单的结构和较快 的处理速度。它采用与或阵列(AND-OR Array)来实现逻辑功能,适用于中小规模的数字 电路设计。

FPGA与CPLD比较

FPGA和CPLD在结构、性能和适用场景上有所不同。FPGA具有更高的逻辑密度和更灵活 的可编程性,适用于大规模的数字电路设计和复杂的算法实现;而CPLD则具有更简单的 结构和更快的处理速度,适用于中小规模的数字电路设计和控制应用。

容量和提高存取速度

应用实例

如计算机的内存条就是采用RAM 存储器进行扩展的;而一些嵌入 式系统中则采用ROM存储器来

存储固件和程序代码等

发展趋势

随着科技的不断发展,存储器的 容量不断增大,存取速度不断提 高,功耗不断降低,未来存储器 将更加智能化、高效化和绿色化

05 可编程逻辑器件与EDA技 术

PLD可编程逻辑器件概述

要点一

PLD定义与分类

可编程逻辑器件(PLD)是一种通用集 成电路,用户可以通过编程来配置其逻 辑功能。根据结构和功能的不同,PLD 可分为PAL、GAL、CPLD、FPGA等类 型。

要点二

PLD基本结构

PLD的基本结构包括可编程逻辑单元 、可编程互连资源和可编程I/O单元 等。其中,可编程逻辑单元是实现逻 辑功能的基本单元,可编程互连资源 用于实现逻辑单元之间的连接,可编 程I/O单元则负责与外部电路的连接 。

逻辑代数法

利用逻辑代数化简和变换电路 表达式

图形化简法

利用卡诺图化简电路

பைடு நூலகம்

状态转换表

列出电路的状态转换过程,便 于分析和理解电路功能

状态转换图

以图形方式表示电路的状态转 换过程,直观易懂

数字电子技术基础教程

第6页/共55页

2.2 逻辑代数的基本定律和规则

反演律 吸收律

A B AB

A AB A

A B A B A (A B) A

A B A B A

(A B)(A B) A

A AB A B

A(A B) AB

冗余律

AB AC BC AB AC

(A+B)(A+C)(B C) (A+B)(A+C)

F AB

2.或非逻辑

F AB

A

F

&

B

与非门

A

F

B

或非门

3. 与或非逻辑

&

F AB CD

第20页/共55页

异或逻辑与同或逻辑

4.异或逻辑

F A B AB AB

A

=1

F

B

5.同或逻辑 F=A ⊙ B= AB AB

A

=

F

B

AB F

00 0 01 1 10 1 11 0

AB F

00 1 01 0 10 0 11 1

② 任意两个i0最小项之积恒i为0A0B,C任·意AB两C个=最0大项之

和恒等于1 。

mi m j 0(i j)

Mi M j 1(i j)

③ n 变量的每一个最小(大)项有n 个相邻项

(相邻项是指两个最小项只有一个因子互为反变

量,其余因子均相同,又称为逻辑相邻项)。

第32页/共55页

2.6 逻辑代数的K诺图

ABC ABC ABC

最大项表达式:

F ( A B C)( A B C)( A B C)

第28页/共55页

最大项的Mi表示

n个变量可以构成2n个最大项。最大项用符号Mi表示。与 最小项恰好相反,对于任何一个最大项,只有一组变量 取值使它为0,而变量的其余取值均使它为1。

数字电子技术基础

上一页 下一页 返回

1.1 数字电路概述

❖ ①数字电路的工作信号是不连续的数字信号,反映在电路上只有高电位 和低电位两种状态,在数字电路中,通常将高电位称为高电平,低电位 称为低电平,为分析方便,可分别用二进制的两个数码1和0来表示。高 电平对应1,低电平对应0,称为正逻辑关系;反之,则称为负逻辑关系。 本书采用的是正逻辑关系。

上一页 下一页 返回

1.1 数字电路概述

❖ ②数字电路在计数和进行数值运算时采用二进制数,每一位只有0和1两 种可能。数字电路中的电子元件通常工作在开关状态,电路结构简单, 容易制造,便于集成化、系列化生产,通用性强,使用方便,成本低。

❖ ③数字电路的工作可靠性高,抗干扰能力强。它是利用脉冲信号的有无 来代表传输0和1这样的数字信息的,幅度较小的干扰不会影响其最终的 结果。

第1章 数字电子技术基础

❖ 1.1 数字电路概述 ❖ 1.2 数制 ❖ 1.3 不同数制间的转换 ❖ 1.4 码制

1.1 数字电路概述

❖ 1.1.1 数字信号与数字电路

❖ 电子电路所处理的电信号可以分为两类:一类是数值随时间的变化而连 续变化的信号,如温度、速度、压力、磁场、电场等物理量通过传感器 变成的电信号,以及广播电视中传送的各种语音信号和图像信号等,它 们都属于模拟信号;另一类信号是在时间上和数值上都是离散的信号,亦 即在时间上是不连续的,总是发生在一系列离散的瞬间,在数值上则是 量化的,只能按有限多个增量或阶梯取值,这类信号称为数字信号。

❖ 脉冲频率f:单位时间(每秒)内出现的脉冲波形个数,单位为赫兹( Hz )、 千赫兹(kHz)、兆赫兹(MHz),脉冲频率f =1/T。

上一页 下一页 返回

1.1 数字电路概述

❖ 1.1.3 数字电路的学习方法

1.1 数字电路概述

❖ ①数字电路的工作信号是不连续的数字信号,反映在电路上只有高电位 和低电位两种状态,在数字电路中,通常将高电位称为高电平,低电位 称为低电平,为分析方便,可分别用二进制的两个数码1和0来表示。高 电平对应1,低电平对应0,称为正逻辑关系;反之,则称为负逻辑关系。 本书采用的是正逻辑关系。

上一页 下一页 返回

1.1 数字电路概述

❖ ②数字电路在计数和进行数值运算时采用二进制数,每一位只有0和1两 种可能。数字电路中的电子元件通常工作在开关状态,电路结构简单, 容易制造,便于集成化、系列化生产,通用性强,使用方便,成本低。

❖ ③数字电路的工作可靠性高,抗干扰能力强。它是利用脉冲信号的有无 来代表传输0和1这样的数字信息的,幅度较小的干扰不会影响其最终的 结果。

第1章 数字电子技术基础

❖ 1.1 数字电路概述 ❖ 1.2 数制 ❖ 1.3 不同数制间的转换 ❖ 1.4 码制

1.1 数字电路概述

❖ 1.1.1 数字信号与数字电路

❖ 电子电路所处理的电信号可以分为两类:一类是数值随时间的变化而连 续变化的信号,如温度、速度、压力、磁场、电场等物理量通过传感器 变成的电信号,以及广播电视中传送的各种语音信号和图像信号等,它 们都属于模拟信号;另一类信号是在时间上和数值上都是离散的信号,亦 即在时间上是不连续的,总是发生在一系列离散的瞬间,在数值上则是 量化的,只能按有限多个增量或阶梯取值,这类信号称为数字信号。

❖ 脉冲频率f:单位时间(每秒)内出现的脉冲波形个数,单位为赫兹( Hz )、 千赫兹(kHz)、兆赫兹(MHz),脉冲频率f =1/T。

上一页 下一页 返回

1.1 数字电路概述

❖ 1.1.3 数字电路的学习方法

数字电路技术基础全清华大学出版社PPT课件

《数字电子技术基础》

《数字电子技术基础》

电子课件

郑州大学电子信息工程学院 2020年6月16日

《数字电子技术基础》

第一章 逻辑代数基础

《数字电子技术基础》

1.1 概述

1.1.1 脉冲波形和数字波形

图1.1.1几种常见的脉冲波形,图(a)为 矩形波、图(b)为锯齿波、图(c)为尖峰波、 图(d)为阶梯波。

八进制有0~7个数码,基数为8,它的计数 规则是“逢八进一”。八进制一般表达式为

D 8 ki8i

《数字电子技术基础》

十六进制数的符号有0、1、2、…、8、9、 A、B、C、D、E和F,其中符号0~9与十进制符 号相同,字母A~F表示10~15。十六进制的计数 规则“逢十六进一”,一般表示形式为

D 16 ki 16 i

十进制数325.12用位置计数法可以表示为

D 1 0 3 1 2 2 0 1 1 5 0 1 0 1 0 1 1 0 2 1 20

任意一个具有n为整数和m为小数的二进制 数表示为

D 2 k n 1 2 n 1 k n 2 2 n 2 k 1 2 1 k 0 2 0 k 1 2 1 k m 2 m

14 2

12

4

10 8 6

• 0110 + 1010 =24 • 1010是- 0110对模24 (16) 的补码

《数字电子技术基础》

四、BCD码(Binary Coded Decimal)

8421BCD码与十进制数之间的转换是直接按位转 换,例如

(2.3 9 )D (001 10 0 . 0 01 0 )84 1 21 1 B

母A、B、C、…表示。其取值只有0或者l两 种。这里的0和1不代表数量大小,而表示两 种不同的逻辑状态,如,电平的高、低;晶 体管的导通、截止;事件的真、假等等。

《数字电子技术基础》

电子课件

郑州大学电子信息工程学院 2020年6月16日

《数字电子技术基础》

第一章 逻辑代数基础

《数字电子技术基础》

1.1 概述

1.1.1 脉冲波形和数字波形

图1.1.1几种常见的脉冲波形,图(a)为 矩形波、图(b)为锯齿波、图(c)为尖峰波、 图(d)为阶梯波。

八进制有0~7个数码,基数为8,它的计数 规则是“逢八进一”。八进制一般表达式为

D 8 ki8i

《数字电子技术基础》

十六进制数的符号有0、1、2、…、8、9、 A、B、C、D、E和F,其中符号0~9与十进制符 号相同,字母A~F表示10~15。十六进制的计数 规则“逢十六进一”,一般表示形式为

D 16 ki 16 i

十进制数325.12用位置计数法可以表示为

D 1 0 3 1 2 2 0 1 1 5 0 1 0 1 0 1 1 0 2 1 20

任意一个具有n为整数和m为小数的二进制 数表示为

D 2 k n 1 2 n 1 k n 2 2 n 2 k 1 2 1 k 0 2 0 k 1 2 1 k m 2 m

14 2

12

4

10 8 6

• 0110 + 1010 =24 • 1010是- 0110对模24 (16) 的补码

《数字电子技术基础》

四、BCD码(Binary Coded Decimal)

8421BCD码与十进制数之间的转换是直接按位转 换,例如

(2.3 9 )D (001 10 0 . 0 01 0 )84 1 21 1 B

母A、B、C、…表示。其取值只有0或者l两 种。这里的0和1不代表数量大小,而表示两 种不同的逻辑状态,如,电平的高、低;晶 体管的导通、截止;事件的真、假等等。

数字电子技术数字电子技术基础知识

一个R 进制数N 可以有两种表示方法:

(1)并列表示法(又称位置计数法) (N)R = ( K n-1K n-2…K 1K 0 . K -1K -2…K -m )R

(2)多项式表示法(又称按权展开法)

(N)R = K n-1×R n-1+ K n-2×R n-2 +…+K 1×R 1 + K 0×R 0

例如,(10110.101)2 =(?)10 (10110.101)2=1×24+1×22+1×21+1×2-1+1×2-3

数字集成电路按照集成度的高低可分为小规模(SSI)、 中规模( MSI )、大规模( LSI )和超大规模( VLSI )几种 类型。

8

第一章 基本知识

三、 数字计算机及其发展 1.数字计算机

数字计算机是一种能够自动、高速、精确地完成数值计算、数据 加工和控制、管理等功能的数字系统。

2.计算机的发展 数字计算机从1946年问世以来,其发展速度是惊人的。 根据组成计算机的主要元器件的不同,至今已经历了四代。 具体如下表所示。

信息的概念:人们站在不同的角度,对“信息”给出了不同的解释。 诸如,“信息是表征物理量数值特征的量”,“信息是物质的反映”, “信息是人类交流的依据”,…,

广义的说,“信息是对客观世界所存在的各种差异的描述”。

3

第一章 基本知识

二、数字系统

什么是数字系统? 数字系统是一个能对数字信号进行存储、传递和加工的实 体,它由实现各种功能的数字逻辑电路相互连接而成。 例如, 数字计算机。 1. 数字信号

1.2 数制及其转换

1.2.1进位计数制

数制是人们对数量计数的一种统计规律。生活中广泛 使用的是十进制,而数字系统中使用的是二进制。

(1)并列表示法(又称位置计数法) (N)R = ( K n-1K n-2…K 1K 0 . K -1K -2…K -m )R

(2)多项式表示法(又称按权展开法)

(N)R = K n-1×R n-1+ K n-2×R n-2 +…+K 1×R 1 + K 0×R 0

例如,(10110.101)2 =(?)10 (10110.101)2=1×24+1×22+1×21+1×2-1+1×2-3

数字集成电路按照集成度的高低可分为小规模(SSI)、 中规模( MSI )、大规模( LSI )和超大规模( VLSI )几种 类型。

8

第一章 基本知识

三、 数字计算机及其发展 1.数字计算机

数字计算机是一种能够自动、高速、精确地完成数值计算、数据 加工和控制、管理等功能的数字系统。

2.计算机的发展 数字计算机从1946年问世以来,其发展速度是惊人的。 根据组成计算机的主要元器件的不同,至今已经历了四代。 具体如下表所示。

信息的概念:人们站在不同的角度,对“信息”给出了不同的解释。 诸如,“信息是表征物理量数值特征的量”,“信息是物质的反映”, “信息是人类交流的依据”,…,

广义的说,“信息是对客观世界所存在的各种差异的描述”。

3

第一章 基本知识

二、数字系统

什么是数字系统? 数字系统是一个能对数字信号进行存储、传递和加工的实 体,它由实现各种功能的数字逻辑电路相互连接而成。 例如, 数字计算机。 1. 数字信号

1.2 数制及其转换

1.2.1进位计数制

数制是人们对数量计数的一种统计规律。生活中广泛 使用的是十进制,而数字系统中使用的是二进制。

数字电子技术基础全套课件ppt

二进制 补码的 形式编 码

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

二、直接A/D转换器

并联比较型

0≤vi < VREF/15 时,7个比较 器输出全为0, CP 到来后,7 个触发器都置 0。经 编码器编码后 输出的二进制 代 码 为 d2d1d0 =000。

教学内容

§11.1 概述 §11.2 D/A转换器 §11.3 A/D转换器

教学要求

1、掌握DAC和ADC的定义及应用; 2、了解DAC的组成、倒T型电阻网络、集 成D/A转换器、转换精度及转换速度; 3、了解ADC组成、逐次逼近型A/D转换器、 积分型A/D转换器、转换精度及转换速度。

11.1 概述

取 1 8

取 2 15

最大量化误差为 △,即1/8V

最大量化误差为 1/2△,即1/15V

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

对双极性模拟电压的量化和编码

由于V-≈V+=0,所以开关S合到哪一边,都相当 于接到了“地”电位,流过每条电路的电流始终不 变。可等效为:

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

i2 Id34 Id28 Id11Id 60 取RF=R

CB7520电路原理图

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

二、直接A/D转换器

并联比较型

0≤vi < VREF/15 时,7个比较 器输出全为0, CP 到来后,7 个触发器都置 0。经 编码器编码后 输出的二进制 代 码 为 d2d1d0 =000。

教学内容

§11.1 概述 §11.2 D/A转换器 §11.3 A/D转换器

教学要求

1、掌握DAC和ADC的定义及应用; 2、了解DAC的组成、倒T型电阻网络、集 成D/A转换器、转换精度及转换速度; 3、了解ADC组成、逐次逼近型A/D转换器、 积分型A/D转换器、转换精度及转换速度。

11.1 概述

取 1 8

取 2 15

最大量化误差为 △,即1/8V

最大量化误差为 1/2△,即1/15V

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

对双极性模拟电压的量化和编码

由于V-≈V+=0,所以开关S合到哪一边,都相当 于接到了“地”电位,流过每条电路的电流始终不 变。可等效为:

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

i2 Id34 Id28 Id11Id 60 取RF=R

CB7520电路原理图

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

任何时刻只允许输入一个编码信号,否则输出将发生混乱。

YY12

I4 I2

I5 I3

I6 I6

I7 I7

Y0 I1 I3 I5 I7

图4.3.2

优先编码器

在优先编码器电路中,允许同时输入两个以 上编码信号。编码时只对优先权最高的进行编码扩展。端

8线-3线优先编码器74LS148选逻通辑输图出(端 图4.3.3)。

写出逻辑表达式

化简

列真值表

说明功能

逻辑图

逐从 级输 1 写入 出到

输 出

逻辑表 达式

化 简

2

最简与或 表达式

Y1 ( AB) Y2 (BC)

Y

Y3 (CA)

1

Y (Y1Y2Y3) (( AB)(BC)(CA))

2

Y AB BC CA

最简与或 表达式

3

真值表

4

电路的逻 辑功能

Y AB BC CA

0 1 1 1 0 ××××

0 1 1 10

0 1 1 1 1 0 ×××

1 0 0 10

0 1 1 1 1 1 0 × ×低电平1表示“0 电路1 工 1 0 0 1 1 1 1 1 1 0 ×作,且1有编码1 输入0 ” 1 0

0 11111110

1 1 1 10

输入:逻辑0(低电平)有效 输出:逻辑0(低电平)有效

用与或非门实现

AG R 00 01 11 10

01 0 1 0

Z (RAG RAG RAG)

10 1 1 1

4.3 若干常用的组合逻辑电路

§4.3.1 编码器

编码:用二进制代码来表示某一信息(文 字、数字、符号)的过程。

实现编码操作的电路称为编码器。

编

高?低?

码 器

码?

一、二进制编码器 输入端:2n

2. 根 ABC L

据 00 0 0

题 00 1 0

意 01 0 0

列 01 1 1 出 10 0 0 真 值 10 1 1 表 11 0 1

11 1 1

3.画出卡诺图化简:

BC A 00 01 11 10

00 0 1 0

10 1 1 1 AC BC AB

L= AC + BC + AB

4、用与非门实现逻辑电路

Z RAG RAG RAG RAG RAG 1 0 1 1

11 0 1

11 1 1

3、化简

AGR AG R 00 01 11 10

01 0 1 0

10 1 1 1

RG AG RA

Z RAG AG RG RA

4、画逻辑图 Z RAG AG RG RA

用与非门实现

Z ((RAG AG RG RA)) ((RAG)(AG)(RG)(RA))

输出端:n

高电平有效3位二进制(8线-3线)编码器真值表

普

I0 I1 I2 I3 I4 I5 I6 I7 Y2 Y1 Y0 10000000000

通 01000000001

编 00100000010

码 00010000011 器 00001000100

00000100101

00000010110

00000001111

例4.3.1:试用两片74LS148组成16线-4线优先编码器。

优先权 最高

A15 ~ A8 均无信号时,才允许对A7 ~ A0 输入信号编码。

3

当输入A、B、

0

C中有2个或3

0

个为1时,输 出Y为1,否则

0 1

4

输出Y为0。所 以这个电路实

际上是一种3

0

人表决用的组

1

合电路:只要 有2票或3票同

1

意,表决就通

1

过。

D C B A

( A )

(DC

) (DCA)

(DCB) (DCB)

(DB)

(DC)

((DBA)(DC ))

((DB) (DC))

L ((AB AC BC)) ((AB)(AC)(BC))

A B

C

L

例4.2.2:

1、列真值表

解:取红、黄、绿三盏灯分别用R、 A、G表示,设灯亮为“1”,不 亮为“0”;故障信号为输出变量 用Z表示,规定正常为“0”,不 正常为“1”。

2、写逻辑函数式

RAGZ 00 0 1 00 1 0 01 0 0 01 1 1 10 0 0

根据设

计要求

分析题意,将设计 要求转化为逻辑关

形式变换

系,这一步为设计

组合逻辑电路的根关据键设计所用

芯片要求

例1:设计三人表决电路(A、B、C)。每人 一个按键,如果同意则按下,不同意则不按。 结果用指示灯表示,多数同意时指示灯亮, 否则不亮。用与非门实现.

解:

1.首先指明逻辑符号取“0”、“1”的含义。三 个按键A、B、C按下时为“1”,不按时为“0”。 输出量为 L,多数赞成时是“1”,否则是“0”。

((DCA) (DCB) (DCB))

解: Y2 ((DBA) (DC)) DBA DC

Y1 ((DCA) (DCB) (DCB)) DCA DCB DCB

Y0 ((DB) (DC)) DB DC

由真值表知:该电路可用来判别输入的4位二 进制数数值的范围。

A B (A B) CI

电

状态无关。

路

时序逻辑电路

任一时刻的输出不仅取决 于现时的输入,而且还与电路 原来状态 有关。

组合逻辑电路的框图

组合逻辑电路在电路结构上不包含存储单 元,仅仅是由各种门电路组成,

4.2 组合逻辑电路的分析和设计方法

§4.2.1 组合逻辑电路的分析方法

已知逻辑电路

分析

分析方法步骤:

说明逻辑功能

组合逻辑电路图

第 四章

-组合逻辑电 路

教学内容

§4.1 概述 §4.2 组合逻辑电路的分析和设计方法 §4.3 常用组合逻辑电路 §4.4 组合逻辑电路的竞争-冒险现象

本章重点

1.组合逻辑电路的分析与设计方法 2.常用组合逻辑模块的使用

4.1 概述

组合逻辑电路

数 字

任一时刻的输出仅取决于 该时刻的输入,与电路原来的

( A B)CI

AB

S A B CI CO ( A B)CI AB

S A B CI CO ( A B)CI AB

这是一个全 加器电路

§4.2.2 组合逻辑电路的设计方法

根据实际逻辑问题

步骤:

确定输入、输出 列出真值表

最简单逻辑电路

设计

选择所需

门电路

写出表达式

并简化

画逻辑电路图

选通输入端

输

入

输

出

S I7 I6 I5 I4 I3 I2 I1 I0 Y2 Y1 Y0 YS YEX

1

××××××××

111

11

0 11111111

1 1 1 01

0 0 ×××××××

0 0 0 10

0

1 0 × × × ×低电×平×表示“电0路工0 1

10

0 1 1 0 × × ×作,×但×无编码输0入”1 0 1 0