一种高速数据采集记录装置的设计

一种高速实时数据采集系统的设计与实现

(2位 总 线 )2 4M /(4 总 线 )。 3 ,6 Bs6 位 1 2 ] P I 部 总线 一边 与处理 器和 存储 器总线 接 口 C 局

数据后置处理等功能 。用 以完成主机对数据采集前 端 送 出的 1 6位并行数 据 的读取 ,和对传感 器数据 的读

取 、 式的转换 、 送} 格 发 l 】 要 包 括 以下 几 个 功 能 模 块 : 。主 P I 线 控 制 器 、IO缓 存 器 ( 片 C 7 4 7 , 度 C 总 FF 一 Y C 25 深

( olg fMa n E gn eig,Notw sen P ltc nc l nv ri C l e o r e n ie r e i n r etr oye h ia U iest h y,Xia 0 2,Chn ) n 71 7 0 ia

【 btat ei i e o f u r seddt a q it na dt nmi inb sd( C (e p ea C m o et A s c】A ds nn m t do sp = p e aa cus i n r s s o ae m P lP f h rl o pn n r g g h a io a s i

另一边 为外设扩展 提供 高带 宽通道 。这样便将 外设 I / O总线上 移下来 , 不需 C U介 入就可进行数据 传输 P PI C 总线 具有 高性 能 、 使用 方便 、 高协 调性 、 数据 完型

基于Lonworks技术的高速数据采集系统的设计

计

i er ace f nt f o LO n tw k N e or an d d ata a s mpli g n mo dul a e dop OP Se e ts C rv r。 Th s t p ses es om pr cti al ty e ys em os s s e a c i si ni ca g fi nce an v ue. d al

Ke wors D a a p i g:H g — p e v d : at S m l n i h s e d; L n o k ; F G owr s P A; O C S r e P e vr

0 引言

L on

系统硬件结构如图一所示 。

爱提了强实 统 很的 供 现 于 段 , 成 为 当今 沥行 的 现 场 总 线 技 术 之 一 。 £

该高速 数据 采集模块 是基于 FG 架构来设 计的。FG PA PA 是整个 系统的控制中心和数据 交换桥梁, 而且能够实现对底

层的信号 陕速预处理 。在很多信号处理系统中,底层的信号 预处理 算法要处理的数据量很大,对处理速度要求很高,但

1 1系统硬件结构设计 .

算法结构相对 比较简单,适于用 FG 进行硬件编程实现。 PA LN O 收发模块采用收发器 F . O,支持 自由拓扑结构, 1_ A ]1

维普资讯

曩 k o r s

{

摘 0CSre。本系统具有一定的实际意义和价值。 P evr

中 图 分 类 号 :T 3 P 11

D s g f H g - p e a a a p i g y t m B s d o 0 w r s e h i u e i n o i h s e d D t S m l n S s e a e n L n 0 k T c n q e 王传云 尹 燕

基于FPGA的高速数据采集系统设计

基于FPGA的高速数据采集系统设计随着科学技术的不断进步,数据采集系统在许多领域都发挥着重要作用。

为了满足高速数据采集的需求,基于现场可编程门阵列(FPGA)的高速数据采集系统设计应运而生。

本文将介绍这一系统的设计原理和关键技术。

首先,我们需要了解FPGA的基本原理。

FPGA是一种可编程的硬件设备,可以根据需要重新配置其内部逻辑电路。

这使得FPGA在数据采集系统中具有极大的灵活性和可扩展性。

与传统的数据采集系统相比,基于FPGA的系统可以实现更高的采样率和更低的延迟。

基于FPGA的高速数据采集系统设计主要包括以下几个关键技术。

首先是模数转换(ADC)技术。

ADC是将连续的模拟信号转换为数字信号的关键环节。

在高速数据采集系统中,需要使用高速、高精度的ADC来保证数据的准确性和完整性。

其次是FPGA内部逻辑电路的设计。

为了实现高速数据采集,需要设计高效的数据处理逻辑电路。

这些电路可以实现数据的实时处理、存储和传输等功能。

同时,还需要考虑电路的时序约束和资源分配等问题,以确保系统的稳定性和可靠性。

另外,时钟同步技术也是高速数据采集系统设计的重要内容。

在高速数据采集过程中,各个模块需要保持同步,以确保数据的准确性。

因此,需要设计合理的时钟同步方案,保证各个模块在同一个时钟周期内完成数据的采样和处理。

最后,还需要考虑系统的接口和通信问题。

基于FPGA的高速数据采集系统通常需要与其他设备进行数据交互,如计算机、存储设备等。

因此,需要设计合适的接口和通信协议,实现数据的传输和存储。

综上所述,基于FPGA的高速数据采集系统设计涉及多个关键技术,包括ADC技术、FPGA内部逻辑电路设计、时钟同步技术以及接口和通信问题。

通过合理的设计和优化,可以实现高速、高精度的数据采集,满足现代科学研究和工程应用的需求。

这将为各个领域的数据采集工作带来巨大的便利和发展空间。

一种基于FPGA的高速数据记录系统的设计

系列的 N N LS A D F ~ H为 存储介 质 的高速 大容 量数 据 记录

系统 的设计 。

2 F G 设计 PA

数据 采集 系统 以三 星 公 司 Fah 芯 片 K F G s O ls 98 O u M 为 主 要存 储器 件 ,使 用 X l x公 司 sat 3 ii n p r n e系 列 F G a PA x 35o C S o E作为 主要控制 器件 , Fah的读 、 、 对 ls 写 擦除 等操 作进 行时序配 置, 另外系统通 过 U B总线将数 据 从 F A H S L S

置 的 高 速 、 容 量 可 独 立 工 作 的 连 续 数 据 流 采 集 记 录 系 统 。 系统 采用 模 块 化 的 设 计 思 想 。 大 具有 设 计 曼 活 、 成度 高 . 集 较

,

I 体 积 和 较 低 的 功 耗 等 优 点 。 服 了常 规 存 储 设 备 容 量 , . 录 时 间 短 。 立 性 不 强 的 缺 点 。相 关 技 术 指 标 满 足 设 计 - 的 克 I记 - 独

C a g Lu h n P nin u Na j g a

Ab t a t T i p p r it d c s a s lt n t aa a q iio ,s r g n rn mi i y tm b s d o h y tm o r- s r c : h s a e nr u e oui O d t c u s in t a e a d t s s o s s ae n t e S s n a P o o o t o a sn e e

Ke r s n, A l ah Soa e MA y wo d : G ;F s trg ;D

实际许多存储 数据记录 系统 中, 由于环境 比较 复杂 , 所

一种高速图像采集装置的设计

一

种 高 速 图像 采 集装 置 的设 计

李 长 乐 , 臧 希 茹 , 赵 杰

( 哈尔 滨 工 业 大 学 机 器 人 研 究 所 , 龙 江 哈尔 滨 1 0 8 ) 黑 5 0 0

摘 要 : 设 计 了一 种 基 于 NI S I 软核 处 理 器为 系统 控 制 核 心 , 高速 线 阵 C D 为 图像 采 集 器 件 、 S R O I 以 C 以 D AM

De i n a H i h— Spe d I a le tn sgn o g e m geCo l c i g Sys e tm

LI a g l ,ZANG — z e Ch n — e Xi h ,ZH AO i Je

( b t sa c n tt t ,H a bnI siu eo Teh oo y,Ha bnH eln Ja g 1 0 8 Ro o e rh I siu e Re ri n tt t f c n lg r i io g in 5 0 0,P. R. C i a hn )

实现 了一 种 高速 图像 采 集 装 置 , 且 简化 了 系统 的 硬 件 结 构 , 高 了装 置 的 实 时性 。 并 提

关 键 词 : 高 速 线 阵 CC FP D; GA; 图像 采 集 中 图 分 类 号 : TN9 1 7 1 . 3;TP 7 . 242 文 献 标 识 码 :A

维普资讯

第 2 卷 第 3 0 期

20 0 7年 9月

石

油

化

工

高

等

学

校

学

报

Hale Waihona Puke VO1 .20N O.3

J OURNAL OF PETROCHEM I CAL UNI VERS TI I ES

一种高速CCD数据采集系统的设计

一种高速CCD数据采集系统的设计作者:刘爽王浩龙再川郭强来源:《现代电子技术》2008年第14期摘要:CCD相机的数据采集是设计实时高分辨率CCD摄像机的瓶颈,1394协议具有高的传输速率,同时在其基础上发展而来的1394b协议,最高的传输速率可以达到32 Gb/s。

设计基于1394传输协议的数据采集系统,该系统具有高的传输速率,可以有效地解决该瓶颈,同时为设计1394b传输系统奠定了基础。

介绍该采集系统的框架图、MCU软件设计流程以及WDM驱动开发等。

经测试,系统工作稳定。

关键词:等时传输;异步传输;TSB12LV32;WDM驱动模型;(1School of Optoelectronic Information,University of Electronic Science and Technology ofAbstract:The data acquisition is the bottleneck in the design of the real[CD2]time and high speed CCD cameraHigh transmission speed is defined in 1394 protocol,and 32 Gb/s is defined in 1394b protocol which comes from 1394 protocolThe system in acquisition based on 1394 is designed in this paper and the system which lays a foundation for the system in acquisition based on 1394b has high speedThe Framework of this system,the flow chart of MCU and development of WDM is givenKeywords:isochronous transaction;asynchronous transaction;TSB12LV32;WDM drive1 引言随着数字技术的进步与发展,对于数据传输的高速率性和时实性提出了很高的要求,IEEE1394协议的出现,很好地解决了该问题。

高精度数据采集系统的设计及性能分析

高精度数据采集系统的设计及性能分析现代工业生产过程中往往需要涉及大量的监测和控制,而高精度数据采集系统的设计和性能分析就是为了满足这种需求而诞生的。

本文将介绍高精度数据采集系统的设计和性能分析的相关技术及应用,同时分析这些技术的应用场景和性能优劣,希望能够对读者有所帮助。

一、高精度数据采集系统的组成高精度数据采集系统是由多个部件组成的复杂系统,其中主要包括传感器、信号调理器、数据采集卡、数据处理软件等。

下面详细介绍这些部件的作用及原理:1. 传感器传感器是高精度数据采集系统中最核心的组成部分之一。

它的作用是将测量对象的物理量转换为电信号输出,常见的传感器包括温度传感器、压力传感器、角度传感器、力传感器等。

不同类型的传感器在测量的物理量和范围上存在差异,同时也有不同的转换方式和输出形式。

2. 信号调理器信号调理器是传感器信号处理的核心,主要负责将传感器输出的信号进行放大、滤波、线性化等处理,使其适合于数据采集卡进行数字化转换。

信号调理器的设计将直接影响系统的稳定性和精度。

3. 数据采集卡数据采集卡是高精度数据采集系统中另一个重要的组成部分,它起到将模拟信号转换成数字信号的作用。

数据采集卡的数字化转换精度和采样率将直接影响采集系统的精度。

4. 数据处理软件数据处理软件是高精度数据采集系统中最后一道关键工序的组成部分。

它的作用是将数据从数据采集卡中读取,并将其经过校准、滤波、标定、控制等算法处理,最终输出给用户需要的数据。

数据处理软件应当具有友好的用户界面、高效的运算能力和稳定的运行性能。

二、高精度数据采集系统的应用场景高精度数据采集系统的应用场景十分广泛,主要包括以下几个领域:1. 工业控制众所周知,现代工厂生产过程需要各种各样的传感器和数据采集设备,以保证产品质量和生产效率。

高精度数据采集系统可以应用于无污染的检测、高速电机控制、发电温度观测、高分辨率精细控制等技术领域。

2. 航空雷达航空雷达数据采集系统需要在高速行动的飞机上进行复杂的数据采集和传输,并要求精度高、稳定性好、机动性强、重量轻等特点。

高速数据采集系统的设计

钟 有 效 ,后 0 5 空 闲 采 样 ,量 化 精 度 为 1 bt .s 2 i。量 化 后 的数 字 量 经 过 通 道 选 择 传 送 到 乒 乓 RAM 中 ,再 以 10 p 2 Mb s的 数 据 率 在 I 周 期 时 间 内 平 稳 输 出 , s的

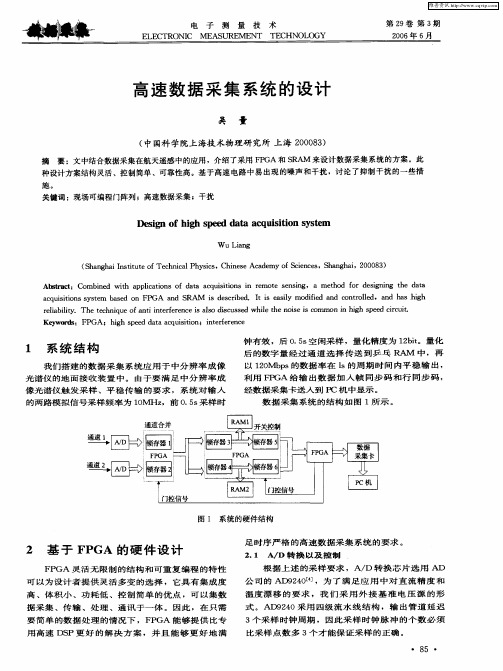

利 用 F GA 给 输 出 数 据 加 入 帧 同 步 码 和 行 同 步 码 , P 经数 据采集 卡送入到 P C机 中 显 示 。 数 据 采 集 系 统 的 结 构 如 图 1所 示 。

摘 要 :文 中结合数据采集在航 天遥感 中的应用 ,介 绍了采用 F GA和 S A 来 设计数 据采集 系统 的方 案。此 P RM 种 设计 方案结构灵活 、控 制简单 、可靠性高 。基 于高速 电路 中易 出现 的噪声和 干扰 ,讨 论 了抑 制干扰 的一 些措

施。

关键词 :现场 可编程 门阵列 ;高速数据 采集 ;干扰

吴

量 :高速数 据采 集 系统 的设 计

由 于 通 道 数 只 有 2路 , 因 此 直 接 取 其 数 字 量 的

第3 期

高 1 b t 人 FP 2 i送 GA 中 ,利 用 FP GA 内部 的 资 源 生 成 锁存器 进 行 两 路 数 据 的合 并 ,这 样 提 高 了集 成 度 ,减 少 了 外 围 的 器 件 数 量 。两 路 锁 存 器 的 时 钟 均

— ~[ — 匝 ) —l = D

i —I/ 1 — — 墅 —◆ ^u —/ —

图 l 系统 的硬件结 构

2 基 于 F GA 的 硬 件 设 计 P

F PGA 灵 活 无 限 制 的 结 构 和 可 重 复 编 程 的 特 性 可 以 为 设 计 者 提 供 灵 活 多 变 的 选 择 ,它 具 有 集 成 度 高 、体 积 小 、 功 耗 低 、 控 制 简 单 的优 点 ,可 以集 数 据 采 集 、传 输 、处 理 、 通 讯 于 一 体 。 因 此 ,在 只 需 要 简 单 的数 据 处 理 的情 况 下 , F PGA 能 够 提 供 比专

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一种高速数据采集记录装置的设计

【摘要】文章介绍了一种基于Flash的高速数据采集记录装置的实现方案;文中采用了Flash高速存储技术与FPGA的二级缓冲技术,提高了存储速度,突破存储芯片的瓶颈,成功实现了数据存储速率与传输速率完美的匹配;同时通过设计合理的电路降低了存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储。

【关键词】数据记录仪;Flash;高速存储

1.系统方案设计

本文设计的数据记录系统由以下几部分组成:两台完全相同的数据记录仪、一个地面综合测试台、上位机、配套软件以及配套电缆。

主要用于记录由雷达系统产生的视频回波、图像及遥测三路LVDS高速信号。

系统工作时,由雷达系统首先发来启动记录信号,使已处于采集状态的两台记录仪同时工作,二者互为备份。

地面测试台产生的模拟信号供记录仪存储,同时可以控制记录仪进入不同的工作状态,通过内置的USB接口读取记录仪的数据;上位机通过USB电缆与地面测试台相接,对回读的数据进行分析,同时验证记录仪是否正常工作。

2.系统硬件设计

该系统采用隔离变压器隔离接收三路LVDS数据,使得隔离前后的电路没有电气连接特性,然后再将隔离后的信号传送给存储模块;经过存储模块的均衡、解串后传给FPGA中心控制器,最后存入两片Flash中。

遥测系统输出的三路数据都有各自的启动记录信号。

当记录仪接收到启动控制信号,开始记录对应路的数据,并存储到相应的存储模块中。

飞行试验完毕后,可以利用备用读数电缆,将各个存储模块中数据通过测试台上传至上位机中进行分析,以便对记录仪的存储功能进行验证。

在飞行模式下记录仪的供电由雷达系统完成。

记录仪由三个存储模块和一个接口模块组成。

存储模块主要接收遥测系统的视频回波、图像及遥测三路LVDS信号,并对其中的有效数据进行实时存储。

该模块主要包括以下几个部分:中心逻辑控制芯片FPGA、配置芯片PROM、LVDS 电缆均衡器、LVDS解串芯片、存储芯片Flash、电源模块以及60MHz晶振等[1]。

如图2.1所示:

接口模块主要包括LVDS高速读数接口、RS-422长线接口、视频及图像遥测雷达信号输入接口、各个存储模块的LVDS输入接口以及数据上传和指令下发接口。

高速读数接口与地面测试台主控卡的相应接口连接,通过LVDS接口高速读取其中的数据;422长线接口通过双绞线电缆与地面测试台连接,主要实现记录仪与地面测试台之间的通信。

3.系统逻辑设计

3.1 Flash高速存储技术设计

由于Flash是基于页读写、块擦除的工作模式[2],在对其进行读、写以及擦除操作都需要一定的等待时间,通过建立无效块列表,有效地提高了读写速率[3]。

由FPGA内部时序控制转换将生成的4K并行数据轮流写入两片Flash中,单片Flash采用交替双平面页编程方式,存储速率能够达到29.85MB/s。

采用两片Flash进行存储,从时间上看两个数据流同时流入两片Flash中,相当于数据总线增加了一倍,实现数据存储速率能够达到单片Flash存储速率的两倍,即有效数据存储率为59.7MB/s,大于有效数据的传输速率59MB/s,能够保证对每路数据源的可靠存储。

3.2 存储模块逻辑设计

LVDS数据流可以直接按字节方式分离并存储,该方式虽然可以降低FPGA 内部资源的消耗,但是加大了对存储数据恢复的复杂程度,并其中一路存储时出现丢数,容易影响到另一路数据的存储,造成数据结构的紊乱,导致存储数据无法恢复。

因此采用FPGA内部双口RAM资源,实现8Kbyte数据的缓冲,之后增加两个4K双口RAM,构成了二级缓冲。

对于单路的I/P/Q信号,数据在60M 的时钟下写入一级缓冲(8K)中,当判断写入数据大于7106后,以60M的速率连续读取4096个数据给二级缓冲A,同时控制Flash(A)模块对二级缓冲A 中的数据进行判断,当写入数据大于10个后,以30M的速率连续读取4096个并写入Flash(A)中;当再次判断一级缓冲(8K)中读写地址差值大于7106后,同样以60M的速率连续读取4096个数据,并写入二级缓冲B,当控制Flash(B)模块判断二级缓冲B中数据大于10个后,同样以30M的速率读取4096个后写满Flash(B)中的一页。

上述操作交替进行,实现LVDS数据流中的有效数据轮流有序地存入两片Flash中。

存储模块内部实现两级缓冲的逻辑原理框图见图:

4.系统可靠性设计

记录仪的正常工作离不开其可靠性设计。

若电路设计的不合理,记录仪的工作性能得不到保障,严重时会损坏设备,可见电路的可靠性设计[4]是记录仪正常运行的首要保障。

4.1 降低存储模块功耗的可靠性设计

存储模块的供电经过电源芯片进行电压转换,给存储模块内部芯片供电。

在未灌封之前进行多次常温测试发现,工作时电源芯片和XC3S200表面温度较高,而且由于对记录仪小体积的要求,要求内部芯片焊接很集中;而且记录仪在高空试验环境中会受到高冲击、高过载的影响,必须对记录仪存储模块进行灌封,增加抗冲击能力。

为了解决上述问题,降低消耗在存储模块电源芯片本身的功耗。

下面对存储模块进行温度测试试验。

为了获得存储单元灌封后的内部温度,我们

使用热电偶对内部多点进行测量,实时显示温度。

在试验一和试验二中,我们选定以下七个点,试验三中增加了中壳体外壁一点。

通过以上设计的试验可以看出,当存储模块的供电电源输入为3.6V左右时,测试各点的温度都所有下降,在芯片正常工作范围内,且存储模块在长达十几小时的高温环境中仍能正常工作,说明存储模块输入电源采用3.6V供电的可靠性。

4.2 记录仪通信的可靠性设计

在整个存储设备中,RS-422传输协议主要实现记录仪与测试台之间的通信功能,控制记录仪的工作状态,另外,还可以完成记录仪的长线读数功能。

数据是以串行差分形式传输,测试台主控卡向记录仪下发传输命令的长度都是以6个字节为基本单位,其中,前两个字节为固定帧头“55H”、“AAH”;第3个字节为命令长度,为固定的“02H”;第4、5个字节为命令字,针对不同的命令会有对应的命令字;第6个字节是校验和,大小等于两个命令字的和。

记录仪也采用相同的命令格式进行返回命令的上传[5]。

为保证控制指令传输的可靠性,数据校验是必不可少的,因此,我们在协议中设计了校验码。

同时,协议中还设计了命令信号从测试台、接口板、存储板、接口板,最后返回测试台指令反馈机制,增强了系统对错误命令的识别能力,提高了系统执行命令的抗干扰能力。

5.结论

文中研究的高速数据记录仪设备采用了双片选、双平面交替编程进行数据存储,并通过FPGA内部的二级缓冲技术,使得记录仪的总体写入速度加倍,采用合理的电路降低存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储,完全满足设计的高速存储要求。

目前该系统通过了高低温、振动、冲击及电磁兼容等环境试验,能够满足实际的工程要求。

参考文献

[1]Gyu Sang Choi,Byung-Won On.Study of the performance impact of a cache buffer in solid-state disks[J].Microproc-essors and Microsystems,2011,35(3):359-369.

[2]高怡祯.基于闪存的星载大容量存储器的研究和实现[J].电子技术应用,2003,8:75-78.

[3]Jeong-Uk Kang,Jin-Soo Kim,Chanik Park,Hyoungjun Park,Joonwon Lee.A multi-channel architecture for high-performance NAND flash-based storage system[J].Journal of Systems Architecture,2007,52(9):644-658.

[4]李煊,丁为.常用设备串口通信协议及其应用[J].自动化仪表,2011,32

(10):82-86.。