数字逻辑期末试卷(A卷)试题及答案

《数字电路与数字逻辑》期末考试及答案

《数字电路与数字逻辑》期末考试试卷考生注意:1.本试卷共有五道大题,满分100分。

2.考试时间90分钟。

3.卷面整洁,字迹工整。

1. 将下列二进制数转为十进制数(1010001)B = ( )D (11.101)B = ( )D 2. 将下列有符号的十进制数转换成相应的二进制数真值、原码、反码和补码 (+254.25)=( )真值 = ( )原码=( )反码 = ( )补码3. 把下列4个不同数制的数(76.125)D 、(27A)H 、(10110)B 、(67)O 按从大到小的次序排列()>( )>( )>( ) 。

4. 对于D 触发器,欲使Q n+1=Q n,输入D=( ),对于T 触发器,欲使Q n+1=Q n,输入T=( )5. 一个512*8位的ROM 芯片,地址线为( )条,数据线为()条。

6. 对32个地址进行译码,需要( )片74138译码器。

7. 存储器起始地址为全0,256K*32的存储系统的最高地址为( )。

8. 将下列各式变换成最简与或式的形式=+B A ( )=+B A A ()=++C B C A AB ())进制。

二、组合电路设计题(每空10分,共20分)1. 用八选一数据选择器74LS151实现逻辑函数AC BC AB C B A L ++=),,( (10分) 2、用74LS138设计一个电路实现函数F = AB+ B C (提示:在74LS138的示意图上直接连线即可)(10分)三、组合电路分析题(共10分) 已知逻辑电路如下图所示,分析该电路的功能。

四、分析题(共24分) 1、分析如下的时序逻辑电路图,画出其状态表和状态图,并画出Q1,Q2的波形图,Q1Q2初态为00。

(14分)2、电路如图所示,要求写出它们的输出函数表达式,化简,并说出它们的逻辑功能。

(10分)五、设计题(共26分)1.用JK 触发器设计一个“111”序列检测器,允许重复,要求用一个输出信号来表示检测结果。

电子技术及数字逻辑试卷A及答案

绝密★启用前黑龙江外国语学院继续教育学院 2014 年 秋 季学期《电子技术及数字逻辑》试卷( A 卷)一、 填空题(本大题共 9小题,每空 1分,共 15分)1.N 型半导体是在本征半导体中掺入 价元素,其多数载流子是 ,少数载流子是 。

2.稳压管的稳压区是其工作在 。

3.数字系统使用 的物理元件,与此相对应,采用的记数制和编码制也都以 数 为基础。

4.使用布尔代数定律时,利用 规则. 规则. 规则可得到更多的公式。

5.放大电路必须加上合适的 才能正常工作。

6.运放的共模抑制比定义为 。

7.直接写出函数F=[(AB+C)D+E]B 的反演函数为 。

8.三极管工作在饱和区时,发射结应为 偏置,集电结应为 偏置。

9.为提高放大电路的输入电阻,应引入 反馈;为降低放大电路输出电阻。

二、选择题(本大题共15小题,每题2分,共30分)1.当温度升高时,二极管的反向饱和电流将 。

A .增大 B.减小 C.不变2.互补输出级采用共集形式是为了使 。

A.电压放大倍数大B.不失真输出电压大C.带负载能力强3.测试放大电路输出电压幅值与相位的变化,可以得到它的频率响应,条件是 。

A. 输入电压幅值不变,改变频率B. B.输入电压频率不变,改变幅值C.输入电压的幅值与频率同时变化 4.交流负反馈是指 。

A .阻容耦合放大电路中所引入的负反馈B .只有放大交流信号时才有的负反馈C .在交流通路中的负反馈5.功率放大电路的最大输出功率是在输入电压为正弦波时,输出基本不失真情况下,负载上可能获得的最大 。

A .交流功率B .直流功率C .平均功率 6.滤波电路应选用 。

A .高通滤波电路 B. 低通滤波电路 C. 带通滤波电路7.放大电路中,测得某三极管三个电极电位U 1.U 2.U 3分别为U 1=3.3V ,U 2=2.6V ,U 3=15V 。

由此可判断该三极管为 。

A .NPN 硅管 B. NPN 锗管 C. PNP 硅管 d.PNP 锗管8.与八进制数(47.3)8等值的数为 。

数字逻辑电路期末考试试卷及答案

期末考试试题(答案)一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____.A .AB F = B .C AB F += C .C A AB F +=D . C B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算.A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断 5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6。

与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D C B A F +++= B . D C B A F +++=C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。

B A F & ∇ F B A &8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。

A. 500KHz B.200KHzC. 100KHz D.50KHz9.下列器件中,属于时序部件的是_____A_____.A.计数器B.译码器C.加法器D.多路选择器10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。

A. 0100100 B.1100011 C. 1011011 D.0011011二、填空题(每小题2分,共20分)11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2。

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分)1、为了表示104个信息,需7位二进制编码[V ]2、BCD码能表示0至15之间的任意整数[X ]3、余3码是有权码[X ]4、2421码是无权码[X ]5、二值数字逻辑中变量只能取值6、计算机主机与鼠标是并行通信7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ][X ][V ][V ]9、上升时间和下降时间越长,器件速度越慢[V ]10、卡诺图可用来化简任意个变量的逻辑表达式[X ]、写出图中电路的逻辑函数表达式。

(每小题5分,共10分)1、F=A B2、F= AB CD2分,共20分)1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A °TTL 电路(A) F = ABCD(B) F = AH ・ CD -(C) F= A + B + C + D(D) F = A + B • C + D (E) F= A BCD4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _°(A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q.(D) BC= 1 , D= 15、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。

(A) AB + AC + BC (B) AB + C (A4-B)(C) AB + CABA — O ?=11 QA |— I1 F •-&1 Q AB L Il —(B)悬0----空。

—A — &Bo —Co- &BA3 •满足如图所示电路的输岀函数F 的表达式为丄3B 1 o — VOF(D) AB +C (E) 19.图示电路中,当各触发器的状态为C 时.再输入一个CP 脉冲,融发器的 状态为QiQ 严0 0。

2001级《数字逻辑》试卷A答案及评分标准

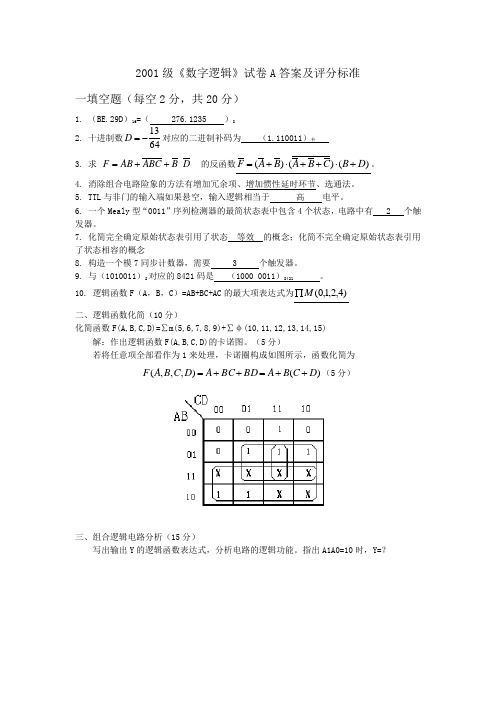

2001级《数字逻辑》试卷A 答案及评分标准一填空题(每空2分,共20分)1. (BE.29D )16=( 276.1235 )82. 十进制数6413-=D 对应的二进制补码为 (1.110011)补 3. 求 D B ABC AB F ++= 的反函数)()()(D B C B A B A F +⋅++⋅+=。

4. 消除组合电路险象的方法有增加冗余项、增加惯性延时环节、选通法。

5. TTL 与非门的输入端如果悬空,输入逻辑相当于 高 电平。

6. 一个Mealy 型“0011”序列检测器的最简状态表中包含4个状态,电路中有 2 个触发器。

7. 化简完全确定原始状态表引用了状态 等效 的概念;化简不完全确定原始状态表引用了状态相容的概念8. 构造一个模7同步计数器,需要 3 个触发器。

9. 与(1010011)2对应的8421码是 (1000 0011)8421 。

10. 逻辑函数F (A ,B ,C )=AB+BC+AC 的最大项表达式为)4,2,1,0(M ∏ 二、逻辑函数化简(10分)化简函数F(A,B,C,D)=∑m(5,6,7,8,9)+∑φ(10,11,12,13,14,15)解:作出逻辑函数F(A,B,C,D)的卡诺图。

(5分)若将任意项全部看作为1来处理,卡诺圈构成如图所示,函数化简为)(),,,(D C B A BD BC A D C B A F ++=++=(5分)三、组合逻辑电路分析(15分)写出输出Y 的逻辑函数表达式,分析电路的逻辑功能。

指出A1A0=10时,Y=?D3 D2 D1 D0 Y解:地址变量A1和A0为00时,D0被送至输出端;A1和A0为01时,D1被送至输出端;A1和A0为10时,D2被送至输出端。

A1和A0为11时,D3被送至输出端。

因此输出Y 的逻辑方程为301201101001D A A D A A D A A D A A Y +++=(8分)为四选一数据选择器。

数字逻辑电路试题

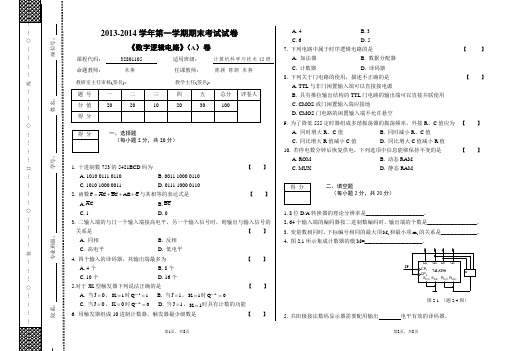

院系: 专业班级: 学号: 姓名: 座位号:A. 4B. 3C. 6D. 57. 下列电路中属于时序逻辑电路的是【 】A. 加法器B. 数据分配器C. 计数器D. 译码器8. 下列关于门电路的使用,描述不正确的是 【 】A. TTL 与非门闲置输入端可以直接接电源B. 具有推拉输出结构的TTL 门电路的输出端可以直接并联使用C. CMOS 或门闲置输入端应接地D. CMOS 门电路的闲置输入端不允许悬空9. 为了降低555定时器组成多谐振荡器的振荡频率,外接R 、C 值应为 【 】A. 同时增大R 、C 值B. 同时减小R 、C 值C. 同比增大R 值减小C 值D. 同比增大C 值减小R 值 10. 若停电数分钟后恢复供电,下列选项中信息能够保持不变的是 【 】A. ROMB. 动态RAMC. MUXD. 静态RAM1. 8位D/A 转换器的理论分辨率是_____________________。

2. 64个输入端的编码器按二进制数编码时,输出端的个数是__________________。

3. 变量数相同时,下标编号相同的最大项i M 和最小项i m 的关系是_____________。

4. 图2.1所示集成计数器的模M=_____________________。

图2.1 (题2.4图)5. 共阳极接法数码显示器需要配用输出 电平有效的译码器。

二、填空题(每小题2分,共20分)6. 对于T 触发器,当T=______时,触发器处于保持状态。

7. 逻辑函数C B AB F +=的反函数F 为_____________________。

8. 5个变量的逻辑函数全部最大项有_____________________个。

9. 二进制数()20110.101110转换成十进制数是___________________。

10. 同步RS 触发器的特性方程中,约束条件为RS=0,说明这两个输入信号不能同时为_____________________。

《数字逻辑》——期末复习题及答案

《数字逻辑》——期末复习题及答案中国⽯油⼤学(北京)远程教育学院《数字逻辑》期末复习题⼀、单项选择题1. TTL 门电路输⼊端悬空时,应视为( )A. ⾼电平B. 低电平C. 不定D. ⾼阻2. 最⼩项D C B A 的逻辑相邻项是()A .ABCDB .D BC A C .CD AB D .BCD A3. 全加器中向⾼位的进位1+i C 为( )A. i i i C B A ⊕⊕B.i i i i i C B A B A )(⊕+C.i i i C B A ++D.i i i B C A )(⊕4. ⼀⽚⼗六选⼀数据选择器,它应有()位地址输⼊变量A. 4B. 5C. 10D. 165. 欲对78个信息以⼆进制代码表⽰,则最少需要()位⼆进制码A. 4B. 7C. 78D. 106. ⼗进制数25⽤8421BCD 码表⽰为()A.10 101B.0010 0101C.100101D.101017. 常⽤的BCD 码有()A:奇偶校验码 B:格雷码 C:8421码 D:ASCII 码8. 已知Y A AB AB =++,下列结果中正确的是()A:Y=A B:Y=B C:Y=A+B D: Y A B =+9. 下列说法不正确的是()A:同⼀个逻辑函数的不同描述⽅法之间可相互转换B:任何⼀个逻辑函数都可以化成最⼩项之和的标准形式C:具有逻辑相邻性的两个最⼩项都可以合并为⼀项D:任⼀逻辑函数的最简与或式形式是唯⼀的10. 逻辑函数的真值表如下表所⽰,其最简与或式是()A: ABC ABC ABC ++ B: ABC ABC ABC ++ C: BC AB + D: BC AC +11.以下不是逻辑代数重要规则的是( ) 。

A. 代⼊规则B. 反演规则C. 对偶规则D. 加法规则12.已知函数E)D (C B A F +?+=的反函数应该是( ) 。

A. [])E (D C B A F +?+?= B. [])E D (C B A F +?+?= C. [])E (D C B A F +?+?=D. [])E D (C B A F +?+?=13.组合逻辑电路⼀般由()组合⽽成。

《数字逻辑》期末复习题及答案

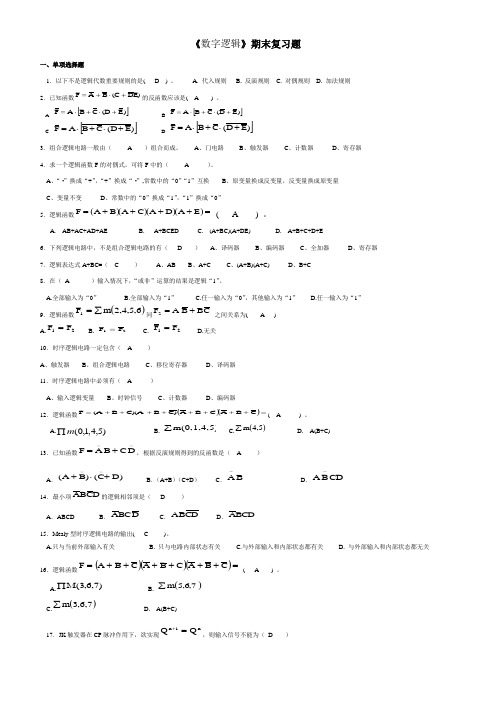

《数字逻辑》期末复习题一、单项选择题1.以下不是逻辑代数重要规则的是( D ) 。

A. 代入规则 B. 反演规则 C. 对偶规则 D. 加法规则2.已知函数E)D (C B A F +⋅+=的反函数应该是( A ) 。

A.[])E (D C B A F +⋅+⋅= B. [])E D (C B A F +⋅+⋅= C. [])E (D C B A F +⋅+⋅= D. [])E D (C B A F +⋅+⋅=3.组合逻辑电路一般由( A )组合而成。

A 、门电路 B 、触发器 C 、计数器 D 、寄存器4.求一个逻辑函数F 的对偶式,可将F 中的( A )。

A 、“·”换成“+”,“+”换成“·”,常数中的“0”“1”互换B 、原变量换成反变量,反变量换成原变量C 、变量不变D 、常数中的“0”换成“1”,“1”换成“0”5.逻辑函数()()()()=++++=E A D A C A B A F ( A ) 。

A. AB+AC+AD+AEB. A+BCEDC. (A+BC)(A+DE)D. A+B+C+D+E6.下列逻辑电路中,不是组合逻辑电路的有( D ) A 、译码器 B 、编码器 C 、全加器 D 、寄存器7.逻辑表达式A+BC=( C ) A 、AB B 、A+C C 、(A+B)(A+C) D 、B+C8.在( A )输入情况下,“或非”运算的结果是逻辑“1”。

A.全部输入为“0”B.全部输入为“1”C.任一输入为“0”,其他输入为“1”D.任一输入为“1”9.逻辑函数()6,5,4,2m F 1∑=同 C B B A F 2+=之间关系为( A ) A.21F F = B. 21F F = C. 21F F = D.无关10.时序逻辑电路一定包含( A )A 、触发器B 、组合逻辑电路C 、移位寄存器D 、译码器11.时序逻辑电路中必须有( A )A 、输入逻辑变量B 、时钟信号C 、计数器D 、编码器12.逻辑函数()()=++++++++=C B A C B A C )B C )(A B (A F ( A ) 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

华东师范大学期末试卷(A)

2009 —2010学年第一学期

课程名称:数字逻辑

学生姓名:学号:

专

业年级/班级

课程性质:公共必修、公共选修、专业必修、专业选修

一、填空题 (20分,每空2分)

1. ( 34.5)10 = ( (1) 11 0100.0101 ) 8421BCI= ((2) 100010.1 ) 2 = ( _( 3)

22.8 ) 16。

2. Y = A(B +C) +CD 的对偶式为(4)Y' = AC+BC + AD 。

3. 在数字系统中,要实现线与功能可选用(5) OC/OD门;要实现总线结

构可选用(6)传输门。

4. 化简F (A,B,C,D) =E m(3, 5, 6, 7, 10) + d (0, 1, 2, 4, 8)可得(7)

F=A'+ B' D' 。

5. 已知某左移寄存器,现态为011001 ,若空位补0,则次态为

(8)110010 ______ 。

6. 二进制数(一10110) 2的反码和补码分别为(9) 101001 和(10)

101010 。

二、选择题(20分,每题2分)

1. 在下列逻辑部件中•不属于组合逻辑部件的是 D 。

A. 译码器 B •编码器 C •全加器 D •寄

存器

2. 逻辑表达式A+BC = __B _______ 。

A . A + C

B . (A + B)(A +

C) C. A+B+ABC D. B+ C

3. 能得出X= 丫的是C

A. X+ Z= Y+ Z

B.XZ=YZ

C. X+ Z= Y+ Z且XZ=YZ

D.以上都不能

4. 为将D触发器转换为T触发器,图中所示电路的虚框内应是 A 。

A .同或门

B .异或门

C .与非

5. 设A1、A2、A3为三个信号,则逻辑函数 C 能检测出这三个信号中

是否含有奇数个高电平。

A . A1A2A3

B . A1+A2+A3

C . A1 ® A2 ®

A3 D . A1+ A2A3

6. 以下说法正确的是_C ___

A. TTL门电路和CMO门电路的输入端都可以悬空

B. TTL门电路和CMOS]电路的输入端都不可以悬空

C. TTL门电路的输入端可以悬空,而CMO门电路的输入端不可以悬空

D. TTL门电路的输入端悬空时相当于接高电平,CMO门电路的输入端悬空时相当

于接低电平。

7. 除JK触发器外,_B ____ 也可实现翻转功能

A. D触发器

B. T 触发器D. SR 触发器

C. SR 锁存器

8. D .触发器是时序逻辑电路的基本逻辑单元

A.计数器B .门电路C .寄存器D .触发器

9. 为了能使用数字电路处理模拟信号,须将模拟信号通过_A ____ 转换为相

应的数字信号。

A. A/D转换器

B. D/A转换器

C. A/D或D/A转换器

D.以上都不行

10. 触发器和时序电路中的时钟脉冲一般是由 A 产生的,它可由555

定时器构成。

A.多谐振荡器

B. 施密特触发器

C. 单稳态触发器

D.边沿触发器

精品文档

三、简答题 (5分)

用卡诺图化简下面逻辑函数,要求为最简与或式 Y=F (A,B,C )=ABC+A'B'+C 答:

F 八 m( 0,1, 3, 4, 5, 7 )

F=B+C

四、分析题 (30分)

1、分析下图的逻辑功能,写出 完成什么功能。

(10分)

Y1、Y2的逻辑函数式,列出真值表,指出电路 答:

1

但迢这两卜式子所表示的逻辑功能还不够直?t所以我们进•步列出人和笃的直值表•如表4-U,从这个其值表上可以看岀.当人厲工中有奇数亍]时1;等于等于唤当乂/工中有闻个以上崗时为I时,岭等于1,否则等于山如果把仁AM看做是相削的三个二进制数,则儿就扭辎出的和就是输出的进位.因此•图4・I实际上就是一个全加器“

2、设触发器的初始状态为Q仁0, Q前0,试画出Q1、Q2端的电压波形(8分)

答:

答:

(1)驱动方程:J O = XQ', K 0=1; J 1二XQ, K 1二X 状态方程:= XQ o Q] XQ 1 Q °* = XQ ;Q o

输出方程:丫二XQ 1 (2)状态转换表: X Q1 Q0 J0 K0 J1 K1 *

Q1 *

Q0 丫

0 0 0 0 1 0 1 0 0 0 0 0 1 0 1 0 1 0 0 0 0 1 0 0 1 0 1 0 0 0 0 1 1 0 1 0 1 0 0 0 1

0 0 1 1 0 0 0 1 0 1

1

1

1

1

1

(叮边沿絶後的发养

3、设下图电路状态S=QiQo ,起始时状态为QiQo=OO 。

要求:(1)写出电路的 输出方程、驱动方程及状态方程(3分);(2)列出状态转换表(4分);(3) 画 出完整的状态转换图(3分);(4)说明该电路的逻辑功能(2分)。

(共12

1 1 0 0 1 0 0 1 0 1 1

1

1

1

1

1

1

(3)状态转换图:

况下输出为0。

四、设计题 (25分)

1、四位同步二进制计数器 74LS161的引脚图和功能表分别如下图所示,Q A 为最高位,请基于74LS161用反馈清零法设计一个模数为7的计数器。

(8分)

i ( I >

二一一二二

-LOAD -CLR CLK

输

入

输

Jll

CP CLR LOAD ENP E5T

A B C D

Q A Q B QcQn

X

0 X X X X X X x

0 0 0 0

t

1 Q X

X AB C D

A B C D

X 1 1 0 X

X X X K 保持(RCO 不变)

X

1 1 X

)(X x x 尿持(耽冋) t

1

1

1 1

X X X X

十六进制让数

答:

10

(4)电路的逻辑功能:

1”时输出为1,其余情

ENP

RCO

74LS1S1

AAAO ^^'

中

輸

入

输

出

崭+舟

^2 Ti -A )

弓 写 网

耐

d

1

d d d 1 1 1 1 1 1 1 1 0

d

d d d 1

1

1

1 1

1

1 1 1

0 0 0

1

1

1 1

1

1 1 1 0 0 0 1 1 0

1 1 1 1 1 1 1

0 0

1

1

1

1

1

1

1

1 1

0 1 1 1

1

1

1

1 1

1 1 0 1 0 0 1 1 1 1 0 1 1 1 1

1

1

1

1

1

1

1

1 1 1

1

1

1

1

1

1

1

1

1 1

1

1

1

1

1

1

1

1

1

1

2、设计用三个开关控制一个电灯的逻辑电路。

要求改变任何一个开关的状 态都能控制电灯由亮变灭或由灭变亮。

试用如下两种中规模组件(逻辑符号及功 能表见下表)实现该逻辑电路功能,可辅以适当的门电路。

(17分) (1) 用四选一数据选择器74LS153实现; (2) 用三—八译码器74LS138实现。

四选一选择器功能表

输入 输出

A t

缶

E'

Y

1

4>

1

也丫

0 0

态序表

N Q D Q C Q B Q A

0 0 1 0 2 0 3 0 4 0 5 0 6 0 7

0 0 0 寸

0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0

1

1

1 _

SCO

QU

QB QC QD

CP

B C

D

EhlF ENT -LOAD

-CLR > CLK

译码器的功能表C4LS158)

答:

逻辑抽象2分,列出真值表3分,写出函数表达式2分。

哦八叭C表用=个双时关•井用0和1分别表示幵关的两个状态" 以,农不灯的状态・阳1表水胚、帀0表爪灭。

设4HC=000时1二亿从这个状态斤始t 单也改变任何卩幵关的状态F的状态都變变化=憔此列出F与仁趴&之间逻辑关系妁專值表

从鹿值表可出逻骑式

y = CC + + ABC f+ ABC

(1)4选1数据选择器输出的逻辑式可写为:

Y= A1' AO' D0+ A1' AOD1+ A1A0 D2+ A1A0D3

只要令数据选择器的输入为A仁A, A0= B, Dg D3= C, D仁D2= C',如图所示,则数据选择器的输出即为要求得到的函数。

$ (5 分)

⑵ Y(A,B,C)=m1+m2+m4+m7=(m1 m2 m4 m7 ) ' =(Y1' Y2' Y4' Y7')'。

Ao Al *2

(5 分)。