锁相环的CD4046应用分析

CD4046锁相环在感应加热电源中的应用

CD4046 锁相环在感应加热电源中的应用

应用于钎焊、熔炼等热加工工艺的感应加热电源在运行过程中,随着负载温度升高和炉料的熔化,负载等效参数会产生时变,从而引起负载固有谐振频率的变化。

为了使逆变器始终工作在功率因数接近或等于 1 的准谐振或谐振状态,控制电路必须能够实现频率自动跟踪。

本文采用LEM 电流传感器、电压比较器和CD4046 锁相环对负载电流

进行频率跟踪,实现了功率器件的零电流开关(ZCS),减小了开关损耗和电磁干扰(EMI)。

由于在电路刚起动时,电流反馈信号为零,CD4046 不能入锁。

本文提出了一种利用CD4046 自身特点实现的它激到自

激的转换电路,很好地解决了这一问题。

另外,加上相位补偿电路的引入,最终实现了频率自动跟踪控制。

整个电路具有跟踪速度快、跟踪频率准确、保护容易、抗干扰能力强等优点。

CD4046 锁相环在感应加热电源中的应用----锁相环功能原理

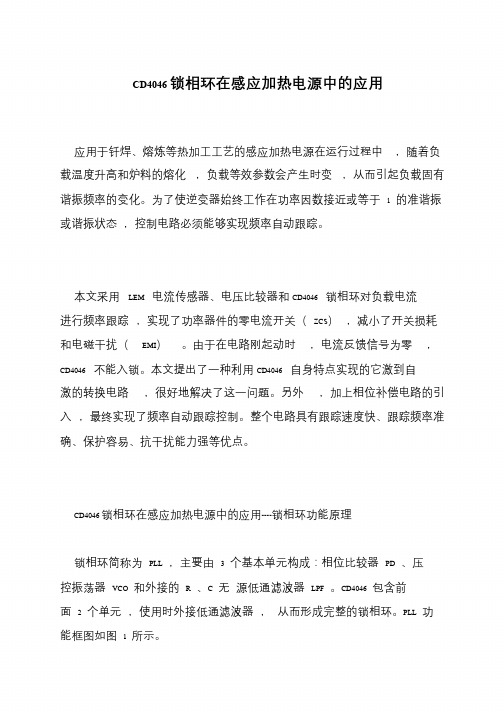

锁相环简称为PLL ,主要由3 个基本单元构成:相位比较器PD 、压

控振荡器VCO 和外接的R 、C 无源低通滤波器LPF 。

CD4046 包含前

面 2 个单元,使用时外接低通滤波器,从而形成完整的锁相环。

PLL 功能框图如图1 所示。

锁相环CD4046应用介绍

锁相环CD4046应用介绍锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)。

低通滤波器三部分组成,如图1所示。

图1压控振荡器的输出U o接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压U d大小决定。

施加于相位比较器另一个输入端的外部输入信号U i与来自压控振荡器的输出信号U o相比较,比较结果产生的误差输出电压UΨ正比于U i和U o两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压U d。

这个平均值电压U d朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

图2当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

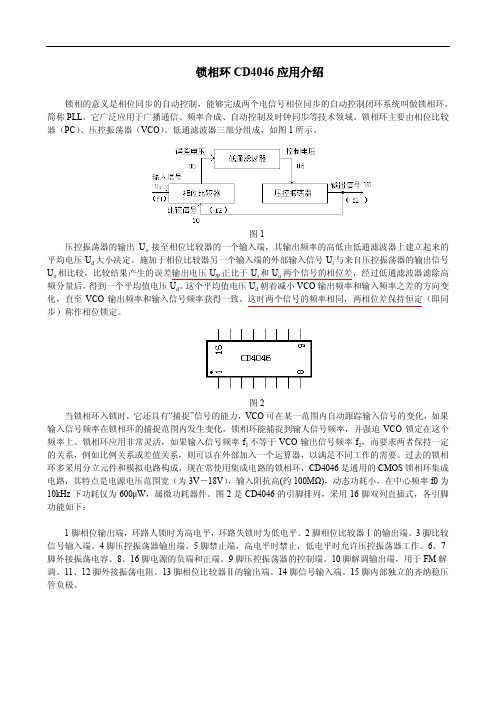

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用16脚双列直插式,各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

锁相环在频率调制与解

1 引言锁相环(pll)是一种能跟踪输入信号相位的闭环自动控制系统。

它在无线电技术的各个领域都得到了广泛的应用。

集成环路部件以其低成本、性能优良、使用简便而得到了青睐。

它在频率调制与解调、频率合成、电视机彩色副波提取、fm立体声解码、遥控系统、频率的编码和译码等诸多方面均得到了利用。

本文介绍了集成锁相环cd4046在频率的调制与解调方面的应用。

2 集成锁相环cd4046介绍2.1 cd4046结构及性能特点它的内部结构框图如图1所示。

它是低功耗cmos型、多功能数字环。

主要参数如下:(1)工作电压3v-18v;(2)静态工作电流(15端开路)10ua;(3)最高工作频率为1.2mhz;(4)稳压管稳定电压4.45v-6.15v。

它含有两个相位比较器p c?与pcii。

pc?要求输入信号为方波,pcii则无此要求,有一个压控(频率)振荡器vco。

在两个相位比较器的输入端有一个前置放大器,可把100mv的微弱信号变为满电平的方波脉冲。

a2是低滤波器输出缓冲放大器。

cd4046采用16线双列直插式封装,各管脚功能如附表所示:图1 cd4046内部结构框图2.2 cd4046构成频率调制与解调电路的工作原理当从9脚输入音频信号时,从4端可输出受输入信号调制的调频信号。

电路如图2所示,由于调频时要求vco有一定的频率范围(频偏),所以不用r2收缩频带,即r2为无穷大(12脚空置)仅用r 1和c1确定vco的中心频率f0即可。

设计参数时,只需由f0查图4(电源电压vdd为9v时的曲线,横坐标为c1取值)求出c1与r1即可。

图2 cd4046构成的频率调制电路当从14脚输入一被音频信号调制的(中心频率与cd4046的vco的中心频率相同)调频信号,则相位比较器输出端将输出一个与音频信号具有相同变化频率的包络信号,经低通滤波器滤去载波后,即剩下调频信号解调后的音频信号了。

一般使用pci,这时仅由r1和c1确定vco的中心频率f0,而不用r2来收缩频率范围(其为无穷大)。

MC4046应用

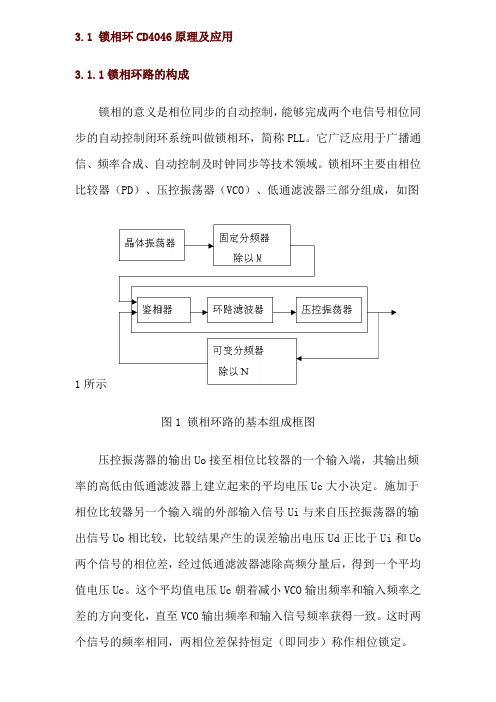

3.1 锁相环CD4046原理及应用3.1.1锁相环路的构成锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PD)、压控振荡器(VCO)、低通滤波器三部分组成,如图1所示图1 锁相环路的基本组成框图压控振荡器的输出Uo接至相位比较器的一个输入端,其输出频率的高低由低通滤波器上建立起来的平均电压Uc大小决定。

施加于相位比较器另一个输入端的外部输入信号Ui与来自压控振荡器的输出信号Uo相比较,比较结果产生的误差输出电压Ud正比于Ui和Uo 两个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压Uc。

这个平均值电压Uc朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号频率获得一致。

这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,它还具有“捕捉”信号的能力,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个频率上。

锁相环应用非常灵活,如果输入信号频率f1不等于VCO 输出信号频率f2,而要求两者保持一定的关系,例如比例关系或差值关系,则可以在外部加入一个运算器,以满足不同工作的需要。

过去的锁相环多采用分立元件和模拟电路构成,现在常使用集成电路的锁相环,CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V-18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

3.1.2CD4046的引脚排列,采用 16 脚双列直插式,各引脚功能如下:图1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

锁相环的CD4046应用

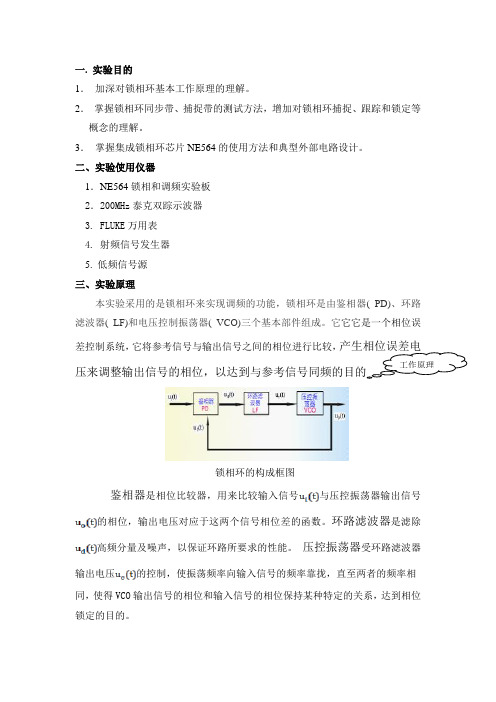

一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

二、实验使用仪器1.NE564锁相和调频实验板2.200MHz泰克双踪示波器3. FLUKE万用表4. 射频信号发生器5. 低频信号源三、实验原理本实验采用的是锁相环来实现调频的功能,锁相环是由鉴相器( PD)、环路滤波器( LF)和电压控制振荡器( VCO)三个基本部件组成。

它它它是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,产生相位误差电工作原理压来调整输出信号的相位,以达到与参考信号同频的目的。

锁相环的构成框图鉴相器是相位比较器,用来比较输入信号与压控振荡器输出信号的相位,输出电压对应于这两个信号相位差的函数。

环路滤波器是滤除高频分量及噪声,以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO输出信号的相位和输入信号的相位保持某种特定的关系,达到相位锁定的目的。

*判断环路是否锁定的方法在有双踪示波器的情况下,开始时环路处于失锁状态,加大输入信号频率,用双踪示波器观察压控振荡器的输出信号和环路的输入信号,当两个信号由不同步变成同步,且时,表示环路已经进入锁定状态。

锁相调频电路在普通的直接调频电路中,振荡器的中心频率稳定度较差,而采用晶体振荡器的调频电路,其调频范围又太窄。

采用锁相环的调频器可以解决这个矛盾。

锁相调频原理框图如下图所示锁相调频原理图 正如上面锁相调频原理图所示,实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外。

使压控振荡器的中心频率锁定在稳定度很高的晶振频率上,而随着输入调制信号的变化,振荡频率可以发生很大偏移。

这种锁相环路称载波跟踪型PLL ,本实验中使用的锁相环是NE564。

NE564内部压控振荡器的最高工作频率是50MHz ,从图10-5的逻辑框图中可以看到,NE564的内部包含一个限幅放大器,对外部的输入信号进行限幅放大,抑制寄生调幅,内部还包含压控振荡器和相位比较器。

锁相技术应用CD4046集成电路

锁相技术应用CD4046集成电路一、实验目的(1) 学习锁相环的工作原理、性能及使用方法;(2) 学习锁相环在调频信号解调中的应用原理。

二、实验要求(1) 装调CD4046锁相环电路,掌握锁定范围和有关参数之间的关系;(2) 观察和分析用锁相环调调频信号的工作过程。

三、锁相环的工作原理1、锁相环路的组成锁相环路为什么能够进入相位跟踪,实现输出与输入信号的同步呢?因为它是一个相位的负反馈控制系统。

这个负反馈控制系统是由鉴相器(PD )、环路滤波器(LF )和电压控制振荡器(VCO )三个基本部件组成的,基本构成如图1: )(1t θ )(t u d )(t u c )(2t θ图1实际应用中有各种形式的环路,但它们都是由这个基本环路演变而来的。

下面逐个介绍基本部件在环路中的作用(1) 鉴相器(PD )是一个相位比较装置,用来检测输入信号相位与反馈信号相位之间的相位差。

输出的误差信号是相差的函数,即鉴相特性可以是多种多样的,有正弦形特性、三角形特性、锯齿形特性等等。

常用的正弦鉴相器可用模拟相乘器与低通滤波器的串接作为模型。

(2) 环路滤波器(LP )具有低通特性,它可以起到图中低通滤波器的作用,更重要的是它对环路参数调整起差决定性的作用。

(3) 压控振荡器(VCO )是一个电压—―频率变换装置,在环中作为被控振荡器,它的振荡频率应随输入控制电压)(t u c 线性地变化。

实际应用中的压控振荡器的控制特性只有有限的线性控制范围,超出这个范围之后控制灵敏度将会下降。

压控振荡器应是一个具有线性控制特性的调频振荡器,对它的基本要求是:频率稳定度好(包括长期稳定度与短期稳定度);控制灵敏度0K 要高;控制特性的线性度要好;线性区域要宽等等。

这些要求之间往往是矛盾的,设计中要折衷考虑。

PD LF VCO压控振荡器电路的形式很多,常用的有LC压控振荡器、晶体压控振荡器、负阻压控振荡器和RC压控振荡器等几种。

前两种振荡器的频率控制都是用变容管来实现的。

锁相环CD4046的应用设计及研究_曾素琼

文章编号:1003- 0107(2012)01- 0072- 04

Ab s tra ct: In this p a p e r,p ha s e loc ke d loop is d is c us s e d of the p rinc ip le a nd a p p lic a tion,PLL fre q ue nc y

CKA,输出端为 QA;另一个为五进制计数电路,计数脉 冲输入端为 CKB,输出端为 QB,QC,QD,这两个计数器 可独立使用;当将 QA 连到 CKB;R 01、R02、R92、R91 接地, 当计数脉冲输入 CKA 时,可构成十进制计数器[7]。

图 7 所示;把 CD4046 的 3 脚与 QB 相连,即 74LS90 为 4 分频时,用示波器测 CD4046 的 4 脚得到频率输出为 3.96kHz (理论值为 4.0kHz)的正弦波形,如图 8 所示;把 CD4046 的 3 脚与 QC 相连,用示波器测 CD4046 的 4 脚 得到频率输出为 7.94kHz (理论值为 8.0kHz)的正弦波形, 如图 9 所示。

频率合成器和常规的振荡式正弦信号频率源相比, 其主要优点是:

(1)具有较高的频率长期稳定度,相位噪声小。若频 率合成器用恒温控制的高稳定度的石英晶体振荡器作 为基准频率源(或称主晶振)的话,则△f/f0 可达 10-10~ 10-8/ 日,而常规的振荡式正弦信号频率源,其稳定度一 般的只能达到△f/f0=10-8~10-5/ 日;

图 2 倍频锁相环频率合成原理方框图

2.2 基于锁相环 CD4046 频率合成器设计

2.2.1 锁相环 CD4046 介绍

CD4046 常使用集成电路的锁相环。它是通用的 CMOS 锁相环集成电路,其特点是电源电压范围宽 (为 3~18V),输入阻抗高(约 100MΩ),动态功耗小,在中心 频率 fo 为 10kHz 下功耗仅为 600μW,属微功耗器件。 CD4046 内部电原理框图如图 3 所示,它主要由相位比

锁相环芯片CD4046引脚,工作原理及应用电路

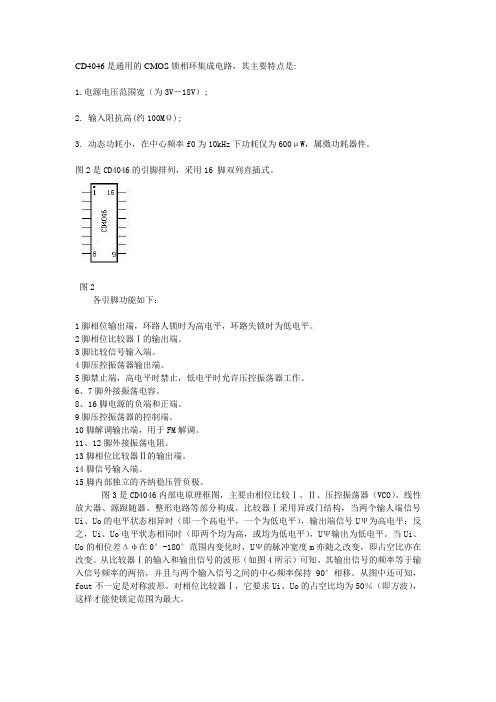

CD4046是通用的CMOS锁相环集成电路,其主要特点是:1.电源电压范围宽(为3V-18V);2. 输入阻抗高(约100MΩ);3. 动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

图2是CD4046的引脚排列,采用16 脚双列直插式。

图2各引脚功能如下:1脚相位输出端,环路人锁时为高电平,环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

图3是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

比较器Ⅰ采用异或门结构,当两个输人端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。

当Ui、Uo的相位差Δφ在0°-180°范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。

从比较器Ⅰ的输入和输出信号的波形(如图4所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°相移。

从图中还可知,fout不一定是对称波形。

对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

图3相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络。

它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。

它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一. 实验目的1. 加深对锁相环基本工作原理的理解。

2. 掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等 概念的理解。

3. 掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

二、实验使用仪器1.NE564锁相和调频实验板 2.200MHz 泰克双踪示波器 3. FLUKE 万用表 4. 射频信号发生器 5. 低频信号源 三、实验原理本实验采用的是锁相环来实现调频的功能,锁相环是由鉴相器( PD)、环路滤波器( LF)和电压控制振荡器( VCO)三个基本部件组成。

它它它是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,产生相位误差电压来调整输出信号的相位,以达到与参考信号同频的目的 。

锁相环的构成框图鉴相器是相位比较器,用来比较输入信号错误!未找到引用源。

与压控振荡器输出信号错误!未找到引用源。

的相位,输出电压对应于这两个信号相位差的函数。

环路滤波器是滤除错误!未找到引用源。

高频分量及噪声,以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压错误!未找到引用源。

的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO 输出信号的相位和输入信号的相位保持某种特定的关系,达到相位 锁定的目的。

工作原理*判断环路是否锁定的方法在有双踪示波器的情况下,开始时环路处于失锁状态,加大输入信号频率,用双踪示波器观察压控振荡器的输出信号和环路的输入信号,当两个信号由不同步变成同步,且错误!未找到引用源。

时,表示环路已经进入锁定状态。

锁相调频电路在普通的直接调频电路中,振荡器的中心频率稳定度较差,而采用晶体振荡器的调频电路,其调频范围又太窄。

采用锁相环的调频器可以解决这个矛盾。

锁相调频原理框图如下图所示锁相调频原理图 正如上面锁相调频原理图所示,实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外。

使压控振荡器的中心频率锁定在稳定度很高的晶振频率上,而随着输入调制信号的变化,振荡频率可以发生很大偏移。

这种锁相环路称载波跟踪型PLL ,本实验中使用的锁相环是NE564。

NE564内部压控振荡器的最高工作频率是50MHz ,从图10-5的逻辑框图中可以看到,NE564的内部包含一个限幅放大器,对外部的输入信号进行限幅放大,抑制寄生调幅,内部还包含压控振荡器和相位比较器。

环路低通滤波器外接,内部有一个放大器对鉴相器的输出电压进行放大,然后经过直流恢复器后得到模拟信号的输出。

内部还有一个斯密特触发器,可以得到TTL 电平的数字信号输出。

锁相环闭环的拉氏模型方程可以表示为:()()()()()V i s KF s H s s s KF s θθ==+()()()()V e e s sH s s s KF s θθ==+ 四、仿真锁相环传递函数锁相环误差传递函其输出调频波的波形如下:仿真的时候输出的波形是完好的调频波(是正弦波的形式),而实验输出的却不是这么好看的调频波,可见仿真与实验还是不能等同的,这也告诫我们在做后续的设计电路的时候,万不能太相信仿真,仿真出了结果可是实际焊的电路未出结果是很正常的。

五、实验内容:锁相环调频实验锁相环调频实验原理图电路原理图电路原理:电容C12和C13是5V的直流电源的去耦电容,NE564的1脚和10脚外接5V正电源,8脚接地。

12脚和13脚之间有一个可变电容,可以微调压控振荡器的中心频率,跳线开关S8可以切换固定电容,决定了载波中心频率的范围。

调制信号从J2输入,滑动变阻器W2分压控制输入调制信号的幅度,电容C1是隔直电容,调制信号从6脚输入鉴相器,电阻R1和电容C2是7脚外接的滤波电路。

9脚是压控振荡器的输出端,电阻R7是上拉电阻。

3脚是鉴相器的另外一个输入端,当跳线S1接到锁相环路时,构成锁相环路。

当跳线S1接到调频回路时,构成调频电路。

调频信号直接从9脚输出,在FM OUT端可以通过示波器观察调频信号。

芯片的4,5脚分别外接低通滤波器的滤波电容,跳线S3,S4的断开时,滤波电容是300pF,闭合时滤波电容是1300pF。

TP4是环路低通滤波器的输出端。

滑动变阻器W3可以调节低通滤波器的截止频率。

滑动变阻器W1可以调节芯片2脚的基准电流,从而调整NE564的频率锁定范围。

16脚是FSK解调的输出端,电阻R4是上拉电阻。

TP3处可以外接示波器观察FSK解调出的TTL电平的数字基带信号。

14脚是普通调频信号的解调输出端,电容C14是外接的积分电容。

15脚是NE564内部斯密特触发器的迟滞电压控制端,当跳线S6闭合时,可以通过滑动变阻器W4调节迟滞电压,来获得FSK解调出的正确的数字基带信号。

实验过程:本实验主要包括如下三个内容1. 压控振荡器的测试;2 . 同步带和捕捉带的测量;3. 调频信号的产生和测量。

Step 1. 压控振荡器的测试(1) 在实验箱主板上插上锁相环调频与测试电路实验模块。

接通实验箱上电源开关,电源指标灯点亮。

(2) 把跳线S1,S2,S5,S6,S7断开,S3,S4合上。

在这种状态下,单独测试压控振荡器的自由振荡频率:①将双排开关S8的5端合上,此时8200pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值,观察振荡频率是否有变化,并思考原因。

然后调节可变电容CW ,观察振荡频率的变化范围,并记录。

当合上S8的5端时,此时振荡器输出频率f=50.91kHz 的方波,Vpp=5.24V 其波形如下图图1图 1图2W1减小上图显示的是W1减小过程的波形变化,在实验过程中,我不断地交线W1的值,发现输出波的频率在不断改变,从起初的50.91kHz 变到了71.02kHz ,而幅度基本不变。

W1能改变输出波频率的原因:滑动变阻器W1可以调节芯片2脚的基准电流,从而调整NE564的频率锁定范围(查书)另外通过调节微变电容CW (此时使得W1保持不变),测得输出信号频率的变化范围为50.735~50.909kHz②将双排开关S8的6端合上,此时820pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值以及CW ,观察及记录振荡频率的变化。

③将双排开关S8的7端合上,此时82pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值以及CW ,观察及记录振荡频率的变化。

W1减小当合上S8的6端时,此时振荡器输出频率f=342.91kHz 的方波,其波形如下图图3。

与S8接到5端时的情况比较,输出频率普遍增大,这是因为S8所接的电容直接接入压控振荡器的12、13脚,它决定了振荡器的载波中心频率,接入的C 越小,振荡频率越大,这可由公式错误!未找到引用源。

得到。

S8接5的时候,接入了8200pF 的电容,而S8接6端时,只接入了820pF 的电容,所以接6端时振荡频率要普遍比它大。

上面两图显示的是W1减小过程的波形变化,同样我们发现输出波的频率随着W1的减小而增大,从起初的342.91kHz 变到了704.20kHz , 其原因在S8接5端的时候已经叙述。

另外调节微变电容CW (此时使得W1保持不变),测得输出信号频率的变化范围为487.281~505.7601kHz图3图4当合上S8的7端时,此时振荡器输出频率f=2.82MHz 的方波,其波形如下图图5。

因为此种情况,接入压控振荡器的是82pF 的电容,所以频率更进一步的增大时理所当然(前面原因解释:这是由频率牵引造成的。

在锁相环中,压控振荡器是一个电压—频率变换装置,在环中作为被控振荡器,它的振荡频率随输入控制电压错误!未找到引用源。

线性的变化(实际上,只是在一定范围内线性变化),即错误!未找到引用源。

,定义错误!未找到引用源。

,在错误!未找到引用源。

稍大于K 时,由于在一周内瞬时相差平均增长率不一样,使得鉴相器输出误差电压称为一个上下不对称的非正弦差拍波形,其频率为输入频率与振荡频率之差,属于有直流分量的情况。

这一非正弦差拍电压作用于VCO 上,使其振荡频率随之作相应规律的周期性变化,最终平均振荡频率偏离VCO 中心频率而向输入频率靠拢,此即为频率牵引现象。

下图即为频率牵引现象造成的输出波形: W1减小上面两图显示的是W1减小过程的波形变化,同样我们发现输出波的频率随着W1的减小而增大,从起初的2.82MHz 变到了3.46MHz , 其原因在S8接5端的时候已经叙述。

另外调节微变电容CW (此时使得W1保持不变),测得输出信号频率的变化范围为2.67~3.6MHz锁相环此时输出的已不是方波,上下已明显不对称?试解释其原因。

图5图6④将双排开关S8的8端合上,此时22pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值,观察振荡频率是否有变化,并思考原因。

然后调节可变电容CW ,观察振荡频率的变化范围,并记录。

Step 2. 同步带和捕捉带的测量把跳线S1接到锁相位置,把跳线S2, S6,S7断开,S3,S4,S5,S8的7端合(即接入82pF 的电容)上。

(1)调节可变电容CW 和滑动变阻器W1的值,,用示波器观察TP2处的波形,使其振荡频率达到4MHz (错误!未找到引用源。

作为参考值),用高频信号源当合上S8的7端,即接入22pF 电容时,此时振荡器输出频率f=7.8MHz 的方波,其波形如下图图7。

图7 图8 上面两图显示的是W1减小过程的波形变化,同样我们发现输出波的频率随着W1的减小而增大,从起初的7.69MHz 变到了11.87MHz ,其原因在S8接5端的时候已经叙述。

另外调节微变电容CW (此时使得W1保持不变),测得输出信号频率的变化范围为5.22~9.54MHz所以我们的输出波形才会出项前面的不对称波形产生频率为3.8MHz ,Vpp=4V 的正弦信号错误!未找到引用源。

,从TP1处输入。

(2)同步带和捕捉带的测量测量方法:基准频率错误!未找到引用源。

,一般情况下环路都会处于失锁状态,然后缓缓增加输入信号频率错误!未找到引用源。

,用双踪示波器仔细观察TP1和TP2处两信号之间(即错误!未找到引用源。

和错误!未找到引用源。

)之间的关系。

当发现两信号由不同步变为同步,表示环路进入刚进入到锁定状态,记下此时的频率错误!未找到引用源。

,这就是捕捉带的下限频率,继续增加错误!未找到引用源。

,此时压控振荡器频率错误!未找到引用源。

将随错误!未找到引用源。

而变。

但当错误!未找到引用源。