fpga开发工具-ise

ISE开发环境使用指南[FPGA开发教程

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

fpGa_CPLD设计工具xilinxISE使用详解

1.第一章:FPGA/CPLD简介●FPGA一般是基于SRAM工艺的,其基于可编程逻辑单元通常是由查找表(LUT,look up table)和寄存器(register)组成。

其中内部的查找表通常是4输入的,查找表一般完成纯组合逻辑功能;●Xilinx可编程逻辑单元叫做slice,它由上下两部分组成,每部分都由一个register加上一个LUT组成,被称为LC(logic cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合工作与级连;●Altera可编程逻辑单元叫做LE(Logic Element,逻辑单元),由一个register加上一个LUT构成;Lattice的底层逻辑单元叫做PFU(programmable Function unit,可编程功能单元),它由8个LUT和9个register组成。

●Ram和dpram/spram/伪双口RAM,CAM(content addressable memory)。

Fpga中其实没有专业的rom硬件资源,实现ROM是对RAM赋初置,并且保存此初值●CAM,即内容地址储存器,在其每个存储单元都包含了一个内嵌的比较逻辑,写入cam的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所以内部数据的地址。

总结:RAM是一种根据地址读/写数据的存储单元;而CAM 和RAM恰恰相反,它返回的是与端口数据相匹配的内部地址。

使用很广,比如路由器中的地址交换表等等●Xilinx块ram大小是4kbit和18kbit两种结构。

Lattice块ram是9kbit●分布式ram适合用于多块小容量的ram的设计;●Dll(delay-locked loop)延迟锁定回环或者pll(phase locked loop)锁相环,可以用以完成时钟的高精度,地抖动的倍频/分频/占空比调整/移相等功能。

Xilinx主要集成的是DLL,叫做CLKDLL,在高端的FPGA中,CLKDLL的增强型模块为DCM (digital clock manager,数字时钟管理模块)。

实验一ISE安装和开发流程

实验一ISE安装和开发流程ISE的安装2.运行安装程序,按照提示完成安装过程。

安装程序会要求选择安装路径、选择组件和许可证等信息,在这些选项中根据实际需求进行选择。

3.安装完成后,可以在开始菜单中找到ISE的快捷方式,通过点击该快捷方式打开ISE。

ISE的开发流程1. 创建新工程:打开ISE后,首先需要创建一个新工程。

在"File"菜单中选择"New Project",然后按照向导的指示填写工程名、工程路径等信息。

2. 添加设计文件:工程创建完成后,需要将相关的设计文件添加到工程中。

在ISE的工程导航器中,右键点击工程名,选择"Add Sources",然后选择要添加的设计文件。

可以添加Verilog、VHDL或其他支持的设计文件格式。

3. 设置仿真和综合选项:在设计文件添加完成后,需要设置仿真和综合选项。

在ISE的工程导航器中,右键点击工程名,选择"Properties",然后选择"Simulation"和"Synthesis"选项卡,按照需要进行配置。

4. 进行综合:在配置完成后,可以进行综合操作。

在ISE的工程导航器中,右键点击顶层设计文件,选择"Synthesize - Xilinx Synthesis Tool",然后等待综合过程完成。

综合将生成逻辑网表作为综合结果。

5. 进行约束:综合完成后,需要对设计进行约束。

约束是为了将设计与FPGA的物理资源进行对应,以满足目标性能和约束条件。

在ISE的工程导航器中,右键点击顶层设计文件,选择"Implement Design",然后进行约束配置。

6. 进行实现:约束配置完成后,可以进行实现操作。

在ISE的工程导航器中,右键点击顶层设计文件,选择"Generate Programming File",然后等待实现过程完成。

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

fpga开发工具-ise

Project Navigator的设置

• Edit -> Preferences • 选择编辑器、综合器、仿真器、片内逻辑分析仪

9

PN(工程管理器)工程创建向导(1)

• New -> New Project • 注意选择顶层模块类型:硬件描述语言HDL、原理图 Schematic

10

PN工程创建向导(2)

22

引脚约束

• 把引脚的名称用鼠标拖动到相应的位置即可 • 引脚约束的设计原则:

– 相关联的信号尽可能地安排在相邻的位置 – 如果相邻的位置安排不下,则应该安排在相邻的Bank – 对于时钟信号,应该安排在GCLK引脚上,以便获得较 快的速度

• 熟悉引脚的时候,用手工编辑约束文件的方式比 用鼠标拖动的方式更为方便 • Ucf约束文件中引脚约束的定义方式如下:

26

counter的综合报告

27

counter的RTL视图

28

实现

• 实现的三个步骤

– 翻译:将通用的NGC文件转换成为Xilinx的NGD文件 – 映射:将综合结果中的基本结构,映射成器件中的物 理资源 – 布局与布线:确定逻辑实现的位置和连线

• 在Process View中双击Implement Design即可完 成实现过程 • 实现的三个步骤中,每一步都可以产生一个仿真 的模型,仿真的效果与实际情况逐步逼近,布局 布线后的仿真模型与实际运行情况基本一致

• View RTL Schematic

– 查看RTL级别的电路图 – Pop和Push按钮用于在电路图的不同层次之间切换 – 建议初学者多看看RTL图,以加深对综合过程的认识

25

综合报告中的常见名词

• • • • • • • • • Pad:引脚 FF/Flip-Flop: FDCE:异步复位和时钟使能的D触发器 LUT:查找表 MUX:多路选通 XOR:异或 IBUF:输入缓冲门 OBUF:输出缓冲门 Fanout:扇出,一个逻辑部件的输出端可能连接到多个逻 辑部件的输入端,所连接的输入端的个数称为扇出数量

FPGA开发全攻略——ISE基本操作

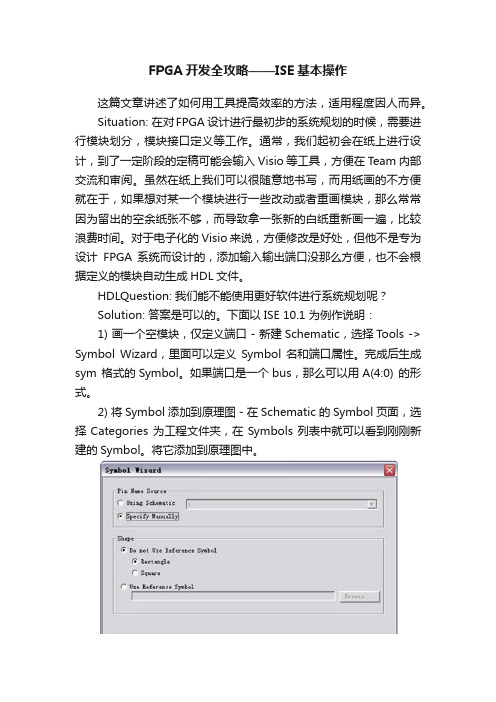

FPGA开发全攻略——ISE基本操作这篇文章讲述了如何用工具提高效率的方法,适用程度因人而异。

Situation: 在对FPGA 设计进行最初步的系统规划的时候,需要进行模块划分,模块接口定义等工作。

通常,我们起初会在纸上进行设计,到了一定阶段的定稿可能会输入Visio 等工具,方便在T eam 内部交流和审阅。

虽然在纸上我们可以很随意地书写,而用纸画的不方便就在于,如果想对某一个模块进行一些改动或者重画模块,那么常常因为留出的空余纸张不够,而导致拿一张新的白纸重新画一遍,比较浪费时间。

对于电子化的Visio 来说,方便修改是好处,但他不是专为设计FPGA 系统而设计的,添加输入输出端口没那么方便,也不会根据定义的模块自动生成HDL文件。

HDLQuestion: 我们能不能使用更好软件进行系统规划呢?Solution: 答案是可以的。

下面以ISE 10.1 为例作说明:1) 画一个空模块,仅定义端口 - 新建Schematic,选择Tools -> Symbol Wizard,里面可以定义Symbol名和端口属性。

完成后生成sym 格式的Symbol。

如果端口是一个bus,那么可以用A(4:0) 的形式。

2) 将Symbol 添加到原理图 - 在Schematic 的Symbol 页面,选择Categories 为工程文件夹,在Symbols列表中就可以看到刚刚新建的Symbol。

将它添加到原理图中。

3) 重复1-2 步骤,建立所有Symbol,并连接端口。

如果需要修改连线的名字或者模块的例化名,可以选择需要修改名字的元件然后按右键--> Object Properties --> 在Name/InstName 窗格中填入需要的名字。

4) 如需修改Symbol,可以直接在sym 文件中修改 - 可以按右键-> Add -> Pin 等等添加,也可以Copy已存在的Pin,然后改变PinName。

ISE软件使用说明

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

FPGA实验课件--ISE的使用与设计流程

分频器,100MHZ1HZ

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

3位计数器

高等教育出版社

基于verilog语言的ISE设计流程 --对该设计进行行为仿真

选中Simulation选项

选中counter.v,点击鼠标右键 选中New Source…

高等教育出版社 测试代码

ISE13.3集成开发环境介绍 --主界面介绍

工作区子窗口 源文件窗口

处理子窗口

高等教育出版社 脚本子窗口

基于verilog语言的ISE设计流程

--一个数字系统的设计原理

计数器

外部50MHz时钟

1Hz时钟

分频器生成 电路

3位的计 数器

LED灯显示计数值

top.v divider.v clk reset 分频器 1HZ counter.v 3位计数器 out[2:0]

选择Implement Design, 并展开

第三步: 布局和布线 ”Place & Route” 高等教育出版社

基于verilog语言的ISE设计流程 --查看布局布线后结果

选择Place & Route, 并展开 选择View/Edit Routed Design(FPGA Editor)

高等教育出版社

工程名

器件名字

生成了空的工程框架

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

选中器件名字,点击鼠标右键 选中New Source…

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

块存储器映像文件 在线逻辑分析仪Chipscope定义和连接文件

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

19

20

用户约束

• 三种类型的约束

– 时序约束: 逻辑设计所要满足的时序 – 引脚约束: 指定设计模块的I/O引脚位置 – 区域约束: 即逻辑设计所占用的资源

• 手动编辑约束

– User Constraints -> Edit Constraints (Text)

• 在小规模的低速逻辑设计中,一般不需要时序约

FPGA开发工具

1

主要内容

• Xilinx ISE

– Project Navigator:集成化开发环境 – Core Generator:核生成器 – StateCAD:状态机输入工具 – Timing Analyzer:时序分析器 – FloorPlanner:布局规划器 – FPGA Editor:FPGA底层编辑器

22

引脚约束

• 把引脚的名称用鼠标拖动到相应的位置即可 • 引脚约束的设计原则:

– 相关联的信号尽可能地安排在相邻的位置 – 如果相邻的位置安排不下,则应该安排在相邻的Bank – 对于时钟信号,应该安排在GCLK引脚上,以便获得较 快的速度

• 熟悉引脚的时候,用手工编辑约束文件的方式比 用鼠标拖动的方式更为方便 • Ucf约束文件中引脚约束的定义方式如下:

Core Generator简介

31

Core Generator简介

• Core Generator是由Xilinx提供的核生成器 • 它可以直接生成各种常见的IP核,以简化设计。比如RAM、 加法器等等 • 使用CoreGen的时候,需要新建一个CoreGen的工程,注: 此工程和Project Navigator中的工程无关! • 使用CoreGen生成的IP核时,只需要把CoreGen生成的IP 核源文件加入到Project Navigator的工程中即可 • 虽然有些IP核也可以自行编写,但是Core Gen所生成的IP 核经过专门针对器件的专业优化,其质量更高 • 在可以用CoreGen生成IP核的场合,建议尽量使用 CoreGen,但6.1版本的CoreGen存在不少bug!必要时可 以考虑更换更高的版本。

– 支持第三方编辑器、仿真器m来实现 • 最新版本为9.1,本课程基于6.1版

4

ISE 中集成工具及其基本功能

• ISE中的工具可以分为两部分,一是Xilinx自己提 供的软件工具,另外一些是其他EDA厂商提供的 软件工具,后者统称为第三方工具。 • Xilinx自带软件在ISE安装完成后即可直接使用, 包括了FPGA/CPLD设计流程中的常用工具。 • 第三方软件指专门EDA工具生产商提供的软件工 具,ISE集成了与这些设计工具的友好接口,在 ISE中可以直接调用这些工具。

16

17

语言模板使用介绍

• 将带有注释符号(--)的计数器端口定义的语句剪切 并粘贴到计数器的实体(entity)描述中去。计数 器端口定义语句如下:

Port( -- CLK: in STD_LOGIC; -- RESET: in STD_LOGIC; -- CE, LOAD, DIR: in STD_LOGIC; -- DIN: in STD_LOGIC_VECTOR(3 downto 0); -- COUNT: inout STD_LOGIC_VECTOR(3 downto 0); );

5

ISE 中集成工具及其基本功能

• 设计输入工具 HDL编辑器(HDL Editor)、状态机编辑器(StateCAD)、原理图编 辑器(ECS)、IP核生成器(Core Generator)和测试激励生成器 (HDL Bencher) 综合的本质是将HDL语言、原理图等设 • 综合工具 Synplicity公司的Synplify/Synplify Pro、Amplify; 计输入翻译成由与、或、非门,触发器, Synopsys公司的FPGA Compiler II(其早期版本为FPGA Express, RAM等基本逻辑单元组成的逻辑网表 已停止发展); (连接),并根据目标要求(约束条件) Mentor 公司旗下的Exemplar Logic公司出品的Leonardo Spectrum;

• View RTL Schematic

– 查看RTL级别的电路图 – Pop和Push按钮用于在电路图的不同层次之间切换 – 建议初学者多看看RTL图,以加深对综合过程的认识

25

综合报告中的常见名词

• • • • • • • • • Pad:引脚 FF/Flip-Flop: FDCE:异步复位和时钟使能的D触发器 LUT:查找表 MUX:多路选通 XOR:异或 IBUF:输入缓冲门 OBUF:输出缓冲门 Fanout:扇出,一个逻辑部件的输出端可能连接到多个逻 辑部件的输入端,所连接的输入端的个数称为扇出数量

优化生成的逻辑连接,输出edf和edn等 Xilinx ISE中的XST。 文件,供FPGA/CPLD厂家的布局布线器 进行实现。

注:XST是Xilinx自主开发的综合工具。虽然Xilinx设计综合软件 的经验还不够丰富,但只有Xilinx自己对其芯片的内部结构最了 解,所以XST的一些优化策略是其他综合工具无法比拟的。

6

ISE 中集成工具及其基本功能

常用的仿真工具还有:

• 仿真工具 Synopsys公司的VCS,Cadence公司的NC-Verilog和NCVHDL,Aldec公司的Active HDL,VHDL/Verilog HDL等。 ISE集成的仿真工具主要有Model Tech公司的仿 真工具ModelSim和测试激励生成器HDL Bencher 通过仿真能及时发现设计中的错误,加快设计进度,提高设 等 计的可靠性。 • 实现工具 综合结果的本质是一些由与、或、非门,触发器,RAM等基本 ISE集成的实现工具有约束编辑器(Constraints 逻辑单元组成的逻辑网表,它与芯片实际的配置情况还有较大 Editor)、引脚与区域约束编辑器(PACE)、时 差别。 此时应该使用FPGA/CPLD厂家的布局布线器,根据所选 序分析器(Timing Analyzer)、FPGA底层编辑 芯片的型号,将综合输出的逻辑网表适配到具体的FPGA/CPLD 器(FPGA Editor)、芯片观察窗(Chip Viewer) 器件上,这个过程就叫做实现过程。Xilinx的实现过程分为翻译 和布局规划器(Floorplanner)等

18

语言模板使用介绍

• 去掉counter_demo.vhd源程序中端口定义语句前 的注释符号(--)。 • 去掉COUNT端口定义语句后的分号(;): COUNT: inout STD_LOGIC_VECTOR(3 downto 0) • 选择【File】->【Save】,保存 counter_demo.vhd源程序。

14

HDL编辑器

• 常规创建工程文件的步骤(演示) • 使用语言模板可以达到事半功倍的效果 (以计数器为例介绍)

15

语言模板使用介绍

• 选择【Edit】->【Language Template】,打开 语言设计模板,或者通过单击工具栏中最又端的 灯泡按钮来打开语言模板。 • 在语言模板【Language Templates】窗口中,通 过单击符号“+”来展开VHDL下的综合模板 【Synthesis Templates】 • 从VHDL综合模板中选择计数器(Counter)模板, 并把它拖动或粘贴到源程序counter_demo.vhd的 begin和end之间。 • 关闭计数器语言模板窗口

• 选择器件型号、封装、速度等级 • 选择综合器、仿真器、仿真语言

11

向PN加入新的源文件

• 关键要选择好源文件的类型

12

设计流程

• • • • • • 编写源文件 制定用户约束 综合 实现 生成编程文件 使用逻辑分析仪分析

13

设计输入工具

• • • • • HDL编辑器(HDL Editor) 状态机编辑器(StateCAD) 原理图编辑器ECS(Schematic Editor) IP核生成器(Core Generator) 测试激励生成器(HDL Bencher)

• ModelSim:仿真工具 • Xilinx ChipScope Pro:片内逻辑分析仪

2

• 第一部分:Xilinx ISE

3

ISE简介

• • • • 由Xilinx公司开发,由Foundation系列发展而来。 支持Xilinx全部CPLD和FPGA器件 支持Verilog和VHDL 除了仿真以外,其它的FPGA设计流程(设计输 入、仿真、逻辑综合、布局布线与实现、时序分 析、芯片下载与配置、功耗分析等)都可以通过 ISE来完成

8

Project Navigator的设置

• Edit -> Preferences • 选择编辑器、综合器、仿真器、片内逻辑分析仪

9

PN(工程管理器)工程创建向导(1)

• New -> New Project • 注意选择顶层模块类型:硬件描述语言HDL、原理图 Schematic

10

PN工程创建向导(2)

24

综合

• 综合的目的是把HDL转换成基本电路结构或者宏单元,比 如LUT、Flip-Flop、加法器等 • 在Process View中双击Synthesis即可完成综合过程 • View Synthesis Report

– 在Final Report可以看到各种资源的利用率 – 在Timing Summary可以看到最高运行频率 – 注意,综合报告中的频率只是在综合过程中的理论值。实际值要 低于这个频率!

26

counter的综合报告

27

counter的RTL视图

28

实现

• 实现的三个步骤

– 翻译:将通用的NGC文件转换成为Xilinx的NGD文件 – 映射:将综合结果中的基本结构,映射成器件中的物 理资源 – 布局与布线:确定逻辑实现的位置和连线