电子科技大学数字逻辑第六章习题答案

数字电子技术第6章习题及解答2

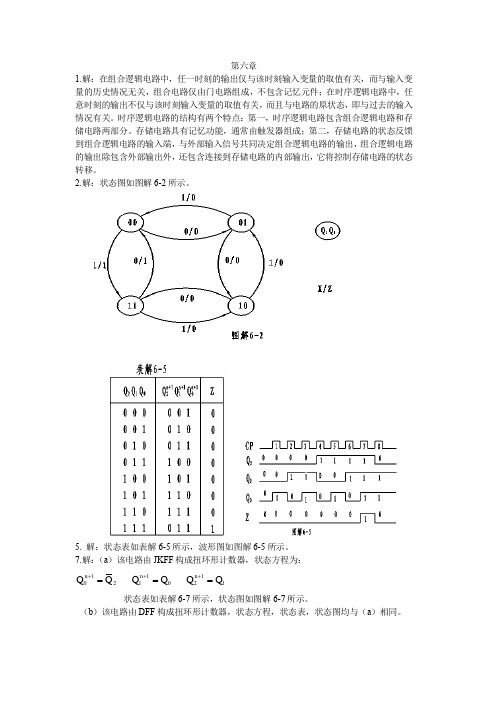

第6章习题解答1. 电路如图6-1所示,试分析其功能。

(1)写出驱动方程、次态方程和输出方程;(2)列出状态表,并画出状态图和时序波形。

图6-1 题1图z解 (1)根据图6-1写出驱动方程'1'21Q Q D =, 12Q D =将其代入D 触发器的特性方程,得每一触发器的状态方程'1'21*1Q Q D Q ==12*2Q D Q ==输出方程为 CP Q z ⋅=2(2)由状态方程可列出状态表如表6-1所示。

按表00,可作出时序波形图如图6-2(b )所示。

图6-2 题1状态图和波形图CP Q 2Q 1z(a )(b )2. 时序电路如图6-3所示。

(1)写出该电路的状态方程、输出方程;(2)列出状态表,画出状态图。

图6-3 题2图解 (1)驱动方程 x K J ==11 122xQ K J ==将其代入JK 触发器的特性方程,的状态方程21'21*21'1*1)'('Q xQ Q xQ Q Q x xQ Q +=+=输出方程 21Q xQ z =(2)假定一个现态,代入状态方程,得出对应的次态和输出状态,列表表示即得状态表,如表6-2所示。

由此算出状态图,如图6-4所示。

表6-2 题2状态表图6-4 题2的状态图3. 某计数器的输出波形如图6-5所示,试确定该计数器是模几计数器,并画出状态图。

图6-5 题3图CP Q A Q B QC解 由波形图画出状态图,Q C 为高位,Q A 为最低位。

010000001100011101Q C Q B Q A故该波形显示的计数器的计数模为六。

4. 分析如图6-6所示的同步时序电路。

图6-6 题4图解 (1)有题图得到各级触发器的驱动方程为⎪⎪⎩⎪⎪⎨⎧====34231242'3'11)'(Q D Q D Q D Q Q Q Q D(2)列出状态方程为⎪⎪⎩⎪⎪⎨⎧========34*423*312*242'3'11*1)'(Q D Q Q D Q Q D Q Q Q Q Q D Q由驱动方程和状态方程可以确定,该电路是移位寄存器型时序电路,其电路的状态转移决定于第一级的驱动信号。

数字逻辑+课后答案数字逻辑+课后答案

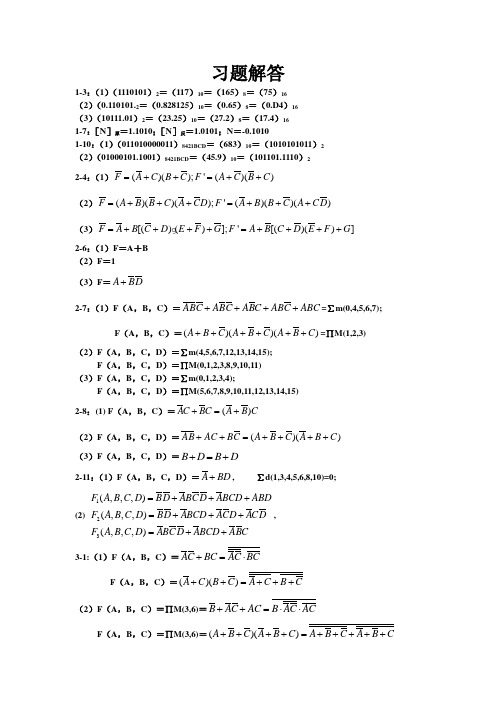

习题解答1-3:(1)(1110101)2=(117)10=(165)8=(75)16 (2)(0.110101.2=(0.828125)10=(0.65)8=(0.D4)16 (3)(10111.01)2=(23.25)10=(27.2)8=(17.4)16 1-7:[N ]原=1.1010;[N ]反=1.0101;N =-0.1010 1-10:(1)(011010000011)8421BCD =(683)10=(1010101011)2 (2)(01000101.1001)8421BCD =(45.9)10=(101101.1110)2 2-4:(1)()();'()()F A C B C F A C B C =++=++(2)()()();'()()()F A B B C A CD F A B B C A CD =+++=+++ (3)[()()];'[()()]F A B C D E F G F A B C D E F G =++++=++++ 2-6:(1)F =A +B (2)F =1 (3)F =A BD +2-7:(1)F (A ,B ,C )=ABC ABC ABC ABC ABC ++++=∑m(0,4,5,6,7);F (A ,B ,C )=()()()A B C A B C A B C ++++++=∏M(1,2,3)(2)F (A ,B ,C ,D )=∑m(4,5,6,7,12,13,14,15);F (A ,B ,C ,D )=∏M(0,1,2,3,8,9,10,11) (3)F (A ,B ,C ,D )=∑m(0,1,2,3,4);F (A ,B ,C ,D )=∏M(5,6,7,8,9,10,11,12,13,14,15) 2-8:(1) F (A ,B ,C )=()A C BC A B C +=+(2)F (A ,B ,C ,D )=()()AB AC BC A B C A B C ++=++++ (3)F (A ,B ,C ,D )=B D B D +=+2-11:(1)F (A ,B ,C ,D )=A BD +, ∑d(1,3,4,5,6,8,10)=0;(2) 123(,,,)(,,,)(,,,)F A B C D BD ABCD ABCD ABDF A B C D BD ABCD ACD A CD F A B C D ABCD ABCD ABC=+++=+++=++,3-1:(1)F (A ,B ,C )=AC BC AC BC +=⋅F (A ,B ,C )=()()A C B C A C B C ++=+++(2)F (A ,B ,C )=∏M(3,6)=B AC AC B AC AC ++=⋅⋅F (A ,B ,C )=∏M(3,6)=()()A B C A B C A B C A B C ++++=+++++(4)F (A ,B ,C ,D )=AB A C BCD AB ++=F (A ,B ,C ,D )=0AB A C BCD A B A B ++=+=++3-3:F (A ,B ,C )=[()()][()()]A B C B C A C B C B C ABC ABC ABC +++⋅+++=++ 3-7:(2)根据真值表,列出逻辑函数表达式,并化简为“与非”式。

电子科大-微机原理习题解答-chap6

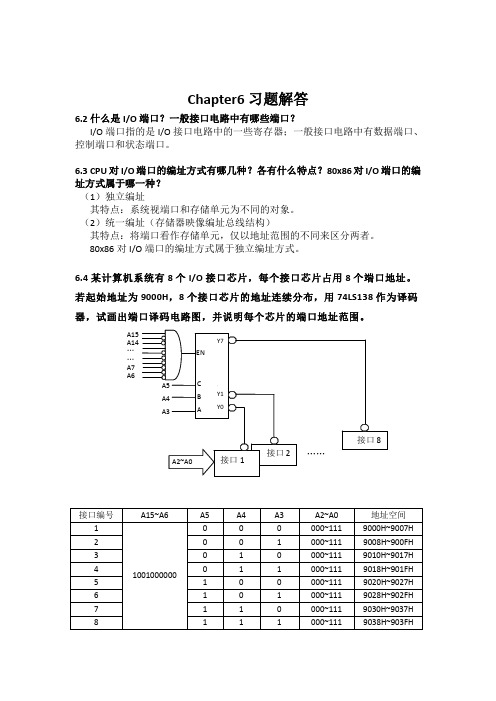

Chapter6习题解答6.2什么是I/O 端口?一般接口电路中有哪些端口?I/O 端口指的是I/O 接口电路中的一些寄存器;一般接口电路中有数据端口、控制端口和状态端口。

6.3 CPU 对I/O 端口的编址方式有哪几种?各有什么特点?80x86对I/O 端口的编址方式属于哪一种? (1)独立编址其特点:系统视端口和存储单元为不同的对象。

(2)统一编址(存储器映像编址总线结构)其特点:将端口看作存储单元,仅以地址范围的不同来区分两者。

80x86对I/O 端口的编址方式属于独立编址方式。

6.4某计算机系统有8个I/O 接口芯片,每个接口芯片占用8个端口地址。

若起始地址为9000H ,8个接口芯片的地址连续分布,用74LS138作为译码器,试画出端口译码电路图,并说明每个芯片的端口地址范围。

A15 A14 … … A7 A66.6 CPU与I/O设备之间的数据传送有哪几种方式?每种工作方式的特点是什么?各适用于什么场合?①无条件控制(同步控制):特点:方式简单,CPU随时可无条件读/写数据,无法保证数据总是有效,适用面窄。

适用于外设数据变化缓慢,操作时间固定,可以被认为始终处于就绪状态。

②条件控制(查询控制):特点:CPU主动,外设被动,执行I/O操作时CPU总要先查询外设状态;若传输条件不满足时,CPU等待直到条件满足。

解决了CPU与外设间的同步问题,可靠性高,但CPU利用率低,低优先级外设可能无法及时得到响应。

适用于CPU不太忙,传送速度不高的场合。

③中断方式:特点:CPU在执行现行程序时为处理一些紧急发出的情况,暂时停止当前程序,转而对该紧急事件进行处理,并在处理完后返回正常程序。

CPU利用率高,外设具有申请CPU中断的主动权,可以实现实时故障处理,实时响应外设的处理,但中断服务需要保护断点(占用存储空间,降低速度)。

适用于CPU的任务较忙,传送速度要求不高的场合,尤其适用实时控制中紧急事件的处理。

西安电子科技大学数电答案第六章

39.试分析图 P6-39 所示的各时序电路。 (1)列出图(a),(b), (c), (d)各电路的状态表,指出电路的逻辑功能。 (2)画出图(e),(f)电路的输出波形,指出电路的逻辑功能。 解: (1)图(a)的态序表如表解 6-39(a)所示,该电路为模 6 计数器(或 6 分频电路) ,

n 1 8.解:状态方程为: Q0 X , Q1n1 XQ0 XQ1

输出函数为: Z X Q1 状态表如表解 6-8 所示,状态图如图解 6-8 所示。 逻辑功能为:110 序列检测器。

9.

n 1 n 1 Q 0 Q 2 Q1 Q 2 Q0 Q1Q2 , Q1n1 Q0 , Q2 Q1 解:状态方程为: Q0

15. 解:设 S 0 为初始状态;

S1 为接收到一个 1 的状态;

S 2 为在收到 1 后接收到一个 0 的状态;

S 3 为在顺序收到 10 后接收到一个 1 的状态;

S 4 为在顺序收到 101 后接收到一个 1 的状态;状态图如图解 6-15(1) (2)所示.

16.解: (a)最大等价类为:[AF],[BE],[CG],[D],简化状态表如表解 6-16(a)所示。 (b)最大等价类为:[ABC],[D],[E],简化状态表如表解 6-16(b)所示。

37.解:用 74LS161 实现模 7 计数器,组合电路真值表如表解 6-37 所示。逻辑电路如图解 6-37 所示。

38.解: (1)用 74LS161 实现模 7 计数,Z 由 CP 和 X 相与得到,函数表如表解 6-38(1) 所示,逻辑电路图如图解 6-38(1)所示。

(2)采用计数型:可用 74LS194 构成模 6 扭环型计数器,然后再用一片 3-8 译码器实 现双序列码输出:Z1 110100 , Z 2 010011 。 序列码输出函数表如表解 6-38 (2) 所示, 逻辑电路图如图解 6-38(2)所示。 (3)八路脉冲分配器:用 74LS161 实现模 8 计数,时钟 CP 同时作为 3-8 译码器的 选通信号,只有当 CP=1 时才有译码输出,其电路图和波形图如图解 6-38(3a)(3b)所示。

数字逻辑课后习题答案科学出版社_第五版(DOCX页)

第一章开关理论基础1.将下列十进制数化为二进制数和八进制数十进制二进制八进制49 110001 6153 110101 65127 1111111 177635 1001111011 11737.493 111.1111 7.7479.43 10011001.0110111 231.3342.将下列二进制数转换成十进制数和八进制数二进制十进制八进制1010 10 12111101 61 751011100 92 1340.10011 0.59375 0.46101111 47 5701101 13 153.将下列十进制数转换成8421BCD码1997=0001 1001 1001 011165.312=0110 0101.0011 0001 00103.1416=0011.0001 0100 0001 01100.9475=0.1001 0100 0111 01014.列出真值表,写出X的真值表达式A B C X0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1 X=A BC+A B C+AB C+ABC5.求下列函数的值当A,B,C为0,1,0时:A B+BC=1(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,1,0时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,0,1时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=06.用真值表证明下列恒等式(1) (A⊕B)⊕C=A⊕(B⊕C)A B C (A⊕B)⊕C A⊕(B⊕C)0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 0 01 0 0 1 11 0 1 0 01 1 0 0 01 1 1 1 1所以由真值表得证。

(2)A⊕B⊕C=A⊕B⊕CA B C A⊕B⊕C A⊕B⊕C0 0 0 1 10 0 1 0 00 1 0 0 00 1 1 1 11 0 0 0 01 0 1 1 11 1 0 1 11 1 1 0 07.证明下列等式(1)A+A B=A+B证明:左边= A+A B=A(B+B)+A B=AB+A B+A B=AB+A B+AB+A B=A+B=右边(2)ABC+A B C+AB C=AB+AC证明:左边= ABC+A B C+AB C= ABC+A B C+AB C+ABC=AC(B+B)+AB(C+C)=AB+AC=右边(3)EDCCDACBAA)(++++=A+CD+E 证明:左边=EDCCDACBAA)(++++=A+CD+A B C+CD E=A+CD+CD E=A+CD+E=右边(4) C B A C B A B A ++=C B C A B A ++ 证明:左边=C B A C B A B A ++=C B A C AB C B A B A +++)( =C B C A B A ++=右边8.用布尔代数化简下列各逻辑函数表达式 (1) F=A+ABC+A C B +CB+C B = A+BC+C B (2) F =(A+B+C )(A+B+C) = (A+B)+C C = A+B(3) F =ABC D +ABD+BC D +ABCD+B C = AB+BC+BD (4) F=C AB C B BC A AC +++= BC(5) F=)()()()(B A B A B A B A ++++=B A 9.将下列函数展开为最小项表达式 (1) F(A,B,C) = Σ(1,4,5,6,7)(2) F(A,B,C,D) = Σ(4,5,6,7,9,12,14) 10.用卡诺图化简下列各式(1)C AB C B BC A AC F +++=0 ABC00 01 11 1011111化简得F=C(2)C B A D A B A D C AB CD B A F++++=111111AB CD 00 01 11 1000011110化简得F=D A B A +(3) F(A,B,C,D)=∑m (0,1,2,5,6,7,8,9,13,14)1111111111AB CD 00 01 11 1000011110化简得F=D BC D C A BC A C B D C ++++(4) F(A,B,C,D)=∑m (0,13,14,15)+∑ϕ(1,2,3,9,10,11)Φ1ΦΦ1ΦΦ1Φ1AB CD 00 01 11 1000011110化简得F=AC AD B A ++11.利用与非门实现下列函数,并画出逻辑图。

杭州电子科技大学计算机组成原理第6章作业答案

作业

P253:1,2,4,10,12,16

6.1 指令包括哪几部分?各表示什么含意?

解:

指令包括操作码和地址码 操作码:用来指明该指令所要完成的操作,即定义指 令的功能 地址码:用来寻找执行指令所需要的操作数,即操作 数的地址信息。

6.2 在一地址指令、二地址指令中,如何指定二个操 作数地址?如)32, -128 -+127 2)

• • • • • • 立即寻址:无有效地址 直接寻址:EA=D 间接寻址:EA=(D) 变址寻址:EA=(RI)+D 基址寻址:EA=(Rb)+D 相对寻址:EA=(PC)+D 立即寻址:无 直接寻址:0-255 间接寻址:0-216-1,即0-65535 变址寻址:0-216-1+127, 0-216+126 基址寻址:0-216-1+127 , 0-216+126 相对寻址: 0-216-1+127, 0-216+126

1110 00_0000 … 1110 11_1111 1111 00_0000 … 1111 00_1111

A1

操作码 16位

零地址指 令 1111 01_0000 000000 … 1111 01_0000 111011

6.10 某机16位字长指令格式如下:

电子科技大学《数字逻辑设计及应用》solu

y z Next state of state A

00 01 11 10

Wx

00 BB BB CC A

01 AA,,BB AA,,BB AA AA 11 AA AA AA AA 10 A A CC A

下一状态未定 义,不满足完 备性。

下一状态不 唯一,不满 足互斥性。

For state C: Z+z’=1 Z∙z’=0 同时满足互斥和完备性。

S*,Z

16

,

补充题 3

已知某状态机针对D触发器的激励/输出表如表3所示,请导出最 小成本激励方程和输出方程

Q1Q0

D1

x

0

0

d

0

0

1d

1

D 1Q 0XQ 1X

表3:激励/输出表

Q1Q0

00 01 10 11

X

0

1

0 0 ,0 0 1 ,0

0 0 ,0 1 0 ,0

0 0 ,0 1 0 ,1

Dd1dD, 0d, Z

10

1 101

Q1*=D1= Q1x’y’+Q1’xy+Q1’Q2y +Q1’Q2x+Q1Q2’x’+Q1Q2’y’

Q2*=D2=Q2x’y’+Q2’x’y+Q2xy+Q2’xy’

xy

Q2*

00 01 11 10

Q1Q2

00 0 1 0 1

01 1

0 10

D1= Q2x’y+Q1x’y+Q1’x’y’ +Q2xy ’

only if x continues to be 1111 or 1001, the output z is 1. Otherwise, the

《数字逻辑》(第二版)习题答案 第六章

习题六1分析图1所示脉冲异步时序逻辑电路。

(1) 作出状态表和状态图;(2) 说明电路功能。

图1解答(1)该电路是一个Mealy型脉冲异步时序逻辑电路。

其输出函数和激励函数表达式为(2)电路的状态表如表1所示,状态图如图2所示。

图2(3) 由状态图可知,该电路是一个三进制计数器。

电路中有一个多余状态10,且存在“挂起”现象。

2 分析图3所示脉冲异步时序逻辑电路。

(1) 作出状态表和时间图;(2) 说明电路逻辑功能。

图3解答○1该电路是一个Moore型脉冲异步时序逻辑电路,其输出即电路状○2电路状态表如表2所示,时间图如图4所示。

表2图4○3 由状态表和时间图可知,该电路是一个模6计数器。

3 分析图5所示脉冲异步时序逻辑电路。

(1) 作出状态表和状态图; (2) 说明电路逻辑功能。

图5解答○1该电路是一个Moore型脉冲异步时序逻辑电路,其输出函数和激励函数表达式为○2该电路的状态表如表3所示,状态图如图6所示。

图6○3该电路是一个“x1—x2—x3”序列检测器。

4分析图7所示脉冲异步时序电路,作出时间图并说明该电路逻辑功能。

图7解答○1该电路是一个Moore型脉冲异步时序逻辑电路,其输出即电路状态。

激励函数表达式为○2电路次态真值表如表4所示,时间图如图8所示。

图8○3该电路是一个模4计数器。

5 用D触发器作为存储元件,设计一个脉冲异步时序电路。

该电路在输入端x的脉冲作用下,实现3位二进制减1计数的功能,当电路状态为“000”时,在输入脉冲作用下输出端Z 产生一个借位脉冲,平时Z 输出0。

解答○1设状态变量用y 2y 1y 0表示根据题意,可作出三位二进制减1计数器的状态转移表如表5所示。

○2 分析表5所示状态转移关系,可发现如下规律:● 最低位触发器的状态y 0只要输入端x 有脉冲出现便发生变化,即每来一个输入脉冲,触发器产生一次翻转。

因此,可令该触发器时钟端信号C 0=x ,输入端信号00y D =。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

01 11 10 1 d 0 d d d d d

d

d

d

1

d

d

d

d

K1 Q0C 00 01 11 10 Q 2 Q1

00 01 d 0 0 d d 0 d 1 0 d 0 1

11

14

10

d

d

d

d

J1 Q0C 00 01 11 10 Q 2 Q1

00

J1 Q2 C

1 d

0 d

d d

d d

01 11 10

X

Q2n

Q1n

Q2n+1 Q1n+1

Z

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

0 1 1 0 1 0 0 1

1 0 1 0 1 0 1 0

0 0 0 1 1 0 0 0

(3) 状态转换图

X/Z 0/0 1/0

00 0/1 1/1 11

01

1/0 1/0

J 3 X Q1Q2、K 3 1 J 2 Q3 ( X Q1 )、K 2 X Q1 J1 X Q3、K1 Q2 Z X Q3

电路图省略

20、试用JK触发器设计一个六进制减法计数器。

000

/1

/0

001

/0

010 /0

101

/0

100

/0

011

Q3n 0 0 0 0 1 1 1 1

J 2 Q1 Q0 C

01 11 10

d

d

d

d

K2 Q0C 00 01 11 10 Q 2 Q1

00 d d d d

K 2 Q0 C

13

01

d

1 d

d

0 0

d

1 d

d

1 d

11

10

现态 Q2 Q1 Q0 000 001 010 011 100 101 110 111 Q -> Qn+1 0 0 0 1 1 0 1 1

1/0

1/1

11、

表6-1 (A,E),B,C,D,F,G 表6-2 A,(B,F),C,(D,E)

12、

表6-3 (A,B,F),(B,E,F)(C,D) 表6-4 (A,B,C),(A,C,D)(A,D,E)

13、

表6-5

A(00),B(01),C(10),D(11) 表6-6

A(00),B(01),C(11),D(10)

Z

Q2n+1 Q1n+1

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

0 1 1 0 0 0 1 0

1 0 0 1 0 0 1 0

0 0 0 1 0 0 0 0

电路图省略

18、试用JK触发器设计一个“110”代码检测器。 0/0 B 0/0 D 0/0 1/0 1/0 E 0/0 1/0 0/0 F A 1/0 C 1/0

现态 Q 2Q 1Q 0 000 001

次态/输出 C=0 C=1 110/0 100/0 111/0 100/0

010 011 100 101 110 111

011/0 111/0 010/0 010/0 010/0 000/1

001/0 000/1 110/0 011/0 111/0 011/0

0/0 10

0/0

(4) 时序图 1 2 3 4 5

1 2 3 4 5

CP X Q1n Q2n Y

CP X Q1n

Q2n Y

“1”

“0”

(5) 电路功能:X=0时,4进制加法计数器; X=1时,4进制减法计数器。

4进制可异计数器(可加可减)。

9、作出“1011”序列检测器的状态图。典型输入、 输出序列如下。 输入X:1010101101100011110110001 输出Z:0000000100100000000010000 1/0 解: 1/0 0/0 X/Z S0 S1 0/0 0/0 0/0 S3 S2

J1=K1=1 J2=K2=XQ1 Z=XQ1Q2+XQ1 Q2

写出状态方程

根据Q

n 1

n 1 n 1

JQ KQ得

Q1 X Q1 Q 2

Q1

Q2

(2) 状态转换表

Q

n 1 1

Q

n 1

n 1 n Q2 X Q1n Q2

n n Z X Q1nQ2 X Q1n Q2

次态/输出 C=0 C=1 110/0 ddd/0 011/0 111/0 ddd/0 ddd/0 010/0 000/1 J 0 1 d d K d d 1 0 100/0 ddd/0 ddd/0 000/1 110/0 ddd/0 111/0 011/0

J1 Q0C 00 01 11 10 Q 2 Q1

17、试用JK触发器设计一个“0010”串行序列检测 器(可重叠)。 X/Z 0/0 S1 0/0

1/0

S0 1/0

1/0 0/1

S3

1/0

S2

0/0

1/0 S0 1/0 S3

X Q2n

0/0 1/0 0/1 1/0

Q1n

S1 S2

J 2 X Q1、K 2 Q1

0/0 J1 X Q2、K1 X Q2 Z X Q2Q1 0/0

01 11 10

d

0

d

d

K0 Q0C 00 01 11 10 Q 2 Q1

00

K 0 Q 2C Q 2 C

d

d

d

d

01

d

d d

d

d d

1

0 d

0

1 d

11

17

10

(3) 检查自启动问题

1 Qn Q2 Q1 Q2Q0 C Q2 Q0C 2 n 1 Q1 Q2 Q1 Q1 C Q2Q1 Q0 Q2Q1C Q2Q1 C Q1 Q0 C 1 Qn Q2Q1 Q0 Q1 Q0C Q2Q0C Q2Q0 C 0

110/0 ddd/d

111/0 011/0

(2) 求输出方程、状态方程、激励方程

现态 Q2 Q1 Q0 000 001 010 011 100 101 110 111 次态/输出 C=0 C=1 110/0 ddd/d 011/0 111/0 ddd/d ddd/d 010/0 000/1 100/0 ddd/d ddd/d 000/1 110/0 ddd/d 111/0 011/0

d

d

K1 Q2C Q2Q0 C

K1 Q0C 00 01 11 10 Q 2 Q1

00 01 d 0 0 d d 0 d 1 0 d 0 1

11

15

10

d

d

d

d

现态 Q2 Q1 Q0 000 001 010 011 100 101 110 111 Q -> Qn+1 0 0 0 1 1 0 1 1

16、试用JK触发器设计一个可控计数器。 当C=1时,实现000→100→110→111→011→000; 当C=0时,实现000→110→010→011→111→000。

解:(1)根据题意,现态 状态表为: Q2 Q1 Q0

000 001 010 011 100 101 110 111 次态/输出 C=0 110/0 ddd/d 011/0 111/0 ddd/d ddd/d 010/0 000/1 C=1 100/0 ddd/d ddd/d 000/1

1/0 000 0/0

010

1/0 0/0

100

1/0 0/1 1/0 0/0

001

1/0 0/0

011

X 1 1 1 1 1 1 1 1

Q3n 0 0 0 0 1 1 1 1

Q2n Q1n Q3n+1 Q2n+1 Q1n+1 Z 0 0 0 1 0 0 0 1 0 1 1 0 1 0 1 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 1 d d d d 1 0 d d d d 1 1 d d d d

G

0/0 1/0 0/1 1/0

由图可见:状态D、E、F是等效的。故可以消去D 和E ,得以下化简后的状态图:

A A 0/0 B 0/0 D 1/0 C 0/0 0/0 0/0 1/0 F G B 1/0 C 1/0

1/0 E

0/0

F

1/0 G

0/0 1/0 0/0 1/0 0/0 1/0 0/1 1/0 0/0 1/0 0/1 1/0

0 1

1 0

0 0

可自启动也无错误输出。电路省略。

23、试利用74LS161构成160进制计数器。 解:根据第141页表6-34中的功能表,74LS161为 异步清0和同步置数。 160进制计数器的有效状态为0-159 所以:若采用异步清0法,则在160状态产生 异步清0信号。 160=10100000 若采用同步置数,则在159状态产生预置数。 159=10011111

00

01 11 10 0 1 0 0 d 1 d d d d d d

d

0

d

d

K0 Q0C 00 01 11 10 Q 2 Q1

00 01 d d d d

d

d d

d

d d

1

0 d

0

1 d

11

16

10

J0 Q0C 00 01 11 10 Q 2 Q1

00

0 1 0 0 d 1 d d d d d d

J 0 Q2Q1 Q1C